Atmel ATmega2564 8bit AVR микроконтролер

Характеристики

- Мрежова поддръжка чрез хардуерно подпомагано филтриране на множество PAN адреси

- Разширено хардуерно подпомагане Намалена консумация на енергия

- Високопроизводителен 8-битов микроконтролер AVR® с ниска мощност

- Разширена RISC архитектура

- 135 мощни инструкции - изпълнение на най-много цикъла на часовника

- 32×8 работни регистри с общо предназначение / множител с 2 цикъла на чип

- До 16 MIPS пропускателна способност при 16 MHz и 1.8 V – напълно статична работа

- Енергонезависима памет за програми и данни

- 256K/128K/64K байта вградена в системата самопрограмируема флаш памет

- Издръжливост: 10'000 цикъла на запис/изтриване при 125°C (25'000 цикъла при 85°C)

- 8K/4K/2K байта EEPROM

- Издръжливост: 20'000 цикъла на запис/изтриване при 125°C (100'000 цикъла при 25°C)

- 32K/16K/8K байта вътрешна SRAM

- JTAG (IEEE std. 1149.1 съвместим) Интерфейс

- Възможности за гранично сканиране според JTAG Стандартен

- Разширена поддръжка за отстраняване на грешки в чип

- Програмиране на Flash EEPROM, предпазители и заключващи битове чрез JTAG интерфейс

- Периферни характеристики

- Множество канали за таймер/брояч и ШИМ

- Брояч в реално време с отделен осцилатор

- 10-битов, 330 ks/s A/D конвертор; аналогов компаратор; Вграден температурен сензор

- Главен/подчинен SPI сериен интерфейс

- Два програмируеми серийни USART

- Байт-ориентиран двупроводен сериен интерфейс

- Разширено обработване на прекъсвания и режими за пестене на енергия

- Таймер за наблюдение с отделен осцилатор в чипа

- Нулиране при включване и детектор за нисък ток

- Напълно интегриран приемо-предавател с ниска мощност за 2.4 GHz ISM обхват

- Висока мощност Ampподдръжка на lifier чрез потискане на страничния лоб на TX спектъра

- Поддържани скорости на данни: 250 kb/s и 500 kb/s, 1 Mb/s, 2 Mb/s

- -100 dBm RX чувствителност; TX изходна мощност до 3.5 dBm

- Хардуерно подпомаган MAC (автоматично потвърждаване, автоматичен повторен опит)

- 32-битов IEEE 802.15.4 брояч на символи

- SFD-откриване, разпространение; Де-разпръскване; Рамкиране ; CRC-16 Изчисление

- Разнообразие на антената и управление на TX/RX / TX/RX 128 байтов буфер на кадри

- PLL синтезатор с 5 MHz и 500 kHz канално разстояние за 2.4 GHz ISM Band

- Хардуерна сигурност (AES, True Random Generator)

- Интегрирани кристални осцилатори (32.768 kHz & 16 MHz, необходим е външен кристал)

- I/O и пакет

- 33 програмируеми I/O линии

- 48-пад QFN (RoHS/напълно зелен)

- Температурен диапазон: -40°C до 125°C Индустриален

- Изключително ниска консумация на енергия (1.8 до 3.6 V) за AVR & Rx/Tx: 10.1 mA/18.6 mA

- Активен режим на процесора (16MHz): 4.1 mA

- 2.4 GHz трансивър: RX_ON 6.0 mA / TX 14.5 mA (максимална изходна мощност на TX)

- Режим на дълбок сън: <700nA при 25°C

- Степен на скорост: 0 – 16 MHz @ 1.8 – 3.6 V обхват с интегриран voltagд регулатори

Приложения

- ZigBee®/ IEEE 802.15.4-2011/2006/2003™ – Устройство с пълна и намалена функция

- Общо предназначение 2.4 GHz ISM честотен трансивър с микроконтролер

- RF4CE, SP100, WirelessHART™, ISM приложения и IPv6 / 6LoWPAN

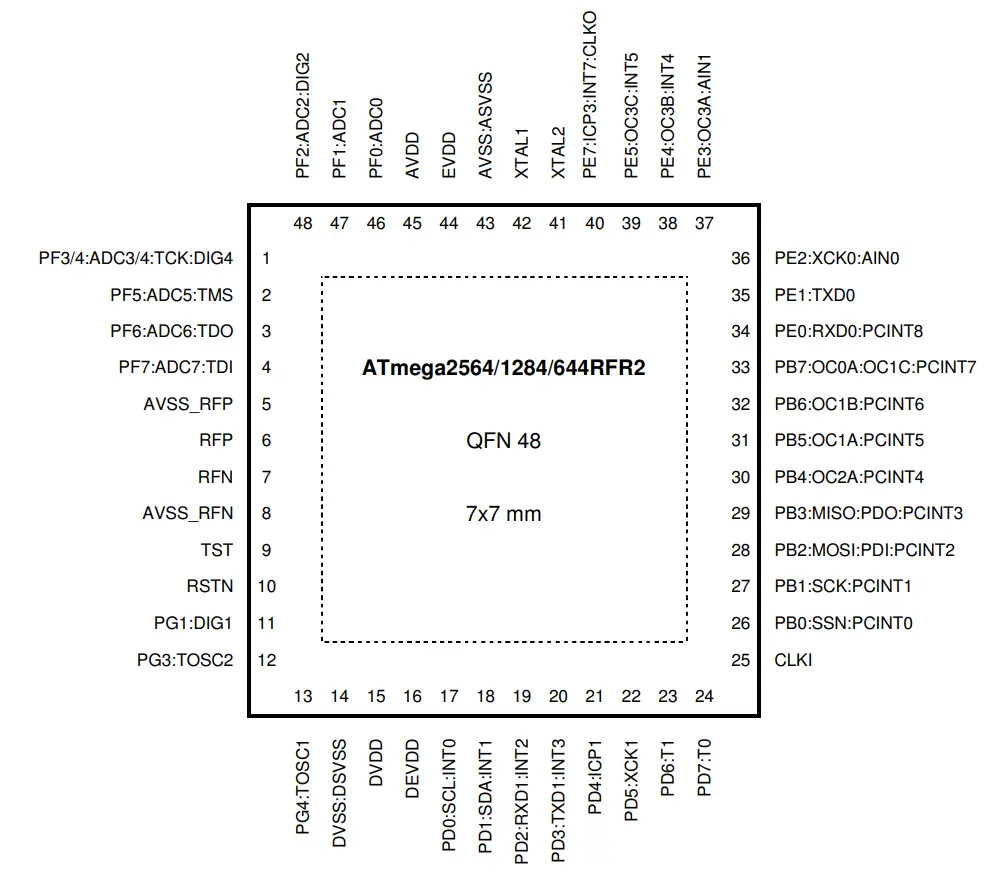

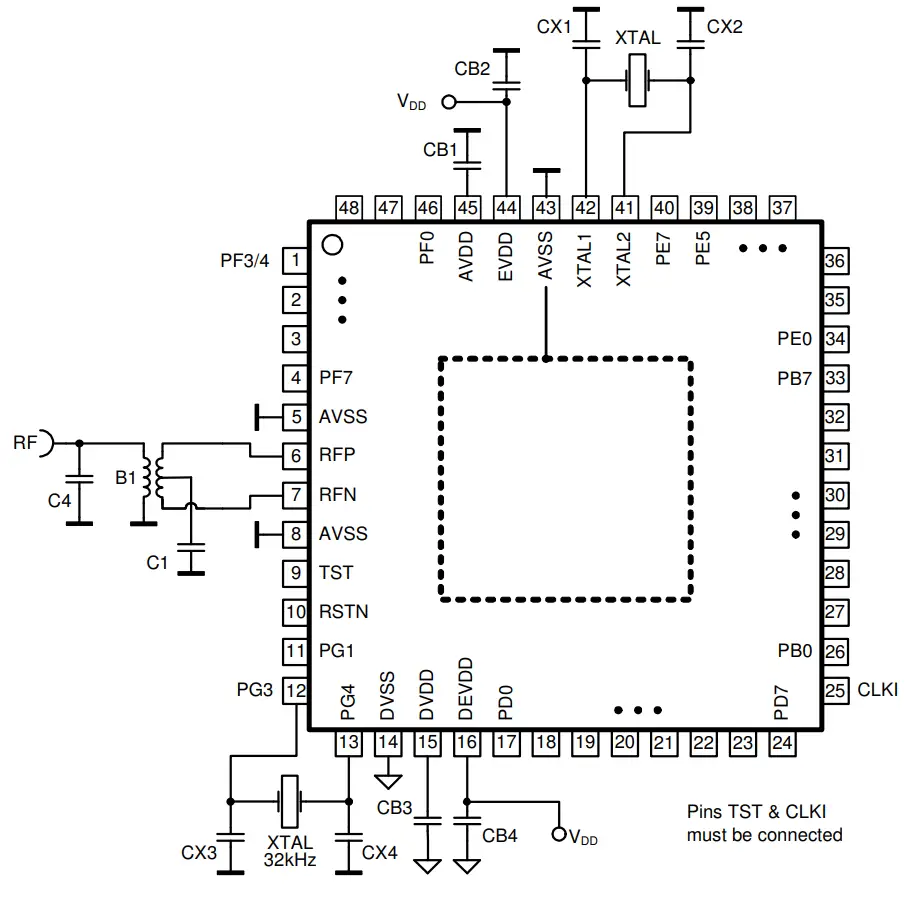

Конфигурации на щифтове

Фигура 1-1. Pinout ATmega2564/1284/644RFR2

Забележка: Голямата централна подложка под пакета QFN/MLF е направена от метал и вътрешно свързана с AVSS. Той трябва да бъде запоен или залепен към платката, за да се осигури добра механична стабилност. Ако централната подложка остане несвързана, пакетът може да се разхлаби от дъската. Не се препоръчва използването на откритата лопатка като заместител на обикновените AVSS щифтове.

Отказ от отговорност

Типичните стойности, съдържащи се в този лист с данни, се основават на резултати от симулация и характеризиране на други AVR микроконтролери и радиопредаватели, произведени по подобна технология на процеса. Минималните и максималните стойности ще бъдат налични след характеризиране на устройството.

крайview

ATmega2564/1284/644RFR2 е CMOS 8-битов микроконтролер с ниска мощност, базиран на подобрената AVR RISC архитектура, комбинирана с трансивър с висока скорост на предаване на данни за 2.4 GHz ISM обхват.

Чрез изпълнение на мощни инструкции в един тактов цикъл, устройството постига пропускателна способност, доближаваща се до 1 MIPS на MHz, което позволява на системния дизайнер да оптимизира консумацията на енергия спрямо скоростта на обработка.

Радио приемопредавателят осигурява високи скорости на данни от 250 kb/s до 2 Mb/s, обработка на кадри, изключителна чувствителност на приемника и висока изходна мощност на предаване, което позволява много стабилна безжична комуникация.

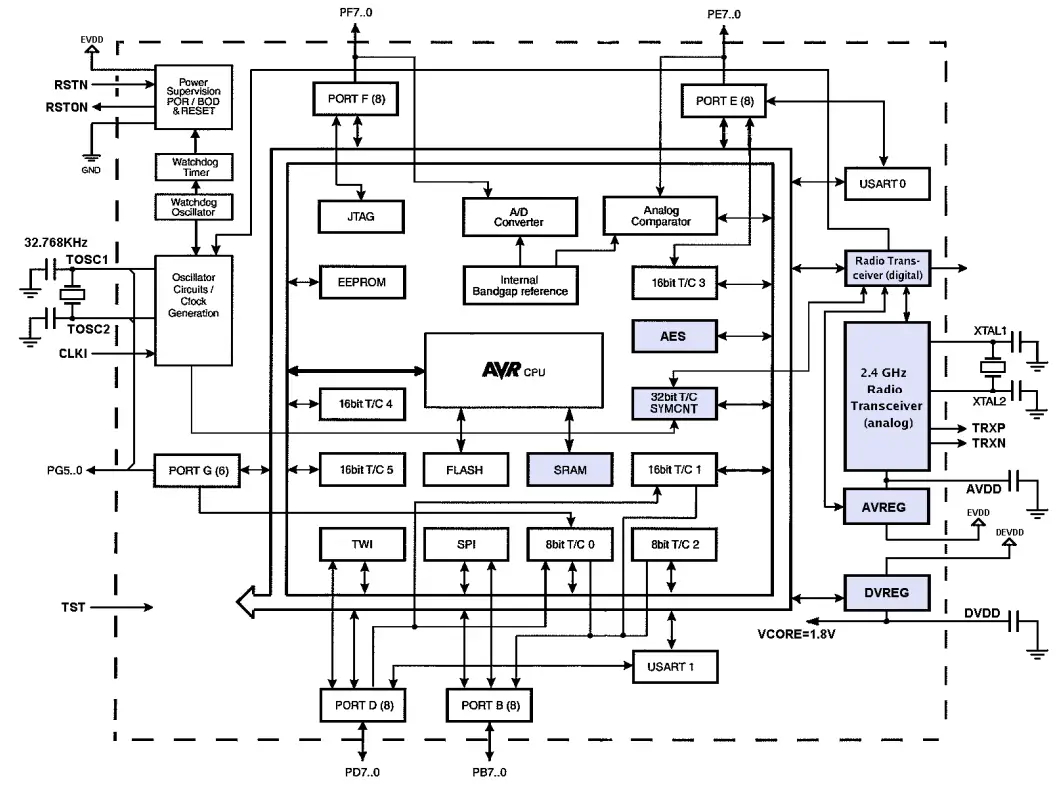

Блок-диаграма

Фигура 3-1 Блокова диаграма

Ядрото на AVR съчетава богат набор от инструкции с 32 работни регистъра с общо предназначение. Всичките 32 регистъра са директно свързани към аритметично-логическата единица (ALU). Два независими регистъра могат да бъдат достъпни с една единствена инструкция, изпълнена в един тактов цикъл. Получената архитектура е много ефективна по отношение на кода, като същевременно постига производителност до десет пъти по-бърза от конвенционалните CISC микроконтролери. Системата включва вътрешни обtage регулиране и разширено управление на мощността. Отличаващ се с малък ток на утечка, той позволява удължено време на работа от батерия.

Радиопредавателят е напълно интегрирано ZigBee решение, използващо минимален брой външни компоненти. Той комбинира отлична RF производителност с ниска цена, малък размер и ниска консумация на ток. Радиопредавателят включва кристално стабилизиран фракционен N синтезатор, предавател и приемник и пълна обработка на директен последователен разширен спектър на сигнала (DSSS) с разпръскване и свиване. Устройството е напълно съвместимо със стандартите IEEE802.15.4-2011/2006/2003 и ZigBee. ATmega2564/1284/644RFR2 предоставя следните характеристики: 256K/128K/64K байта вътрешносистемна програмируема (ISP) флаш памет с възможности за четене и запис, 8K/4K/2K байта EEPROM, 32K/16K/8K байта SRAM, до 35 I/O линии с общо предназначение, 32 работни регистъра с общо предназначение, брояч в реално време (RTC), 6 гъвкави таймер/броячи с режими на сравнение и PWM, 32 битов таймер/брояч, 2 USART, байт ориентиран 2-жилен Сериен интерфейс, 8-канален, 10-битов аналогово-цифров преобразувател (ADC) с опционален диференциален вход stage с програмируемо усилване, програмируем Watchdog Timer с вътрешен осцилатор, SPI сериен порт, IEEE стандарт. 1149.1 съвместим JTAG тестов интерфейс, използван също за достъп до системата за отстраняване на грешки в чипа и програмиране и 6 режима за пестене на енергия, избираеми от софтуера.

Режимът на неактивност спира процесора, като същевременно позволява на SRAM, таймера/броячите, SPI порта и системата за прекъсване да продължат да функционират. Режимът на изключване запазва съдържанието на регистъра, но замразява осцилатора, дезактивирайки всички други функции на чипа до следващото прекъсване или хардуерно нулиране. В режим на пестене на енергия асинхронният таймер продължава да работи, позволявайки на потребителя да поддържа базата на таймера, докато останалата част от устройството спи. Режимът за намаляване на шума на ADC спира процесора и всички I/O модули, с изключение на асинхронния таймер и ADC, за да минимизира шума при превключване по време на преобразуване на ADC. В режим на готовност RC осцилаторът работи, докато останалата част от устройството спи. Това позволява много бързо стартиране в комбинация с ниска консумация на енергия. В режим на разширен режим на готовност главният RC осцилатор и асинхронният таймер продължават да работят.

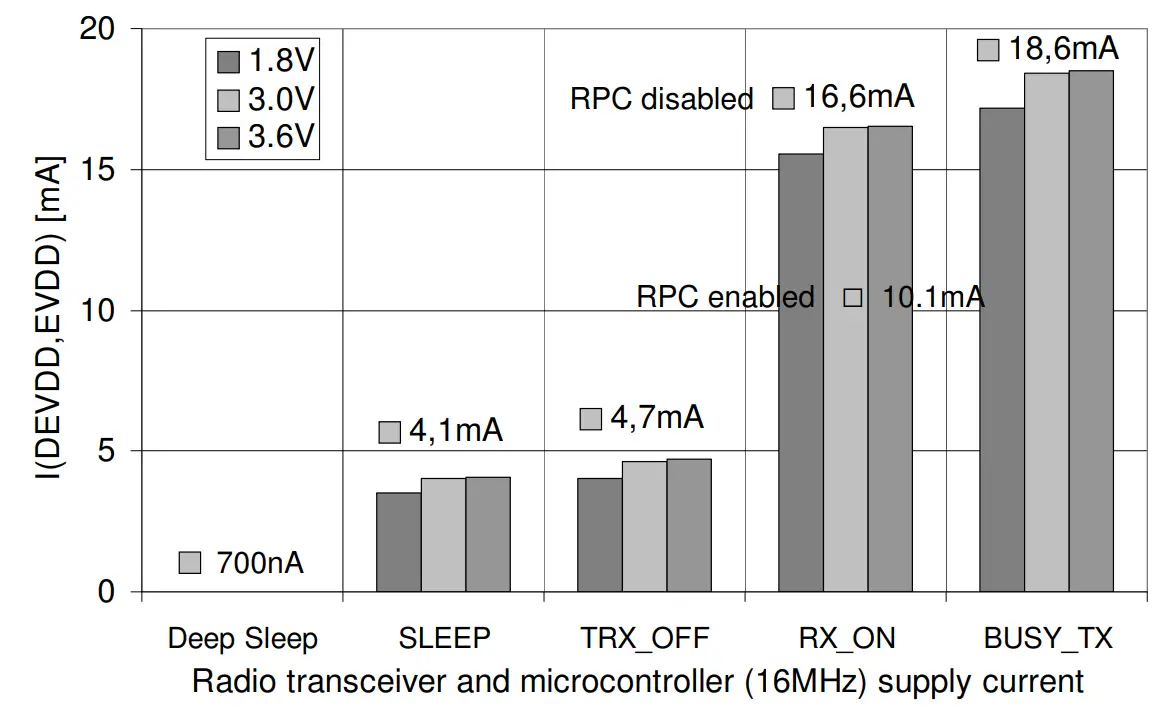

Типичният захранващ ток на микроконтролера с тактова честота на процесора, настроен на 16MHz, и радиопредавателя за най-важните състояния е показан на фигура 3-2 по-долу.

Фигура 3-2 Радио приемопредавател и микроконтролер (16MHz) захранващ ток

Изходната мощност на предаване е зададена на максимум. Ако радиопредавателят е в режим SLEEP, токът се разсейва само от AVR микроконтролера.

В режим Deep Sleep всички основни цифрови блокове без изисквания за запазване на данни са изключени от основното захранване, осигурявайки много малък ток на утечка. Таймерът за наблюдение, броячът на MAC символи и 32.768kHz осцилатор могат да бъдат конфигурирани да продължат да работят.

Устройството е произведено с помощта на технологията за енергонезависима памет с висока плътност на Atmel.

Вградената в чипа ISP Flash позволява програмната памет да бъде препрограмирана в системата чрез SPI сериен интерфейс, от конвенционален програмист за енергонезависима памет или от програма за зареждане на чип, работеща на ядрото на AVR. Програмата за зареждане може да използва всеки интерфейс, за да изтегли приложната програма във флаш паметта на приложението.

Софтуерът в секцията Flash за зареждане ще продължи да работи, докато секцията Flash на приложението се актуализира, осигурявайки истинска операция за четене-докато-запис. Чрез комбиниране на 8-битов RISC CPU с вътрешносистемна самопрограмируема Flash на монолитен чип, Atmel ATmega2564/1284/644RFR2 е мощен микроконтролер, който осигурява много гъвкаво и рентабилно решение за много приложения за вграден контрол.

ATmega2564/1284/644RFR2 AVR се поддържа с пълен набор от инструменти за разработка на програми и системи, включително: C компилатор, асемблери на макроси, програма за отстраняване на грешки/симулатори, вътрешносхемни емулатори и комплекти за оценка.

Описания на пинове

EVDD

Външно аналогово захранване обtage.

DEVDD

Външно цифрово захранване обtage.

AVDD

Регулирано аналогово захранване обtage (вътрешно генериран).

DVD

Регулирани цифрови доставки обtage (вътрешно генериран).

DVSS

Цифрова земя.

AVSS

Аналогова земя.

Порт B (PB7…PB0)

Порт B е 8-битов двупосочен I/O порт с вътрешни издърпващи резистори (избрани за всеки бит). Изходните буфери на порт B имат симетрични характеристики на задвижване с висока способност както за приемник, така и за източник. Като входове, щифтовете на порт B, които са външно изтеглени ниско, ще генерират ток, ако издърпващите резистори са активирани. Изводите на порт B са в три състояния, когато условието за нулиране стане активно, дори ако часовникът не работи.

Порт B също предоставя функции на различни специални характеристики на ATmega2564/1284/644RFR2.

Порт D (PD7…PD0)

Порт D е 8-битов двупосочен I/O порт с вътрешни издърпващи резистори (избрани за всеки бит). Изходните буфери на порт D имат симетрични характеристики на задвижване с висока способност за поглъщане и източник. Като входове, щифтовете на порт D, които са външно изтеглени ниско, ще генерират ток, ако издърпващите резистори са активирани. Изводите на порт D са в три състояния, когато условието за нулиране стане активно, дори ако часовникът не работи.

Порт D също предоставя функции на различни специални функции на ATmega2564/1284/644RFR2.

Порт E (PE7,PE5…PE0)

Вътрешно порт E е 8-битов двупосочен I/O порт с вътрешни издърпващи резистори (избрани за всеки бит). Изходните буфери на порт E имат симетрични характеристики на задвижване с висока способност за поглъщане и източник. Като входове, щифтовете на порт E, които са външно изтеглени ниско, ще генерират ток, ако издърпващите резистори са активирани. Щифтовете на порт E са в три състояния, когато условието за нулиране стане активно, дори ако часовникът не работи.

Поради ниския брой щифтове на пакета QFN48 порт E6 не е свързан с щифт. Порт E също така предоставя функции на различни специални характеристики на ATmega2564/1284/644RFR2.

Port F (PF7..PF5,PF4/3,PF2…PF0)

Вътрешно порт F е 8-битов двупосочен I/O порт с вътрешни издърпващи резистори (избрани за всеки бит). Изходните буфери на порт F имат симетрични характеристики на задвижване с висока способност както за приемник, така и за източник. Като входове, щифтовете на порт F, които са външно изтеглени ниско, ще генерират ток, ако издърпващите резистори са активирани. Щифтовете на порт F са в три състояния, когато условието за нулиране стане активно, дори ако часовникът не работи.

Поради ниския брой щифтове на пакета QFN48, портовете F3 и F4 са свързани към един и същи щифт. I/O конфигурацията трябва да се извърши внимателно, за да се избегне прекомерно разсейване на мощността.

Порт F също предоставя функции на различни специални характеристики на ATmega2564/1284/644RFR2.

Порт G (PG4,PG3,PG1)

Вътрешно порт G е 6-битов двупосочен I/O порт с вътрешни издърпващи резистори (избрани за всеки бит). Изходните буфери на порт G имат симетрични характеристики на задвижване с висока способност за поглъщане и източник. Силата на драйвера на PG3 и PG4 обаче е намалена в сравнение с другите щифтове на порта. Изходният обtagСпадът (VOH, VOL) е по-висок, докато токът на утечка е по-малък. Като входове, щифтовете на порт G, които са външно изтеглени ниско, ще генерират ток, ако издърпващите резистори са активирани. Щифтовете на порт G са в три състояния, когато условието за нулиране стане активно, дори ако часовникът не работи.

Поради ниския брой щифтове на пакета QFN48 портът G0, G2 и G5 не са свързани с щифт.

Порт G също предоставя функции на различни специални характеристики на ATmega2564/1284/644RFR2.

AVSS_RFP

AVSS_RFP е специален заземен щифт за двупосочния, диференциален RF I/O порт.

AVSS_RFN

AVSS_RFN е специален заземен щифт за двупосочния, диференциален RF I/O порт.

RFP

RFP е положителният терминал за двупосочния, диференциален RF I/O порт.

RFN

RFN е отрицателният извод за двупосочния, диференциален RF I/O порт.

RSTN

Нулиране на входа. Ниско ниво на този щифт за по-дълго от минималната дължина на импулса ще генерира нулиране, дори ако часовникът не работи. Не е гарантирано, че по-кратките импулси ще генерират нулиране.

XTAL1

Вход към инвертиращия 16MHz кристален осцилатор ampлифиер. Като цяло кристал между XTAL1 и XTAL2 осигурява 16MHz референтна честота на радио приемопредавателя.

XTAL2

Изход на инвертиращия 16MHz кристален осцилатор ampлифир.

TST

Пин за активиране на режим на програмиране и тестване. Ако щифтът TST не се използва, дръпнете го на ниско ниво.

CLKI

Вход към часовниковата система. Ако е избрано, то осигурява работния часовник на микроконтролера.

Неизползвани щифтове

Плаващите щифтове могат да причинят разсейване на мощността в цифровите входовеtagд. Те трябва да бъдат свързани към подходящ източник. В нормални режими на работа вътрешните подтягащи резистори могат да бъдат активирани (при Нулиране всички GPIO са конфигурирани като вход и подтягащите резистори все още не са активирани).

Двупосочните входно/изходни щифтове не трябва да се свързват директно към заземяване или захранване.

Цифровите входни щифтове TST и CLKI трябва да бъдат свързани. Ако неизползваният щифт TST може да бъде свързан към AVSS, докато CLKI трябва да бъде свързан към DVSS.

Изходните щифтове се задвижват от устройството и не плават. Щифтовете за захранване, съответните щифтове за заземяване, са свързани вътрешно.

XTAL1 и XTAL2 никога няма да бъдат принуждавани да доставят voltage в същото време.

Съвместимост и ограничения на функциите на пакета QFN-48

AREF

Референтният томtagИзходът на A/D преобразувателя не е свързан към щифт в ATmega2564/1284/644RFR2.

Порт E6

Порт E6 не е свързан към щифт в ATmega2564/1284/644RFR2. Функциите на алтернативния щифт като тактов вход към таймер 3 и външно прекъсване 6 не са налични.

Порт F3 и F4

Портовете F3 и F4 са свързани към един и същи щифт в ATmega2564/1284/644RFR2. Конфигурирането на изхода трябва да се извърши внимателно, за да се избегне прекомерна консумация на ток.

Алтернативната функция на щифта на порт F4 се използва от JTAG интерфейс. Ако ДжTAG използва се интерфейс, портът F3 трябва да бъде конфигуриран като вход и изходът за алтернативна пин функция DIG4 (индикатор RX/TX) трябва да бъде деактивиран. Иначе ДжTAG интерфейсът няма да работи. SPIEN Fuse трябва да бъде програмиран, за да може да изтрие програма, която случайно управлява порт F3.

Налични са само 7 входни канала с единичен край към ADC.

Порт G0

Портът G0 не е свързан към щифт в ATmega2564/1284/644RFR2. Алтернативната функция на щифта DIG3 (инвертиран RX/TX индикатор) не е налична. Ако ДжTAG интерфейсът не се използва, изходът на алтернативната пин функция DIG4 на порт F3 все още може да се използва като RX/TX индикатор.

Порт G2

Портът G2 не е свързан към щифт в ATmega2564/1284/644RFR2. Алтернативната пин функция AMR (асинхронно автоматизирано въвеждане на отчитане на измервателен уред към таймер 2) не е налична.

Порт G5

Портът G5 не е свързан към щифт в ATmega2564/1284/644RFR2. Алтернативната пин функция OC0B (изходен канал за сравнение на 8-битов таймер 0) не е налична.

RSTON

Изходът за нулиране RSTON, сигнализиращ вътрешното състояние на нулиране, не е свързан към щифт в ATmega2564/1284/644RFR2.

Резюме на конфигурацията

Според изискванията на приложението променливият размер на паметта позволява да се оптимизира потреблението на ток и тока на утечка.

Таблица 3-1 Конфигурация на паметта

| устройство | Светкавица | EEPROM | SRAM |

| ATmega2564RFR2 | 256KB | 8KB | 32KB |

| ATmega1284RFR2 | 128KB | 4KB | 16KB |

| ATmega644RFR2 | 64KB | 2KB | 8KB |

Пакетът и свързаната конфигурация на щифта са еднакви за всички устройства, осигуряващи пълна функционалност на приложението.

Таблица 3-2 Системна конфигурация

| устройство | Пакет | GPIO | Сериен IF | ADC канал |

| ATmega2564RFR2 | QFN48 | 33 | 2 USART, SPI, TWI | 7 |

| ATmega1284RFR2 | QFN48 | 33 | 2 USART, SPI, TWI | 7 |

| ATmega644RFR2 | QFN48 | 33 | 2 USART, SPI, TWI | 7 |

Устройствата са оптимизирани за приложения, базирани на ZigBee и спецификацията IEEE 802.15.4. Наличието на стек от приложения, мрежов слой, сензорен интерфейс и отличен контрол на мощността, комбинирани в един чип, трябва да е възможно много години работа.

Таблица 3-3 Application Profile

| устройство | Приложение |

| ATmega2564RFR2 | Голям мрежов координатор / рутер за IEEE 802.15.4 / ZigBee Pro |

| ATmega1284RFR2 | Мрежов координатор/рутер за IEEE 802.15.4 |

| ATmega644RFR2 | Устройство на крайния възел / мрежов процесор |

Приложни вериги

Основна схема на приложение

Основна схема на приложение на ATmega2564/1284/644RFR2 с еднопосочен RF конектор е показана на Фигура 4-1 по-долу и свързаната спецификация на материалите в Таблица 4-1 на страница 10. 50Ω еднопосочен RF вход се трансформира към импеданса на диференциалния RF порт от 100Ω с помощта на Balun B1. Кондензаторите C1 и C2 осигуряват AC свързване на RF входа към RF порта, кондензатор C4 подобрява съвпадението.

Фигура 4-1. Основна схема на приложение (48-пинов пакет)

Байпасните кондензатори на захранването (CB2, CB4) са свързани към външния аналогов захранващ щифт (EVDD, щифт 44) и външен цифров щифт за захранване (DEVDD, щифт 16). Кондензаторът C1 осигурява необходимото AC свързване на RFN/RFP.

Плаващите щифтове могат да причинят прекомерно разсейване на мощност (напр. по време на включване). Те трябва да бъдат свързани към подходящ източник. GPIO не трябва да се свързва директно със заземяване или захранване.

Цифровите входни щифтове TST и CLKI трябва да бъдат свързани. Ако щифтът TST никога няма да бъде използван, той може да бъде свързан към AVSS, докато неизползван щифт CLKI може да бъде свързан към DVSS (вижте глава „Неизползвани щифтове“).

Кондензаторите CB1 и CB3 са байпасни кондензатори за интегрирания аналогов и цифров обемtage регулатори за осигуряване на стабилна работа и за подобряване на устойчивостта на шум.

Кондензаторите трябва да се поставят възможно най-близо до щифтовете и трябва да имат връзка с ниско съпротивление и ниска индуктивност към земята, за да се постигне най-добра производителност.

Кристалът (XTAL), двата товарни кондензатора (CX1, CX2) и вътрешната верига, свързана към изводите XTAL1 и XTAL2, образуват 16MHz кристален осцилатор за 2.4GHz трансивър. За да се постигне най-добра точност и стабилност на референтната честота, трябва да се избягват големи паразитни капацитети. Кристалните линии трябва да се насочват възможно най-късо и да не са в близост до цифрови I/O сигнали. Това е особено необходимо за режимите с висока скорост на данни.

Кристалът от 32.768 kHz, свързан към вътрешния кристален осцилатор с ниска мощност (под 1µA), осигурява стабилна времева референтна стойност за всички режими на ниска мощност, включително 32-битов IEEE 802.15.4 брояч на символи („MAC символен брояч“) и приложение за часовник в реално време, използващо асинхронния таймер T/C2 („Таймер/брояч2 с ШИМ и асинхронна работа“).

Общият капацитет на шунт, включително CX3, CX4, не трябва да надвишава 15pF на двата извода.

Много ниският захранващ ток на осцилатора изисква внимателно оформление на печатната платка и всякакъв път на изтичане трябва да се избягва.

Смущаване и излъчване от превключване на цифрови сигнали към кристалните щифтове или RF щифтовете могат да влошат производителността на системата. Препоръчва се програмирането на настройките за минимална сила на задвижване за цифровия изходен сигнал (вижте „DPDS0 – Регистър на силата на драйвера на порт 0“).

Таблица 4-1. Списък на материалите (BoM)

| Обозначител | Описание | Стойност | производител | Номер на част | Коментирайте |

| B1 | SMD балун

SMD балун / филтър |

2.4 GHz | Wuerth Johanson Technology | 748421245

2450FB15L0001 |

Включен филтър |

| CB1 CB3 | LDO VREG

байпас кондензатор |

1 mF (100nF минимум) | AVX

Мурата |

0603YD105KAT2A GRM188R61C105KA12D | X5R (0603) 10% 16V |

| CB2 CB4 | Захранващ байпасен кондензатор | 1 mF (100nF минимум) | |||

| CX1, CX2 | 16MHz кристален кондензатор за натоварване | 12 pF | AVX

Мурата |

06035A120JA GRP1886C1H120JA01 | COG (0603) 5% 50V |

| CX3, CX4 | 32.768kHz кристален кондензатор за натоварване | 12 … 25 pF | |||

| C1, C2 | RF свързващ кондензатор | 22 pF | Epcos Epcos AVX | B37930 B37920

06035A220JAT2A |

C0G 5% 50V (0402 или 0603) |

| C4 (по избор) | RF съвпадение | 0.47 pF | Джонстех | ||

| XTAL | Кристал | CX-4025 16 MHz

SX-4025 16 MHz |

ACAL Taitjen Siward | XWBBPL-F-1 A207-011 | |

| XTAL 32kHz | Кристал | Rs=100 kOhm |

История на ревизиите

Моля, имайте предвид, че номерата на препращащите страници в този раздел се отнасят за този документ. Референтната редакция в този раздел се отнася за ревизията на документа.

Rev. 42073BS-MCU Wireless-09/14

- Съдържанието непроменено – пресъздадено за комбинирано издание с листа с данни.

Rev. 8393AS-MCU Wireless-02/13

- Първоначално издание.

© 2014 Atmel Corporation. Всички права запазени. / Рев.: 42073BS-MCU Wireless-09/14 Atmel®, логото на Atmel и комбинациите от тях, Enabling Unlimited Possibilities® и други са регистрирани търговски марки или търговски марки на Atmel Corporation или нейните филиали. Други термини и имена на продукти може да са търговски марки на други.

Отказ от отговорност: Информацията в този документ е предоставена във връзка с продуктите на Atmel. Този документ или във връзка с продажбата на продуктите на Atmel не предоставя никакъв лиценз, изричен или подразбиращ се, чрез изключване или по друг начин, за право на интелектуална собственост. ОСВЕН КАКВОТО Е ПОСОЧЕНО В ПРАВИЛАТА И УСЛОВИЯТА ЗА ПРОДАЖБА НА ATMEL, РАЗПОЛОЖЕНИ В ATMEL WEBСАЙТ, ATMEL НЕ ПОЕМА НИКАКВА ОТГОВОРНОСТ И СЕ ОТХВЪРЛЯ ИЗРИЧНА, КОСВЕНА ИЛИ ЗАКОНОВА ГАРАНЦИЯ, СВЪРЗАНА С НЕГОВИТЕ ПРОДУКТИ, ВКЛЮЧИТЕЛНО, НО НЕ САМО, КОСВЕНАТА ГАРАНЦИЯ ЗА ПРОДАВАЕМОСТ, ГОДНОСТ ЗА ОПРЕДЕЛЕНА ЦЕЛ ИЛИ НЕНАРУШЕНИЕ. В НИКАКЪВ СЛУЧАЙ ATMEL НЕ НОСИ ОТГОВОРНОСТ ЗА ПРЯКИ, НЕПРЯКИ, ПОСЛЕДВАЩИ, НАКАЗАТЕЛНИ, СПЕЦИАЛНИ ИЛИ СЛУЧАЙНИ ЩЕТИ (ВКЛЮЧИТЕЛНО, БЕЗ ОГРАНИЧЕНИЕ, ЩЕТИ ЗА ЗАГУБИ И ПЕЧАЛБИ, ПРЕКЪСВАНЕ НА БИЗНЕС ИЛИ ЗАГУБА НА ИНФОРМАЦИЯ), ПРОИЗТИЧАЩИ ОТ ИЗПОЛЗВАНЕТО ИЛИ НЕВЪЗМОЖНОСТТА ТОЗИ ДОКУМЕНТ, ДОРИ И АКО ATMEL Е БИЛ УВЕДОМЛЕН ЗА ВЪЗМОЖНОСТТА ЗА ТАКИВА ЩЕТИ. Atmel не дава никакви декларации или гаранции по отношение на точността или пълнотата на съдържанието на този документ и си запазва правото да прави промени в спецификациите и описанията на продуктите по всяко време без предизвестие. Atmel не поема никакъв ангажимент да актуализира информацията, съдържаща се тук. Освен ако изрично не е предвидено друго, продуктите на Atmel не са подходящи и не трябва да се използват в автомобилни приложения. Продуктите на Atmel не са предназначени, разрешени или гарантирани за употреба като компоненти в приложения, предназначени да поддържат или поддържат живота.

Mouser Electronics

Оторизиран дистрибутор

Кликнете, за да View Информация за цените, инвентара, доставката и жизнения цикъл:

ATMEGA644RFR2-ZU

ATMEGA2564RFR2-ZF

ATMEGA644RFR2-ZF

ATMEGA644RFR2-ZUR

ATMEGA1284RFR2-ZU

ATMEGA2564RFR2-ZFR

ATMEGA1284RFR2-ZFR

ATMEGA1284RFR2-ZUR

ATMEGA644RFR2-ZFR

ATMEGA2564RFR2-ZU

ATMEGA1284RFR2-ZF

ATMEGA2564RFR2-ZUR

Поддръжка на клиенти

Atmel Corporation

1600 технологично задвижване

Сан Хосе, Калифорния 95110

САЩ

тел.: (+1)408-441-0311

Факс: (+1)408-487-2600

www.atmel.com

Документи / Ресурси

|

Atmel ATmega2564 8bit AVR микроконтролер [pdf] Ръководство за употреба ATmega2564RFR2, ATmega1284RFR2, ATmega644RFR2, ATmega2564 8-битов AVR микроконтролер, ATmega2564, 8-битов AVR микроконтролер, AVR микроконтролер, Микроконтролер |