Microcontrolador AVR Atmel ATmega2564 de 8 bits

Características

- Soporte de red mediante filtrado de direcciones PAN múltiples asistido por hardware

- Hardware avanzado asistido Consumo de energía reducido

- Microcontrolador AVR® de 8 bits de alto rendimiento y bajo consumo

- Arquitectura RISC avanzada

- 135 poderosas instrucciones: la mayoría de las ejecuciones de ciclo de reloj único

- Registros de trabajo de uso general de 32×8/multiplicador de 2 ciclos en chip

- Rendimiento de hasta 16 MIPS a 16 MHz y 1.8 V: funcionamiento totalmente estático

- Memorias de datos y programas no volátiles

- 256 K/128 K/64 K bytes de flash autoprogramable en el sistema

- Resistencia: 10 ciclos de escritura/borrado a 000 °C (125 ciclos a 25 °C)

- EEPROM de 8K/4K/2Kbytes

- Resistencia: 20 ciclos de escritura/borrado a 000 °C (125 ciclos a 100 °C)

- SRAM interna de 32K/16K/8Kbytes

- JTAG (Cumple con el estándar IEEE 1149.1) Interfaz

- Capacidades de exploración de límites según la JTAG Estándar

- Amplio soporte de depuración en chip

- Programación de Flash EEPROM, Fusibles y Bits de Bloqueo a través del JTAG interfaz

- Funciones periféricas

- Múltiples canales de temporizador/contador y PWM

- Contador en tiempo real con oscilador separado

- Convertidor A/D de 10 bits, 330 ks/s; Comparador analógico; Sensor de temperatura en chip

- Interfaz serie SPI maestro/esclavo

- Dos USART seriales programables

- Interfaz serie de 2 hilos orientada a bytes

- Manejador de interrupciones avanzado y modos de ahorro de energía

- Temporizador de vigilancia con oscilador independiente en chip

- Reinicio de encendido y detector de caída de tensión de baja corriente

- Transceptor de baja potencia totalmente integrado para banda ISM de 2.4 GHz

- Energía alta AmpSoporte de lificador mediante supresión de lóbulos laterales del espectro TX.

- Velocidades de datos admitidas: 250 kb/s y 500 kb/s, 1 Mb/s, 2 Mb/s

- -100 dBm Sensibilidad RX; Potencia de salida TX de hasta 3.5 dBm

- MAC asistida por hardware (reconocimiento automático, reintento automático)

- Contador de símbolos IEEE 32 de 802.15.4 bits

- SFD-Detección, Difusión; De-propagación; encuadre; Computación CRC-16

- Diversidad de antena y control TX/RX / TX/RX 128 Byte Frame Buffer

- Sintetizador PLL con espaciado de canales de 5 MHz y 500 kHz para banda ISM de 2.4 GHz

- Seguridad de hardware (AES, verdadero generador aleatorio)

- Osciladores de cristal integrados (32.768 kHz y 16 MHz, se necesita cristal externo)

- E/S y paquete

- 33 líneas de E/S programables

- QFN de 48 pads (RoHS/completamente verde)

- Rango de temperatura: -40°C a 125°C Industrial

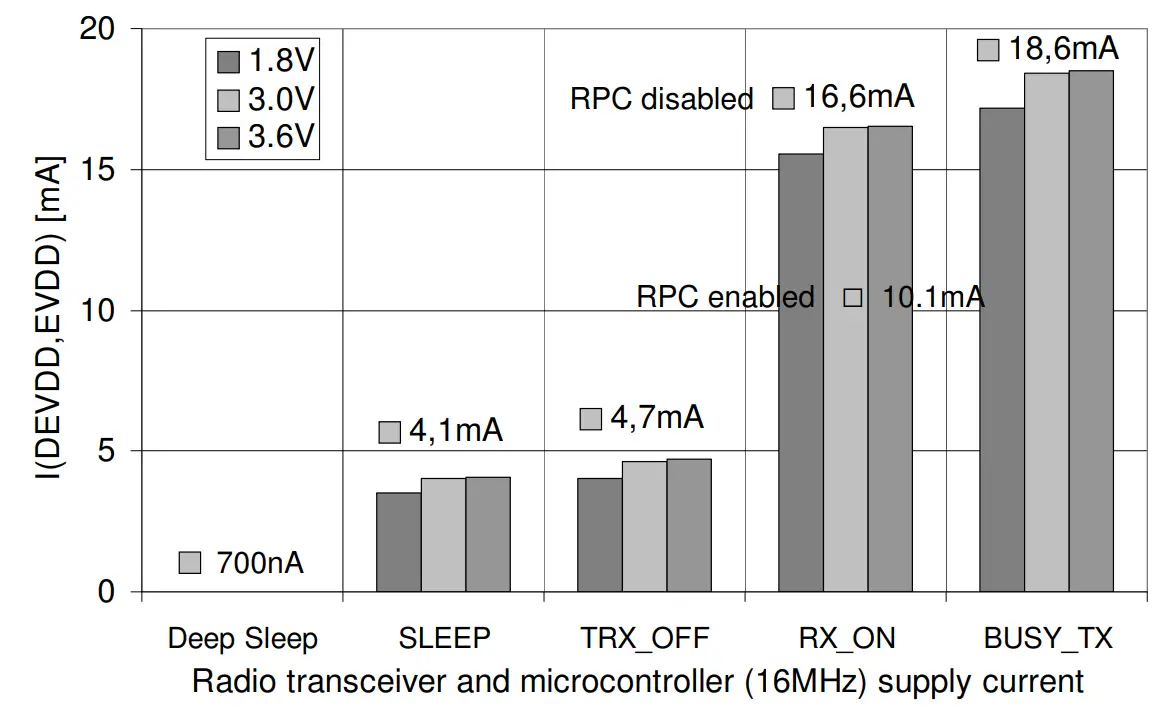

- Consumo de energía ultrabajo (1.8 a 3.6 V) para AVR y Rx/Tx: 10.1 mA/18.6 mA

- Modo activo de CPU (16 MHz): 4.1 mA

- Transceptor de 2.4 GHz: RX_ON 6.0 mA / TX 14.5 mA (potencia máxima de salida TX)

- Modo de suspensión profunda: <700 nA a 25 °C

- Grado de velocidad: 0 – 16 MHz @ rango de 1.8 – 3.6 V con vol integradotage reguladores

Aplicaciones

- ZigBee®/ IEEE 802.15.4-2011/2006/2003™ – Dispositivo de función completa y reducida

- Transceptor de banda ISM de 2.4 GHz de uso general con microcontrolador

- RF4CE, SP100, WirelessHART™, aplicaciones ISM e IPv6/6LoWPAN

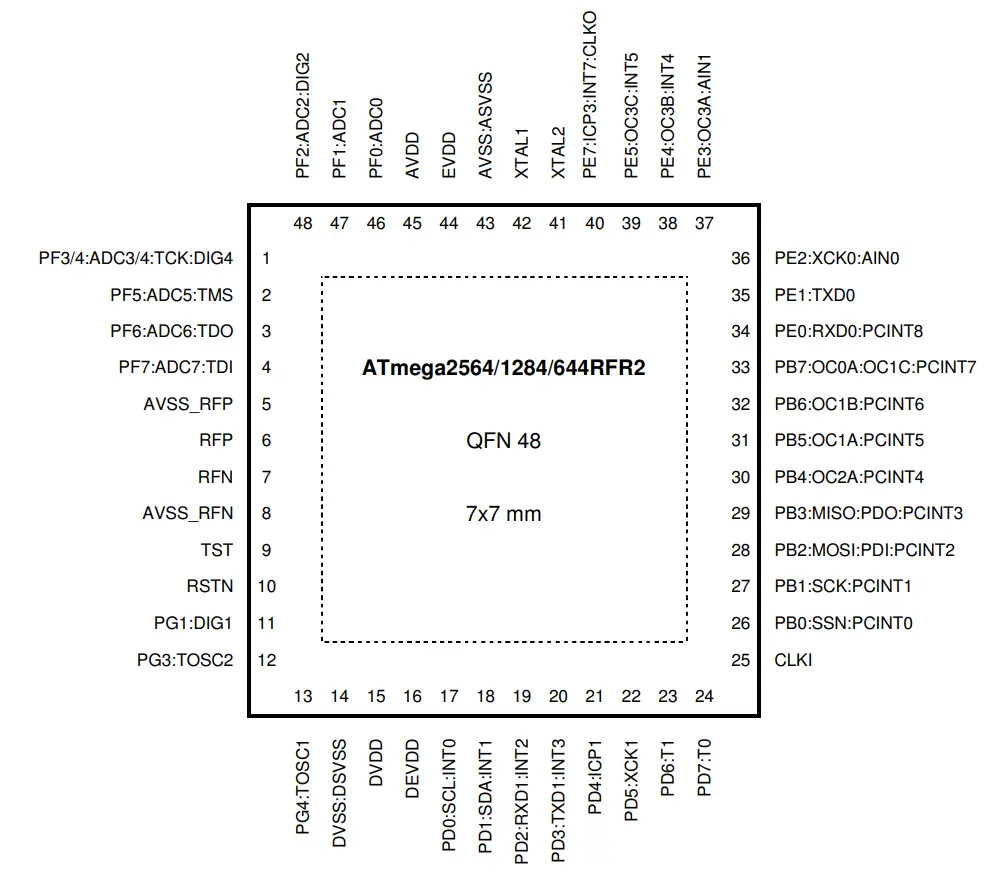

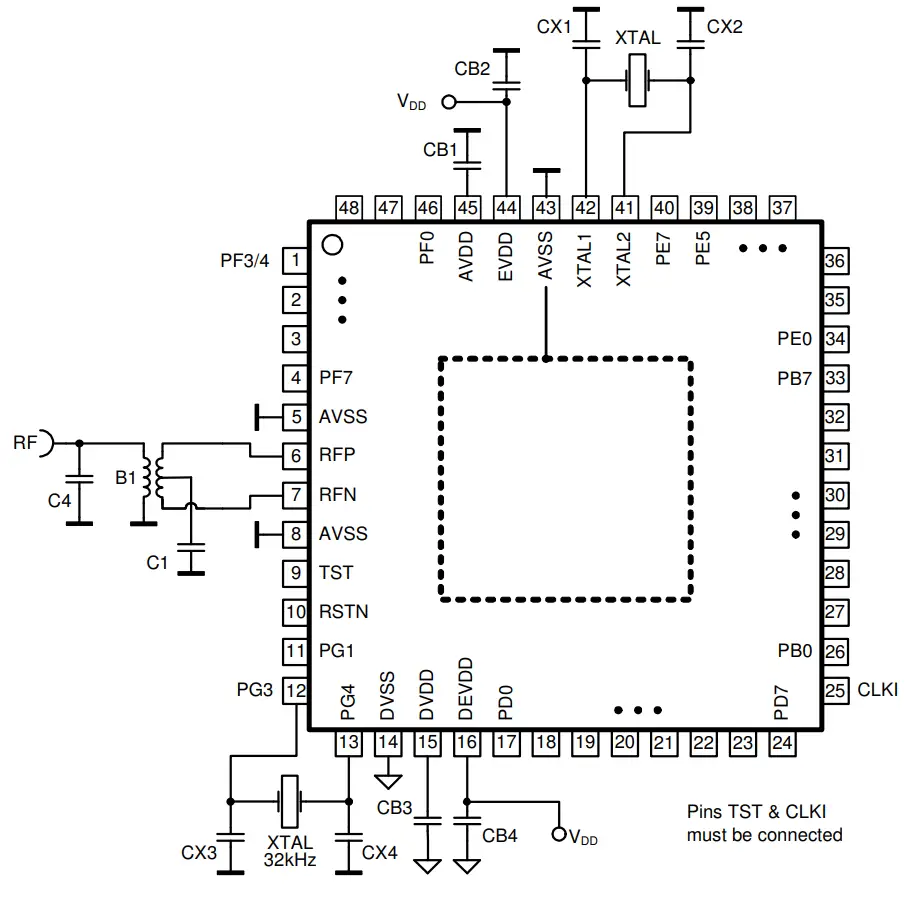

Configuraciones de pines

Figura 1-1. Configuración de pines ATmega2564/1284/644RFR2

Nota: La gran almohadilla central debajo del paquete QFN/MLF está hecha de metal y conectada internamente a AVSS. Debe soldarse o pegarse a la placa para garantizar una buena estabilidad mecánica. Si la almohadilla central se deja desconectada, el paquete podría soltarse del tablero. No se recomienda utilizar la paleta expuesta como reemplazo de los pasadores AVSS normales.

Descargo de responsabilidad

Los valores típicos contenidos en esta hoja de datos se basan en resultados de simulación y caracterización de otros microcontroladores AVR y transceptores de radio fabricados con una tecnología de proceso similar. Los valores mínimo y máximo estarán disponibles después de caracterizar el dispositivo.

Encimaview

El ATmega2564/1284/644RFR2 es un microcontrolador CMOS de 8 bits de bajo consumo basado en la arquitectura RISC mejorada de AVR combinada con un transceptor de alta velocidad de datos para la banda ISM de 2.4 GHz.

Al ejecutar potentes instrucciones en un solo ciclo de reloj, el dispositivo logra rendimientos cercanos a 1 MIPS por MHz, lo que permite al diseñador del sistema optimizar el consumo de energía frente a la velocidad de procesamiento.

El transceptor de radio proporciona altas velocidades de datos desde 250 kb/s hasta 2 Mb/s, manejo de tramas, excelente sensibilidad del receptor y alta potencia de salida de transmisión, lo que permite una comunicación inalámbrica muy sólida.

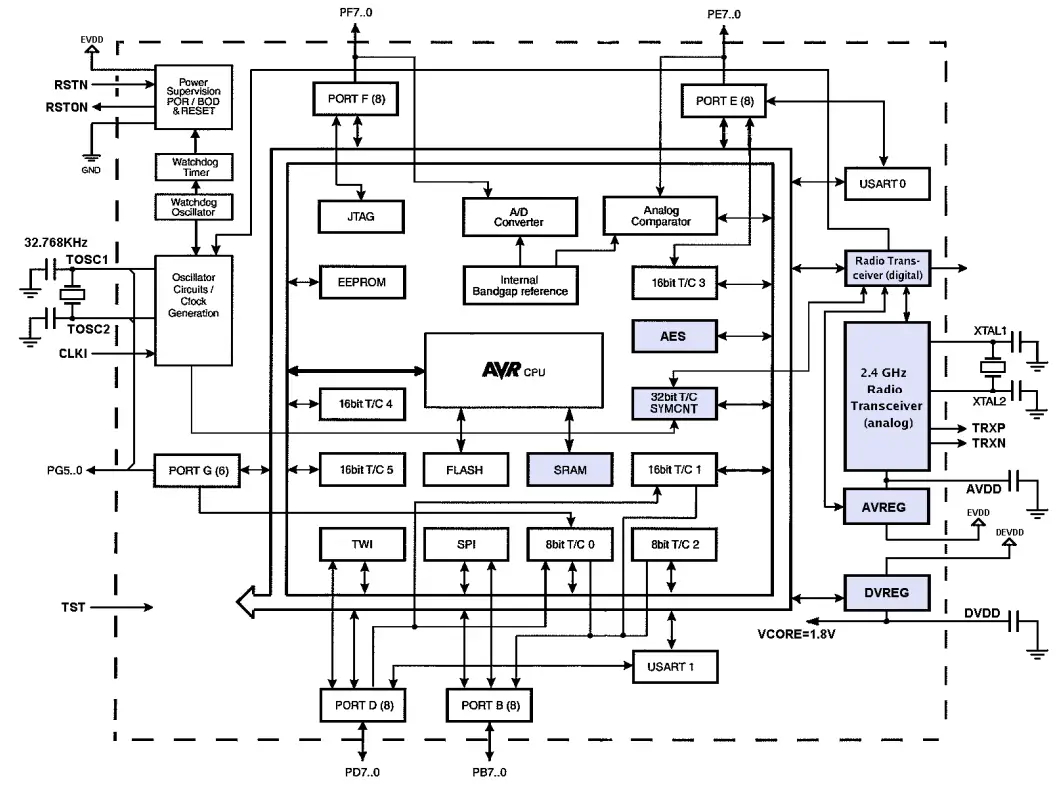

Diagrama de bloques

Figura 3-1 Diagrama de bloques

El núcleo AVR combina un rico conjunto de instrucciones con 32 registros de trabajo de propósito general. Los 32 registros están conectados directamente a la Unidad Lógica Aritmética (ALU). Se puede acceder a dos registros independientes con una sola instrucción ejecutada en un ciclo de reloj. La arquitectura resultante es muy eficiente en cuanto a código y logra rendimientos hasta diez veces más rápidos que los microcontroladores CISC convencionales. El sistema incluye vol internotagRegulación electrónica y gestión avanzada de la energía. Se distingue por la pequeña corriente de fuga y permite un mayor tiempo de funcionamiento con batería.

El transceptor de radio es una solución ZigBee totalmente integrada que utiliza un número mínimo de componentes externos. Combina un excelente rendimiento de RF con bajo costo, tamaño pequeño y bajo consumo de corriente. El transceptor de radio incluye un sintetizador, transmisor y receptor de N fraccional estabilizado con cristal, y procesamiento completo de señal de espectro ensanchado de secuencia directa (DSSS) con ensanchamiento y desensanchamiento. El dispositivo es totalmente compatible con los estándares IEEE802.15.4-2011/2006/2003 y ZigBee. El ATmega2564/1284/644RFR2 proporciona las siguientes características: 256K/128K/64K Bytes de Flash programable en el sistema (ISP) con capacidades de lectura mientras escribe, EEPROM de 8K/4K/2K Bytes, SRAM de 32K/16K/8K, hasta 35 líneas de E/S de uso general, 32 registros de trabajo de uso general, contador en tiempo real (RTC), 6 temporizadores/contadores flexibles con modos de comparación y PWM, un temporizador/contador de 32 bits, 2 USART, un byte de 2 cables orientado Interfaz serie, un convertidor analógico a digital (ADC) de 8 bits y 10 canales con entrada diferencial opcionaltage con ganancia programable, temporizador de vigilancia programable con oscilador interno, un puerto serie SPI, estándar IEEE. Cumple con 1149.1 JTAG Interfaz de prueba, también utilizada para acceder al sistema de depuración en chip y programación y 6 modos de ahorro de energía seleccionables por software.

El modo inactivo detiene la CPU mientras permite que la SRAM, el temporizador/contadores, el puerto SPI y el sistema de interrupción continúen funcionando. El modo de apagado guarda el contenido del registro pero congela el oscilador, desactivando todas las demás funciones del chip hasta la siguiente interrupción o reinicio del hardware. En el modo de ahorro de energía, el temporizador asíncrono continúa ejecutándose, lo que permite al usuario mantener una base de temporizador mientras el resto del dispositivo está inactivo. El modo de reducción de ruido ADC detiene la CPU y todos los módulos de E/S, excepto el temporizador asíncrono y el ADC, para minimizar el ruido de conmutación durante las conversiones de ADC. En el modo de espera, el oscilador RC está funcionando mientras el resto del dispositivo está inactivo. Esto permite un arranque muy rápido combinado con un bajo consumo de energía. En el modo de espera extendido, tanto el oscilador RC principal como el temporizador asíncrono continúan funcionando.

En la Figura 16-3 a continuación se muestra la corriente de suministro típica del microcontrolador con el reloj de la CPU configurado en 2 MHz y el transceptor de radio para los estados más importantes.

Figura 3-2 Corriente de suministro del transceptor de radio y microcontrolador (16 MHz)

La potencia de salida de transmisión está configurada al máximo. Si el transceptor de radio está en modo SLEEP, la corriente es disipada únicamente por el microcontrolador AVR.

En el modo Deep Sleep, todos los bloques digitales principales sin requisitos de retención de datos se desconectan del suministro principal, lo que proporciona una corriente de fuga muy pequeña. El temporizador de vigilancia, el contador de símbolos MAC y el oscilador de 32.768 kHz se pueden configurar para que continúen funcionando.

El dispositivo está fabricado utilizando la tecnología de memoria no volátil de alta densidad de Atmel.

El flash ISP en chip permite reprogramar la memoria del programa en el sistema a través de una interfaz serie SPI, mediante un programador de memoria no volátil convencional o mediante un programa de arranque en chip que se ejecuta en el núcleo del AVR. El programa de inicio puede utilizar cualquier interfaz para descargar el programa de aplicación en la memoria Flash de la aplicación.

El software en la sección Flash de arranque continuará ejecutándose mientras se actualiza la sección Flash de la aplicación, proporcionando una verdadera operación de lectura mientras se escribe. Al combinar una CPU RISC de 8 bits con flash autoprogramable en el sistema en un chip monolítico, el Atmel ATmega2564/1284/644RFR2 es un potente microcontrolador que proporciona una solución altamente flexible y rentable para muchas aplicaciones de control integradas.

El AVR ATmega2564/1284/644RFR2 es compatible con un conjunto completo de herramientas de desarrollo de programas y sistemas que incluyen: compilador de C, ensambladores de macros, depuradores/simuladores de programas, emuladores en circuito y kits de evaluación.

Descripciones de pines

DDVE

Volumen de suministro analógico externotage.

DEVDD

Volumen de suministro digital externotage.

AVDD

Volumen de suministro analógico reguladotage (generado internamente).

DVDD

Volumen de suministro digital reguladotage (generado internamente).

DVSS

Tierra digital.

AVSS

Tierra analógica.

Puerto B (PB7…PB0)

El puerto B es un puerto de E/S bidireccional de 8 bits con resistencias pull-up internas (seleccionadas para cada bit). Los búferes de salida del puerto B tienen características de unidad simétricas con alta capacidad de fuente y sumidero. Como entradas, los pines del puerto B que se bajan externamente generarán corriente si se activan las resistencias pull-up. Los pines del puerto B tienen tres estados cuando se activa una condición de reinicio, incluso si el reloj no está funcionando.

El puerto B también proporciona funciones de varias características especiales del ATmega2564/1284/644RFR2.

Puerto D (PD7…PD0)

El puerto D es un puerto de E/S bidireccional de 8 bits con resistencias pull-up internas (seleccionadas para cada bit). Los búferes de salida del puerto D tienen características de unidad simétricas con alta capacidad de fuente y sumidero. Como entradas, los pines del puerto D que se bajan externamente generarán corriente si se activan las resistencias pull-up. Los pines del puerto D tienen tres estados cuando se activa una condición de reinicio, incluso si el reloj no está funcionando.

El puerto D también proporciona funciones de varias características especiales del ATmega2564/1284/644RFR2.

Puerto E (PE7,PE5…PE0)

Internamente, el puerto E es un puerto de E/S bidireccional de 8 bits con resistencias pull-up internas (seleccionadas para cada bit). Los buffers de salida del puerto E tienen características de unidad simétricas con alta capacidad de fuente y sumidero. Como entradas, los pines del puerto E que están bajados externamente generarán corriente si las resistencias pull-up están activadas. Los pines del Puerto E tienen tres estados cuando se activa una condición de reinicio, incluso si el reloj no está funcionando.

Debido al bajo número de pines del paquete QFN48, el puerto E6 no está conectado a un pin. El puerto E también proporciona funciones de varias características especiales del ATmega2564/1284/644RFR2.

Port F (PF7..PF5,PF4/3,PF2…PF0)

Internamente, el puerto F es un puerto de E/S bidireccional de 8 bits con resistencias pull-up internas (seleccionadas para cada bit). Los buffers de salida del puerto F tienen características de unidad simétricas con alta capacidad de fuente y sumidero. Como entradas, los pines del puerto F que están bajados externamente generarán corriente si las resistencias pull-up están activadas. Los pines del puerto F tienen tres estados cuando se activa una condición de reinicio, incluso si el reloj no está funcionando.

Debido al bajo número de pines del paquete QFN48, los puertos F3 y F4 están conectados al mismo pin. La configuración de E/S debe realizarse con cuidado para evitar una disipación excesiva de energía.

El puerto F también proporciona funciones de varias características especiales del ATmega2564/1284/644RFR2.

Puerto G (PG4,PG3,PG1)

Internamente, el puerto G es un puerto de E/S bidireccional de 6 bits con resistencias pull-up internas (seleccionadas para cada bit). Los buffers de salida del puerto G tienen características de unidad simétricas con alta capacidad de fuente y sumidero. Sin embargo, la fuerza del controlador de PG3 y PG4 se reduce en comparación con los otros pines del puerto. El volumen de salidatagLa caída (VOH, VOL) es mayor mientras que la corriente de fuga es menor. Como entradas, los pines del Puerto G que están bajados externamente generarán corriente si las resistencias pull-up están activadas. Los pines del Puerto G tienen tres estados cuando se activa una condición de reinicio, incluso si el reloj no está funcionando.

Debido al bajo número de pines del puerto del paquete QFN48, G0, G2 y G5 no están conectados a un pin.

El puerto G también proporciona funciones de varias características especiales del ATmega2564/1284/644RFR2.

AVSS_RFP

AVSS_RFP es un pin de tierra dedicado para el puerto de E/S de RF diferencial y bidireccional.

AVSS_RFN

AVSS_RFN es un pin de tierra dedicado para el puerto de E/S de RF diferencial bidireccional.

Solicitud de propuestas

RFP es el terminal positivo para el puerto de E/S de RF diferencial bidireccional.

RFN

RFN es el terminal negativo para el puerto de E/S de RF diferencial y bidireccional.

RSTN

Restablecer entrada. Un nivel bajo en este pin durante más tiempo que la duración mínima del pulso generará un reinicio, incluso si el reloj no está funcionando. No se garantiza que los pulsos más cortos generen un reinicio.

XTAL1

Entrada al oscilador de cristal inversor de 16MHz amplificador. En general, un cristal entre XTAL1 y XTAL2 proporciona el reloj de referencia de 16 MHz del transceptor de radio.

XTAL2

Salida del oscilador de cristal inversor de 16MHz ampmás duradero.

TST

Pin de habilitación del modo de programación y prueba. Si no se utiliza el pin TST, jálelo hacia abajo.

CLKI

Entrada al sistema de reloj. Si se selecciona, proporciona el reloj de funcionamiento del microcontrolador.

Pines no utilizados

Los pines flotantes pueden causar disipación de energía en las entradas digitales.tagmi. Deben estar conectados a una fuente adecuada. En los modos de funcionamiento normal, las resistencias pull-up internas se pueden habilitar (en Restablecer, todos los GPIO están configurados como entrada y las resistencias pull-up aún no están habilitadas).

Los pines de E/S bidireccionales no deben conectarse directamente a tierra ni a la fuente de alimentación.

Se deben conectar los pines de entrada digital TST y CLKI. Si el pin TST no utilizado se puede conectar a AVSS, mientras que CLKI debe conectarse a DVSS.

Los pines de salida son accionados por el dispositivo y no flotan. Los pines de fuente de alimentación, los respectivos pines de suministro de tierra, están conectados entre sí internamente.

XTAL1 y XTAL2 nunca se verán obligados a suministrar vol.tagy al mismo tiempo.

Compatibilidad y limitaciones de funciones del paquete QFN-48

ARÉF

La referencia voltagLa salida del convertidor A/D no está conectada a un pin en el ATmega2564/1284/644RFR2.

Puerto E6

El puerto E6 no está conectado a un pin en el ATmega2564/1284/644RFR2. Las funciones de pin alternativo como entrada de reloj para el temporizador 3 y la interrupción externa 6 no están disponibles.

Puerto F3 y F4

Los puertos F3 y F4 están conectados al mismo pin en el ATmega2564/1284/644RFR2. La configuración de salida debe realizarse con cuidado para evitar un consumo excesivo de corriente.

La función de pin alternativo del puerto F4 es utilizada por el JTAG interfaz. Si la JTAG Cuando se utiliza una interfaz, el puerto F3 debe configurarse como entrada y la salida de función de pin alternativo DIG4 (indicador RX/TX) debe estar desactivada. De lo contrario, la JTAG La interfaz no funcionará. El fusible SPIEN debe programarse para poder borrar un programa que accidentalmente controla el puerto F3.

Solo hay 7 canales de entrada de un solo extremo disponibles para el ADC.

Puerto G0

El puerto G0 no está conectado a un pin en el ATmega2564/1284/644RFR2. La función de pin alternativo DIG3 (indicador RX/TX invertido) no está disponible. si el jTAG La interfaz no se usa, la salida de función de pin alternativo DIG4 del puerto F3 aún se puede usar como indicador RX/TX.

Puerto G2

El puerto G2 no está conectado a un pin en el ATmega2564/1284/644RFR2. La función de pin alternativo AMR (entrada de lectura de medidor automatizada asíncrona al temporizador 2) no está disponible.

Puerto G5

El puerto G5 no está conectado a un pin en el ATmega2564/1284/644RFR2. La función de pin alternativo OC0B (canal de comparación de salida del temporizador 8 de 0 bits) no está disponible.

RSTON

La salida de reinicio RSTON que indica el estado de reinicio interno no está conectada a un pin en el ATmega2564/1284/644RFR2.

Resumen de configuración

Según los requisitos de la aplicación, un tamaño de memoria variable permite optimizar el consumo de corriente y la corriente de fuga.

Tabla 3-1 Configuración de la memoria

| Dispositivo | Destello | Memoria EEPROM | Memoria RAM |

| ATmega2564RFR2 | 256 KB | 8 KB | 32 KB |

| ATmega1284RFR2 | 128 KB | 4 KB | 16 KB |

| ATmega644RFR2 | 64 KB | 2 KB | 8 KB |

El paquete y la configuración de pines asociados son los mismos para todos los dispositivos que brindan funcionalidad completa a la aplicación.

Tabla 3-2 Configuración del sistema

| Dispositivo | Paquete | Entrada y salida de GP | Serie SI | canal CAD |

| ATmega2564RFR2 | QFN48 | 33 | 2 USART, SPI, TWI | 7 |

| ATmega1284RFR2 | QFN48 | 33 | 2 USART, SPI, TWI | 7 |

| ATmega644RFR2 | QFN48 | 33 | 2 USART, SPI, TWI | 7 |

Los dispositivos están optimizados para aplicaciones basadas en ZigBee y la especificación IEEE 802.15.4. Debería ser posible tener una pila de aplicaciones, una capa de red, una interfaz de sensor y un excelente control de energía combinados en un solo chip durante muchos años de funcionamiento.

Tabla 3-3 Aplicación Profile

| Dispositivo | Solicitud |

| ATmega2564RFR2 | Coordinador/enrutador de red grande para IEEE 802.15.4/ZigBee Pro |

| ATmega1284RFR2 | Coordinador de Red / Enrutador para IEEE 802.15.4 |

| ATmega644RFR2 | Dispositivo de nodo final/procesador de red |

Circuitos de aplicación

Esquema de aplicación básica

En la Figura 2564-1284 a continuación se muestra un esquema de aplicación básica del ATmega644/2/4RFR1 con un conector RF de un solo extremo y la Lista de materiales asociada en la Tabla 4-1 en la página 10. La entrada de RF de un solo extremo de 50 Ω se transforma a la impedancia diferencial del puerto de RF de 100 Ω usando Balun B1. Los condensadores C1 y C2 proporcionan acoplamiento de CA de la entrada de RF al puerto de RF, el condensador C4 mejora la adaptación.

Figura 4-1. Esquema de aplicación básica (paquete de 48 pines)

Los condensadores de derivación de la fuente de alimentación (CB2, CB4) están conectados al pin de suministro analógico externo (EVDD, pin 44) y al pin de suministro digital externo (DEVDD, pin 16). El condensador C1 proporciona el acoplamiento de CA requerido de RFN/RFP.

Los pasadores flotantes pueden causar una disipación excesiva de energía (por ejemplo, durante el encendido). Deben estar conectados a una fuente adecuada. GPIO no se conectará directamente a tierra ni a la fuente de alimentación.

Se deben conectar los pines de entrada digital TST y CLKI. Si nunca se va a utilizar el pin TST, se puede conectar a AVSS, mientras que un pin CLKI no utilizado se puede conectar a DVSS (consulte el capítulo “Pines no utilizados”).

Los condensadores CB1 y CB3 son condensadores de derivación para el voltaje analógico y digital integrado.tage reguladores para garantizar un funcionamiento estable y mejorar la inmunidad al ruido.

Los condensadores deben colocarse lo más cerca posible de las clavijas y deben tener una conexión a tierra de baja resistencia e inductancia para lograr el mejor rendimiento.

El cristal (XTAL), los dos condensadores de carga (CX1, CX2) y el circuito interno conectado a los pines XTAL1 y XTAL2 forman el oscilador de cristal de 16 MHz para el transceptor de 2.4 GHz. Para lograr la mejor precisión y estabilidad de la frecuencia de referencia, se deben evitar grandes capacitancias parásitas. Las líneas Crystal deben tenderse lo más cortas posible y no cerca de señales de E/S digitales. Esto es especialmente necesario para los modos de alta velocidad de datos.

El cristal de 32.768 kHz conectado al oscilador de cristal interno de baja potencia (sub 1 µA) proporciona una referencia de tiempo estable para todos los modos de baja potencia, incluido el contador de símbolos IEEE 32 de 802.15.4 bits (“Contador de símbolos MAC”) y la aplicación de reloj en tiempo real utilizando el sistema asíncrono. temporizador T/C2 (“Temporizador/Contador2 con PWM y funcionamiento asíncrono”).

La capacitancia en derivación total, incluidos CX3 y CX4, no debe exceder los 15 pF en ambos pines.

La muy baja corriente de suministro del oscilador requiere un diseño cuidadoso de la PCB y se debe evitar cualquier ruta de fuga.

La diafonía y la radiación provenientes de la conmutación de señales digitales a las clavijas de cristal o a las clavijas de RF pueden degradar el rendimiento del sistema. Se recomienda programar los ajustes mínimos de intensidad del controlador para la señal de salida digital (consulte “DPDS0 – Registro de intensidad del controlador de puerto 0”).

Tabla 4-1. Lista de materiales (BoM)

| Designante | Descripción | Valor | Fabricante | Número de pieza | Comentario |

| B1 | Balún SMD

Balún/filtro SMD |

2.4 GHz | Tecnología Wuerth Johanson | 748421245

2450FB15L0001 |

Filtro incluido |

| CB1 CB3 | LDO VREG

condensador de derivación |

1 mF (mínimo 100 nF) | AVX

Murata |

0603YD105KAT2A GRM188R61C105KA12D | X5R (0603) 10% 16 V |

| CB2 CB4 | Condensador de derivación de la fuente de alimentación | 1 mF (mínimo 100 nF) | |||

| CX1, CX2 | Condensador de carga de cristal de 16MHz | 12 pF | AVX

Murata |

06035A120JA GRP1886C1H120JA01 | DIENTE (0603) 5% 50 V |

| CX3, CX4 | Condensador de carga de cristal de 32.768 kHz. | 12 … 25 pF | |||

| C1, C2 | Condensador de acoplamiento RF | 22 pF | Epcos Epcos AVX | B37930 B37920

06035A220JAT2A |

C0G 5% 50V (0402 o 0603) |

| C4 (opcional) | coincidencia de radiofrecuencia | 0.47 pF | Tecnología Johnstech | ||

| XTAL | Cristal | CX-4025 16MHz

SX-4025 16MHz |

ACAL Taitjen Siward | XWBBPL-F-1 A207-011 | |

| XTAL 32kHz | Cristal | Rs=100 kiloohmios |

Historial de revisiones

Tenga en cuenta que los números de página de referencia en esta sección se refieren a este documento. La revisión de referencia en esta sección se refiere a la revisión del documento.

Rev. 42073BS-MCU Inalámbrico-09/14

- Contenido sin cambios: recreado para lanzamiento combinado con la hoja de datos.

Rev. 8393AS-MCU Inalámbrico-02/13

- Lanzamiento inicial.

© 2014 Corporación Atmel. Reservados todos los derechos. / Rev.: 42073BS-MCU Wireless-09/14 Atmel®, el logotipo de Atmel y sus combinaciones, Enabling Unlimited Possibilities® y otros son marcas comerciales registradas o marcas comerciales de Atmel Corporation o sus subsidiarias. Otros términos y nombres de productos pueden ser marcas comerciales de otros.

Descargo de responsabilidad: La información de este documento se proporciona en relación con los productos de Atmel. No se otorga ninguna licencia, expresa o implícita, por impedimento legal o de otro modo, a ningún derecho de propiedad intelectual mediante este documento o en relación con la venta de productos Atmel. EXCEPTO LO ESTABLECIDO EN LOS TÉRMINOS Y CONDICIONES DE VENTAS DE ATMEL UBICADOS EN EL ATMEL WEBSITIO WEB, ATMEL NO ASUME NINGUNA RESPONSABILIDAD Y RENUNCIA A CUALQUIER GARANTÍA EXPRESA, IMPLÍCITA O LEGAL RELACIONADA CON SUS PRODUCTOS, INCLUYENDO, ENTRE OTROS, LA GARANTÍA IMPLÍCITA DE COMERCIABILIDAD, IDONEIDAD PARA UN FIN DETERMINADO O NO VIOLACIÓN. EN NINGÚN CASO ATMEL SERÁ RESPONSABLE DE CUALQUIER DAÑO DIRECTO, INDIRECTO, CONSECUENTE, PUNITIVO, ESPECIAL O INCIDENTAL (INCLUYENDO, SIN LIMITACIÓN, DAÑOS POR PÉRDIDAS Y BENEFICIOS, INTERRUPCIÓN DEL NEGOCIO O PÉRDIDA DE INFORMACIÓN) QUE SURJAN DEL USO O LA INCAPACIDAD DE USO ESTE DOCUMENTO, INCLUSO SI ATMEL HA SIDO ADVERTIDO DE LA POSIBILIDAD DE TALES DAÑOS. Atmel no hace representaciones ni garantías con respecto a la exactitud o integridad del contenido de este documento y se reserva el derecho de realizar cambios en las especificaciones y descripciones de los productos en cualquier momento sin previo aviso. Atmel no se compromete a actualizar la información aquí contenida. A menos que se indique específicamente lo contrario, los productos de Atmel no son adecuados y no deben utilizarse en aplicaciones automotrices. Los productos de Atmel no están destinados, autorizados ni garantizados para su uso como componentes en aplicaciones destinadas a soportar o sostener la vida.

Electrónica Mouser

Distribuidor autorizado

Haga clic para View Información sobre precios, inventario, entrega y ciclo de vida:

ATMEGA644RFR2-ZU

ATMEGA2564RFR2-ZF

ATMEGA644RFR2-ZF

ATMEGA644RFR2-ZUR

ATMEGA1284RFR2-ZU

ATMEGA2564RFR2-ZFR

ATMEGA1284RFR2-ZFR

ATMEGA1284RFR2-ZUR

ATMEGA644RFR2-ZFR

ATMEGA2564RFR2-ZU

ATMEGA1284RFR2-ZF

ATMEGA2564RFR2-ZUR

Atención al cliente

Corporación Atmel

1600 Technology Drive

San José, CA 95110

EE.UU

Teléfono: (+1)408-441-0311

Fax: (+1)408-487-2600

www.atmel.com

Documentos / Recursos

|

Microcontrolador AVR Atmel ATmega2564 de 8 bits [pdf] Manual del propietario ATmega2564RFR2, ATmega1284RFR2, ATmega644RFR2, Microcontrolador AVR de 2564 bits ATmega8, ATmega2564, Microcontrolador AVR de 8 bits, Microcontrolador AVR, Microcontrolador |