Atmel ATmega2564 8位 AVR 微控制器

特征

- 硬件辅助网络支持多 PAN 地址过滤

- 先进的硬件辅助降低功耗

- 高性能、低功耗 AVR® 8 位微控制器

- 先进的RISC架构

- 135条功能强大的指令–多数单个时钟周期执行

- 32×8 通用工作寄存器 / 片上 2 周期乘法器

- 16 MHz 和 16V 时吞吐量高达 1.8 MIPS – 完全静态操作

- 非易失性程序和数据存储器

- 256K/128K/64K 字节系统内自编程闪存

- 耐久性:10°C 下 000 次写入/擦除循环(125°C 下 25 次循环)

- 8K/4K/2K字节EEPROM

- 耐久性:20°C 下 000 次写入/擦除循环(125°C 下 100 次循环)

- 32K/16K/8K 字节内部 SRAM

- JTAG (符合 IEEE 标准 1149.1)接口

- 根据 J 的边界扫描能力TAG 标准

- 广泛的片上调试支持

- 通过 J 对闪存 EEPROM、保险丝和锁定位进行编程TAG 界面

- 外围功能

- 多个定时器/计数器和 PWM 通道

- 具有独立振荡器的实时计数器

- 10 位、330 ks/s A/D 转换器;模拟比较器;片上温度传感器

- 主/从 SPI 串行接口

- 两个可编程串行 USART

- 面向字节的双线串行接口

- 高级中断处理程序和省电模式

- 带有独立片上振荡器的看门狗定时器

- 上电复位和低电流欠压检测器

- 适用于 2.4 GHz ISM 频段的完全集成低功耗收发器

- 高功率 AmpTX 频谱旁瓣抑制支持放大器

- 支持的数据速率:250 kb/s、500 kb/s、1 Mb/s、2 Mb/s

- RX 灵敏度为 -100 dBm;TX 输出功率高达 3.5 dBm

- 硬件辅助 MAC(自动确认、自动重试)

- 32 位 IEEE 802.15.4 符号计数器

- SFD-检测、扩展;解扩展;帧结构;CRC-16 计算

- 天线分集和 TX/RX 控制 / TX/RX 128 字节帧缓冲器

- 具有 5 MHz 和 500 kHz 通道间隔的 PLL 合成器,适用于 2.4 GHz ISM 频段

- 硬件安全(AES、真随机数生成器)

- 集成晶体振荡器(32.768 kHz 和 16 MHz,需要外部晶体)

- I/O 和封装

- 33 条可编程 I/O 线

- 48 焊盘 QFN(符合 RoHS/完全绿色标准)

- 温度范围:-40°C 至 125°C 工业

- AVR 和 Rx/Tx 的超低功耗(1.8 至 3.6V):10.1mA/18.6 mA

- CPU 活动模式 (16MHz):4.1 mA

- 2.4GHz 收发器:RX_ON 6.0 mA / TX 14.5 mA(最大 TX 输出功率)

- 深度睡眠模式:<700nA @ 25°C

- 速度等级:0 – 16 MHz @ 1.8 – 3.6V 范围,带集成音量tag监管者

应用

- ZigBee®/ IEEE 802.15.4-2011/2006/2003™ – 完整和精简功能设备

- 带微控制器的通用 2.4GHz ISM 频段收发器

- RF4CE、SP100、WirelessHART™、ISM 应用和 IPv6/6LoWPAN

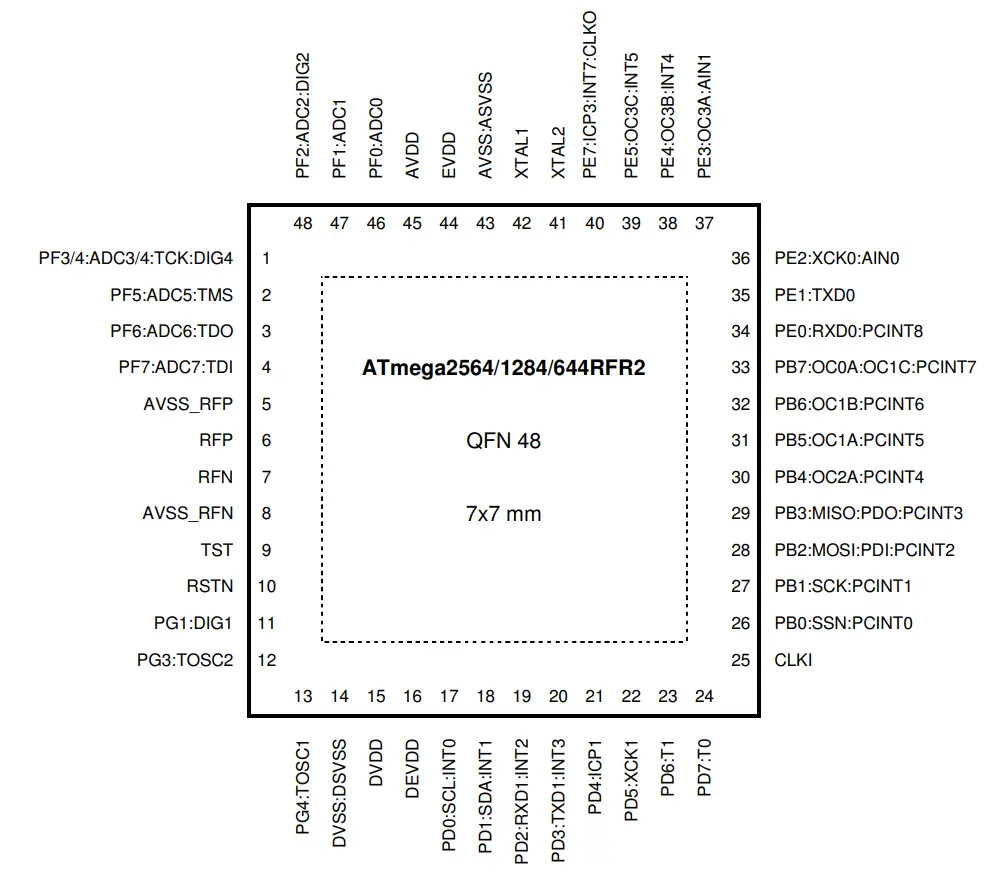

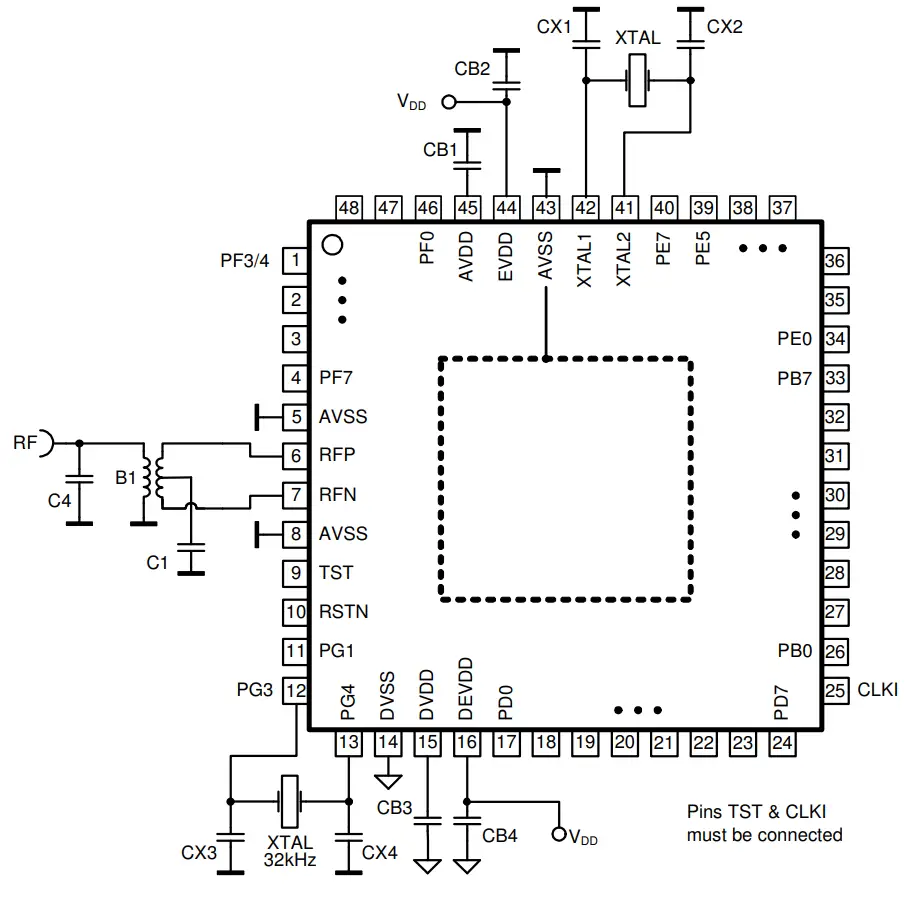

引脚配置

图 1-1. ATmega2564/1284/644RFR2 引脚分布

笔记:QFN/MLF 封装下方的大型中心焊盘由金属制成,内部连接到 AVSS。应将其焊接或粘合到电路板上,以确保良好的机械稳定性。如果中心焊盘未连接,封装可能会从电路板上松动。不建议使用裸露焊盘代替常规 AVSS 引脚。

免责声明

本数据表所含的典型值基于采用类似工艺技术制造的其他 AVR 微控制器和无线电收发器的模拟和特性分析结果。最小值和最大值将在器件特性分析后提供。

超过view

ATmega2564/1284/644RFR2 是基于 AVR 增强型 RISC 架构的低功耗 CMOS 8 位微控制器,结合了 2.4 GHz ISM 频段的高数据速率收发器。

通过在单个时钟周期内执行强大的指令,该设备实现了接近每MHz 1 MIPS的吞吐量,从而使系统设计人员能够优化功耗与处理速度。

无线电收发器提供从 250 kb/s 到 2 Mb/s 的高数据速率、帧处理、出色的接收器灵敏度和高发射输出功率,从而实现非常稳定的无线通信。

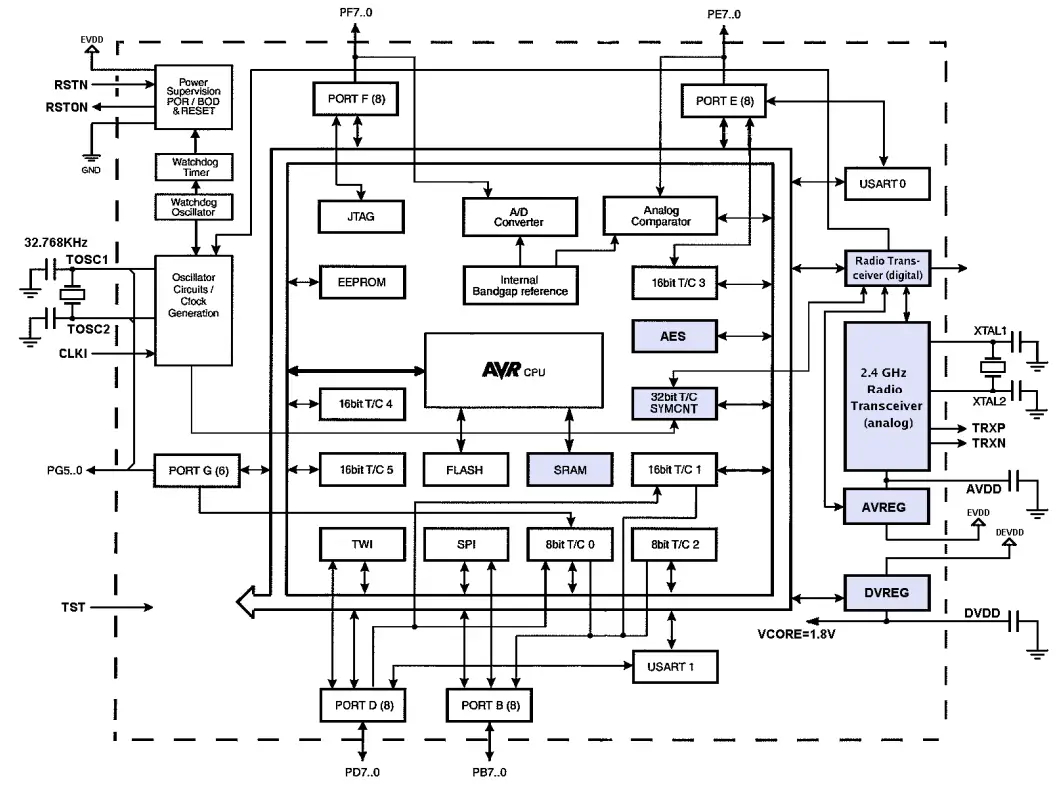

框图

图 3-1 框图

AVR 核心结合了丰富的指令集和 32 个通用工作寄存器。所有 32 个寄存器都直接连接到算术逻辑单元 (ALU)。两个独立的寄存器可以通过一个时钟周期内执行的一条指令进行访问。由此产生的架构非常高效地执行代码,同时实现比传统 CISC 微控制器快十倍的吞吐量。该系统包括内部卷tag调节和先进的电源管理。漏电流小,可延长电池供电时间。

该无线电收发器是一款完全集成的 ZigBee 解决方案,使用最少数量的外部元件。它结合了出色的 RF 性能、低成本、小尺寸和低电流消耗。该无线电收发器包括晶体稳定的分数 N 合成器、发射器和接收器,以及具有扩频和解扩功能的全直接序列扩频信号 (DSSS) 处理。该设备完全兼容 IEEE802.15.4-2011/2006/2003 和 ZigBee 标准。 ATmega2564/1284/644RFR2 提供以下功能:具有读写功能的 256K/128K/64K 字节系统内可编程 (ISP) 闪存、8K/4K/2K 字节 EEPROM、32K/16K/8K 字节 SRAM、最多 35 个通用 I/O 线、32 个通用工作寄存器、实时计数器 (RTC)、6 个灵活的定时器/计数器(具有比较模式和 PWM)、一个 32 位定时器/计数器、2 个 USART、一个面向字节的两线串行接口、一个 2 通道、8 位模数转换器 (ADC)(带有可选差分输入tage 具有可编程增益、带内部振荡器的可编程看门狗定时器、SPI 串行端口、符合 IEEE 标准 1149.1 JTAG 测试接口,也用于访问片上调试系统和编程以及6种软件可选的省电模式。

空闲模式会停止 CPU,同时允许 SRAM、定时器/计数器、SPI 端口和中断系统继续运行。掉电模式会保存寄存器内容,但会冻结振荡器,禁用所有其他芯片功能,直到下一次中断或硬件复位。在省电模式下,异步定时器继续运行,允许用户在设备其余部分处于休眠状态时维持定时器基数。ADC 降噪模式会停止 CPU 和除异步定时器和 ADC 之外的所有 I/O 模块,以最大限度地减少 ADC 转换期间的开关噪声。在待机模式下,RC 振荡器正在运行,而设备其余部分处于休眠状态。这允许非常快速的启动和低功耗。在扩展待机模式下,主 RC 振荡器和异步定时器都继续运行。

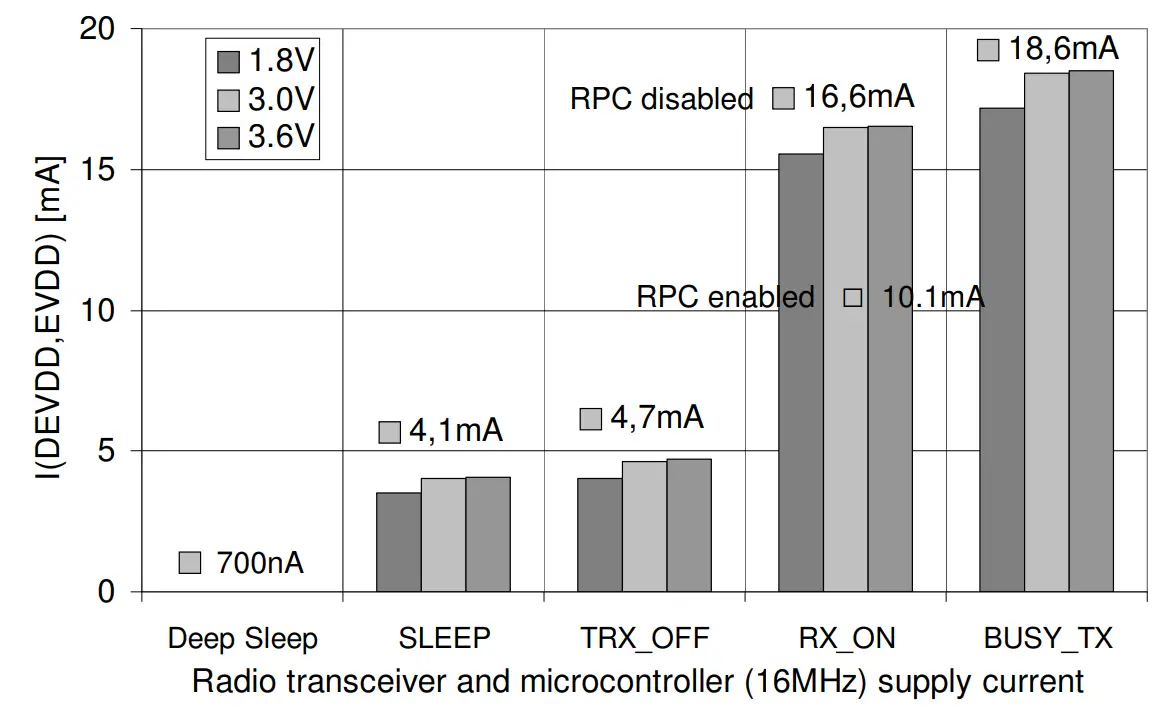

当 CPU 时钟设置为 16MHz 时,微控制器和无线电收发器处于最重要状态时的典型电源电流如下图 3-2 所示。

图 3-2 无线电收发器和微控制器(16MHz)电源电流

发射输出功率设置为最大值。如果无线电收发器处于休眠模式,电流仅由 AVR 微控制器耗散。

在深度睡眠模式下,所有没有数据保留要求的主要数字模块都与主电源断开,从而提供非常小的漏电流。看门狗定时器、MAC 符号计数器和 32.768kHz 振荡器可以配置为继续运行。

该设备采用 Atmel 的高密度非易失性存储器技术制造。

片上 ISP 闪存允许通过 SPI 串行接口、常规非易失性存储器编程器或运行在 AVR 核心上的片上引导程序在系统内对程序存储器进行重新编程。引导程序可以使用任何接口将应用程序下载到应用闪存中。

在更新应用程序闪存部分时,引导闪存部分中的软件将继续运行,从而提供真正的“边读边写”操作。通过将 8 位 RISC CPU 与单片芯片上的系统内自编程闪存相结合,Atmel ATmega2564/1284/644RFR2 是一款功能强大的微控制器,可为许多嵌入式控制应用提供高度灵活且经济高效的解决方案。

ATmega2564/1284/644RFR2 AVR 配备全套程序和系统开发工具,包括:C 编译器、宏汇编器、程序调试器/模拟器、在线仿真器和评估套件。

引脚说明

电压差

外部模拟电源电压tage.

开发板

外部数字电源电压tage.

电源电压

稳压模拟电源电压tage(内部生成)。

影碟

受监管的数字供应量tage(内部生成)。

DVSS

数字地。

AVSS

模拟接地。

端口 B (PB7…PB0)

B口是一个8位双向I/O口,内部有上拉电阻(每位选择)。 端口 B 输出缓冲器具有对称驱动特性,具有高灌电流和拉电流能力。 作为输入,如果上拉电阻被激活,外部拉低的端口 B 引脚将提供电流。 当复位条件激活时,端口 B 引脚处于三态,即使时钟未运行也是如此。

端口 B 还提供 ATmega2564/1284/644RFR2 的各种特殊功能。

端口 D (PD7…PD0)

D口是一个8位双向I/O口,带有内部上拉电阻(为每一位选择)。 端口 D 输出缓冲器具有对称驱动特性,具有高灌电流和拉电流能力。 作为输入,如果上拉电阻被激活,外部拉低的端口 D 引脚将提供电流。 当复位条件激活时,端口 D 引脚处于三态,即使时钟未运行也是如此。

端口 D 还提供 ATmega2564/1284/644RFR2 的各种特殊功能。

端口 E(PE7、PE5…PE0)

端口 E 内部是一个 8 位双向 I/O 端口,带有内部上拉电阻(每个位都可选)。端口 E 输出缓冲器具有对称驱动特性,具有高吸电和拉电能力。作为输入,如果上拉电阻激活,则从外部拉低的端口 E 引脚将拉出电流。当复位条件变为有效时,即使时钟未运行,端口 E 引脚也会处于三态。

由于 QFN48 封装的引脚数较少,端口 E6 未连接到引脚。端口 E 还提供 ATmega2564/1284/644RFR2 的各种特殊功能。

Port F (PF7..PF5,PF4/3,PF2…PF0)

内部而言,端口 F 是一个 8 位双向 I/O 端口,带有内部上拉电阻(每个位都可选)。端口 F 输出缓冲器具有对称驱动特性,具有高吸电和拉电能力。作为输入,如果上拉电阻激活,则从外部拉低的端口 F 引脚将拉出电流。当复位条件变为有效时,即使时钟未运行,端口 F 引脚也会处于三态。

由于 QFN48 封装引脚数较少,端口 F3 和 F4 连接到同一引脚。应谨慎进行 I/O 配置,以避免功耗过大。

端口 F 还提供 ATmega2564/1284/644RFR2 的各种特殊功能。

G 口 (PG4,PG3,PG1)

内部端口 G 是一个 6 位双向 I/O 端口,带有内部上拉电阻(每个位都选择)。端口 G 输出缓冲器具有对称驱动特性,具有高灌入和拉出能力。但是,与其他端口引脚相比,PG3 和 PG4 的驱动强度有所降低。输出电压tag压降 (VOH、VOL) 越高,漏电流越小。作为输入,如果上拉电阻激活,外部拉低的端口 G 引脚将提供电流。当复位条件变为有效时,即使时钟未运行,端口 G 引脚也会处于三态。

由于QFN48封装的引脚数少,因此端口G0、G2和G5没有连接到引脚。

端口 G 还提供 ATmega2564/1284/644RFR2 的各种特殊功能。

AVSS_RFP

AVSS_RFP 是双向差分 RF I/O 端口的专用接地引脚。

AVSS_RFN

AVSS_RFN 是双向差分 RF I/O 端口的专用接地引脚。

征求建议书

RFP 是双向差分 RF I/O 端口的正极。

射频网

RFN 是双向差分 RF I/O 端口的负极。

RSTN

复位输入。此引脚上的低电平持续时间超过最小脉冲长度将产生复位,即使时钟未运行。较短的脉冲不能保证产生复位。

晶振1

输入至反相 16MHz 晶体振荡器 amp收发器。通常,XTAL1 和 XTAL2 之间的晶体为无线电收发器提供 16MHz 参考时钟。

晶振2

反相16MHz晶体振荡器的输出 amp扩音器。

尖沙咀

编程和测试模式启用引脚。如果未使用引脚 TST,请将其拉至低电平。

时钟输入接口

时钟系统输入。如果选中,则提供微控制器的工作时钟。

未使用的引脚

浮动引脚可能会导致数字输入引脚的功率耗散tage. 它们应该连接到适当的源。在正常操作模式下,可以启用内部上拉电阻(在重置时,所有 GPIO 都配置为输入,上拉电阻仍未启用)。

双向I/O引脚不得直接连接到地或者电源。

数字输入引脚 TST 和 CLKI 必须连接。如果未使用,引脚 TST 可以连接到 AVSS,而 CLKI 应连接到 DVSS。

输出引脚由器件驱动,不浮动。电源引脚和接地引脚在内部连接在一起。

XTAL1和XTAL2不得被迫提供voltag同时。

QFN-48 封装的兼容性和功能限制

参考文献

参考体积tagA/D 转换器的输出未连接到 ATmega2564/1284/644RFR2 中的引脚。

E6端口

端口 E6 未连接到 ATmega2564/1284/644RFR2 中的引脚。备用引脚用作定时器 3 的时钟输入,并且外部中断 6 不可用。

端口 F3 和 F4

端口 F3 和 F4 连接到 ATmega2564/1284/644RFR2 中的同一引脚。输出配置应谨慎进行,以避免电流消耗过大。

端口F4的备用引脚功能由JTAG 界面。 如果 JTAG 接口时,必须将端口 F3 配置为输入,并且必须禁用备用引脚功能输出 DIG4(RX/TX 指示器)。否则,JTAG 接口将无法工作。应对 SPIEN 保险丝进行编程,以便能够擦除意外驱动端口 F3 的程序。

该 ADC 仅有 7 个单端输入通道可用。

G0端口

端口 G0 未连接到 ATmega2564/1284/644RFR2 中的引脚。备用引脚功能 DIG3(反转 RX/TX 指示器)不可用。如果 JTAG 接口未使用时,端口 F4 的 DIG3 备用引脚功能输出仍可用作 RX/TX 指示器。

G2端口

端口 G2 未连接到 ATmega2564/1284/644RFR2 中的引脚。备用引脚功能 AMR(异步自动仪表读数输入至定时器 2)不可用。

G5端口

端口 G5 未连接到 ATmega2564/1284/644RFR2 中的引脚。备用引脚功能 OC0B(8 位定时器 0 的输出比较通道)不可用。

瑞斯顿

表示内部复位状态的 RSTON 复位输出未连接到 ATmega2564/1284/644RFR2 中的引脚。

配置摘要

根据应用要求,可变的存储器大小可以优化电流消耗和漏电流。

表 3-1 内存配置

| 设备 | 闪光 | 电可擦除只读存储器 | 静态存储器 |

| ATmega2564RFR2 | 256 KB | 8 KB | 32 KB |

| ATmega1284RFR2 | 128 KB | 4 KB | 16 KB |

| ATmega644RFR2 | 64 KB | 2 KB | 8 KB |

所有器件的封装和相关引脚配置都是相同的,从而为应用提供完整的功能。

表 3-2 系统配置

| 设备 | 包裹 | 通用输入输出 | 串行中频 | ADC 通道 |

| ATmega2564RFR2 | QFN48 | 33 | 2 USART、SPI、TWI | 7 |

| ATmega1284RFR2 | QFN48 | 33 | 2 USART、SPI、TWI | 7 |

| ATmega644RFR2 | QFN48 | 33 | 2 USART、SPI、TWI | 7 |

这些设备针对基于 ZigBee 和 IEEE 802.15.4 规范的应用进行了优化。将应用堆栈、网络层、传感器接口和出色的电源控制集成到单个芯片中,可以运行多年。

表 3-3 申请程序file

| 设备 | 应用 |

| ATmega2564RFR2 | IEEE 802.15.4 / ZigBee Pro 大型网络协调器 / 路由器 |

| ATmega1284RFR2 | IEEE 802.15.4 网络协调器/路由器 |

| ATmega644RFR2 | 端节点设备/网络处理器 |

应用电路

基本应用原理图

下图 2564-1284 显示了带有单端 RF 连接器的 ATmega644/2/4RFR1 的基本应用原理图,第 4 页表 1-10 显示了相关的物料清单。使用 Balun B50 将 100Ω 单端 RF 输入转换为 1Ω 差分 RF 端口阻抗。电容器 C1 和 C2 提供 RF 输入到 RF 端口的交流耦合,电容器 C4 可改善匹配。

图 4-1. 基本应用原理图(48 引脚封装)

电源旁路电容(CB2、CB4)连接到外部模拟电源引脚(EVDD,引脚 44)和外部数字电源引脚(DEVDD,引脚 16)。电容 C1 提供 RFN/RFP 所需的交流耦合。

浮动引脚可能导致功耗过大(例如,在通电期间)。应将它们连接到适当的电源。GPIO 不得直接接地或连接到电源。

必须连接数字输入引脚 TST 和 CLKI。如果引脚 TST 永远不会使用,则可以将其连接到 AVSS,而未使用的引脚 CLKI 可以连接到 DVSS(请参阅“未使用的引脚”一章)。

电容器 CB1 和 CB3 是集成模拟和数字音量控制器的旁路电容器。tag调节器以确保稳定运行并提高抗噪能力。

电容器应尽可能靠近引脚放置,并且应具有低电阻和低电感接地,以实现最佳性能。

晶体 (XTAL)、两个负载电容器 (CX1、CX2) 以及连接到引脚 XTAL1 和 XTAL2 的内部电路构成了 16GHz 收发器的 2.4MHz 晶体振荡器。为了实现参考频率的最佳精度和稳定性,必须避免较大的寄生电容。晶体线路应尽可能短,并且不要靠近数字 I/O 信号。这对于高数据速率模式尤其需要。

连接到内部低功耗(低于 32.768µA)晶体振荡器的 1 kHz 晶体为所有低功耗模式提供了稳定的时间参考,包括 32 位 IEEE 802.15.4 符号计数器(“MAC 符号计数器”)和使用异步定时器 T/C2(“带 PWM 和异步操作的定时器/计数器 2”)的实时时钟应用程序。

包括 CX3、CX4 在内的总分流电容在两个引脚上不应超过 15pF。

振荡器的极低电源电流要求精心布局 PCB,并且必须避免任何泄漏路径。

切换数字信号到晶体引脚或 RF 引脚的串扰和辐射会降低系统性能。建议对数字输出信号的最小驱动强度设置进行编程(参见“DPDS0 – 端口驱动器强度寄存器 0”)。

表 4-1. 物料清单 (BoM)

| 代号 | 描述 | 价值 | 制造商 | 零件编号 | 评论 |

| B1 | SMD平衡器

SMD 平衡器/滤波器 |

2.4 GHz | 伍尔特约翰逊技术公司 | 748421245

2450FB15L0001 |

包含过滤器 |

| CB1 CB3 | LDO电压调节器

旁路电容 |

1 mF(最小 100 nF) | AVX

村田 |

0603YD105KAT2A GRM188R61C105KA12D | X5R (0603) 10%16V |

| CB2 CB4 | 电源旁路电容 | 1 mF(最小 100 nF) | |||

| CX1、CX2 | 16MHz 晶体负载电容 | 12 皮法 | AVX

村田 |

06035A120JA GRP1886C1H120JA01 | 重心 (0603) 5%50V |

| CX3、CX4 | 32.768kHz晶体负载电容 | 12 … 25 皮法 | |||

| C1、C2 | 射频耦合电容 | 22 皮法 | 爱普科斯 爱普科斯 AVX | B37930 B37920

06035A220JAT2A |

C0G 5% 50V (0402 或 0603) |

| C4(可选) | 射频匹配 | 0.47 皮法 | 约翰斯特奇 | ||

| 晶振 | 水晶 | CX-4025 16 兆赫

SX-4025 16兆赫 |

ACAL 泰特珍·西沃德 | XWBBPL-F-1 A207-011 | |

| 晶体 32kHz | 水晶 | Rs=100千欧姆 |

修订历史

请注意,本节中的引用页码是指本文档。 本节中的引用修订是指文档修订。

修订版 42073BS-MCU 无线-09/14

- 内容不变 – 重新创建以便与数据表合并发布。

修订版 8393AS-MCU 无线-02/13

- 初始版本。

© 2014 Atmel Corporation。保留所有权利。/ 修订版:42073BS-MCU Wireless-09/14 Atmel®、Atmel 徽标及其组合、Enabling Unlimited Possibilities® 等是 Atmel Corporation 或其子公司的注册商标或商标。其他术语和产品名称可能是其他公司的商标。

免责声明:本文档中的信息与 Atmel 产品有关。 本文档或与 Atmel 产品的销售相关的任何知识产权均未以禁止反言或其他方式授予任何明示或暗示的许可。 ATMEL 上的 ATMEL 销售条款和条件中规定的除外 WEBSITE, ATMEL 不承担任何责任,并且不承担与其产品有关的任何明示、默示或法定保证,包括但不限于对适销性、特定用途适用性或不侵权的默示保证。 在任何情况下,ATMEL 均不对因使用或无法使用而引起的任何直接、间接、后果性、惩罚性、特殊或附带损害(包括但不限于损失和利润损害、业务中断或信息丢失)负责本文件,即使 ATMEL 已被告知此类损害的可能性。 Atmel 对本文档内容的准确性或完整性不作任何陈述或保证,并保留随时更改规格和产品说明的权利,恕不另行通知。 Atmel 不承诺更新此处包含的信息。 除非另有明确规定,否则 Atmel 产品不适合也不应用于汽车应用。 Atmel 产品并非旨在、授权或保证用作旨在支持或维持生命的应用中的组件。

贸泽电子

授权经销商

点击 View 定价、库存、交付和生命周期信息:

微芯片:

ATMEGA644RFR2-ZU

ATMEGA2564RFR2-ZF

ATMEGA644RFR2-ZF

ATMEGA644RFR2-ZUR

ATMEGA1284RFR2-ZU

ATMEGA2564RFR2-ZFR

ATMEGA1284RFR2-ZFR

ATMEGA1284RFR2-ZUR

ATMEGA644RFR2-ZFR

ATMEGA2564RFR2-ZU

ATMEGA1284RFR2-ZF

ATMEGA2564RFR2-ZUR

客户支持

爱特梅尔公司

1600技术驱动

加利福尼亚州圣何塞 95110

美国

电话: (+1)408-441-0311

传真:(+1)408-487-2600

www.atmel.com

文件/资源

|

Atmel ATmega2564 8位 AVR 微控制器 [pdf] 用户手册 ATmega2564RFR2、ATmega1284RFR2、ATmega644RFR2、ATmega2564 8 位 AVR 微控制器、ATmega2564、8 位 AVR 微控制器、AVR 微控制器、微控制器 |