Espressif ESP32-C6 Series SoC Errata användarmanual

Introduktion

Detta dokument beskriver kända fel i ESP32-C6-serien av SoCs.

Detta dokument beskriver kända fel i ESP32-C6-serien av SoCs.

Chip Identifiering

Notera:

Kontrollera länken eller QR-koden för att se till att du använder den senaste versionen av detta dokument:

https://espressif.com/sites/default/files/documentation/esp32-c6_errata_en.pdf

Kontrollera länken eller QR-koden för att se till att du använder den senaste versionen av detta dokument:

https://espressif.com/sites/default/files/documentation/esp32-c6_errata_en.pdf

1 Chiprevision

Espressif introducerar vM.X numreringsschema för att indikera chiprevisioner.

M – Huvudnummer, som indikerar den större revisionen av chipprodukten. Om detta nummer ändras betyder det att programvaran som används för den tidigare versionen av produkten är inkompatibel med den nya produkten, och mjukvaruversionen ska uppgraderas för användning av den nya produkten.

X – Mindre nummer, som indikerar den mindre revideringen av chipprodukten. Om detta nummer ändras betyder det

programvara som används för den tidigare versionen av produkten är kompatibel med den nya produkten och det finns inget behov av att uppgradera programvaran.

programvara som används för den tidigare versionen av produkten är kompatibel med den nya produkten och det finns inget behov av att uppgradera programvaran.

vM.X-schemat ersätter tidigare använda chiprevisionsscheman, inklusive ECOx-nummer, Vxxx och andra format om sådana finns.

Chiprevisionen identifieras av:

- eFuse-fält EFUSE_RD_MAC_SPI_SYS_3_REG[23:22] och EFUSE_RD_MAC_SPI_SYS_3_REG[21:18]

Tabell 1: Chiprevisionsidentifiering med eFuse-bitar

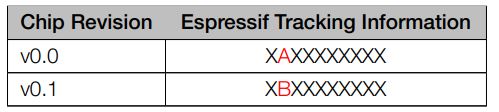

- Spårningsinformation för espressif linje i spånmärkning

Figur 1: Spånmarkeringsdiagram

Tabell 2: Chip Revision Identifiering genom Chip Markering

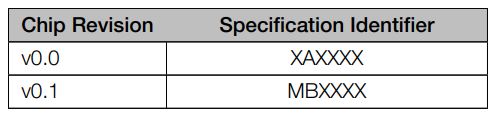

- Specifikationsidentifierare linje i modulmärkning

Figur 2: Modulmarkeringsdiagram

Tabell 3: Chiprevisionsidentifiering genom modulmärkning

Notera:

- Information om ESP-IDF-release som stöder en specifik chiprevision finns i Kompatibilitet mellan ESP-IDF-utgåvor och revisioner av Espressif SoCs.

- För mer information om chiprevisionsuppgraderingen och deras identifiering av produkter i ESP32-C6-serien, se ESP32-C6 Produkt-/processändringsmeddelanden (PCN).

- För mer information om numreringsschemat för chiprevision, se Kompatibilitetsrådgivning för Chip Revision Numbering Scheme.

2 Ytterligare metoder

Vissa fel i chipprodukten behöver inte åtgärdas på kiselnivå, eller med andra ord i en ny chiprevision.

I det här fallet kan chippet identifieras med datumkod i chipmärkning (se figur 1). För mer information,

se till Espressif Chip Packaging Information.

se till Espressif Chip Packaging Information.

Moduler byggda runt chippet kan identifieras med PW-nummer på produktetiketten (se figur 3). För mer information, se Espressif-modulförpackningsinformation.

Figur 3: Modulproduktetikett

Notera:

Observera det PW-nummer tillhandahålls endast för rullar förpackade i fuktspärrspåsar av aluminium (MBB).

Observera det PW-nummer tillhandahålls endast för rullar förpackade i fuktspärrspåsar av aluminium (MBB).

Errata Beskrivning

Tabell 4: Errata Sammanfattning

3 RISC-V CPU

3.1 Möjligt dödläge på grund av felaktig utförande av instruktioner vid skrivning till LP SRAM

Beskrivning

När HP CPU kör instruktioner (instruktion A och instruktion B successivt) i LP SRAM, och instruktion A och instruktion B råkar följa följande mönster:

- Instruktion A går ut på att skriva till minnet. Examples: sw/sh/sb

- Instruktion B involverar endast åtkomst till instruktionsbussen. Examples: nop/jal/jalr/lui/auipc

- Adressen för instruktion B är inte 4-byte justerad

Data som skrivs av instruktion A till minnet överförs endast efter att instruktion B har avslutat exekvering. Detta introducerar en risk där, efter att instruktion A skrivit till minnet, om en oändlig slinga exekveras i instruktion B, skrivningen av instruktion A aldrig kommer att slutföras.

lösningar

När du upplever detta problem, eller när du kontrollerar monteringskoden och ser det ovan nämnda mönstret,

- Lägg till en stängselinstruktion mellan instruktion A och den oändliga slingan. Detta kan uppnås genom att använda gränssnittet rv_utils_memory_barrier i ESP-IDF.

- Byt ut den oändliga slingan med instruktion wfi. Detta kan uppnås genom att använda rv_utils_wait_for_intr-gränssnittet i ESP-IDF.

- Inaktivera RV32C-tillägget (komprimerat) när du kompilerar kod som ska köras i LP SRAM för att undvika instruktioner utan 4-byte-justerade adresser.

Lösning

Ska fixas i framtida chiprevisioner.

Ska fixas i framtida chiprevisioner.

4 Klocka

4.1 Felaktig kalibrering av RC_FAST_CLK-klocka

Beskrivning

I ESP32-C6-chippet är frekvensen för RC_FAST_CLK-klockkällan för nära referensklockfrekvensen (40 MHz XTAL_CLK), vilket gör det omöjligt att kalibrera exakt. Detta kan påverka kringutrustning som använder RC_FAST_CLK och som har stränga krav på dess exakta klockfrekvens.

För kringutrustning som använder RC_FAST_CLK, se ESP32-C6 Teknisk referensmanual > Kapitel Återställning och klocka.

lösningar

Använd andra klockkällor istället för RC_FAST_CLK.

Använd andra klockkällor istället för RC_FAST_CLK.

Lösning

Fixat i chiprevision v0.1.

Fixat i chiprevision v0.1.

5 Återställ

5.1 Systemåterställning utlöst av RTC Watchdog Timer kan inte rapporteras korrekt

Beskrivning

När RTC Watchdog-timern (RWDT) utlöser en systemåterställning, kan återställningskällkoden inte låsas korrekt. Som ett resultat är den rapporterade återställningsorsaken obestämd och kan vara felaktig.

När RTC Watchdog-timern (RWDT) utlöser en systemåterställning, kan återställningskällkoden inte låsas korrekt. Som ett resultat är den rapporterade återställningsorsaken obestämd och kan vara felaktig.

lösningar

Ingen lösning.

Ingen lösning.

Lösning

Fixat i chiprevision v0.1.

Fixat i chiprevision v0.1.

6 RMT

6.1 Signalnivån för viloläge kan uppstå i RMT kontinuerligt sändningsläge

Beskrivning

I ESP32-C6:s RMT-modul, om det kontinuerliga TX-läget är aktiverat, förväntas det att dataöverföringen stannar efter att data har skickats för RMT_TX_LOOP_NUM_CHn rundor, och efter det bör signalnivån i viloläge styras av "nivån" slutmarkörens fält.

I ESP32-C6:s RMT-modul, om det kontinuerliga TX-läget är aktiverat, förväntas det att dataöverföringen stannar efter att data har skickats för RMT_TX_LOOP_NUM_CHn rundor, och efter det bör signalnivån i viloläge styras av "nivån" slutmarkörens fält.

Men i en verklig situation, efter att dataöverföringen stoppats, styrs inte kanalens vilolägessignalnivå av "nivå"-fältet på slutmarkören, utan av nivån i den tillbakadragna datan, som är obestämd.

lösningar

Användare föreslås att ställa in RMT_IDLE_OUT_EN_CHn till 1 för att endast använda register för att styra tomgångsnivån.

Det här problemet har förbigåtts sedan den första ESP-IDF-versionen som stöder kontinuerligt TX-läge (v5.1). I dessa versioner av ESP-IDF är det konfigurerat att tomgångsnivån endast kan styras av register.

Användare föreslås att ställa in RMT_IDLE_OUT_EN_CHn till 1 för att endast använda register för att styra tomgångsnivån.

Det här problemet har förbigåtts sedan den första ESP-IDF-versionen som stöder kontinuerligt TX-läge (v5.1). I dessa versioner av ESP-IDF är det konfigurerat att tomgångsnivån endast kan styras av register.

Lösning

Ingen fix planerad.

Ingen fix planerad.

7 WiFi

7.1 ESP32-C6 kan inte vara 802.11mc FTM-initiator

Beskrivning

Tiden för T3 (dvs. tiden för avgång av ACK från initiator) som används i 802.11mc Fine Time Measurement (FTM) kan inte erhållas korrekt, och som ett resultat av detta kan ESP32-C6 inte vara FTM-initiatorn.

Tiden för T3 (dvs. tiden för avgång av ACK från initiator) som används i 802.11mc Fine Time Measurement (FTM) kan inte erhållas korrekt, och som ett resultat av detta kan ESP32-C6 inte vara FTM-initiatorn.

lösningar

Ingen lösning.

Ingen lösning.

Lösning

Ska fixas i framtida chiprevisioner.

Ska fixas i framtida chiprevisioner.

Relaterad dokumentation

- Datablad i ESP32-C6-serien – Specifikationer för ESP32-C6-hårdvaran.

- ESP32-C6 teknisk referensmanual – Detaljerad information om hur du använder ESP32-C6-minnet och kringutrustning.

- ESP32-C6 Hardware Design Guidelines – Riktlinjer för hur du integrerar ESP32-C6 i din hårdvaruprodukt.

- Certifikat https://espressif.com/en/support/documents/certificates

- ESP32-C6 Produkt-/processändringsmeddelanden (PCN) https://espressif.com/en/support/documents/pcns?keys=ESP8684

- Dokumentationsuppdateringar och prenumeration på uppdateringsmeddelanden https://espressif.com/en/support/download/documents

Utvecklarzon

- ESP-IDF programmeringsguide för ESP32-C6 – Omfattande dokumentation för ESP-IDF utvecklingsramverk.

- ESP-IDF och andra utvecklingsramverk på GitHub.

https://github.com/espressif - ESP32 BBS Forum – Engineer-to-Engineer (E2E) Community för Espressif-produkter där du kan ställa frågor, dela kunskap, utforska idéer och hjälpa till att lösa problem med andra ingenjörer.

https://esp32.com/ - ESP Journal – Bästa metoder, artiklar och anteckningar från Espressif-folk.

https://blog.espressif.com/ - Se flikarna SDK:er och Demos, Appar, Verktyg, AT Firmware.

https://espressif.com/en/support/download/sdks-demos

Produkter

- ESP32-C6 Series SoCs – Bläddra igenom alla ESP32-C6 SoCs.

https://espressif.com/en/products/socs?id=ESP32-C6 - Moduler i ESP32-C6-serien – Bläddra igenom alla ESP32-C6-baserade moduler.

https://espressif.com/en/products/modules?id=ESP32-C6 - ESP32-C6 Series DevKits – Bläddra igenom alla ESP32-C6-baserade devkits.

https://espressif.com/en/products/devkits?id=ESP32-C6 - ESP Product Selector – Hitta en Espressif-hårdvaruprodukt som passar dina behov genom att jämföra eller använda filter.

https://products.espressif.com/#/product-selector?language=en

Kontakta oss

- Se flikarna Försäljningsfrågor, Tekniska förfrågningar, Kretsschema & PCB Design Review, Skaffa Samples

(onlinebutiker), bli vår leverantör, kommentarer och förslag.

https://espressif.com/en/contact-us/sales-questions

Revisionshistorik

Ansvarsfriskrivning och upphovsrättsmeddelande

Information i detta dokument, inklusive URL referenser, kan ändras utan föregående meddelande.

ALL TREDJE PARTS INFORMATION I DETTA DOKUMENT TILLHANDAHÅLLS I BEFINTLIGT SKICK UTAN GARANTIER FÖR DESS ÄKTHET OCH RIKTIGHET.

INGEN GARANTI TILLHANDAHÅLLS DETTA DOKUMENT FÖR SÄLJBARHET, Icke-intrång, LÄMPLIGHET FÖR NÅGOT SÄRSKILT ÄNDAMÅL, ELLER GÖR NÅGON GARANTI ANNAT SOM UPPSTÅR UR NÅGOT FÖRSLAG, SPECIFIKATIONER ELLERAMPLE.

Allt ansvar, inklusive ansvar för intrång i eventuella äganderätter, relaterat till användningen av informationen i detta dokument friskrivs. Inga licenser, uttryckliga eller underförstådda, genom estoppel eller på annat sätt, till några immateriella rättigheter beviljas häri.

Wi-Fi Alliance Members logotyp är ett varumärke som tillhör Wi-Fi Alliance. Bluetooth-logotypen är ett registrerat varumärke som tillhör Bluetooth SIG.

Alla varumärken, varumärken och registrerade varumärken som nämns i detta dokument tillhör sina respektive ägare och erkänns härmed.

Copyright © 2023 Espressif Systems (Shanghai) Co., Ltd. Med ensamrätt.

Information i detta dokument, inklusive URL referenser, kan ändras utan föregående meddelande.

ALL TREDJE PARTS INFORMATION I DETTA DOKUMENT TILLHANDAHÅLLS I BEFINTLIGT SKICK UTAN GARANTIER FÖR DESS ÄKTHET OCH RIKTIGHET.

INGEN GARANTI TILLHANDAHÅLLS DETTA DOKUMENT FÖR SÄLJBARHET, Icke-intrång, LÄMPLIGHET FÖR NÅGOT SÄRSKILT ÄNDAMÅL, ELLER GÖR NÅGON GARANTI ANNAT SOM UPPSTÅR UR NÅGOT FÖRSLAG, SPECIFIKATIONER ELLERAMPLE.

Allt ansvar, inklusive ansvar för intrång i eventuella äganderätter, relaterat till användningen av informationen i detta dokument friskrivs. Inga licenser, uttryckliga eller underförstådda, genom estoppel eller på annat sätt, till några immateriella rättigheter beviljas häri.

Wi-Fi Alliance Members logotyp är ett varumärke som tillhör Wi-Fi Alliance. Bluetooth-logotypen är ett registrerat varumärke som tillhör Bluetooth SIG.

Alla varumärken, varumärken och registrerade varumärken som nämns i detta dokument tillhör sina respektive ägare och erkänns härmed.

Copyright © 2023 Espressif Systems (Shanghai) Co., Ltd. Med ensamrätt.

Dokument/resurser

|

Espressif ESP32-C6 Series SoC Errata [pdf] Användarmanual ESP32-C6 Series SoC Errata, ESP32-C6 Series, SoC Errata, Errata |