SoC Espressif serie ESP32-C6 Manual de usuario de erratas

Introducción

Este documento describe erratas conocidas en la serie de SoC ESP32-C6.

Este documento describe erratas conocidas en la serie de SoC ESP32-C6.

Identificación de chips

Nota:

Consulte el enlace o el código QR para asegurarse de utilizar la última versión de este documento:

https://espressif.com/sites/default/files/documentation/esp32-c6_errata_en.pdf

Consulte el enlace o el código QR para asegurarse de utilizar la última versión de este documento:

https://espressif.com/sites/default/files/documentation/esp32-c6_errata_en.pdf

1 revisión de chips

Espressif está presentando vM.X Esquema de numeración para indicar revisiones de chips.

M – Número mayor, que indica la revisión mayor del producto de chip. Si este número cambia, significa que el software utilizado para la versión anterior del producto es incompatible con el nuevo producto y la versión del software deberá actualizarse para el uso del nuevo producto.

X – Número menor, que indica la revisión menor del producto chip. Si este número cambia, significa que

El software utilizado para la versión anterior del producto es compatible con el nuevo producto y no es necesario actualizar el software.

El software utilizado para la versión anterior del producto es compatible con el nuevo producto y no es necesario actualizar el software.

El esquema vM.X reemplaza los esquemas de revisión de chips utilizados anteriormente, incluidos los números ECOx, Vxxx y otros formatos, si los hubiera.

La revisión del chip se identifica por:

- Campo eFuse EFUSE_RD_MAC_SPI_SYS_3_REG[23:22] y EFUSE_RD_MAC_SPI_SYS_3_REG[21:18]

Tabla 1: Identificación de revisión del chip mediante bits eFuse

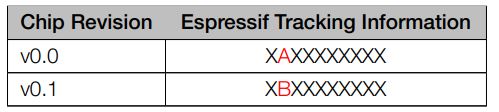

- Información de seguimiento de Espressif línea en marcado de chip

Figura 1: Diagrama de marcado de chips

Tabla 2: Identificación de la revisión del chip mediante marcado del chip

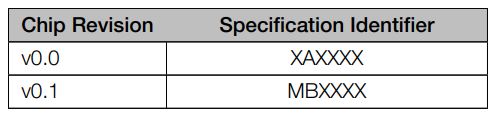

- Identificador de especificación línea en el marcado del módulo

Figura 2: Diagrama de marcado del módulo

Tabla 3: Identificación de revisión de chip por marca de módulo

Nota:

- La información sobre la versión ESP-IDF que admite una revisión de chip específica se proporciona en Compatibilidad entre versiones ESP-IDF y revisiones de SoC Espressif.

- Para obtener más información sobre la actualización de la revisión del chip y su identificación de los productos de la serie ESP32-C6, consulte ESP32-C6 Notificaciones de cambio de producto/proceso (PCN).

- Para obtener más información sobre el esquema de numeración de revisión del chip, consulte Aviso de compatibilidad para el esquema de numeración de revisiones de chips.

2 métodos adicionales

Algunos errores en el producto del chip no necesitan corregirse a nivel de silicio o, en otras palabras, en una nueva revisión del chip.

En este caso, el chip puede identificarse mediante el código de fecha en el marcado del chip (consulte la Figura 1). Para más información,

por favor refiérase a Información sobre el embalaje de chips Espressif.

por favor refiérase a Información sobre el embalaje de chips Espressif.

Los módulos construidos alrededor del chip pueden identificarse mediante el número PW en la etiqueta del producto (consulte la Figura 3). Para obtener más información, consulte Información de embalaje del módulo Espressif.

Figura 3: Etiqueta del producto del módulo

Nota:

Tenga en cuenta que Número de contraseña solo se proporciona para carretes empaquetados en bolsas de aluminio con barrera contra la humedad (MBB).

Tenga en cuenta que Número de contraseña solo se proporciona para carretes empaquetados en bolsas de aluminio con barrera contra la humedad (MBB).

Descripción de la fe de erratas

Tabla 4: Resumen de erratas

3 CPU RISC-V

3.1 Posible punto muerto debido a la ejecución desordenada de instrucciones cuando se trata de escribir en LP SRAM

Descripción

Cuando la CPU HP ejecuta instrucciones (instrucción A e instrucción B sucesivamente) en LP SRAM, la instrucción A y la instrucción B siguen los siguientes patrones:

- La instrucción A implica escribir en la memoria. Examparchivos: sw/sh/sb

- La instrucción B implica únicamente acceder al bus de instrucciones. Examparchivos: nop/jal/jalr/lui/auipc

- La dirección de la instrucción B no está alineada con 4 bytes

Los datos escritos por la instrucción A en la memoria solo se confirman después de que la instrucción B haya completado su ejecución. Esto introduce un riesgo de que, después de escribir la instrucción A en la memoria, si se ejecuta un bucle infinito en la instrucción B, la escritura de la instrucción A nunca se completará.

Soluciones provisionales

Cuando experimenta este problema, o cuando verifica el código ensamblador y ve el patrón mencionado anteriormente,

- Agregue una instrucción de valla entre la instrucción A y el bucle infinito. Esto se puede lograr utilizando la interfaz rv_utils_memory_barrier en ESP-IDF.

- Reemplace el bucle infinito con la instrucción wfi. Esto se puede lograr utilizando la interfaz rv_utils_wait_for_intr en ESP-IDF.

- Deshabilite la extensión RV32C (comprimida) al compilar código que se ejecutará en LP SRAM para evitar instrucciones con direcciones que no estén alineadas de 4 bytes.

Solución

Se solucionará en futuras revisiones del chip.

Se solucionará en futuras revisiones del chip.

4 Reloj

4.1 Calibración inexacta del reloj RC_FAST_CLK

Descripción

En el chip ESP32-C6, la frecuencia de la fuente de reloj RC_FAST_CLK está demasiado cerca de la frecuencia del reloj de referencia (40 MHz XTAL_CLK), lo que hace imposible una calibración precisa. Esto puede afectar a los periféricos que utilizan RC_FAST_CLK y tienen requisitos estrictos para su frecuencia de reloj precisa.

Para periféricos que utilizan RC_FAST_CLK, consulte el Manual de referencia técnica de ESP32-C6 > Capítulo Reinicio y reloj.

Soluciones provisionales

Utilice otras fuentes de reloj en lugar de RC_FAST_CLK.

Utilice otras fuentes de reloj en lugar de RC_FAST_CLK.

Solución

Corregido en la revisión del chip v0.1.

Corregido en la revisión del chip v0.1.

5 Restablecer

5.1 El reinicio del sistema activado por el temporizador de vigilancia RTC no se puede informar correctamente

Descripción

Cuando el temporizador de vigilancia RTC (RWDT) activa un reinicio del sistema, el código fuente de reinicio no se puede bloquear correctamente. Como resultado, la causa del reinicio informada es indeterminada y puede ser incorrecta.

Cuando el temporizador de vigilancia RTC (RWDT) activa un reinicio del sistema, el código fuente de reinicio no se puede bloquear correctamente. Como resultado, la causa del reinicio informada es indeterminada y puede ser incorrecta.

Soluciones provisionales

Sin solución.

Sin solución.

Solución

Corregido en la revisión del chip v0.1.

Corregido en la revisión del chip v0.1.

6 RMT

6.1 El nivel de señal de estado inactivo puede generar un error en el modo de transmisión continua RMT

Descripción

En el módulo RMT de ESP32-C6, si el modo TX continuo está habilitado, se espera que la transmisión de datos se detenga después de que los datos se envíen durante RMT_TX_LOOP_NUM_CHn rondas, y después de eso, el nivel de señal en estado inactivo debe ser controlado por el "nivel" campo del marcador final.

En el módulo RMT de ESP32-C6, si el modo TX continuo está habilitado, se espera que la transmisión de datos se detenga después de que los datos se envíen durante RMT_TX_LOOP_NUM_CHn rondas, y después de eso, el nivel de señal en estado inactivo debe ser controlado por el "nivel" campo del marcador final.

Sin embargo, en una situación real, después de que se detiene la transmisión de datos, el nivel de la señal del estado inactivo del canal no está controlado por el campo "nivel" del marcador final, sino por el nivel en los datos reenvueltos, que es indeterminado.

Soluciones provisionales

Se sugiere a los usuarios configurar RMT_IDLE_OUT_EN_CHn en 1 para usar solo registros para controlar el nivel inactivo.

Este problema se ha solucionado desde la primera versión de ESP-IDF que admite el modo TX continuo (v5.1). En estas versiones de ESP-IDF, está configurado que el nivel inactivo solo puede ser controlado por registros.

Se sugiere a los usuarios configurar RMT_IDLE_OUT_EN_CHn en 1 para usar solo registros para controlar el nivel inactivo.

Este problema se ha solucionado desde la primera versión de ESP-IDF que admite el modo TX continuo (v5.1). En estas versiones de ESP-IDF, está configurado que el nivel inactivo solo puede ser controlado por registros.

Solución

No hay ninguna solución programada.

No hay ninguna solución programada.

Wi-Fi 7

7.1 ESP32-C6 no puede ser el iniciador 802.11mc FTM

Descripción

La hora de T3 (es decir, la hora de salida del ACK del iniciador) utilizada en la medición precisa del tiempo (FTM) 802.11mc no se puede adquirir correctamente y, como resultado, ESP32-C6 no puede ser el iniciador de FTM.

La hora de T3 (es decir, la hora de salida del ACK del iniciador) utilizada en la medición precisa del tiempo (FTM) 802.11mc no se puede adquirir correctamente y, como resultado, ESP32-C6 no puede ser el iniciador de FTM.

Soluciones provisionales

Sin solución.

Sin solución.

Solución

Se solucionará en futuras revisiones del chip.

Se solucionará en futuras revisiones del chip.

Documentación relacionada

- Hoja de datos de la serie ESP32-C6: especificaciones del hardware ESP32-C6.

- Manual de referencia técnica del ESP32-C6: información detallada sobre cómo utilizar la memoria y los periféricos del ESP32-C6.

- Pautas de diseño de hardware ESP32-C6: pautas sobre cómo integrar el ESP32-C6 en su producto de hardware.

- Certificados https://espressif.com/en/support/documents/certificates

- ESP32-C6 Notificaciones de cambio de producto/proceso (PCN) https://espressif.com/en/support/documents/pcns?keys=ESP8684

- Actualizaciones de documentación y suscripción a notificaciones de actualizaciones https://espressif.com/en/support/download/documents

Zona de desarrolladores

- Guía de programación ESP-IDF para ESP32-C6: documentación extensa para el marco de desarrollo ESP-IDF.

- ESP-IDF y otros marcos de desarrollo en GitHub.

https://github.com/espressif - ESP32 BBS Forum: comunidad de ingeniero a ingeniero (E2E) para productos Espressif donde puede publicar preguntas, compartir conocimientos, explorar ideas y ayudar a resolver problemas con otros ingenieros.

https://esp32.com/ - The ESP Journal: mejores prácticas, artículos y notas de la gente de Espressif.

https://blog.espressif.com/ - Consulte las pestañas SDK y Demostraciones, Aplicaciones, Herramientas, Firmware AT.

https://espressif.com/en/support/download/sdks-demos

Productos

- SoC de la serie ESP32-C6: explore todos los SoC de ESP32-C6.

https://espressif.com/en/products/socs?id=ESP32-C6 - Módulos de la serie ESP32-C6: explore todos los módulos basados en ESP32-C6.

https://espressif.com/en/products/modules?id=ESP32-C6 - DevKits de la serie ESP32-C6: explore todos los devkits basados en ESP32-C6.

https://espressif.com/en/products/devkits?id=ESP32-C6 - Selector de productos ESP: encuentre un producto de hardware Espressif adecuado para sus necesidades comparando o aplicando filtros.

https://products.espressif.com/#/product-selector?language=en

Contáctenos

- Consulte las pestañas Preguntas de ventas, Consultas técnicas, Esquema del circuito y Diseño de PCB Review, ObtieneampLos

(Tiendas online), Conviértete en Nuestro Proveedor, Comentarios y Sugerencias.

https://espressif.com/en/contact-us/sales-questions

Historial de revisiones

Descargo de responsabilidad y aviso de derechos de autor

Información en este documento, incluyendo URL referencias, está sujeta a cambios sin previo aviso.

TODA LA INFORMACIÓN DE TERCEROS EN ESTE DOCUMENTO SE PROPORCIONA TAL CUAL SIN GARANTÍAS DE SU AUTENTICIDAD Y PRECISIÓN.

NO SE OTORGA NINGUNA GARANTÍA A ESTE DOCUMENTO POR SU COMERCIABILIDAD, NO VIOLACIÓN, IDONEIDAD PARA CUALQUIER FIN EN PARTICULAR, NI NINGUNA GARANTÍA QUE SURJA DE CUALQUIER PROPUESTA, ESPECIFICACIÓN O SAMPEL.

Se renuncia a toda responsabilidad, incluida la responsabilidad por la infracción de cualquier derecho de propiedad, relacionada con el uso de la información contenida en este documento. No se otorgan licencias expresas o implícitas, por impedimento o de otro modo, a ningún derecho de propiedad intelectual en este documento.

El logotipo de miembro de Wi-Fi Alliance es una marca comercial de Wi-Fi Alliance. El logotipo de Bluetooth es una marca registrada de Bluetooth SIG.

Todos los nombres comerciales, marcas comerciales y marcas comerciales registradas que se mencionan en este documento son propiedad de sus respectivos dueños y se reconocen aquí.

Copyright © 2023 Espressif Systems (Shanghai) Co., Ltd. Todos los derechos reservados.

Información en este documento, incluyendo URL referencias, está sujeta a cambios sin previo aviso.

TODA LA INFORMACIÓN DE TERCEROS EN ESTE DOCUMENTO SE PROPORCIONA TAL CUAL SIN GARANTÍAS DE SU AUTENTICIDAD Y PRECISIÓN.

NO SE OTORGA NINGUNA GARANTÍA A ESTE DOCUMENTO POR SU COMERCIABILIDAD, NO VIOLACIÓN, IDONEIDAD PARA CUALQUIER FIN EN PARTICULAR, NI NINGUNA GARANTÍA QUE SURJA DE CUALQUIER PROPUESTA, ESPECIFICACIÓN O SAMPEL.

Se renuncia a toda responsabilidad, incluida la responsabilidad por la infracción de cualquier derecho de propiedad, relacionada con el uso de la información contenida en este documento. No se otorgan licencias expresas o implícitas, por impedimento o de otro modo, a ningún derecho de propiedad intelectual en este documento.

El logotipo de miembro de Wi-Fi Alliance es una marca comercial de Wi-Fi Alliance. El logotipo de Bluetooth es una marca registrada de Bluetooth SIG.

Todos los nombres comerciales, marcas comerciales y marcas comerciales registradas que se mencionan en este documento son propiedad de sus respectivos dueños y se reconocen aquí.

Copyright © 2023 Espressif Systems (Shanghai) Co., Ltd. Todos los derechos reservados.

Documentos / Recursos

|

Erratas del SoC Espressif serie ESP32-C6 [pdf] Manual del usuario Erratas de SoC de la serie ESP32-C6, Serie ESP32-C6, Erratas de SoC, Erratas |