SoC da série Espressif ESP32-C6 Errata Manual do Usuário

Introdução

Este documento descreve erratas conhecidas na série de SoCs ESP32-C6.

Este documento descreve erratas conhecidas na série de SoCs ESP32-C6.

Identificação de Chip

Observação:

Verifique o link ou o código QR para ter certeza de que está usando a versão mais recente deste documento:

https://espressif.com/sites/default/files/documentation/esp32-c6_errata_en.pdf

Verifique o link ou o código QR para ter certeza de que está usando a versão mais recente deste documento:

https://espressif.com/sites/default/files/documentation/esp32-c6_errata_en.pdf

1 Revisão de Chip

Espressif está apresentando vM.X esquema de numeração para indicar revisões de chips.

M – Número principal, indicando a revisão principal do produto de chip. Se este número mudar, significa que o software usado para a versão anterior do produto é incompatível com o novo produto, e a versão do software deverá ser atualizada para uso do novo produto.

X – Número menor, indicando a pequena revisão do produto de chip. Se este número mudar, significa que o

o software usado para a versão anterior do produto é compatível com o novo produto e não há necessidade de atualizar o software.

o software usado para a versão anterior do produto é compatível com o novo produto e não há necessidade de atualizar o software.

O esquema vM.X substitui esquemas de revisão de chip usados anteriormente, incluindo números ECOx, Vxxx e outros formatos, se houver.

A revisão do chip é identificada por:

- Campo eFuse EFUSE_RD_MAC_SPI_SYS_3_REG[23:22] e EFUSE_RD_MAC_SPI_SYS_3_REG[21:18]

Tabela 1: Identificação de revisão de chip por eFuse Bits

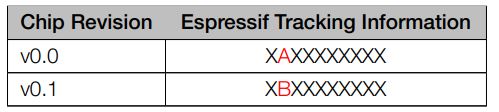

- Informações de rastreamento do Espressif linha na marcação de chips

Figura 1: Diagrama de marcação de cavacos

Tabela 2: Identificação de Revisão de Chip por Marcação de Chip

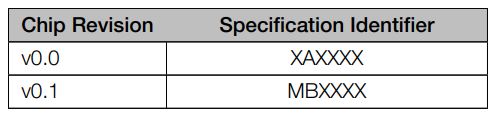

- Identificador de especificação linha na marcação do módulo

Figura 2: Diagrama de Marcação do Módulo

Tabela 3: Identificação de Revisão de Chip por Marcação de Módulo

Observação:

- Informações sobre o lançamento do ESP-IDF que suporta uma revisão específica do chip são fornecidas em Compatibilidade entre versões ESP-IDF e revisões de SoCs Espressif.

- Para obter mais informações sobre a atualização da revisão do chip e sua identificação dos produtos da série ESP32-C6, consulte Notificações de alteração de produto/processo ESP32-C6 (PCN).

- Para obter mais informações sobre o esquema de numeração de revisão de chip, consulte Aviso de compatibilidade para esquema de numeração de revisão de chip.

2 métodos adicionais

Alguns erros no produto do chip não precisam ser corrigidos no nível do silício ou, em outras palavras, em uma nova revisão do chip.

Neste caso, o chip poderá ser identificado pelo Código de Data na marcação do chip (ver Figura 1). Para maiores informações,

por favor consulte Informações de embalagem do chip Espressif.

por favor consulte Informações de embalagem do chip Espressif.

Os módulos construídos em torno do chip podem ser identificados pelo número PW na etiqueta do produto (veja a Figura 3). Para obter mais informações, consulte Informações de embalagem do módulo Espressif.

Figura 3: Etiqueta do Produto do Módulo

Observação:

Observe que Número de senha é fornecido apenas para bobinas embaladas em sacos de alumínio com barreira contra umidade (MBB).

Observe que Número de senha é fornecido apenas para bobinas embaladas em sacos de alumínio com barreira contra umidade (MBB).

Descrição da Errata

Tabela 4: Resumo da Errata

3CPU RISC-V

3.1 Possível deadlock devido à execução fora de ordem de instruções ao escrever em LP SRAM está envolvida

Descrição

Quando a CPU HP executa instruções (instrução A e instrução B sucessivamente) na SRAM LP, e a instrução A e a instrução B seguem os seguintes padrões:

- A instrução A envolve escrever na memória. Examparquivos: sw/sh/sb

- A instrução B envolve apenas acessar o barramento de instruções. Examparquivos: nop/jal/jalr/lui/auipc

- O endereço da instrução B não está alinhado com 4 bytes

Os dados gravados pela instrução A na memória só são confirmados após a instrução B ter concluído a execução. Isso introduz um risco onde, após a instrução A ser escrita na memória, se um loop infinito for executado na instrução B, a escrita da instrução A nunca será concluída.

soluções alternativas

Quando você enfrentar esse problema ou ao verificar o código assembly e ver o padrão mencionado acima,

- Adicione uma instrução fence entre a instrução A e o loop infinito. Isso pode ser conseguido usando a interface rv_utils_memory_barrier no ESP-IDF.

- Substitua o loop infinito pela instrução wfi. Isso pode ser conseguido usando a interface rv_utils_wait_for_intr no ESP-IDF.

- Desabilite a extensão RV32C (compactada) ao compilar código que será executado em LP SRAM para evitar instruções com endereços não alinhados a 4 bytes.

Solução

A ser corrigido nas futuras revisões do chip.

A ser corrigido nas futuras revisões do chip.

4 Relógio

4.1 Calibração imprecisa do relógio RC_FAST_CLK

Descrição

No chip ESP32-C6, a frequência da fonte do clock RC_FAST_CLK está muito próxima da frequência do clock de referência (40 MHz XTAL_CLK), impossibilitando uma calibração precisa. Isso pode afetar periféricos que usam RC_FAST_CLK e possuem requisitos rigorosos para sua frequência de clock precisa.

Para periféricos usando RC_FAST_CLK, consulte o Manual de Referência Técnica ESP32-C6 > Capítulo Reset e Relógio.

soluções alternativas

Use outras fontes de relógio em vez de RC_FAST_CLK.

Use outras fontes de relógio em vez de RC_FAST_CLK.

Solução

Corrigido na revisão do chip v0.1.

Corrigido na revisão do chip v0.1.

5 Reiniciar

5.1 A reinicialização do sistema acionada pelo temporizador Watchdog RTC não pode ser relatada corretamente

Descrição

Quando o temporizador watchdog RTC (RWDT) aciona uma reinicialização do sistema, o código-fonte da reinicialização não pode ser travado corretamente. Como resultado, a causa da reinicialização relatada é indeterminada e pode estar errada.

Quando o temporizador watchdog RTC (RWDT) aciona uma reinicialização do sistema, o código-fonte da reinicialização não pode ser travado corretamente. Como resultado, a causa da reinicialização relatada é indeterminada e pode estar errada.

soluções alternativas

Nenhuma solução alternativa.

Nenhuma solução alternativa.

Solução

Corrigido na revisão do chip v0.1.

Corrigido na revisão do chip v0.1.

6 TRM

6.1 O nível do sinal de estado inativo pode apresentar erro no modo TX contínuo RMT

Descrição

No módulo RMT do ESP32-C6, se o modo TX contínuo estiver habilitado, espera-se que a transmissão de dados pare após os dados serem enviados para rodadas RMT_TX_LOOP_NUM_CHn, e após isso, o nível do sinal em estado inativo deverá ser controlado pelo “nível” campo do marcador final.

No módulo RMT do ESP32-C6, se o modo TX contínuo estiver habilitado, espera-se que a transmissão de dados pare após os dados serem enviados para rodadas RMT_TX_LOOP_NUM_CHn, e após isso, o nível do sinal em estado inativo deverá ser controlado pelo “nível” campo do marcador final.

Porém, na situação real, após a interrupção da transmissão de dados, o nível do sinal de estado ocioso do canal não é controlado pelo campo “nível” do marcador final, mas pelo nível nos dados retornados, que é indeterminado.

soluções alternativas

Sugere-se que os usuários definam RMT_IDLE_OUT_EN_CHn como 1 para usar apenas registros para controlar o nível ocioso.

Este problema foi contornado desde a primeira versão do ESP-IDF que suporta o modo TX contínuo (v5.1). Nestas versões do ESP-IDF está configurado que o nível de inatividade só pode ser controlado por registradores.

Sugere-se que os usuários definam RMT_IDLE_OUT_EN_CHn como 1 para usar apenas registros para controlar o nível ocioso.

Este problema foi contornado desde a primeira versão do ESP-IDF que suporta o modo TX contínuo (v5.1). Nestas versões do ESP-IDF está configurado que o nível de inatividade só pode ser controlado por registradores.

Solução

Nenhuma correção agendada.

Nenhuma correção agendada.

7 Wi-Fi

7.1 ESP32-C6 não pode ser iniciador 802.11mc FTM

Descrição

O tempo de T3 (isto é, tempo de partida do ACK do Iniciador) usado na Medição de Tempo Fino (FTM) 802.11mc não pode ser adquirido corretamente e, como resultado, ESP32-C6 não pode ser o Iniciador FTM.

O tempo de T3 (isto é, tempo de partida do ACK do Iniciador) usado na Medição de Tempo Fino (FTM) 802.11mc não pode ser adquirido corretamente e, como resultado, ESP32-C6 não pode ser o Iniciador FTM.

soluções alternativas

Nenhuma solução alternativa.

Nenhuma solução alternativa.

Solução

A ser corrigido nas futuras revisões do chip.

A ser corrigido nas futuras revisões do chip.

Documentação relacionada

- Folha de dados da série ESP32-C6 – Especificações do hardware ESP32-C6.

- Manual de Referência Técnica ESP32-C6 – Informações detalhadas sobre como usar a memória e periféricos ESP32-C6.

- Diretrizes de design de hardware ESP32-C6 – Diretrizes sobre como integrar o ESP32-C6 em seu produto de hardware.

- Certificados https://espressif.com/en/support/documents/certificates

- Notificações de alteração de produto/processo ESP32-C6 (PCN) https://espressif.com/en/support/documents/pcns?keys=ESP8684

- Atualizações de documentação e assinatura de notificação de atualização https://espressif.com/en/support/download/documents

Zona do Desenvolvedor

- Guia de programação ESP-IDF para ESP32-C6 – Documentação extensa para a estrutura de desenvolvimento ESP-IDF.

- ESP-IDF e outros frameworks de desenvolvimento no GitHub.

https://github.com/espressif - ESP32 BBS Forum – Comunidade Engineer-to-Engineer (E2E) para produtos Espressif, onde você pode postar perguntas, compartilhar conhecimento, explorar ideias e ajudar a resolver problemas com colegas engenheiros.

https://esp32.com/ - The ESP Journal – Melhores práticas, artigos e notas do pessoal da Espressif.

https://blog.espressif.com/ - Veja as abas SDKs e Demos, Apps, Tools, AT Firmware.

https://espressif.com/en/support/download/sdks-demos

Produtos

- SoCs da série ESP32-C6 – Navegue por todos os SoCs ESP32-C6.

https://espressif.com/en/products/socs?id=ESP32-C6 - Módulos da série ESP32-C6 – Navegue por todos os módulos baseados em ESP32-C6.

https://espressif.com/en/products/modules?id=ESP32-C6 - DevKits da série ESP32-C6 – Navegue por todos os devkits baseados em ESP32-C6.

https://espressif.com/en/products/devkits?id=ESP32-C6 - Seletor de produtos ESP – Encontre um produto de hardware Espressif adequado às suas necessidades comparando ou aplicando filtros.

https://products.espressif.com/#/product-selector?language=en

Contate-nos

- Consulte as guias Perguntas sobre vendas, consultas técnicas, esquema de circuito e design de PCB Review, Obter Sampos

(Lojas online), Torne-se nosso fornecedor, comentários e sugestões.

https://espressif.com/en/contact-us/sales-questions

Histórico de revisão

Aviso de isenção de responsabilidade e direitos autorais

Informações neste documento, incluindo URL referências, está sujeito a alterações sem aviso prévio.

TODAS AS INFORMAÇÕES DE TERCEIROS NESTE DOCUMENTO SÃO FORNECIDAS NO ESTADO EM QUE SE ENCONTRAM, SEM GARANTIAS DE SUA AUTENTICIDADE E PRECISÃO.

NENHUMA GARANTIA É FORNECIDA A ESTE DOCUMENTO PARA SUA COMERCIABILIDADE, NÃO VIOLAÇÃO, ADEQUAÇÃO PARA QUALQUER FINALIDADE ESPECÍFICA, NEM QUALQUER GARANTIA DE OUTRA FORMA DECORRENTE DE QUALQUER PROPOSTA, ESPECIFICAÇÃO OU SAMPLE.

Todas as responsabilidades, incluindo responsabilidade por violação de quaisquer direitos de propriedade, relacionadas ao uso das informações contidas neste documento são isentas de responsabilidade. Nenhuma licença expressa ou implícita, por preclusão ou de outra forma, a quaisquer direitos de propriedade intelectual é concedida aqui.

O logotipo de membro da Wi-Fi Alliance é uma marca registrada da Wi-Fi Alliance. O logotipo Bluetooth é uma marca registrada da Bluetooth SIG.

Todos os nomes comerciais, marcas comerciais e marcas registradas mencionadas neste documento são de propriedade de seus respectivos proprietários e são aqui reconhecidas.

Copyright © 2023 Espressif Systems (Shanghai) Co., Ltd. Todos os direitos reservados.

Informações neste documento, incluindo URL referências, está sujeito a alterações sem aviso prévio.

TODAS AS INFORMAÇÕES DE TERCEIROS NESTE DOCUMENTO SÃO FORNECIDAS NO ESTADO EM QUE SE ENCONTRAM, SEM GARANTIAS DE SUA AUTENTICIDADE E PRECISÃO.

NENHUMA GARANTIA É FORNECIDA A ESTE DOCUMENTO PARA SUA COMERCIABILIDADE, NÃO VIOLAÇÃO, ADEQUAÇÃO PARA QUALQUER FINALIDADE ESPECÍFICA, NEM QUALQUER GARANTIA DE OUTRA FORMA DECORRENTE DE QUALQUER PROPOSTA, ESPECIFICAÇÃO OU SAMPLE.

Todas as responsabilidades, incluindo responsabilidade por violação de quaisquer direitos de propriedade, relacionadas ao uso das informações contidas neste documento são isentas de responsabilidade. Nenhuma licença expressa ou implícita, por preclusão ou de outra forma, a quaisquer direitos de propriedade intelectual é concedida aqui.

O logotipo de membro da Wi-Fi Alliance é uma marca registrada da Wi-Fi Alliance. O logotipo Bluetooth é uma marca registrada da Bluetooth SIG.

Todos os nomes comerciais, marcas comerciais e marcas registradas mencionadas neste documento são de propriedade de seus respectivos proprietários e são aqui reconhecidas.

Copyright © 2023 Espressif Systems (Shanghai) Co., Ltd. Todos os direitos reservados.

Documentos / Recursos

|

Errata de SoC da série Espressif ESP32-C6 [pdf] Manual do Usuário Errata SoC Série ESP32-C6, Série ESP32-C6, Errata SoC, Errata |