Układ SoC Espressif ESP32-C6 Series Instrukcja obsługi Errata

Wstęp

W dokumencie tym opisano znane błędy w układach SoC serii ESP32-C6.

W dokumencie tym opisano znane błędy w układach SoC serii ESP32-C6.

Identyfikacja chipa

Notatka:

Sprawdź link lub kod QR, aby upewnić się, że korzystasz z najnowszej wersji tego dokumentu:

https://espressif.com/sites/default/files/documentation/esp32-c6_errata_en.pdf

Sprawdź link lub kod QR, aby upewnić się, że korzystasz z najnowszej wersji tego dokumentu:

https://espressif.com/sites/default/files/documentation/esp32-c6_errata_en.pdf

1 Rewizja układu scalonego

Espressif wprowadza vM.X schemat numeracji określający wersje układów scalonych.

M – Numer główny, wskazujący na główną rewizję produktu chipowego. Jeśli ten numer ulegnie zmianie, oznacza to, że oprogramowanie używane w poprzedniej wersji produktu jest niezgodne z nowym produktem, a wersja oprogramowania musi zostać zaktualizowana do użytku z nowym produktem.

X – Numer drugorzędny, wskazujący na drobną rewizję produktu chipowego. Jeśli ten numer ulega zmianie, oznacza to, że

oprogramowanie używane w poprzedniej wersji produktu jest kompatybilne z nowym produktem i nie ma potrzeby aktualizacji oprogramowania.

oprogramowanie używane w poprzedniej wersji produktu jest kompatybilne z nowym produktem i nie ma potrzeby aktualizacji oprogramowania.

Schemat vM.X zastępuje poprzednio używane schematy rewizji układów scalonych, obejmujące numery ECOx, Vxxx i inne formaty, jeśli takie istnieją.

Rewizję układu scalonego identyfikuje się poprzez:

- Pole eFuse EFUSE_RD_MAC_SPI_SYS_3_REG[23:22] i EFUSE_RD_MAC_SPI_SYS_3_REG[21:18]

Tabela 1: Identyfikacja wersji układu scalonego za pomocą bitów eFuse

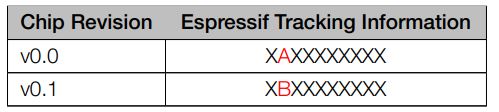

- Informacje o śledzeniu Espressif linia w znakowaniu chipów

Rysunek 1: Schemat znakowania chipów

Tabela 2: Identyfikacja rewizji układu scalonego za pomocą oznaczenia układu scalonego

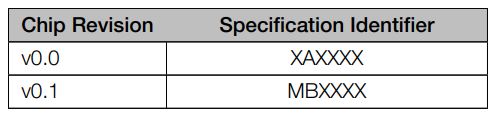

- Identyfikator specyfikacji linia w oznakowaniu modułu

Rysunek 2: Schemat oznaczania modułów

Tabela 3: Identyfikacja rewizji układu scalonego według oznaczenia modułu

Notatka:

- Informacje o wydaniu ESP-IDF obsługującym konkretną wersję układu scalonego znajdują się w Zgodność między wersjami ESP-IDF i rewizjami układów SoC Espressif.

- Aby uzyskać więcej informacji na temat aktualizacji wersji układu scalonego i ich identyfikacji w produktach serii ESP32-C6, zapoznaj się z ESP32-C6 Powiadomienia o zmianach produktu/procesu (PCN).

- Aby uzyskać więcej informacji na temat schematu numerowania wersji układów scalonych, zobacz Porady dotyczące zgodności dla schematu numeracji rewizji układów scalonych.

2 Dodatkowe metody

Niektóre błędy w układzie scalonym nie muszą być naprawiane na poziomie układu scalonego, czyli innymi słowy w nowej wersji układu scalonego.

W tym przypadku chip można zidentyfikować za pomocą kodu daty w oznaczeniu chipa (patrz rysunek 1). Aby uzyskać więcej informacji,

należy zapoznać się Informacje o opakowaniu Espressif Chip.

należy zapoznać się Informacje o opakowaniu Espressif Chip.

Moduły zbudowane wokół układu scalonego można zidentyfikować po numerze PW na etykiecie produktu (patrz rysunek 3). Aby uzyskać więcej informacji, zapoznaj się z Informacje o opakowaniu modułu Espressif.

Rysunek 3: Etykieta produktu modułu

Notatka:

Proszę pamiętać, że Numer PW jest przeznaczony wyłącznie do szpul pakowanych w aluminiowe worki barierowe chroniące przed wilgocią (MBB).

Proszę pamiętać, że Numer PW jest przeznaczony wyłącznie do szpul pakowanych w aluminiowe worki barierowe chroniące przed wilgocią (MBB).

Opis erraty

Tabela 4: Podsumowanie erraty

3 procesory RISC-V

3.1 Możliwe jest zablokowanie z powodu nieprawidłowego wykonywania instrukcji podczas zapisywania do pamięci LP SRAM

Opis

Gdy procesor HP wykonuje instrukcje (kolejno instrukcję A i instrukcję B) w pamięci LP SRAM, instrukcja A i instrukcja B podążają za następującymi wzorcami:

- Instrukcja A obejmuje pisanie do pamięci.amples: sw/sh/sb

- Instrukcja B obejmuje jedynie dostęp do magistrali instrukcji. Np.amples: nop/jal/jalr/lui/auipc

- Adres instrukcji B nie jest wyrównany do 4 bajtów

Dane zapisane przez instrukcję A do pamięci są zatwierdzane dopiero po zakończeniu wykonywania instrukcji B. Wprowadza to ryzyko, że po zapisaniu instrukcji A do pamięci, jeśli nieskończona pętla zostanie wykonana w instrukcji B, zapis instrukcji A nigdy się nie zakończy.

Obejścia

Jeśli napotkasz ten problem lub sprawdzisz kod języka assembly i zobaczysz powyższy wzorzec,

- Dodaj instrukcję ogrodzenia między instrukcją A a pętlą nieskończoną. Można to osiągnąć, używając interfejsu rv_utils_memory_barrier w ESP-IDF.

- Zastąp nieskończoną pętlę instrukcją wfi. Można to osiągnąć, używając interfejsu rv_utils_wait_for_intr w ESP-IDF.

- Wyłącz rozszerzenie RV32C (skompresowane) podczas kompilacji kodu, który ma zostać wykonany w pamięci LP SRAM, aby uniknąć instrukcji z adresami niespójnymi 4-bajtowo.

Rozwiązanie

Zostanie to naprawione w przyszłych wersjach układu scalonego.

Zostanie to naprawione w przyszłych wersjach układu scalonego.

4 Zegar

4.1 Niedokładna kalibracja zegara RC_FAST_CLK

Opis

W układzie ESP32-C6 częstotliwość źródła zegara RC_FAST_CLK jest zbyt bliska częstotliwości zegara referencyjnego (40 MHz XTAL_CLK), co uniemożliwia dokładną kalibrację. Może to mieć wpływ na urządzenia peryferyjne, które używają RC_FAST_CLK i mają rygorystyczne wymagania dotyczące jego dokładnej częstotliwości zegara.

W przypadku urządzeń peryferyjnych wykorzystujących RC_FAST_CLK zapoznaj się z podręcznikiem technicznym ESP32-C6 > Rozdział Resetowanie i zegar.

Obejścia

Użyj innych źródeł zegara zamiast RC_FAST_CLK.

Użyj innych źródeł zegara zamiast RC_FAST_CLK.

Rozwiązanie

Naprawiono w wersji układu v0.1.

Naprawiono w wersji układu v0.1.

5 Resetuj

5.1 Reset systemu wywołany przez zegar RTC Watchdog nie może zostać poprawnie zgłoszony

Opis

Gdy zegar RTC watchdog (RWDT) wyzwala reset systemu, kod źródłowy resetu nie może zostać poprawnie zablokowany. W rezultacie zgłoszona przyczyna resetu jest nieokreślona i może być błędna.

Gdy zegar RTC watchdog (RWDT) wyzwala reset systemu, kod źródłowy resetu nie może zostać poprawnie zablokowany. W rezultacie zgłoszona przyczyna resetu jest nieokreślona i może być błędna.

Obejścia

Brak obejścia.

Brak obejścia.

Rozwiązanie

Naprawiono w wersji układu v0.1.

Naprawiono w wersji układu v0.1.

6 godz.

6.1 Poziom sygnału w stanie bezczynności może być błędny w trybie ciągłego nadawania RMT

Opis

W module RMT układu ESP32-C6, jeśli włączony jest tryb ciągłego TX, oczekuje się, że transmisja danych zatrzyma się po przesłaniu danych przez liczbę rund RMT_TX_LOOP_NUM_CHn, a następnie poziom sygnału w stanie bezczynności powinien być kontrolowany przez pole „level” znacznika końcowego.

W module RMT układu ESP32-C6, jeśli włączony jest tryb ciągłego TX, oczekuje się, że transmisja danych zatrzyma się po przesłaniu danych przez liczbę rund RMT_TX_LOOP_NUM_CHn, a następnie poziom sygnału w stanie bezczynności powinien być kontrolowany przez pole „level” znacznika końcowego.

Jednak w rzeczywistej sytuacji, po zatrzymaniu transmisji danych, poziom sygnału stanu bezczynności kanału nie jest kontrolowany przez pole „poziomu” znacznika końcowego, lecz przez poziom w zawiniętych danych, który jest nieokreślony.

Obejścia

Użytkownikom zaleca się ustawienie parametru RMT_IDLE_OUT_EN_CHn na 1, aby do kontrolowania poziomu bezczynności używać wyłącznie rejestrów.

Ten problem został pominięty od pierwszej wersji ESP-IDF obsługującej tryb ciągłego TX (v5.1). W tych wersjach ESP-IDF skonfigurowano tak, że poziom bezczynności może być kontrolowany tylko przez rejestry.

Użytkownikom zaleca się ustawienie parametru RMT_IDLE_OUT_EN_CHn na 1, aby do kontrolowania poziomu bezczynności używać wyłącznie rejestrów.

Ten problem został pominięty od pierwszej wersji ESP-IDF obsługującej tryb ciągłego TX (v5.1). W tych wersjach ESP-IDF skonfigurowano tak, że poziom bezczynności może być kontrolowany tylko przez rejestry.

Rozwiązanie

Nie zaplanowano naprawy.

Nie zaplanowano naprawy.

Wi-Fi 7

7.1 ESP32-C6 nie może być inicjatorem 802.11mc FTM

Opis

Czas T3 (tj. czas wyjścia ACK z inicjatora) używany w pomiarze czasu dokładnego (FTM) 802.11mc nie może zostać prawidłowo pozyskany i w rezultacie układ ESP32-C6 nie może być inicjatorem FTM.

Czas T3 (tj. czas wyjścia ACK z inicjatora) używany w pomiarze czasu dokładnego (FTM) 802.11mc nie może zostać prawidłowo pozyskany i w rezultacie układ ESP32-C6 nie może być inicjatorem FTM.

Obejścia

Brak obejścia.

Brak obejścia.

Rozwiązanie

Zostanie to naprawione w przyszłych wersjach układu scalonego.

Zostanie to naprawione w przyszłych wersjach układu scalonego.

Powiązana dokumentacja

- Karta katalogowa serii ESP32-C6 – Specyfikacje sprzętu ESP32-C6.

- Instrukcja techniczna ESP32-C6 – szczegółowe informacje na temat korzystania z pamięci i urządzeń peryferyjnych ESP32-C6.

- Wytyczne dotyczące projektowania sprzętu ESP32-C6 – Wytyczne dotyczące sposobu integracji ESP32-C6 z produktem sprzętowym.

- Certyfikaty https://espressif.com/en/support/documents/certificates

- ESP32-C6 Powiadomienia o zmianach produktu/procesu (PCN) https://espressif.com/en/support/documents/pcns?keys=ESP8684

- Aktualizacje dokumentacji i subskrypcja powiadomień o aktualizacjach https://espressif.com/en/support/download/documents

Strefa programisty

- Przewodnik programowania ESP-IDF dla ESP32-C6 – obszerna dokumentacja dotycząca środowiska programistycznego ESP-IDF.

- ESP-IDF i inne frameworki programistyczne na GitHub.

https://github.com/espressif - ESP32 BBS Forum — społeczność inżynierów dla inżynierów (E2E) dla produktów Espressif, w której można publikować pytania, dzielić się wiedzą, badać pomysły i pomagać w rozwiązywaniu problemów z innymi inżynierami.

https://esp32.com/ - The ESP Journal – najlepsze praktyki, artykuły i notatki od ludzi Espressif.

https://blog.espressif.com/ - Zobacz zakładki SDK i wersje demonstracyjne, Aplikacje, Narzędzia, Oprogramowanie sprzętowe AT.

https://espressif.com/en/support/download/sdks-demos

Produkty

- Układy SoC serii ESP32-C6 — przeglądaj wszystkie układy SoC ESP32-C6.

https://espressif.com/en/products/socs?id=ESP32-C6 - Moduły serii ESP32-C6 — przeglądaj wszystkie moduły oparte na ESP32-C6.

https://espressif.com/en/products/modules?id=ESP32-C6 - Zestawy deweloperskie serii ESP32-C6 — przeglądaj wszystkie zestawy deweloperskie oparte na ESP32-C6.

https://espressif.com/en/products/devkits?id=ESP32-C6 - Selektor produktów ESP — Znajdź produkt sprzętowy Espressif odpowiedni dla Twoich potrzeb, porównując lub stosując filtry.

https://products.espressif.com/#/product-selector?language=en

Skontaktuj się z nami

- Zobacz zakładki Pytania dotyczące sprzedaży, Zapytania techniczne, Schemat obwodów i Projektowanie PCB Review, Pobierz Samples

(Sklepy internetowe), Zostań naszym dostawcą, Komentarze i sugestie.

https://espressif.com/en/contact-us/sales-questions

Historia rewizji

Zastrzeżenie i informacja o prawach autorskich

Informacje zawarte w tym dokumencie, w tym URL referencje mogą ulec zmianie bez powiadomienia.

WSZYSTKIE INFORMACJE STRON TRZECICH W NINIEJSZYM DOKUMENCIE SĄ DOSTARCZANE BEZ GWARANCJI CO DO ICH AUTENTYCZNOŚCI I DOKŁADNOŚCI.

NA NINIEJSZY DOKUMENT NIE UDZIELA SIĘ ŻADNEJ GWARANCJI PRZYDATNOŚCI HANDLOWEJ, NIENARUSZALNOŚCI PRAW I PRZYDATNOŚCI DO JAKIEGOKOLWIEK OKREŚLONEGO CELU ANI ŻADNEJ GWARANCJI WYNIKAJĄCEJ W INNY SPOSÓB Z JAKICHKOLWIEK PROPOZYCJI, SPECYFIKACJI LUB SPECYFIKACJIAMPLE.

Wyklucza się wszelką odpowiedzialność, w tym odpowiedzialność za naruszenie jakichkolwiek praw własności, związanych z wykorzystaniem informacji zawartych w tym dokumencie. W niniejszym dokumencie nie udziela się żadnych licencji wyraźnych ani dorozumianych, przez estoppel lub w inny sposób, na jakiekolwiek prawa własności intelektualnej.

Logo Wi-Fi Alliance Member jest znakiem towarowym Wi-Fi Alliance. Logo Bluetooth jest zastrzeżonym znakiem towarowym firmy Bluetooth SIG.

Wszystkie nazwy handlowe, znaki towarowe i zarejestrowane znaki towarowe wymienione w tym dokumencie są własnością ich odpowiednich właścicieli i zostają niniejszym potwierdzone.

Copyright © 2023 Espressif Systems (Shanghai) Co., Ltd. Wszelkie prawa zastrzeżone.

Informacje zawarte w tym dokumencie, w tym URL referencje mogą ulec zmianie bez powiadomienia.

WSZYSTKIE INFORMACJE STRON TRZECICH W NINIEJSZYM DOKUMENCIE SĄ DOSTARCZANE BEZ GWARANCJI CO DO ICH AUTENTYCZNOŚCI I DOKŁADNOŚCI.

NA NINIEJSZY DOKUMENT NIE UDZIELA SIĘ ŻADNEJ GWARANCJI PRZYDATNOŚCI HANDLOWEJ, NIENARUSZALNOŚCI PRAW I PRZYDATNOŚCI DO JAKIEGOKOLWIEK OKREŚLONEGO CELU ANI ŻADNEJ GWARANCJI WYNIKAJĄCEJ W INNY SPOSÓB Z JAKICHKOLWIEK PROPOZYCJI, SPECYFIKACJI LUB SPECYFIKACJIAMPLE.

Wyklucza się wszelką odpowiedzialność, w tym odpowiedzialność za naruszenie jakichkolwiek praw własności, związanych z wykorzystaniem informacji zawartych w tym dokumencie. W niniejszym dokumencie nie udziela się żadnych licencji wyraźnych ani dorozumianych, przez estoppel lub w inny sposób, na jakiekolwiek prawa własności intelektualnej.

Logo Wi-Fi Alliance Member jest znakiem towarowym Wi-Fi Alliance. Logo Bluetooth jest zastrzeżonym znakiem towarowym firmy Bluetooth SIG.

Wszystkie nazwy handlowe, znaki towarowe i zarejestrowane znaki towarowe wymienione w tym dokumencie są własnością ich odpowiednich właścicieli i zostają niniejszym potwierdzone.

Copyright © 2023 Espressif Systems (Shanghai) Co., Ltd. Wszelkie prawa zastrzeżone.

Dokumenty / Zasoby

|

Espressif ESP32-C6 Series SoC Errata [plik PDF] Instrukcja obsługi Seria ESP32-C6 SoC Errata, Seria ESP32-C6, SoC Errata, Errata |