SoC Espressif série ESP32-C6 Manuel d'utilisation des erratas

Introduction

Ce document décrit les errata connus dans la série ESP32-C6 de SoC.

Ce document décrit les errata connus dans la série ESP32-C6 de SoC.

Identification de la puce

Note:

Vérifiez le lien ou le code QR pour vous assurer que vous utilisez la dernière version de ce document :

https://espressif.com/sites/default/files/documentation/esp32-c6_errata_en.pdf

Vérifiez le lien ou le code QR pour vous assurer que vous utilisez la dernière version de ce document :

https://espressif.com/sites/default/files/documentation/esp32-c6_errata_en.pdf

1 révision de la puce

Espressif présente vM.X schéma de numérotation pour indiquer les révisions des puces.

M – Numéro majeur, indiquant la révision majeure du produit à puce. Si ce numéro change, cela signifie que le logiciel utilisé pour la version précédente du produit est incompatible avec le nouveau produit et que la version du logiciel doit être mise à niveau pour l'utilisation du nouveau produit.

X – Numéro mineur, indiquant la révision mineure du produit à puce. Si ce numéro change, cela signifie que

le logiciel utilisé pour la version précédente du produit est compatible avec le nouveau produit et il n'est pas nécessaire de mettre à niveau le logiciel.

le logiciel utilisé pour la version précédente du produit est compatible avec le nouveau produit et il n'est pas nécessaire de mettre à niveau le logiciel.

Le schéma vM.X remplace les schémas de révision de puces précédemment utilisés, y compris les numéros ECOx, Vxxx et d'autres formats, le cas échéant.

La révision de la puce est identifiée par :

- Champ eFuse EFUSE_RD_MAC_SPI_SYS_3_REG[23:22] et EFUSE_RD_MAC_SPI_SYS_3_REG[21:18]

Tableau 1 : Identification de la révision de la puce par bits eFuse

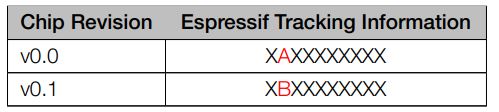

- Informations de suivi Espressif ligne dans le marquage des puces

Figure 1 : Diagramme de marquage des puces

Tableau 2 : Identification de la révision de la puce par marquage de la puce

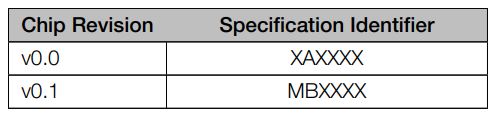

- Identificateur de spécification ligne dans le marquage du module

Figure 2 : Diagramme de marquage des modules

Tableau 3 : Identification de la révision de la puce par marquage du module

Note:

- Des informations sur la version ESP-IDF prenant en charge une révision de puce spécifique sont fournies dans Compatibilité entre les versions ESP-IDF et les révisions des SoC Espressif.

- Pour plus d'informations sur la mise à niveau de la révision de la puce et leur identification des produits de la série ESP32-C6, veuillez vous référer à ESP32-C6 Notifications de modification de produit/processus (PCN).

- Pour plus d'informations sur le schéma de numérotation des révisions des puces, voir Avis de compatibilité pour le système de numérotation des révisions de puces.

2 méthodes supplémentaires

Certaines erreurs dans le produit de la puce n'ont pas besoin d'être corrigées au niveau du silicium, ou en d'autres termes lors d'une nouvelle révision de la puce.

Dans ce cas, la puce peut être identifiée par le code de date dans le marquage de la puce (voir Figure 1). Pour plus d'informations,

prière de se référer à Informations sur l'emballage des chips Espressif.

prière de se référer à Informations sur l'emballage des chips Espressif.

Les modules construits autour de la puce peuvent être identifiés par le numéro PW sur l'étiquette du produit (voir Figure 3). Pour plus d'informations, veuillez vous référer à Informations sur l'emballage du module Espressif.

Figure 3 : Étiquette du produit du module

Note:

Veuillez noter que Numéro de mot de passe n’est prévu que pour les bobines conditionnées dans des sacs en aluminium avec barrière contre l’humidité (MBB).

Veuillez noter que Numéro de mot de passe n’est prévu que pour les bobines conditionnées dans des sacs en aluminium avec barrière contre l’humidité (MBB).

Description des errata

Tableau 4 : Résumé des erratas

3 processeurs RISC-V

3.1 Possibilité de blocage en raison d'une exécution dans le désordre des instructions lors de l'écriture sur LP SRAM

Description

Lorsque le processeur HP exécute des instructions (instruction A et instruction B successivement) dans LP SRAM, et que l'instruction A et l'instruction B suivent les modèles suivants :

- L’instruction A consiste à écrire en mémoire. Examples : sw/sh/sb

- L’instruction B implique uniquement l’accès au bus d’instructions. Exampfichiers : nop/jal/jalr/lui/auipc

- L'adresse de l'instruction B n'est pas alignée sur 4 octets

Les données écrites par l'instruction A en mémoire ne sont validées qu'une fois l'exécution de l'instruction B terminée. Cela introduit un risque où, après l'écriture de l'instruction A en mémoire, si une boucle infinie est exécutée dans l'instruction B, l'écriture de l'instruction A ne se terminera jamais.

Solutions de contournement

Lorsque vous rencontrez ce problème, ou lorsque vous vérifiez le code assembleur et voyez le modèle mentionné ci-dessus,

- Ajoutez une instruction de clôture entre l'instruction A et la boucle infinie. Ceci peut être réalisé en utilisant l'interface rv_utils_memory_barrier dans ESP-IDF.

- Remplacez la boucle infinie par l'instruction wfi. Ceci peut être réalisé en utilisant l'interface rv_utils_wait_for_intr dans ESP-IDF.

- Désactivez l'extension RV32C (compressée) lors de la compilation du code à exécuter dans LP SRAM pour éviter les instructions dont les adresses ne sont pas alignées sur 4 octets.

Solution

À corriger dans les futures révisions de la puce.

À corriger dans les futures révisions de la puce.

4 Horloge

4.1 Calibrage inexact de l'horloge RC_FAST_CLK

Description

Dans la puce ESP32-C6, la fréquence de la source d'horloge RC_FAST_CLK est trop proche de la fréquence de l'horloge de référence (40 MHz XTAL_CLK), ce qui rend impossible un calibrage précis. Cela peut affecter les périphériques qui utilisent RC_FAST_CLK et qui ont des exigences strictes concernant leur fréquence d'horloge précise.

Pour les périphériques utilisant RC_FAST_CLK, veuillez vous référer au Manuel de référence technique ESP32-C6 > Chapitre Réinitialisation et horloge.

Solutions de contournement

Utilisez d'autres sources d'horloge au lieu de RC_FAST_CLK.

Utilisez d'autres sources d'horloge au lieu de RC_FAST_CLK.

Solution

Corrigé dans la révision de la puce v0.1.

Corrigé dans la révision de la puce v0.1.

5 Réinitialiser

5.1 La réinitialisation du système déclenchée par la minuterie de surveillance RTC ne peut pas être correctement signalée

Description

Lorsque le minuteur de surveillance RTC (RWDT) déclenche une réinitialisation du système, le code source de réinitialisation ne peut pas être verrouillé correctement. Par conséquent, la cause de la réinitialisation signalée est indéterminée et peut être erronée.

Lorsque le minuteur de surveillance RTC (RWDT) déclenche une réinitialisation du système, le code source de réinitialisation ne peut pas être verrouillé correctement. Par conséquent, la cause de la réinitialisation signalée est indéterminée et peut être erronée.

Solutions de contournement

Aucune solution de contournement.

Aucune solution de contournement.

Solution

Corrigé dans la révision de la puce v0.1.

Corrigé dans la révision de la puce v0.1.

6 RMT

6.1 Le niveau du signal à l'état inactif peut présenter une erreur en mode TX continu RMT

Description

Dans le module RMT de l'ESP32-C6, si le mode TX continu est activé, il est prévu que la transmission des données s'arrête après l'envoi des données pendant RMT_TX_LOOP_NUM_CHn tours, et après cela, le niveau du signal en état de veille doit être contrôlé par le « niveau » champ du marqueur de fin.

Dans le module RMT de l'ESP32-C6, si le mode TX continu est activé, il est prévu que la transmission des données s'arrête après l'envoi des données pendant RMT_TX_LOOP_NUM_CHn tours, et après cela, le niveau du signal en état de veille doit être contrôlé par le « niveau » champ du marqueur de fin.

Cependant, en situation réelle, après l'arrêt de la transmission des données, le niveau du signal à l'état inactif du canal n'est pas contrôlé par le champ « niveau » du marqueur de fin, mais par le niveau dans les données renvoyées, qui est indéterminé.

Solutions de contournement

Il est suggéré aux utilisateurs de définir RMT_IDLE_OUT_EN_CHn sur 1 pour utiliser uniquement les registres pour contrôler le niveau d'inactivité.

Ce problème a été contourné depuis la première version d'ESP-IDF prenant en charge le mode TX continu (v5.1). Dans ces versions d'ESP-IDF, il est configuré que le niveau d'inactivité ne peut être contrôlé que par des registres.

Il est suggéré aux utilisateurs de définir RMT_IDLE_OUT_EN_CHn sur 1 pour utiliser uniquement les registres pour contrôler le niveau d'inactivité.

Ce problème a été contourné depuis la première version d'ESP-IDF prenant en charge le mode TX continu (v5.1). Dans ces versions d'ESP-IDF, il est configuré que le niveau d'inactivité ne peut être contrôlé que par des registres.

Solution

Aucun correctif prévu.

Aucun correctif prévu.

7 Wi-Fi

7.1 ESP32-C6 ne peut pas être un initiateur 802.11mc FTM

Description

L'heure de T3 (c'est-à-dire l'heure de départ de l'ACK de l'initiateur) utilisée dans la mesure du temps fin (FTM) 802.11mc ne peut pas être acquise correctement et, par conséquent, l'ESP32-C6 ne peut pas être l'initiateur FTM.

L'heure de T3 (c'est-à-dire l'heure de départ de l'ACK de l'initiateur) utilisée dans la mesure du temps fin (FTM) 802.11mc ne peut pas être acquise correctement et, par conséquent, l'ESP32-C6 ne peut pas être l'initiateur FTM.

Solutions de contournement

Aucune solution de contournement.

Aucune solution de contournement.

Solution

À corriger dans les futures révisions de la puce.

À corriger dans les futures révisions de la puce.

Documentation connexe

- Fiche technique de la série ESP32-C6 – Spécifications du matériel ESP32-C6.

- Manuel de référence technique ESP32-C6 – Informations détaillées sur l'utilisation de la mémoire et des périphériques ESP32-C6.

- Directives de conception matérielle ESP32-C6 – Directives sur la façon d'intégrer l'ESP32-C6 dans votre produit matériel.

- Certificats https://espressif.com/en/support/documents/certificates

- ESP32-C6 Notifications de modification de produit/processus (PCN) https://espressif.com/en/support/documents/pcns?keys=ESP8684

- Mises à jour de la documentation et abonnement aux notifications de mise à jour https://espressif.com/en/support/download/documents

Zone des développeurs

- Guide de programmation ESP-IDF pour ESP32-C6 – Documentation complète pour le cadre de développement ESP-IDF.

- ESP-IDF et autres frameworks de développement sur GitHub.

https://github.com/espressif - ESP32 BBS Forum - Communauté d'ingénieur à ingénieur (E2E) pour les produits Espressif où vous pouvez poser des questions, partager des connaissances, explorer des idées et aider à résoudre des problèmes avec d'autres ingénieurs.

https://esp32.com/ - The ESP Journal - Meilleures pratiques, articles et notes des gens d'Espressif.

https://blog.espressif.com/ - Voir les onglets SDK et démos, Apps, Tools, AT Firmware.

https://espressif.com/en/support/download/sdks-demos

Produits

- SoC de la série ESP32-C6 – Parcourez tous les SoC ESP32-C6.

https://espressif.com/en/products/socs?id=ESP32-C6 - Modules de la série ESP32-C6 - Parcourez tous les modules basés sur ESP32-C6.

https://espressif.com/en/products/modules?id=ESP32-C6 - Kits de développement de la série ESP32-C6 – Parcourez tous les kits de développement basés sur ESP32-C6.

https://espressif.com/en/products/devkits?id=ESP32-C6 - Sélecteur de produits ESP - Trouvez un produit matériel Espressif adapté à vos besoins en comparant ou en appliquant des filtres.

https://products.espressif.com/#/product-selector?language=en

Contactez-nous

- Voir les onglets Sales Questions, Technical Enquiries, Circuit Schematic & PCB Design Review, Obtenez Samples

(Boutiques en ligne), Devenez notre fournisseur, Commentaires et suggestions.

https://espressif.com/en/contact-us/sales-questions

Historique des révisions

Avis de non-responsabilité et de droit d'auteur

Les informations contenues dans ce document, y compris URL références, est sujet à changement sans préavis.

TOUTES LES INFORMATIONS DE TIERS CONTENUES DANS CE DOCUMENT SONT FOURNIES EN L'ÉTAT SANS GARANTIE D'AUTHENTICITÉ ET D'EXACTITUDE.

AUCUNE GARANTIE N'EST FOURNIE À CE DOCUMENT POUR SA QUALITÉ MARCHANDE, SA NON-CONTREFAÇON, SON ADÉQUATION À UN USAGE PARTICULIER, NI AUCUNE GARANTIE DÉCOULANT AUTREMENT DE TOUTE PROPOSITION, SPÉCIFICATION OU SAMPLE.

Toute responsabilité, y compris la responsabilité pour violation de tout droit de propriété, relative à l'utilisation des informations contenues dans ce document est déclinée. Aucune licence expresse ou implicite, par préclusion ou autrement, sur des droits de propriété intellectuelle n'est concédée aux présentes.

Le logo Wi-Fi Alliance Member est une marque de Wi-Fi Alliance. Le logo Bluetooth est une marque déposée de Bluetooth SIG.

Tous les noms commerciaux, marques commerciales et marques déposées mentionnés dans ce document sont la propriété de leurs propriétaires respectifs et sont reconnus par la présente.

Copyright © 2023 Espressif Systems (Shanghai) Co., Ltd. Tous droits réservés.

Les informations contenues dans ce document, y compris URL références, est sujet à changement sans préavis.

TOUTES LES INFORMATIONS DE TIERS CONTENUES DANS CE DOCUMENT SONT FOURNIES EN L'ÉTAT SANS GARANTIE D'AUTHENTICITÉ ET D'EXACTITUDE.

AUCUNE GARANTIE N'EST FOURNIE À CE DOCUMENT POUR SA QUALITÉ MARCHANDE, SA NON-CONTREFAÇON, SON ADÉQUATION À UN USAGE PARTICULIER, NI AUCUNE GARANTIE DÉCOULANT AUTREMENT DE TOUTE PROPOSITION, SPÉCIFICATION OU SAMPLE.

Toute responsabilité, y compris la responsabilité pour violation de tout droit de propriété, relative à l'utilisation des informations contenues dans ce document est déclinée. Aucune licence expresse ou implicite, par préclusion ou autrement, sur des droits de propriété intellectuelle n'est concédée aux présentes.

Le logo Wi-Fi Alliance Member est une marque de Wi-Fi Alliance. Le logo Bluetooth est une marque déposée de Bluetooth SIG.

Tous les noms commerciaux, marques commerciales et marques déposées mentionnés dans ce document sont la propriété de leurs propriétaires respectifs et sont reconnus par la présente.

Copyright © 2023 Espressif Systems (Shanghai) Co., Ltd. Tous droits réservés.

Documents / Ressources

|

Errata SoC Espressif série ESP32-C6 [pdf] Manuel de l'utilisateur Errata SoC série ESP32-C6, Série ESP32-C6, Errata SoC, Errata |