Espressif ESP32-C6 Serio SoC Errata UzantManlibro

Enkonduko

Ĉi tiu dokumento priskribas konatajn erarojn en ESP32-C6 serioj de SoCs.

Ĉi tiu dokumento priskribas konatajn erarojn en ESP32-C6 serioj de SoCs.

Identigo de blato

Notu:

Kontrolu la ligilon aŭ la QR-kodon por certigi, ke vi uzas la lastan version de ĉi tiu dokumento:

https://espressif.com/sites/default/files/documentation/esp32-c6_errata_en.pdf

Kontrolu la ligilon aŭ la QR-kodon por certigi, ke vi uzas la lastan version de ĉi tiu dokumento:

https://espressif.com/sites/default/files/documentation/esp32-c6_errata_en.pdf

1 Peceto-Revizio

Espressif enkondukas vM.X numera skemo por indiki blatreviziojn.

M – Grava nombro, indikante la plej gravan revizion de la blatprodukto. Se ĉi tiu nombro ŝanĝiĝas, tio signifas, ke la programaro uzata por la antaŭa versio de la produkto estas nekongrua kun la nova produkto, kaj la programaro versio estos ĝisdatigita por la uzo de la nova produkto.

X – Malgranda nombro, indikante la negravan revizion de la blatprodukto. Se ĉi tiu nombro ŝanĝiĝas, ĝi signifas la

programaro uzata por la antaŭa versio de la produkto estas kongrua kun la nova produkto, kaj ne necesas ĝisdatigi la programaron.

programaro uzata por la antaŭa versio de la produkto estas kongrua kun la nova produkto, kaj ne necesas ĝisdatigi la programaron.

La vM.X-skemo anstataŭigas antaŭe uzitajn pecetajn reviziokabalojn, inkluzive de ECOx-nombroj, Vxxx, kaj aliajn formatojn se entute.

La peceta revizio estas identigita per:

- eFuse-kampo EFUSE_RD_MAC_SPI_SYS_3_REG[23:22] kaj EFUSE_RD_MAC_SPI_SYS_3_REG[21:18]

Tabelo 1: Identigo pri Revizio de Blato per eFuse Bitoj

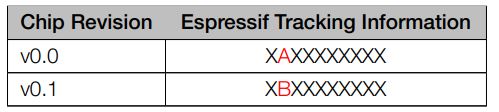

- Espressif Spuranta Informon linio en blato markado

Figuro 1: Blato Markado Diagramo

Tabelo 2: Identigo pri Revizio de Blato per Blata Markado

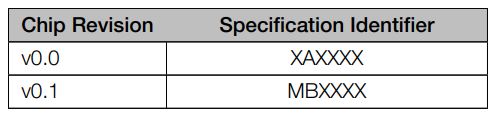

- Specifa identigilo linio en modulo markado

Figuro 2: Modula Markada Diagramo

Tabelo 3: Identigo pri Revizio de Blato per Modula Markado

Notu:

- Informoj pri ESP-IDF-eldono kiu subtenas specifan pececan revizion estas provizitaj en Kongrueco Inter ESP-IDF-Eldonoj kaj Revizioj de Espressif SoCs.

- Por pliaj informoj pri la ĝisdatigo de la revizio de blato kaj ilia identigo de produktoj de la serio ESP32-C6, bonvolu raporti al ESP32-C6 Sciigoj pri Produkto/Proceza Ŝanĝo (PCN).

- Por pliaj informoj pri la ĉipa revizia numeradskemo, vidu Konsilo pri Kongrueco por Chip Revision Numbering Scheme.

2 Pliaj Metodoj

Iuj eraroj en la peceta produkto ne bezonas esti riparitaj ĉe la silicia nivelo, aŭ alivorte en nova peceta revizio.

En ĉi tiu kazo, la blato povas esti identigita per Datkodo en pecetmarkado (vidu Figuro 1). Por pliaj informoj,

bonvolu konsulti Espressif Chip Packaging Informoj.

bonvolu konsulti Espressif Chip Packaging Informoj.

Moduloj konstruitaj ĉirkaŭ la blato povas esti identigitaj per PW-Numero en produktetikedo (vidu Figuro 3). Por pliaj informoj, bonvolu raporti al Espressif Module Packaging Information.

Figuro 3: Modula Produkta Etikedo

Notu:

Bonvolu noti tion PW Nombro estas nur provizita por bobenoj pakitaj en aluminiaj humidaj baraj sakoj (MBB).

Bonvolu noti tion PW Nombro estas nur provizita por bobenoj pakitaj en aluminiaj humidaj baraj sakoj (MBB).

Erara Priskribo

Tablo 4: Resumo de eraroj

3 CPU RISC-V

3.1 Ebla blokiĝo pro neorda plenumo de instrukcioj kiam skribas al LP SRAM estas implikita

Priskribo

Kiam HP CPU plenumas instrukciojn (instrukcio A kaj instrukcio B sinsekve) en LP SRAM, kaj instrukcio A kaj instrukcio B okazas sekvas la sekvajn padronojn:

- Instrukcio A implikas skribi al memoro. Ekzamples: sw/sh/sb

- Instrukcio B implikas nur aliri la instrukcibuson. Ekzamples: nop/jal/jalr/lui/auipc

- La adreso de instrukcio B ne estas 4-bajta vicigita

La datenoj skribitaj per instrukcio A al memoro estas nur transigitaj post instrukcio B kompletigis ekzekuton. Tio enkondukas riskon kie, post instrukcio A skribo al memoro, se senfina buklo estas efektivigita en instrukcio B, la skribo de instrukcio A neniam kompletiĝos.

Solvoj

Kiam vi spertas ĉi tiun problemon, aŭ kiam vi kontrolas la kunigkodon kaj vidas la supre menciitan ŝablonon,

- Aldonu barilon instrukcion inter instrukcio A kaj la senfina buklo. Ĉi tio povas esti atingita uzante la interfacon rv_utils_memory_barrier en ESP-IDF.

- Anstataŭigu la senfinan buklon per instrukcio wfi. Ĉi tio povas esti atingita uzante la interfacon rv_utils_wait_for_intr en ESP-IDF.

- Malebligu la etendon RV32C (kunpremita) dum kompilado de kodo, kiu estos efektivigita en LP SRAM por eviti instrukciojn kun ne 4-bajtaj vicigitaj adresoj.

Solvo

Riparota en la estontaj blatrevizioj.

Riparota en la estontaj blatrevizioj.

4 Horloĝo

4.1 Nepreciza Kalibrado de RC_FAST_CLK Horloĝo

Priskribo

En la ESP32-C6-peceto, la frekvenco de la horloĝfonto RC_FAST_CLK estas tro proksima al la referenca horloĝo (40 MHz XTAL_CLK) frekvenco, igante ĝin malebla kalibri precize. Ĉi tio povas influi ekstercentrajn uzojn RC_FAST_CLK kaj havas striktajn postulojn por ĝia preciza horloĝfrekvenco.

Por ekstercentraj uzantaj RC_FAST_CLK, bonvolu raporti al ESP32-C6 Teknika Referenca Manlibro > Ĉapitro Restarigi kaj Horloĝo.

Solvoj

Uzu aliajn horloĝfontojn anstataŭ RC_FAST_CLK.

Uzu aliajn horloĝfontojn anstataŭ RC_FAST_CLK.

Solvo

Riparita en blata revizio v0.1.

Riparita en blata revizio v0.1.

5 Restarigi

5.1 Sistemo Rekomencigita de RTC Watchdog Timer Ne Povas esti Ĝuste Raportita

Priskribo

Kiam la RTC-gardisto-tempigilo (RWDT) ekigas sisteman rekomencigon, la rekomencigita fontkodo ne povas esti fiksita ĝuste. Kiel rezulto, la raportita kaŭzo de rekomencigita estas nedeterminita kaj eble estas malĝusta.

Kiam la RTC-gardisto-tempigilo (RWDT) ekigas sisteman rekomencigon, la rekomencigita fontkodo ne povas esti fiksita ĝuste. Kiel rezulto, la raportita kaŭzo de rekomencigita estas nedeterminita kaj eble estas malĝusta.

Solvoj

Neniu solvo.

Neniu solvo.

Solvo

Riparita en blata revizio v0.1.

Riparita en blata revizio v0.1.

6 RMT

6.1 La neaktiva ŝtatsignalo-nivelo eble trafos eraron en RMT-kontinua TX-reĝimo

Priskribo

En la RMT-modulo de ESP32-C6, se la kontinua TX-reĝimo estas ebligita, oni atendas, ke la transdono de datumoj ĉesos post kiam la datumoj estas senditaj por RMT_TX_LOOP_NUM_CHn-rondoj, kaj post tio, la signalnivelo en neaktiva stato devus esti kontrolita de la "nivelo" kampo de la finmarko.

En la RMT-modulo de ESP32-C6, se la kontinua TX-reĝimo estas ebligita, oni atendas, ke la transdono de datumoj ĉesos post kiam la datumoj estas senditaj por RMT_TX_LOOP_NUM_CHn-rondoj, kaj post tio, la signalnivelo en neaktiva stato devus esti kontrolita de la "nivelo" kampo de la finmarko.

Tamen, en reala situacio, post kiam la datumtranssendo ĉesas, la neaktiva ŝtatsignalnivelo de la kanalo ne estas kontrolita per la "nivela" kampo de la fin-signo, sed per la nivelo en la datenoj envolvitaj reen, kiu estas nedeterminita.

Solvoj

Uzantoj estas sugestitaj agordi RMT_IDLE_OUT_EN_CHn al 1 por nur uzi registrojn por kontroli la neaktivan nivelon.

Ĉi tiu problemo estis preteririta ekde la unua ESP-IDF-versio kiu subtenas kontinuan TX-reĝimon (v5.1). En ĉi tiuj versioj de ESP-IDF, estas agorde ke la neaktiva nivelo povas esti kontrolita nur per registroj.

Uzantoj estas sugestitaj agordi RMT_IDLE_OUT_EN_CHn al 1 por nur uzi registrojn por kontroli la neaktivan nivelon.

Ĉi tiu problemo estis preteririta ekde la unua ESP-IDF-versio kiu subtenas kontinuan TX-reĝimon (v5.1). En ĉi tiuj versioj de ESP-IDF, estas agorde ke la neaktiva nivelo povas esti kontrolita nur per registroj.

Solvo

Neniu riparo planita.

Neniu riparo planita.

7 interreto

7.1 ESP32-C6 Ne povas esti 802.11mc FTM-Iniciato

Priskribo

La tempo de T3 (t.e. tempo de foriro de ACK de Iniciatilo) uzata en 802.11mc Fine Time Measurement (FTM) ne povas esti ĝuste akirita, kaj kiel rezulto ESP32-C6 ne povas esti la FTM Iniciatoro.

La tempo de T3 (t.e. tempo de foriro de ACK de Iniciatilo) uzata en 802.11mc Fine Time Measurement (FTM) ne povas esti ĝuste akirita, kaj kiel rezulto ESP32-C6 ne povas esti la FTM Iniciatoro.

Solvoj

Neniu solvo.

Neniu solvo.

Solvo

Riparota en la estontaj blatrevizioj.

Riparota en la estontaj blatrevizioj.

Rilata Dokumentaro

- ESP32-C6 Series Datasheet - Specifoj de la ESP32-C6-aparataro.

- ESP32-C6 Teknika Referenca Manlibro - Detalaj informoj pri kiel uzi la ESP32-C6-memoron kaj ekstercentrajn.

- Gvidlinioj pri Aparataro pri ESP32-C6 - Gvidlinioj pri kiel integri la ESP32-C6 en vian aparataron.

- Atestiloj https://espressif.com/en/support/documents/certificates

- ESP32-C6 Sciigoj pri Produkto/Proceza Ŝanĝo (PCN) https://espressif.com/en/support/documents/pcns?keys=ESP8684

- Dokumentaj Ĝisdatigoj kaj Ĝisdatiga Sciigo-Abono https://espressif.com/en/support/download/documents

Zono por programistoj

- ESP-IDF-Programming Guide por ESP32-C6 - Ampleksa dokumentaro por la ESP-IDF-disvolva kadro.

- ESP-IDF kaj aliaj disvolvaj kadroj sur GitHub.

https://github.com/espressif - ESP32 BBS Forumo - Inĝeniero-al-Inĝeniero (E2E) Komunumo por Espressif-produktoj kie vi povas afiŝi demandojn, dividi scion, esplori ideojn kaj helpi solvi problemojn kun kolegaj inĝenieroj.

https://esp32.com/ - La ESP-Ĵurnalo - Plej Bonaj Praktikoj, Artikoloj kaj Notoj de Espressif-uloj.

https://blog.espressif.com/ - Vidu la langetojn SDK-oj kaj Demonstraĵoj, Aplikoj, Iloj, AT Firmware.

https://espressif.com/en/support/download/sdks-demos

Produktoj

- ESP32-C6 Series SoCs - Foliumi ĉiujn ESP32-C6 SoCs.

https://espressif.com/en/products/socs?id=ESP32-C6 - ESP32-C6-Seriaj Moduloj - Foliumi ĉiujn ESP32-C6-bazitajn modulojn.

https://espressif.com/en/products/modules?id=ESP32-C6 - ESP32-C6 Series DevKits - Foliumi ĉiujn ESP32-C6-bazitajn devkits.

https://espressif.com/en/products/devkits?id=ESP32-C6 - ESP-Produkta Elektilo - Trovu Espressif aparataron taŭgan por viaj bezonoj komparante aŭ aplikante filtrilojn.

https://products.espressif.com/#/product-selector?language=en

Kontaktu Nin

- Vidu la langetojn Vendaj Demandoj, Teknikaj Demandoj, Circuit Schematic & PCB Design Review, Ricevasamples

(Retaj butikoj), Fariĝu Nia Provizanto, Komentoj kaj Sugestoj.

https://espressif.com/en/contact-us/sales-questions

Historio de Revizio

Malgarantio kaj Kopirajto-Avizo

Informoj en ĉi tiu dokumento, inkluzive URL referencoj, estas ŝanĝebla sen avizo.

ĈIUJ INFORMOJ DE TRIAPARTO EN ĈI TIU DOKUMENTO ESTAS PROVIZITA KIAL SEN NENIAJ GARANTIOJ PRI ĜIAA AUTENTECO KAJ PREZECO.

NENIAJ GARANTIO ESTAS PROVIZITA AL ĈI ĈI DOKUMENTO POR ĜIA KOMERCIEBLECO, NE-MALFRONTO, TAŬGECO POR IUJ APARTA CELO, NEK AJN GARANTIO ALIE EKZISTANTA EL IUJ PROPONO, SPECIFICADO AŬ S.AMPLE.

Ĉiu respondeco, inkluzive de respondeco por malobservo de ajnaj proprietaj rajtoj, rilate al uzo de informoj en ĉi tiu dokumento estas malakceptita. Neniuj licencoj esprimaj aŭ implicitaj, per malpermeso aŭ alie, al iuj rajtoj pri intelekta proprieto estas donitaj ĉi tie.

La emblemo de Wi-Fi Alliance Member estas varmarko de la Wi-Fi Alliance. La Bluetooth-emblemo estas registrita varmarko de Bluetooth SIG.

Ĉiuj komercaj nomoj, varmarkoj kaj registritaj markoj menciitaj en ĉi tiu dokumento estas posedaĵo de siaj respektivaj posedantoj, kaj estas ĉi-pere agnoskitaj.

Kopirajto © 2023 Espressif Systems (Shanghai) Co., Ltd. Ĉiuj rajtoj rezervitaj.

Informoj en ĉi tiu dokumento, inkluzive URL referencoj, estas ŝanĝebla sen avizo.

ĈIUJ INFORMOJ DE TRIAPARTO EN ĈI TIU DOKUMENTO ESTAS PROVIZITA KIAL SEN NENIAJ GARANTIOJ PRI ĜIAA AUTENTECO KAJ PREZECO.

NENIAJ GARANTIO ESTAS PROVIZITA AL ĈI ĈI DOKUMENTO POR ĜIA KOMERCIEBLECO, NE-MALFRONTO, TAŬGECO POR IUJ APARTA CELO, NEK AJN GARANTIO ALIE EKZISTANTA EL IUJ PROPONO, SPECIFICADO AŬ S.AMPLE.

Ĉiu respondeco, inkluzive de respondeco por malobservo de ajnaj proprietaj rajtoj, rilate al uzo de informoj en ĉi tiu dokumento estas malakceptita. Neniuj licencoj esprimaj aŭ implicitaj, per malpermeso aŭ alie, al iuj rajtoj pri intelekta proprieto estas donitaj ĉi tie.

La emblemo de Wi-Fi Alliance Member estas varmarko de la Wi-Fi Alliance. La Bluetooth-emblemo estas registrita varmarko de Bluetooth SIG.

Ĉiuj komercaj nomoj, varmarkoj kaj registritaj markoj menciitaj en ĉi tiu dokumento estas posedaĵo de siaj respektivaj posedantoj, kaj estas ĉi-pere agnoskitaj.

Kopirajto © 2023 Espressif Systems (Shanghai) Co., Ltd. Ĉiuj rajtoj rezervitaj.

Dokumentoj/Rimedoj

| Espressif ESP32-C6 Series SoC Errato [pdf] Uzanto-manlibro ESP32-C6 Serio SoC Eraro, ESP32-C6 Serio, SoC Eraro, Eraro |