Atmel ATF15xx-DK3 CPLD þróunar-/forritarasett

Inngangur

Atmel® ATF15xx-DK3 Complex Programmable Logic Device (CPLD) þróunar-/forritarasett er fullkomið þróunarkerfi og ISP forritara fyrir Atmel ATF15xx fjölskyldu iðnaðarstaðlaðra pinna samhæfra CPLDs með Logic Doubleling® eiginleika. Þetta sett veitir hönnuðum mjög fljótlega og auðvelda leið til að þróa frumgerðir og meta nýja hönnun með ATF15xx ISP CPLD. ATF15xx fjölskyldan af ISP CPLDs inniheldur Atmel ATF15xxAS, ATF15xxASL, ATF15xxASV og ATF15xxASVL CPLD. Þar sem mismunandi innstu millistykki eru til staðar til að styðja flestar pakkategundirnar(1) sem boðið er upp á í ATF15xx fjölskyldunni af ISP CPLD, er hægt að nota þetta sett sem ISP forritara til að forrita ATF15xx ISP CPLD í flestum tiltækum pakkategundum (1) í gegnum iðnaðarstaðalinn JTAG tengi (IEEE 1149.1).

Innihald setts

- Atmel CPLD þróunar-/forritararáð (P/N: ATF15xx-DK3)

- Atmel 44-pinna TQFP fals millistykki (P/N: ATF15xx-DK3-SAA44)(2)

- Atmel ATF15xx LPT-undirstaða JTAG ISP niðurhalssnúra (P/N: ATDH1150VPC)

- Tveir Atmel 44-pinna TQFP Sample Tæki

Stuðningur við tæki

ATF15xx-DK3 CPLD þróunar-/forritarasettið styður eftirfarandi tæki í öllum Atmel hraðaflokkum og pökkum sem nú eru fáanlegir (nema 100-PQFP):

- ATF1502AS/ASL

- ATF1504AS/ASL

- ATF1508ASV/ASVL

- ATF1502ASV

- ATF1504ASV/ASVL

- ATF1508AS/ASL

- Innstungu millistykkið er ekki í boði fyrir 100 pinna PQFP.

- Aðeins 44-pinna TQFP Socket Adapter Board er innifalið í þessu setti. Önnur millistykki fyrir innstungu eru seld sér. Sjá kafla, „Lýsing vélbúnaðar“ til að fá frekari upplýsingar um pöntunarkóða fyrir millistykki fyrir innstungu.i

Eiginleikar Kit

Stjórn CPLD þróunar/forritara

- 10 pinna JTAG-ISP höfn

- Stýrðar aflgjafarrásir fyrir 9VDC aflgjafa

- Valanlegt 5V, 3.3V, 2.5V, eða 1.8VI/O Voltage Framboð

- Valanlegt 1.8V, 3.3V eða 5.0V Core Voltage Framboð

- 44-pinna TQFP Socket Adapter Board

- Hausar fyrir I/O pinna á ATF15xx tækinu

- 2MHz kristalsveifla

- Fjórir 7-hluta LED skjáir

- Átta einstök LED

- Átta þrýstihnappa rofar

- Global Clear og Output Enable Þrýstihnapparofar

- Straummælingarstökkvarar

Rökfræðileg tvöföldun CPLDs

ATF15xx ISP CPLD með Logic Doubling Architecture

- ATF15xx ISP niðurhalssnúra

- 5V, 3.3V, 2.5V eða 1.8V ISP niðurhalssnúra fyrir PC Parallel Printer (LPT) tengi

- PLD þróunarhugbúnaður

- Atmel PLD þróunarhugbúnaðarverkfærin eru fáanleg á netinu fyrir notkun PLD hönnuða á ATF15xx ISP CPLD. Vinsamlegast vísað til Overview skjal, „PLD

- Hönnunarhugbúnaður lokiðview“ fæst á:

- http://www.atmel.com/images/atmel-3629-pld-design-software-overview.pdf

Kerfiskröfur

- Lágmarks vélbúnaður og hugbúnaður sem þarf til að forrita ATF15xx ISP CPLD tæki sem er hannað með Atmel ProChip Designer hugbúnaðinum á CPLD þróunar-/forritaborðinu í gegnum Atmel ATMISP v6.x (ATF15xx CPLD ISP hugbúnaðinn) eru:

- x86 Tölva með örgjörva

- Windows XP®, Windows® 98, Windows NT® 4.0 eða Windows 2000

- 128 MB vinnsluminni

- 500 MByte ókeypis harður diskur

- Windows-studd mús

- Laus samhliða prentara (LPT) tengi

- 9VDC aflgjafi með 500mA af straumi

- SVGA skjár (800 x 600 upplausn)

Upplýsingar um pöntun

| Atmel hlutanúmer | Lýsing |

| ATF15xx-DK3 | CPLD þróunar-/forritarasett (inniheldur ATF15xxDK3-SAA44*) |

| ATF15xxDK3-SAA100 | 100-pinna TQFP Socket Adapter Board fyrir DK3 Board |

| ATF15xxDK3-SAJ44 | 44-pinna PLCC innstungu millistykki fyrir DK3 borð |

| ATF15xxDK3-SAJ84 | 84-pinna PLCC innstungu millistykki fyrir DK3 borð |

| ATF15xxDK3-SAA44* | 44-pinna TQFP Socket Adapter Board fyrir DK3 Board |

Vélbúnaðarlýsing

Stjórn CPLD þróunar/forritara

- CPLD þróunar-/forritara- og innstungukortin sem sýnd eru á myndinni hér að neðan innihalda eiginleika sem eru gagnlegir við þróun, frumgerð eða mat

- ATF15xx CPLD hönnun. Eiginleikar sem gera þetta að mjög fjölhæfu byrjunar-/þróunarsetti og ISP forritara fyrir ATF15xx fjölskyldu JTAG-ISP CPLDs innihalda:

- Rofar með þrýstihnappi

- LED

- 7-hluta skjár

- 2MHz kristalsveifla

- 5V, 3.3V, 2.5V eða 1.8V VCCIO val

- 1.8V, 3.3V eða 5.0V VCCINT val

- JTAG ISP tengi

- Innstungu millistykki

- 7-hluta skjár með valanlegum stökkum

- CPLD þróunar-/forritaborðið inniheldur fjóra 7-hluta skjái sem gera kleift að fylgjast með ATF15xx CPLD úttakunum. Þessir fjórir skjáir eru merktir sem DSP1, DSP2, DSP3 og DSP4. 7-hluta skjáirnir eru með algengar rafskautsljós með sameiginlegu rafskautalínunum tengdum VCCIO (I/O framboðsrúmmálitage fyrir CPLD) í gegnum röð viðnáms með valanlegum stökkum merktum JPDSP1, JPDSP2, JPDSP3 og JPDSP4. Þessa jumpers er hægt að fjarlægja til

slökkva á skjánum með því að aftengja VCCIO við skjáina. Einstakar bakskautslínur eru tengdar við I/O pinna á ATF15xx CPLD á CPLD - Þróunar-/forritarasett. Til að kveikja á tilteknum hluta, þar með talið DOT á skjá, verður samsvarandi ATF15xx I/O pinna sem er tengdur þessum LED hluta að vera í rökfræðilegu lágu ástandi með samsvarandi valanlegum jumper setti; þess vegna mun úttak ATF15xx tækisins krefjast stillingar fyrir virkt-lágt úttak í hönnuninni file. Skjárarnir virka best við 2.5V VCCIO eða hærra.

- Hver hluti hvers skjás er tengdur við einn tiltekinn I/O pinna á ATF15xx tækinu. Fyrir tæki með hærri pinnafjölda (100 pinna og stærri) eru allir sjö hlutar og DOT hlutir fjögurra skjáanna tengdir við I/O pinna; Hins vegar, fyrir tæki með lægri pinnafjölda, er aðeins hluti af skjánum, fyrsta og fjórða skjánum, tengt við I/O pinna ATF15xx tækisins. Töflur 1 og 2 sýna 7-hluta skjápakkatengingar við ATF15xx tækið. Hringrásarteikning skjáanna og stökkvaranna er sýnd á myndinni hér að neðan.

Mynd 2. Hringrásarmynd af 7-hluta skjá og jumpers

Tafla 1.ATF15xx 44-pinna tengingar við 7-hluta skjái

| 44-pinna TQFP | |||

| DSP/Segment | PLD pinna | DSP/Segment | PLD pinna |

| 1/A | 27 | 3/A | NC |

| 1/B | 33 | 3/B | NC |

| 1/C | 30 | 3/C | NC |

| 1/D | 21 | 3/D | NC |

| 1/E | 18 | 3/E | NC |

| 1 / F | 23 | 3 / F | NC |

| 1 / G | 20 | 3 / G | NC |

| 1/PUNKTUR | 31 | 3/PUNKTUR | NC |

| 2/A | NC | 4/A | 3 |

| 2/B | NC | 4/B | 10 |

| 2/C | NC | 4/C | 6 |

| 2/D | NC | 4/D | 43 |

| 2/E | NC | 4/E | 35 |

| 2 / F | NC | 4 / F | 42 |

| 2 / G | NC | 4 / G | 34 |

| 2/PUNKTUR | NC | 4/PUNKTUR | 11 |

| 44 pinna PLCC | |||

| DSP/Segment | PLD pinna | DSP/Segment | PLD pinna |

| 1/A | 33 | 3/A | NC |

| 1/B | 39 | 3/B | NC |

| 1/C | 36 | 3/C | NC |

| 1/D | 27 | 3/D | NC |

| 1/E | 24 | 3/E | NC |

| 1 / F | 29 | 3 / F | NC |

| 1 / G | 26 | 3 / G | NC |

| 1/PUNKTUR | 37 | 3/PUNKTUR | NC |

| 2/A | NC | 4/A | 9 |

| 2/B | NC | 4/B | 16 |

| 2/C | NC | 4/C | 12 |

| 2/D | NC | 4/D | 5 |

| 2/E | NC | 4/E | 41 |

| 2 / F | NC | 4 / F | 4 |

| 2 / G | NC | 4 / G | 40 |

| 2/PUNKTUR | NC | 4/PUNKTUR | 17 |

Tafla 2.ATF15xx 84-pinna og 100-pinna tengingar við 7-hluta skjái

| 84 pinna PLCC | |||

| DSP/Segment | PLD pinna | DSP/Segment | PLD pinna |

| 1/A | 68 | 3/A | 22 |

| 1/B | 74 | 3/B | 28 |

| 1/C | 70 | 3/C | 25 |

| 1/D | 63 | 3/D | 21 |

| 1/E | 58 | 3/E | 16 |

| 1 / F | 65 | 3 / F | 17 |

| 1 / G | 61 | 3 / G | 12 |

| 1/PUNKTUR | 73 | 3/PUNKTUR | 29 |

| 2/A | 52 | 4/A | 5 |

| 2/B | 57 | 4/B | 10 |

| 2/C | 55 | 4/C | 8 |

| 2/D | 48 | 4/D | 79 |

| 2/E | 41 | 4/E | 76 |

| 2 / F | 50 | 4 / F | 77 |

| 2 / G | 45 | 4 / G | 75 |

| 2/PUNKTUR | 50 | 4/PUNKTUR | 11 |

| 100-pinna TQFP | |||

| DSP/Segment | PLD pinna | DSP/Segment | PLD pinna |

| 1/A | 67 | 3/A | 13 |

| 1/B | 71 | 3/B | 19 |

| 1/C | 69 | 3/C | 16 |

| 1/D | 61 | 3/D | 8 |

| 1/E | 57 | 3/E | 83 |

| 1 / F | 64 | 3 / F | 6 |

| 1 / G | 60 | 3 / G | 92 |

| 1/PUNKTUR | 75 | 3/PUNKTUR | 20 |

| 2/A | 52 | 4/A | 100 |

| 2/B | 54 | 4/B | 94 |

| 2/C | 47 | 4/C | 97 |

| 2/D | 41 | 4/D | 81 |

| 2/E | 46 | 4/E | 76 |

| 2 / F | 40 | 4 / F | 80 |

| 2 / G | 45 | 4 / G | 79 |

| 2/PUNKTUR | 56 | 4/PUNKTUR | 93 |

LED með valanlegum stökkum

CPLD þróunar-/forritaraborðið er með átta einstökum ljósdíóðum, sem gera hönnuðum kleift að birta úttaksmerki frá inn/útum notenda ATF15xx tækjanna. Þessar átta LED eru merktar LED1 til LED8 á CPLD þróunar-/forritaraborðinu. Bakskaut hvers LED er tengt við jörðu (GND) í gegnum raðviðnám en rafskaut hvers LED er tengt við notanda I/O pinna á CPLD í gegnum JPL1/2/3/4/5/6/7 /8 veljanlegur jumper. Hægt er að fjarlægja þessa jumper til að slökkva á ljósdíóðum með því að aftengja rafskaut ljósdíóða við I/O pinna CPLD. Myndin hér að neðan sýnir hringrásarmynd ljósdíóðanna með valstökkunum.

Til að kveikja á tilteknu LED verður samsvarandi ATF15xx I/O pinna sem er tengt við LED að vera í rökfræðilegu háu ástandi með samsvarandi jumper setti; því þarf að stilla úttak ATF15xx tækisins sem virk háútgang. LED virkar best við 2.5V VCCIO eða hærra.

Tækin með lægri pinnafjölda (44 pinna) hafa aðeins fjögur I/O tengi tengd við LED1/2/3/4. Fyrir tæki með hærri pinnafjölda (100 pinna og stærri) eru allar átta ljósdídurnar tengdar við I/O tækisins. Tafla 3 sýnir mismunandi pakkatengingar CPLD I/Os við LED.

Tafla 3.ATF15xx Tengingar við LED

| 44-pinna TQFP | |

| LED | PLD pinna |

| LED1 | 28 |

| LED2 | 25 |

| LED3 | 22 |

| LED4 | 19 |

| 44 pinna PLCC | |

| LED | PLD pinna |

| LED1 | 34 |

| LED2 | 31 |

| LED3 | 28 |

| LED4 | 25 |

| 84 pinna PLCC | |

| LED | PLD pinna |

| LED1 | 69 |

| LED2 | 67 |

| LED3 | 64 |

| LED4 | 60 |

| LED5 | 27 |

| LED6 | 24 |

| LED7 | 18 |

| LED8 | 15 |

| 100-pinna TQFP | |

| LED | PLD pinna |

| LED1 | 68 |

| LED2 | 65 |

| LED3 | 63 |

| LED4 | 58 |

| LED5 | 17 |

| LED6 | 14 |

| LED7 | 10 |

| LED8 | 9 |

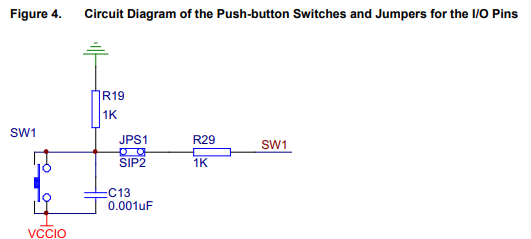

Þrýstihnapparofar með valanlegum stökkum fyrir I/O pinna

- CPLD þróunar-/forritaborðið inniheldur átta þrýstihnappa rofa, sem eru tengdir við I/O pinna CPLD. Rofarnir senda inntaksrökmerki til notenda I/O pinna ATF15xx tækisins. Þessir rofar eru merktir SW1 til SW8 á CPLD þróun/forritara

Stjórn. Annar endi hvers inntaksþrýstihnappsrofa er tengdur við VCCIO, en hinn endi hvers þrýstihnappsrofa er tengdur við niðurdráttarviðnám og síðan tengdur tilteknum I/O pinna CPLD í gegnum JPS1/2 /3/4/5/6/7/8 valanleg topp. - Ef ýtt er á einhvern af þessum rofum og samsvarandi jumper er stilltur, verður sérstakur I/O pinna tækisins keyrður í rökfræðilegt hátt ástand með úttak rofarásarinnar. Þar sem hver þrýstihnappsrofi er einnig tengdur við niðurdráttarviðnám mun inntakið hafa rökfræðilegt lágt ástand ef ekki er ýtt á rofann með samsvarandi jumper sett. Ef þrýstihnappurinn er ekki stilltur, verður samsvarandi pinna meðhöndluð sem ótengdur pinna. Mynd 4 er hringrásarmynd af þrýstihnappsrofanum og valanlegum jumper. Tafla 4 sýnir tengingar þessara átta þrýstihnappa rofa við CPLD I/O pinna í mismunandi pakkagerðum.

Tafla 4.ATF15xx Tengingar við I/O pinnarofa

| 44-pinna TQFP | |

| Þrýstihnappur | PLD pinna |

| SW1 | 15 |

| SW2 | 14 |

| SW3 | 13 |

| SW4 | 12 |

| SW5 | 8 |

| SW6 | 5 |

| SW7 | 2 |

| SW8 | 44 |

| 44 pinna PLCC | |

| Þrýstihnappur | PLD pinna |

| SW1 | 21 |

| SW2 | 20 |

| SW3 | 19 |

| SW4 | 18 |

| SW5 | 14 |

| SW6 | 11 |

| SW7 | 8 |

| SW8 | 6 |

| 84 pinna PLCC | |

| Þrýstihnappur | PLD pinna |

| SW1 | 54 |

| SW2 | 51 |

| SW3 | 49 |

| SW4 | 44 |

| SW5 | 9 |

| SW6 | 6 |

| SW7 | 4 |

| SW8 | 80 |

| 100-pinna TQFP | |

| Þrýstihnappur | PLD pinna |

| SW1 | 48 |

| SW2 | 36 |

| SW3 | 44 |

| SW4 | 37 |

| SW5 | 96 |

| SW6 | 98 |

| SW7 | 84 |

| SW8 | 99 |

Þrýstihnapparofar með valanlegum stökkum fyrir GCLR og OE1 pinna

CPLD þróunar-/forritaraborðið inniheldur tvo þrýstihnappa fyrir Global Clear (GCLR) og Output Enable (OE1) pinna á CPLD. Rofarnir stjórna rökfræðiástandi OE1 og GCLR inntaks ATF15xx tækjanna. Þessir rofar eru merktir SW-GCLR og SW-GOE1 á borðinu. Annar endi SW-GCLR inntakshnapparofans er tengdur við GND. Hinum endanum á

þrýstihnapparofinn er tengdur við uppdráttarviðnám við VCCIO og síðan tengdur við GCLR sérstaka inntakspinnann á ATF15xx tækinu. Það er ætlað að nota sem virkt-lágt endurstillingarmerki til að endurstilla skrárnar í ATF15xx tækinu með JPGCLR valanlegu jumper settinu. Á sama hátt er annar endi SW-GOE1 inntakshnapparofans tengdur við GND. Hinn endinn á þrýstihnappsrofanum

er tengdur við uppdráttarviðnám við VCCIO og síðan tengdur við OE1 sérstaka inntakspinnann á ATF15xx tækinu. Það er ætlað til notkunar sem virkt-lágt úttaksmerki til að stjórna kveikingu/slökkva á þriggja stöðu úttaksbuffum í ATF15xx með JPGOE valanlegum jumper setti. Mynd 5 er hringrásarmynd af þrýstihnapparofunum og stökkunum fyrir GCLR og OE1 pinnana.

Ef ýtt er á einhvern af þessum þrýstihnapparofum og samsvarandi jumper er stilltur, verður tiltekið I/O CPLD keyrt í rökfræðilegt lágt ástand. Þar sem hver þrýstihnappur er einnig tengdur við uppdráttarviðnám, mun samsvarandi CPLD-inntak hafa rökfræðilegt hátt ástand ef ekki er ýtt á þrýstihnapparofann með samsvarandi valanlegum jumper. Ef valinn stökkvari er ekki stilltur getur samsvarandi sérinntakspinninn á CPLD talist No Connect (NC) pinna. Tafla 5 sýnir pinnanúmer GCLR og OE1 sérstaka inntakspinna ATF15xx tækjanna í öllum tiltækum pakkagerðum.

Mynd 5. Hringrásarmynd af þrýstihnappsrofum og valanlegum stökkum fyrir GCLR og OE1

Tafla 5.Pinnanúmer GCLR og OE1

| 44-pinna TQFP | 44 pinna PLCC | 84 pinna PLCC | 100-pinna TQFP | |

| GCLR | 39 | 1 | 1 | 89 |

| OE1 | 38 | 44 | 84 | 88 |

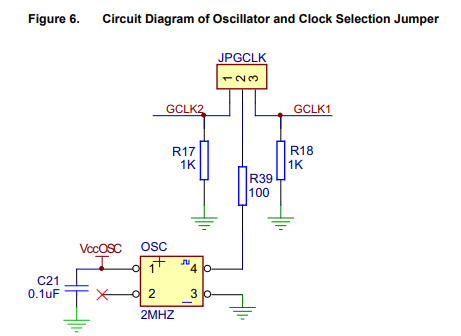

2MHz Oscillator og Clock Selection Jumper

Klukkuvalstökkvarinn merktur JP-GCLK á CPLD þróunar-/forritaraborðinu er tveggja staða jumper sem gerir notendum kleift að velja hvaða GCLK sérstaka inntakspinna (annaðhvort GCLK1 eða GCLK2) ATF15xx tækisins á að vera tengdur við úttak 2MHz oscillator. Að auki er hægt að fjarlægja stökkvarann til að leyfa ytri klukkugjafa að vera tengdur við GCLK1 og/eða GCLK2 á ATF15xx tækinu. Mynd 6 er mynd af hringrásarmynd sveiflunnar og valstökkvarans. Tafla 6 sýnir pinnanúmer fyrir GCLK1 og GCLK2 sérstaka inntakspinna ATF15xx tækisins í öllum mismunandi tiltækum pakkagerðum.

Ef GCLK1 stökkvarinn er stilltur verður stökkvarinn staðsettur til hliðar á borðinu. Á hinn bóginn, ef GCLK2 stökkvarinn er stilltur, verður stökkvarinn staðsettur í átt að miðju borði.

Tafla 6.Pinnanúmer GCLK1 og GCLK2

| 44-pinna TQFP | 44 pinna PLCC | 84 pinna PLCC | 100-pinna TQFP | |

| GCLK1 | 37 | 43 | 83 | 87 |

| GCLK2 | 40 | 2 | 2 | 90 |

VCCIO og VCCINT Voltage Valstökkvarar og LED

- VCCIO og VCCINT Voltage Selection jumpers, merktir VCCIO Selector og VCCINT Selector í sömu röð á ATF15xx-DK3 þróunar-/forritunarsettinu, leyfa val á I/O framboði

- binditage-stig (VCCIO) og kjarnaframboð binditage-stig (VCCINT) sem eru notuð fyrir mark-CPLD á settinu. Þegar þessir stökkvarar eru rétt stilltir kviknar á ljósdíóðum (merkt VCCINT LED og VCCIO LED); þó við lægra framboð voltage stigum (þ.e. 2.5V eða lægra), gætu LED-ljósin verið mjög dauf.

- Fyrir ATF15xxAS/ASL (5.0V) CPLD verða bæði VCCIO Selector og VCCINT Selector jumper að vera stillt á 5.0V.

- Fyrir ATF15xxASV/ASVL (3.3V) CPLDs verða bæði VCCIO Selector og VCCINT Selector Jumpers að vera stilltir á 3.3V eingöngu.

- Slökkt verður á krafti CPLD þróunar/forritarasettsins þegar skipt er um stöðu VCCIO eða VCCINT Voltage Valstökkvari (VCCIO vali eða VCCINT vali).

- ICCIO og ICCINT Jumpers

- Hægt er að fjarlægja ICCIO og ICCINT jumperana og nota sem ICC mælipunkta. Þegar stökkvararnir eru fjarlægðir er hægt að tengja straummæla við póstana til að mæla straumnotkun mark-CPLD. Þegar notendur eru ekki að nota þessa jumper til að mæla strauminn verða þessir jumpers að vera stilltir til að settið og CPLD virki.

- Voltage Eftirlitsaðilar

- Tvö binditage eftirlitsaðilar, merktir VR1 og VR2, eru notaðir til að mynda og stjórna sjálfstætt

- VCCINT og VCCIO binditages frá 9VDC aflgjafanum. Fyrir frekari upplýsingar, vinsamlegast sjáðu ATF15xx-DK3 setta skýringarmyndina, mynd 12.

- Aflgjafarofi og Power LED

- Hægt er að skipta um aflgjafarofa, merktan POWER SWITCH, í kveikt eða slökkt, sem er notað til að kveikja eða slökkva á afli ATF15xx-DK3 borðsins í sömu röð. Það gerir 9VDC voltage á Power Supply Jack til að fara í voltage eftirlitsstofnanir þegar það er í á stöðu. Þegar kveikt er á aflgjafarofanum mun Power LED (merkt POWER LED) kvikna til að gefa til kynna að ATF15xx-DK3 Kit sé með rafmagni.

- Aflgjafatjakkur og aflgjafahaus

- ATF15xx-DK3 borðið inniheldur tvær mismunandi gerðir af aflgjafatengi merkt JPower og JP Power. Annaðhvort þessara aflgjafatengja er hægt að nota til að tengja 9VDC aflgjafa við settið. Fyrsta rafmagnstengið sem er merkt JPower, er rafmagnstengi í tunnu með 2.1 mm þvermál stöng, og það passar við 2.1 mm (innra þvermál) x 5.5 mm (ytra þvermál) kventappa. Annar aflgjafahausinn merktur JP Power, er 4-pinna karlkyns 0.100" haus með 0.025" ferningapóstum. Framboð þessara tveggja tegunda af rafmagnstengi gerir notendum kleift að velja tegund aflgjafabúnaðar til að nota fyrir ATF15xx-DK3 þróunar-/forritarasett.

- Aðeins annað af þessum tveimur aflgjafatengjum ætti að vera knúið með 9VDC orkugjafa en ekki bæði á sama tíma.

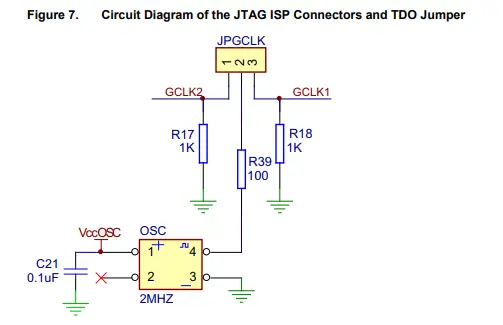

- JTAG ISP tengi og TDO Val Jumper

- Hinn J.TAG ISP tengi merkt JTAG-IN, er notað til að tengja ATF15xx JTAG tengipinnar (TCK, TDI, TMS og TDO) í gegnum ISP niðurhalssnúruna í samhliða prentara (LPT) tengi tölvu fyrir JTAG ISP forritun á ATF15xx tækinu. Skautuð tengi eru notuð á ATF15xx-DK3 og ISP niðurhalssnúrunni til að lágmarka tengingarvandamál. PIN1 merkimiðinn neðst á JTAG ISP tengi gefur til kynna pinna 1 stöðu 10 pinna haussins og dregur enn frekar úr líkunum á að tengja ISP niðurhalssnúruna rangt.

- Vinstra megin við JTAG-IN tengi, það eru tveir dálkar af vias, og þeir eru merktir JTAG-ÚT. Þeim er ætlað að leyfa notendum að búa til JTAG Daisy chain til að framkvæma JTAG aðgerðir á mörg tæki. Notendur þurfa að lóða sams konar tengi og það sem notað er fyrir JTAG-INN í JTAG-OUT stöðu til að nýta þennan tiltæka eiginleika.

- Til að búa til JTAG Daisy chain með mörgum ATF15xx-DK3 spjöldum, TDO Selection Jumper, merktur JP-TDO, verður að vera stilltur í viðeigandi stöðu. Fyrir öll tækin í keðjunni nema síðasta tækið, verður þessi jumper að vera stilltur á TO NEXT DEVICE stöðu. Fyrir síðasta tækið í keðjunni verður þessi jumper að vera stilltur á TO ISP CABLE stöðu. Þegar þessi stökkvari er í TO NEXT DEVICE stöðunni, er TDO þess tiltekna JTAG tækið verður tengt við TDI næsta

- JTAG tæki í keðjunni. Þegar þessi jumper er í TO ISP CABLE stöðu, verður TDO þess tækis tengdur við TDO á JTAG 10-pinna tengi, sem gerir kleift að senda TDO merki þess tækis í keðjunni aftur til hýsingartölvunnar með ISP hugbúnaðinum. Myndin hér að neðan er hringrásarmynd af

- JTAG tengi og JP-TDO jumper. Taflan hér að neðan sýnir pin-númerin á fjórum JTAG pinna fyrir ATF15xx tækið í öllum tiltækum pakkningum.

Fyrir uppsetningu á einni tæki verður staða JP-TDO jumper að vera stillt á TO ISP CABLE.

Mynd 7. Hringrásarmynd af JTAG ISP tengi og TDO Jumper

- Tafla 7.Pinnanúmer JTAG Hafnarmerki

| 44-pinna TQFP | 44 pinna PLCC | 84 pinna PLCC | 100-pinna TQFP | |

| TDI | 1 | 7 | 14 | 4 |

| TDO | 32 | 38 | 71 | 73 |

| TMS | 7 | 13 | 23 | 15 |

| TCK | 26 | 32 | 62 | 62 |

ISP reikniritinu er stjórnað af ATMISP hugbúnaðinum sem keyrir á tölvunni. Hinir fjórir JTAG merki eru mynduð af LPT tenginu og þau eru í biðminni af ISP niðurhalssnúrunni áður en þau fara inn í ATF15xx tækið á CPLD þróunar/forritara borðinu. 10 pinna JTAG Port Header pinout á CPLD Development/Programmer borðinu er sýnt á mynd 8, og mál þessa 10 pinna karlkyns JTAG hausinn er sýndur á mynd 9.

Mynd 8. 10-pinna JTAG Port Header Pinout

- 10 pinna JTAG Port Header pinout er samhæft við ATDH1150PC/VPC LPT tengitengda snúru og ATDH1150USB USB tengi byggða snúru, auk Altera

- ByteBlaster/MV/II Snúrar sem byggjast á LPT tengi. Að auki leyfir ATMISP v6.7 hugbúnaðurinn notkun annaðhvort Atmel

- ATDH1150PC/VPC/USB snúru eða ByteBlaster/MV/II snúru til að útfæra ISP.

- ATMISP v7.0 styður aðeins ATDH1150USB snúruna.

- Socket Adapter Board

- ATF15xx-DK3 CPLD þróunar/forritara innstungu millistykki (ATF15xx-DK3-XXXXX) eru hringrásartöflur sem tengjast ATF15xx-DK3 CPLD þróunar/forritara borði. Þau eru notuð í tengslum við ATF15xx-DK3 CPLD þróunar-/forritararáð til að meta eða forrita ATF15xx ISP CPLD tæki í mismunandi pakkagerðum. Það eru fjögur innstungukort í boði fyrir ATF15xx-DK3 sem nær yfir 44-TQFP, 44-PLCC, 84-PLCC og 100-

- TQFP pakkagerðir í ATF15xx fjölskyldu CPLD.

- Hvert millistykki fyrir innstungur inniheldur innstungu fyrir ATF15xx tækið og eru karlkyns hausar á neðri hliðinni, merktir JP1 og JP2. Hausarnir á neðri hliðinni passa saman við kvenkyns hausana á ATF15xx-DK3 borðinu, merkt JP4 og JP3. Fjórir 7-hluta skjáir, þrýstihnapparofar,

- JTAG tengimerki, oscillator, VCCINT, VCCIO og GND á CPLD þróunar-/forritatöflunni eru tengd við ATF15xx tækið á innstungu millistykkinu í gegnum þessi tvö sett af tengjum.

- Efst á 44-TQFP tengi millistykkinu eru fjögur 10 pinna tengi með sömu stærð og JTAG ISP tengi. Pinnar á þessum fjórum tengjum eru tengdir við inntaks- og I/O pinna (nema JTAG pinna) CPLD-marktækisins. Þeir geta verið notaðir til að tengja við sveiflusjá eða rökfræðigreiningartæki til að fanga starfsemi inntaks- og I/O pinna CPLD. Þeir geta einnig verið notaðir til að tengja inntak og I/O pinna CPLD við önnur ytri borð eða tæki til að meta eða prófa kerfisstig.

- Atmel ATF15xx ISP niðurhalssnúra

- ATF15xx ISP niðurhalssnúran (P/N: ATDH1150VPC) tengir LPT tengi tölvunnar við 10 pinna JTAG haus á CPLD Development/Programmer Board eða sérsniðnu hringrásarborði. Þetta er sýnt á mynd 10. Þessi ISP kapall virkar sem biðminni til að jafna JTAG merki á milli LPT tengi tölvunnar og ATF15xx á hringrásarborðinu. Power-On LED á bakhlið 25-pinna karltengishússins gefur til kynna að snúran sé rétt tengd.

- Vertu viss um að kveikt sé á þessari LED áður en þú notar Atmel CPLD ISP hugbúnaðinn (ATMISP).

- Þessi ISP kapall samanstendur af 25 pinna (DB25) karltengi, sem er tengt við LPT tengi tölvunnar. 10 pinna kvenkyns tengið tengist 10 pinna karlkyns JTAG haus á ISP hringrásarborðinu. Rauða litaröndin á borði snúrunni gefur til kynna stefnu pinna 1 á kventappinu. 10 pinna karlinn JTAG haus á CPLD

- Þróunar-/forritaraborð er skautað til að koma í veg fyrir að notendur setji kventappann í ranga átt.

- CPLD þróunar-/forritarasettin innihalda ATF15xx ISP niðurhalssnúruna

(ATDH1150VPC); Hins vegar er einnig hægt að nota aðrar studdar ISP snúrur. Hægt er að nota ATDH1150VPC, ATDH1150USB, ByteBlasterMV og ByteBlasterII snúrurnar fyrir ATF15xx/ASL (5V) og ATF15xxASV/ASVL (3.3V) tækin, en eldri ATDH1150PC og ByteBlaster/ ATFV15 geta verið notaðir fyrir snúrurnar (5V) aðeins.

- Mynd 11 sýnir 10 pinna kvenkyns haus pinout fyrir ATF15xx ISP niðurhalssnúruna. 10 pinna karlkyns haus pinout á PC borðinu (ef það er notað fyrir ISP) verður að passa við þetta pinout.

- Athugið: Hringrásin verður að veita VCC og GND til CPLD ISP snúrunnar í gegnum 10 pinna karlhausinn.

Skýringarmyndir

Tilvísanir og stuðningur

Fyrir frekari tilvísanir í PLD hönnunarhugbúnað og stuðning, skjöl eins og hjálp files, kennsluefni, athugasemdir/skýringar um forrit og notendaleiðbeiningar eru fáanlegar á www.atmel.com.

Atmel ProChip hönnuður hugbúnaður

Tafla 8.ProChip hönnuður tilvísanir og stuðningur

| ProChip hönnuður | Frá aðal ProChip gluggavalmyndinni... |

| Hjálp | Veldu Hjálp > Prochip hönnuður hjálp. |

| Kennsluefni | Veldu Hjálp > Kennsluefni. |

| Þekkt vandamál og lausnir | Veldu Hjálp > Review KPS. |

Atmel WinCUPL hugbúnaður

Tafla 9. WinCUPL tilvísanir og stuðningur

| WinCUPL | Frá aðal WinCUPL gluggavalmyndinni... |

| Hjálp | Veldu Hjálp > Innihald. |

| CUPL forritara tilvísunarhandbók | Veldu Hjálp > Tilvísun CUPL forritara. |

| Kennsluefni | Veldu Hjálp > Atmel upplýsingar > Kennsla1.pdf. |

| Þekkt vandamál og lausnir | Veldu Hjálp > Atmel upplýsingar > CUPL_BUG.pdf. |

Atmel ATMISP hugbúnaður

Tafla 10. ATMISP tilvísanir og stuðningur

| ATMISP | Í aðalvalmynd ATMISP gluggans... |

| Hjálp Files | Veldu Hjálp > Hjálp ISP. |

| Kennsluefni | Veldu Hjálp > ATMISP kennsluefni. |

| Þekkt vandamál og lausnir | Notaðu Windows Explorer vafrann, finndu ATMISP möppuna og opnaðu readme.txt file með ASCII textaritli. |

Atmel POF2JED viðskiptahugbúnaður

Tafla 11. POF2JED tilvísanir og stuðningur

| POF2JED | Frá aðal POF2JED gluggavalmyndinni... |

| ATF15xx viðskiptaumsókn stutt | Veldu Hjálp > Viðskiptavalkostir. |

Tæknileg aðstoð

- Fyrir tæknilega aðstoð varðandi öll Atmel PLD-tengd mál, hafðu samband við Atmel PLD Applications Group á:

- Tölvupóstur pld@atmel.com

- Neyðarlína (+1)408-436-4333

- Stuðningseyðublað á netinu http://support.atmel.com/bin/customer.exe

Endurskoðunarsaga

| Endurskoðun | Dagsetning | Lýsing |

| 3605C | 06/2014 | Uppfærðu skýringarmyndir, sniðmát, lógó og fyrirvarasíðu. Bættu við hlutanum Endurskoðunarsaga. |

| 3605B | 05/2008 |

- Atmel Corporation 1600 Technology Drive, San Jose, CA 95110 USA T: (+1)(408) 441.0311 F: (+1)(408) 436.4200 | www.atmel.com

- © 2014 Atmel Corporation. / Rev.: Atmel-3605C-CPLD-ATF15xx-DK3-Development-Kit-UserGuide_062014.

- Atmel®, Atmel lógó og samsetningar þeirra, Enabling Unlimited Possibilities og aðrir eru skráð vörumerki eða vörumerki Atmel Corporation í Bandaríkjunum og

önnur lönd. Aðrir skilmálar og vöruheiti geta verið vörumerki annarra. - FYRIRVARI: Upplýsingarnar í þessu skjali eru veittar í tengslum við Atmel vörur. Ekkert leyfi, beint eða óbeint, með estoppel eða á annan hátt, á neinum hugverkarétti er veitt með þessu skjali eða í tengslum við sölu á Atmel vörum.

- NEMA EINS OG SEM KOMIÐ er fram í ATMEL SÖLUSKILMÁLUM OG SÖLUSKILYRÐUM sem eru staðsettir á ATMEL WEBSÍÐAN, ATMEL TEKUR ENGA ÁBYRGÐ OG FYRIR EINHVERJU SKÝRI, ÓBEININU EÐA LÖGBEÐA ÁBYRGÐ SEM VARÐUR SÍN, Þ.M.T. IN

- ENGINN ATBYR SKAL ATMEL BÆRA ÁBYRGÐ AF EINHVERJU BEINUM, ÓBEINU, AFLEIDANDI, REFSINGU, SÉRSTAKUM EÐA tilfallandi tjóni (ÞAR á meðal án takmarkana tjóni vegna taps og hagnaðar, truflunar í viðskiptum, EÐA TAPS Á NOTKUNNI) ÞETTA SKJÁL, JAFNVEL ÞÓ ATMEL HEF FYRIR LEYFIÐ UM MÖGULEIKUR SVONA SKAÐA.

- Atmel gefur engar yfirlýsingar eða ábyrgðir með tilliti til nákvæmni eða heilleika innihalds þessa

skjal og áskilur sér rétt til að gera breytingar á forskriftum og vörulýsingum hvenær sem er án fyrirvara. Atmel skuldbindur sig ekki til að uppfæra upplýsingarnar sem hér er að finna. Nema annað sé sérstaklega tekið fram, eru Atmel vörur ekki hentugar fyrir, og má ekki nota í, bílum. Atmel vörur eru ekki ætlaðar, heimilaðar eða ábyrgðar til notkunar sem íhlutir í forritum sem ætlað er að styðja við eða viðhalda lífi. - FYRIRVARI UM ÖRYGGISKRITÍKUR, HER OG BÍFIRÍÐARFYRIRVARI: Atmel vörur eru ekki hannaðar fyrir og verða ekki notaðar í tengslum við nein forrit þar sem með sanngirni má búast við að bilun slíkra vara muni leiða til verulegra líkamstjóna eða dauða („öryggismikilvæg forrit“) án sérstaks skriflegs Atmel yfirmanns.

- samþykki. Öryggis-kritísk forrit fela í sér, án takmarkana, björgunarbúnað og kerfi, búnað eða kerfi til að reka kjarnorkuver og vopnakerfi.

- Atmel vörur eru hvorki hannaðar né ætlaðar til notkunar í hernaðar- eða geimferðaþjónustu eða umhverfi nema Atmel hafi sérstaklega tilnefnt sem hernaðargildi. Atmel vörur eru hvorki hannaðar né ætlaðar til notkunar í bílaframkvæmdum nema sérstaklega sé tilgreint af Atmel sem bílaflokka.

- Sótt frá: Arrow.com.

Skjöl / auðlindir

|

Atmel ATF15xx-DK3 CPLD þróunar-/forritarasett [pdfNotendahandbók ATF15xx-DK3 CPLD þróunarforritarasett, ATF15xx-DK3, CPLD þróunarforritarasett, þróunarforritarasett, forritarasett |