Κιτ ανάπτυξης/προγραμματιστή Atmel ATF15xx-DK3 CPLD

Εισαγωγή

Το Atmel® ATF15xx-DK3 Complex Programmable Logic Device (CPLD) Development/Programmer Kit είναι ένα πλήρες σύστημα ανάπτυξης και ένας προγραμματιστής In-System Programming (ISP) για την Atmel ATF15xx Οικογένεια βιομηχανικών τυποποιημένων ακίδων CPLD με δυνατότητες Logic Doubling®. Αυτό το κιτ παρέχει στους σχεδιαστές έναν πολύ γρήγορο και εύκολο τρόπο να αναπτύξουν πρωτότυπα και να αξιολογήσουν νέα σχέδια με έναν ATF15xx ISP CPLD. Η οικογένεια των ISP CPLD ATF15xx περιλαμβάνει τα Atmel ATF15xxAS, ATF15xxASL, ATF15xxASV και ATF15xxASVL CPLD. Με τη διαθεσιμότητα των διαφορετικών πλακών προσαρμογέων υποδοχής για την υποστήριξη των περισσότερων τύπων πακέτων(1) που προσφέρονται στην οικογένεια ISP CPLD ATF15xx, αυτό το κιτ μπορεί να χρησιμοποιηθεί ως προγραμματιστής ISP για τον προγραμματισμό των ATF15xx ISP CPLD στους περισσότερους από τους διαθέσιμους τύπους πακέτων (1) μέσω του βιομηχανικού προτύπου JTAG διεπαφή (IEEE 1149.1).

Περιεχόμενα κιτ

- Atmel CPLD Development/Programmer Board (P/N: ATF15xx-DK3)

- Πλακέτα προσαρμογέα υποδοχής TQFP 44 ακίδων Atmel (P/N: ATF15xx-DK3-SAA44)(2)

- Atmel ATF15xx LPT JTAG Καλώδιο λήψης ISP (P/N: ATDH1150VPC)

- Δύο Atmel 44-pin TQFP Sample Συσκευές

Υποστήριξη συσκευής

Το κιτ ανάπτυξης/προγραμματιστή ATF15xx-DK3 CPLD υποστηρίζει τις ακόλουθες συσκευές σε όλους τους διαθέσιμους βαθμούς και πακέτα ταχύτητας Atmel (εκτός από το 100-PQFP):

- ATF1502AS/ASL

- ATF1504AS/ASL

- ATF1508ASV/ASVL

- ATF1502ASV

- ATF1504ASV/ASVL

- ATF1508AS/ASL

- Η πλακέτα προσαρμογέα υποδοχής δεν προσφέρεται για το PQFP 100 ακίδων.

- Μόνο η πλακέτα προσαρμογέα υποδοχής TQFP 44 ακίδων περιλαμβάνεται σε αυτό το κιτ. Άλλες πλακέτες προσαρμογέα υποδοχής πωλούνται χωριστά. Ανατρέξτε στην ενότητα «Περιγραφή υλικού» για περισσότερες πληροφορίες σχετικά με τους κωδικούς παραγγελίας πλακέτας προσαρμογέα υποδοχής.i

Χαρακτηριστικά κιτ

Συμβούλιο Ανάπτυξης/Προγραμματιστή CPLD

- 10 ακίδων JTAG- Θύρα ISP

- Ρυθμιζόμενα κυκλώματα τροφοδοσίας για πηγή τροφοδοσίας 9VDC

- Επιλέξιμο 5V, 3.3V, 2.5V ή 1.8VI/O Voltagε Προμήθεια

- Επιλέξιμο 1.8V, 3.3V ή 5.0V Core Voltagε Προμήθεια

- Πλακέτα προσαρμογέα υποδοχής TQFP 44 ακίδων

- Κεφαλίδες για ακίδες εισόδου/εξόδου της συσκευής ATF15xx

- Κρυσταλλικός Ταλαντωτής 2MHz

- Τέσσερις οθόνες LED 7 τμημάτων

- Οκτώ μεμονωμένα LED

- Οκτώ διακόπτες με κουμπιά

- Καθολική εκκαθάριση και έξοδος Ενεργοποίηση διακοπτών με κουμπιά

- Τρέχοντες άλτες μέτρησης

Λογικός διπλασιασμός CPLD

ATF15xx ISP CPLD με Logic Doubling Architecture

- Καλώδιο λήψης ATF15xx ISP

- Καλώδιο λήψης ISP 5V, 3.3V, 2.5V ή 1.8V για θύρα παράλληλου εκτυπωτή (LPT) υπολογιστή

- Λογισμικό ανάπτυξης PLD

- Τα εργαλεία λογισμικού ανάπτυξης Atmel PLD είναι διαθέσιμα στο διαδίκτυο για χρήση από τον σχεδιαστή PLD των ATF15xx ISP CPLD. Ανατρέξτε στο Overview έγγραφο, «PLD

- Λογισμικό σχεδίασης Πάνωview” διαθέσιμο στο:

- http://www.atmel.com/images/atmel-3629-pld-design-software-overview.pdf

Απαιτήσεις συστήματος

- Το ελάχιστο υλικό και λογισμικό που απαιτείται για τον προγραμματισμό μιας συσκευής ATF15xx ISP CPLD που έχει σχεδιαστεί χρησιμοποιώντας το λογισμικό Atmel ProChip Designer στην πλακέτα ανάπτυξης/προγραμματιστή CPLD μέσω του Atmel ATMISP v6.x (ATF15xx CPLD ISP Software) είναι:

- x86 Υπολογιστής με μικροεπεξεργαστή

- Windows XP®, Windows® 98, Windows NT® 4.0 ή Windows 2000

- RAM 128 MByte

- 500-MByte ελεύθερος χώρος στον σκληρό δίσκο

- Ποντίκι που υποστηρίζεται από Windows

- Διαθέσιμη θύρα παράλληλου εκτυπωτή (LPT).

- Τροφοδοτικό 9VDC με ρεύμα τροφοδοσίας 500mA

- Οθόνη SVGA (ανάλυση 800 x 600)

Πληροφορίες Παραγγελίας

| Αριθμός ανταλλακτικού Atmel | Περιγραφή |

| ATF15xx-DK3 | Κιτ ανάπτυξης/προγραμματιστή CPLD (περιλαμβάνει το ATF15xxDK3-SAA44*) |

| ATF15xxDK3-SAA100 | Πλακέτα προσαρμογέα υποδοχής TQFP 100 ακίδων για πλακέτα DK3 |

| ATF15xxDK3-SAJ44 | Πλακέτα προσαρμογέα υποδοχής PLCC 44 ακίδων για πλακέτα DK3 |

| ATF15xxDK3-SAJ84 | Πλακέτα προσαρμογέα υποδοχής PLCC 84 ακίδων για πλακέτα DK3 |

| ATF15xxDK3-SAA44* | Πλακέτα προσαρμογέα υποδοχής TQFP 44 ακίδων για πλακέτα DK3 |

Περιγραφή υλικού

Συμβούλιο Ανάπτυξης/Προγραμματιστή CPLD

- Οι πλακέτες CPLD Development/Programmer και Socket Adapter που φαίνονται στο παρακάτω σχήμα περιέχουν λειτουργίες που είναι χρήσιμες για την ανάπτυξη, τη δημιουργία πρωτοτύπων ή την αξιολόγηση

- Σχέδια ATF15xx CPLD. Χαρακτηριστικά που το καθιστούν ένα πολύ ευέλικτο κιτ εκκίνησης/ανάπτυξης και προγραμματιστή ISP για την οικογένεια ATF15xx του JTAG-Τα ISP CPLD περιλαμβάνουν:

- Διακόπτες με κουμπιά

- LED

- Οθόνες 7 τμημάτων

- Κρυσταλλικός Ταλαντωτής 2MHz

- Επιλογέας VCCIO 5V, 3.3V, 2.5V ή 1.8V

- Επιλογέας VCCINT 1.8V, 3.3V ή 5.0V

- JTAG Θύρα ISP

- Προσαρμογείς Socket

- Εμφανίσεις 7 τμημάτων με επιλέξιμους βραχυκυκλωτήρες

- Η πλακέτα ανάπτυξης/προγραμματιστή CPLD περιέχει τέσσερις οθόνες 7 τμημάτων που επιτρέπουν την παρατήρηση των εξόδων ATF15xx CPLD. Αυτές οι τέσσερις οθόνες χαρακτηρίζονται ως DSP1, DSP2, DSP3 και DSP4. Οι οθόνες 7 τμημάτων έχουν κοινές λυχνίες LED ανόδου με τις κοινές γραμμές ανόδου συνδεδεμένες στο VCCIO (Τόμος τροφοδοσίας I/Otage για το CPLD) μέσω μιας σειράς αντιστάσεων με επιλέξιμους βραχυκυκλωτήρες με την ένδειξη JPDSP1, JPDSP2, JPDSP3 και JPDSP4. Αυτά τα jumper μπορούν να αφαιρεθούν σε

απενεργοποιήστε τις οθόνες αποσυνδέοντας το VCCIO στις οθόνες. Μεμονωμένες γραμμές καθόδου συνδέονται με τις ακίδες I/O του ATF15xx CPLD στο CPLD - Κιτ ανάπτυξης/προγραμματιστή. Για να ενεργοποιήσετε ένα συγκεκριμένο τμήμα, συμπεριλαμβανομένου του DOT μιας οθόνης, η αντίστοιχη ακίδα εισόδου/εξόδου ATF15xx που είναι συνδεδεμένη σε αυτό το τμήμα LED πρέπει να βρίσκεται σε λογικά χαμηλή κατάσταση με το αντίστοιχο επιλεγμένο σετ βραχυκυκλωτήρα. Επομένως, οι έξοδοι της συσκευής ATF15xx θα απαιτούν διαμόρφωση για ενεργές-χαμηλές εξόδους στη σχεδίαση file. Οι οθόνες λειτουργούν καλύτερα σε 2.5 V VCCIO ή υψηλότερη.

- Κάθε τμήμα κάθε οθόνης είναι συνδεδεμένο με έναν συγκεκριμένο ακροδέκτη I/O της συσκευής ATF15xx. Για τις συσκευές υψηλότερου αριθμού ακίδων (100 ακίδων και μεγαλύτερες), και τα επτά τμήματα και τα τμήματα DOT των τεσσάρων οθονών συνδέονται με τις ακίδες I/O. Ωστόσο, για τις συσκευές χαμηλότερου αριθμού ακίδων, μόνο ένα υποσύνολο των οθονών, η πρώτη και η τέταρτη οθόνη, συνδέονται με τις ακίδες εισόδου/εξόδου της συσκευής ATF15xx. Οι πίνακες 1 και 2 δείχνουν τις συνδέσεις του πακέτου οθόνης 7 τμημάτων με τη συσκευή ATF15xx. Το σχηματικό κύκλωμα των οθονών και των βραχυκυκλωτών φαίνεται στο παρακάτω σχήμα.

Εικόνα 2. Διάγραμμα κυκλώματος οθόνης 7 τμημάτων και βραχυκυκλωτήρες

Πίνακας 1.ATF15xx Συνδέσεις 44 ακίδων σε οθόνες 7 τμημάτων

| TQFP 44 ακίδων | |||

| DSP/Τμήμα | PLD Pin | DSP/Τμήμα | PLD Pin |

| 1/Α | 27 | 3/Α | NC |

| 1/Β | 33 | 3/Β | NC |

| 1/C | 30 | 3/C | NC |

| 1/Δ | 21 | 3/Δ | NC |

| 1 / Ε | 18 | 3 / Ε | NC |

| 1 / ΣΤ | 23 | 3 / ΣΤ | NC |

| 1 / G | 20 | 3 / G | NC |

| 1/ΤΕΛΕΙΑ | 31 | 3/ΤΕΛΕΙΑ | NC |

| 2/Α | NC | 4/Α | 3 |

| 2/Β | NC | 4/Β | 10 |

| 2/C | NC | 4/C | 6 |

| 2/Δ | NC | 4/Δ | 43 |

| 2 / Ε | NC | 4 / Ε | 35 |

| 2 / ΣΤ | NC | 4 / ΣΤ | 42 |

| 2 / G | NC | 4 / G | 34 |

| 2/ΤΕΛΕΙΑ | NC | 4/ΤΕΛΕΙΑ | 11 |

| PLCC 44 ακίδων | |||

| DSP/Τμήμα | PLD Pin | DSP/Τμήμα | PLD Pin |

| 1/Α | 33 | 3/Α | NC |

| 1/Β | 39 | 3/Β | NC |

| 1/C | 36 | 3/C | NC |

| 1/Δ | 27 | 3/Δ | NC |

| 1 / Ε | 24 | 3 / Ε | NC |

| 1 / ΣΤ | 29 | 3 / ΣΤ | NC |

| 1 / G | 26 | 3 / G | NC |

| 1/ΤΕΛΕΙΑ | 37 | 3/ΤΕΛΕΙΑ | NC |

| 2/Α | NC | 4/Α | 9 |

| 2/Β | NC | 4/Β | 16 |

| 2/C | NC | 4/C | 12 |

| 2/Δ | NC | 4/Δ | 5 |

| 2 / Ε | NC | 4 / Ε | 41 |

| 2 / ΣΤ | NC | 4 / ΣΤ | 4 |

| 2 / G | NC | 4 / G | 40 |

| 2/ΤΕΛΕΙΑ | NC | 4/ΤΕΛΕΙΑ | 17 |

Πίνακας 2.ATF15xx 84 ακίδων και 100 ακίδων Συνδέσεις σε οθόνες 7 τμημάτων

| PLCC 84 ακίδων | |||

| DSP/Τμήμα | PLD Pin | DSP/Τμήμα | PLD Pin |

| 1/Α | 68 | 3/Α | 22 |

| 1/Β | 74 | 3/Β | 28 |

| 1/C | 70 | 3/C | 25 |

| 1/Δ | 63 | 3/Δ | 21 |

| 1 / Ε | 58 | 3 / Ε | 16 |

| 1 / ΣΤ | 65 | 3 / ΣΤ | 17 |

| 1 / G | 61 | 3 / G | 12 |

| 1/ΤΕΛΕΙΑ | 73 | 3/ΤΕΛΕΙΑ | 29 |

| 2/Α | 52 | 4/Α | 5 |

| 2/Β | 57 | 4/Β | 10 |

| 2/C | 55 | 4/C | 8 |

| 2/Δ | 48 | 4/Δ | 79 |

| 2 / Ε | 41 | 4 / Ε | 76 |

| 2 / ΣΤ | 50 | 4 / ΣΤ | 77 |

| 2 / G | 45 | 4 / G | 75 |

| 2/ΤΕΛΕΙΑ | 50 | 4/ΤΕΛΕΙΑ | 11 |

| TQFP 100 ακίδων | |||

| DSP/Τμήμα | PLD Pin | DSP/Τμήμα | PLD Pin |

| 1/Α | 67 | 3/Α | 13 |

| 1/Β | 71 | 3/Β | 19 |

| 1/C | 69 | 3/C | 16 |

| 1/Δ | 61 | 3/Δ | 8 |

| 1 / Ε | 57 | 3 / Ε | 83 |

| 1 / ΣΤ | 64 | 3 / ΣΤ | 6 |

| 1 / G | 60 | 3 / G | 92 |

| 1/ΤΕΛΕΙΑ | 75 | 3/ΤΕΛΕΙΑ | 20 |

| 2/Α | 52 | 4/Α | 100 |

| 2/Β | 54 | 4/Β | 94 |

| 2/C | 47 | 4/C | 97 |

| 2/Δ | 41 | 4/Δ | 81 |

| 2 / Ε | 46 | 4 / Ε | 76 |

| 2 / ΣΤ | 40 | 4 / ΣΤ | 80 |

| 2 / G | 45 | 4 / G | 79 |

| 2/ΤΕΛΕΙΑ | 56 | 4/ΤΕΛΕΙΑ | 93 |

LED με επιλέξιμους βραχυκυκλωτήρες

Η πλακέτα ανάπτυξης/προγραμματιστή CPLD διαθέτει οκτώ μεμονωμένες λυχνίες LED, οι οποίες επιτρέπουν στους σχεδιαστές να εμφανίζουν τα σήματα εξόδου από τις εισόδους/εξόδους χρήστη των συσκευών ATF15xx. Αυτά τα οκτώ LED φέρουν την ένδειξη LED1 έως LED8 στην πλακέτα ανάπτυξης/προγραμματιστή CPLD. Η κάθοδος κάθε LED συνδέεται με τη γείωση (GND) μέσω μιας αντίστασης σειράς, ενώ η άνοδος κάθε LED συνδέεται με έναν ακροδέκτη I/O χρήστη του CPLD μέσω του JPL1/2/3/4/5/6/7 /8 επιλέξιμο βραχυκυκλωτήρα. Αυτοί οι βραχυκυκλωτήρες μπορούν να αφαιρεθούν για να απενεργοποιηθούν τα LED αποσυνδέοντας τις ανόδους των LED στις ακίδες I/O του CPLD. Το παρακάτω σχήμα απεικονίζει το διάγραμμα κυκλώματος των LED με τους βραχυκυκλωτήρες επιλογής.

Για να ενεργοποιήσετε μια συγκεκριμένη λυχνία LED, η αντίστοιχη ακίδα εισόδου/εξόδου ATF15xx που είναι συνδεδεμένη με τη λυχνία LED πρέπει να βρίσκεται σε λογική υψηλή κατάσταση με το αντίστοιχο σετ βραχυκυκλωτήρα. Επομένως, οι έξοδοι της συσκευής ATF15xx θα πρέπει να διαμορφωθούν ως ενεργές έξοδοι υψηλής ταχύτητας. Τα LED λειτουργούν καλύτερα σε 2.5V VCCIO ή υψηλότερη.

Οι συσκευές κατώτερου αριθμού ακίδων (44 ακίδων) έχουν μόνο τέσσερις εισόδους/εξόδους συνδεδεμένες σε LED1/2/3/4. Για τις συσκευές με υψηλότερο αριθμό ακίδων (100 ακίδων και μεγαλύτερες), και οι οκτώ LED συνδέονται στα I/O της συσκευής. Ο Πίνακας 3 δείχνει τις διαφορετικές συνδέσεις πακέτων των εισόδων/εξόδων CPLD με τις λυχνίες LED.

Πίνακας 3.ATF15xx Συνδέσεις με LED

| TQFP 44 ακίδων | |

| LED | PLD Pin |

| LED1 | 28 |

| LED2 | 25 |

| LED3 | 22 |

| LED4 | 19 |

| PLCC 44 ακίδων | |

| LED | PLD Pin |

| LED1 | 34 |

| LED2 | 31 |

| LED3 | 28 |

| LED4 | 25 |

| PLCC 84 ακίδων | |

| LED | PLD Pin |

| LED1 | 69 |

| LED2 | 67 |

| LED3 | 64 |

| LED4 | 60 |

| LED5 | 27 |

| LED6 | 24 |

| LED7 | 18 |

| LED8 | 15 |

| TQFP 100 ακίδων | |

| LED | PLD Pin |

| LED1 | 68 |

| LED2 | 65 |

| LED3 | 63 |

| LED4 | 58 |

| LED5 | 17 |

| LED6 | 14 |

| LED7 | 10 |

| LED8 | 9 |

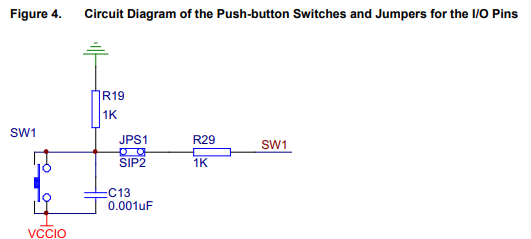

Διακόπτες με κουμπιά με επιλέξιμους βραχυκυκλωτήρες για ακίδες εισόδου/εξόδου

- Η πλακέτα ανάπτυξης/προγραμματιστή CPLD περιέχει οκτώ διακόπτες με κουμπιά, οι οποίοι συνδέονται με τις ακίδες I/O του CPLD. Οι διακόπτες στέλνουν λογικά σήματα εισόδου στις ακίδες εισόδου/εξόδου χρήστη της συσκευής ATF15xx. Αυτοί οι διακόπτες φέρουν την ένδειξη SW1 έως SW8 στον CPLD Development/Programmer

Επιτροπή. Το ένα άκρο κάθε μπουτόν διακόπτη εισόδου συνδέεται στο VCCIO, ενώ το άλλο άκρο κάθε διακόπτη κουμπιού συνδέεται με μια αντίσταση πτυσσόμενης και στη συνέχεια συνδέεται με τον ειδικό ακροδέκτη I/O του CPLD μέσω του JPS1/2 /3/4/5/6/7/8 επιλέξιμο βραχυκυκλωτήρα. - Εάν πατηθεί οποιοσδήποτε από αυτούς τους διακόπτες και ρυθμιστεί ο αντίστοιχος βραχυκυκλωτήρας, ο συγκεκριμένος ακροδέκτης I/O της συσκευής θα οδηγηθεί σε μια λογική υψηλή κατάσταση από την έξοδο του κυκλώματος διακόπτη. Δεδομένου ότι κάθε διακόπτης με κουμπιά συνδέεται επίσης με μια πτυσσόμενη αντίσταση, η είσοδος θα έχει μια λογική χαμηλή κατάσταση εάν ο διακόπτης δεν πατηθεί με το αντίστοιχο σετ βραχυκυκλωτήρα. Εάν ο βραχυκυκλωτήρας του κουμπιού δεν έχει ρυθμιστεί, ο αντίστοιχος πείρος θα αντιμετωπιστεί ως μη συνδεδεμένος πείρος. Το σχήμα 4 είναι ένα διάγραμμα κυκλώματος του διακόπτη με μπουτόν και του επιλέξιμου βραχυκυκλωτήρα. Ο Πίνακας 4 δείχνει τις συνδέσεις αυτών των οκτώ διακοπτών με κουμπιά με τις ακίδες εισόδου/εξόδου CPLD στους διαφορετικούς τύπους πακέτων.

Πίνακας 4.ATF15xx Συνδέσεις στους διακόπτες ακίδων I/O

| TQFP 44 ακίδων | |

| Πιέστε το κουμπί | PLD Pin |

| SW1 | 15 |

| SW2 | 14 |

| SW3 | 13 |

| SW4 | 12 |

| SW5 | 8 |

| SW6 | 5 |

| SW7 | 2 |

| SW8 | 44 |

| PLCC 44 ακίδων | |

| Πιέστε το κουμπί | PLD Pin |

| SW1 | 21 |

| SW2 | 20 |

| SW3 | 19 |

| SW4 | 18 |

| SW5 | 14 |

| SW6 | 11 |

| SW7 | 8 |

| SW8 | 6 |

| PLCC 84 ακίδων | |

| Πιέστε το κουμπί | PLD Pin |

| SW1 | 54 |

| SW2 | 51 |

| SW3 | 49 |

| SW4 | 44 |

| SW5 | 9 |

| SW6 | 6 |

| SW7 | 4 |

| SW8 | 80 |

| TQFP 100 ακίδων | |

| Πιέστε το κουμπί | PLD Pin |

| SW1 | 48 |

| SW2 | 36 |

| SW3 | 44 |

| SW4 | 37 |

| SW5 | 96 |

| SW6 | 98 |

| SW7 | 84 |

| SW8 | 99 |

Διακόπτες με κουμπιά με επιλέξιμους βραχυκυκλωτήρες για ακίδες GCLR και OE1

Η πλακέτα ανάπτυξης/προγραμματιστή CPLD περιέχει δύο διακόπτες με κουμπιά για τις ακίδες Global Clear (GCLR) και Output Enable (OE1) του CPLD. Οι διακόπτες ελέγχουν τις λογικές καταστάσεις των εισόδων OE1 και GCLR των συσκευών ATF15xx. Αυτοί οι διακόπτες φέρουν τις ετικέτες SW-GCLR και SW-GOE1 στην πλακέτα. Το ένα άκρο του διακόπτη εισόδου SW-GCLR είναι συνδεδεμένο στο GND. Το άλλο άκρο του

ο διακόπτης του κουμπιού συνδέεται με μια αντίσταση έλξης στο VCCIO και στη συνέχεια συνδέεται στον ειδικό ακροδέκτη εισόδου GCLR της συσκευής ATF15xx. Προορίζεται να χρησιμοποιηθεί ως σήμα ενεργής-χαμηλής επαναφοράς για την επαναφορά των καταχωρητών στη συσκευή ATF15xx με το επιλεγμένο σετ βραχυκυκλωτήρα JPGCLR. Ομοίως, το ένα άκρο του διακόπτη εισόδου SW-GOE1 είναι συνδεδεμένο στο GND. Το άλλο άκρο του διακόπτη με μπουτόν

συνδέεται με μια pull-up αντίσταση στο VCCIO και στη συνέχεια συνδέεται στον ειδικό ακροδέκτη εισόδου OE1 της συσκευής ATF15xx. Προορίζεται να χρησιμοποιηθεί ως ενεργό σήμα ενεργοποίησης χαμηλής εξόδου για τον έλεγχο της ενεργοποίησης/απενεργοποίησης των buffer εξόδου τριών καταστάσεων στο ATF15xx με το επιλεγμένο σετ βραχυκυκλωτήρα JPGOE. Το σχήμα 5 είναι το διάγραμμα κυκλώματος των διακοπτών με κουμπιά και των βραχυκυκλωτικών για τους ακροδέκτες GCLR και OE1.

Εάν πατηθεί οποιοσδήποτε από αυτούς τους διακόπτες πλήκτρων και ρυθμιστεί ο αντίστοιχος βραχυκυκλωτήρας, η συγκεκριμένη I/O του CPLD θα οδηγηθεί σε μια λογική χαμηλή κατάσταση. Δεδομένου ότι κάθε κουμπί είναι επίσης συνδεδεμένο με μια αντίσταση έλξης, η αντίστοιχη είσοδος CPLD θα έχει μια λογική υψηλή κατάσταση εάν δεν πατηθεί ο διακόπτης του κουμπιού με το αντίστοιχο επιλεγμένο σετ βραχυκυκλωτήρα. Εάν ο επιλέξιμος βραχυκυκλωτήρας δεν έχει ρυθμιστεί, η αντίστοιχη ειδική ακίδα εισόδου του CPLD μπορεί να θεωρηθεί ως ακροδέκτης No Connect (NC). Ο Πίνακας 5 δείχνει τους αριθμούς ακίδων των ειδικών ακίδων εισόδου GCLR και OE1 των συσκευών ATF15xx σε όλους τους διαθέσιμους τύπους πακέτων.

Εικόνα 5. Διάγραμμα κυκλώματος διακοπτών κουμπιού και επιλέξιμων βραχυκυκλωτικών για GCLR και OE1

Πίνακας 5.Pin Numbers of GCLR and OE1

| TQFP 44 ακίδων | PLCC 44 ακίδων | PLCC 84 ακίδων | TQFP 100 ακίδων | |

| GCLR | 39 | 1 | 1 | 89 |

| OE1 | 38 | 44 | 84 | 88 |

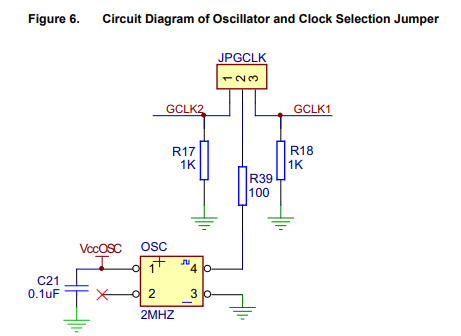

Ταλαντωτής 2MHz και Jumper επιλογής ρολογιού

Ο βραχυκυκλωτήρας επιλογής ρολογιού με την ένδειξη JP-GCLK στην πλακέτα ανάπτυξης/προγραμματιστή CPLD είναι ένας βραχυκυκλωτήρας δύο θέσεων που επιτρέπει στους χρήστες να επιλέξουν ποια ειδική ακίδα εισόδου GCLK (είτε GCLK1 είτε GCLK2) της συσκευής ATF15xx θα πρέπει να συνδεθεί στην έξοδο της Ταλαντωτής 2MHz. Επιπλέον, ο βραχυκυκλωτήρας μπορεί να αφαιρεθεί για να επιτραπεί η σύνδεση μιας εξωτερικής πηγής ρολογιού στο GCLK1 ή/και στο GCLK2 της συσκευής ATF15xx. Το σχήμα 6 είναι μια απεικόνιση του διαγράμματος κυκλώματος του ταλαντωτή και του βραχυκυκλωτήρα επιλογής. Ο Πίνακας 6 δείχνει τους αριθμούς ακίδων για τους ειδικούς ακροδέκτες εισόδου GCLK1 και GCLK2 της συσκευής ATF15xx σε όλους τους διαφορετικούς διαθέσιμους τύπους πακέτων.

Εάν ο βραχυκυκλωτήρας GCLK1 είναι ρυθμισμένος, ο βραχυκυκλωτήρας θα βρίσκεται στο πλάι της πλακέτας. Από την άλλη πλευρά, εάν έχει ρυθμιστεί ο βραχυκυκλωτήρας GCLK2, ο βραχυκυκλωτήρας θα βρίσκεται προς τη μέση της πλακέτας.

Πίνακας 6. Αριθμοί ακίδων GCLK1 και GCLK2

| TQFP 44 ακίδων | PLCC 44 ακίδων | PLCC 84 ακίδων | TQFP 100 ακίδων | |

| GCLK1 | 37 | 43 | 83 | 87 |

| GCLK2 | 40 | 2 | 2 | 90 |

VCCIO and VCCINT Voltage Επιλογή Jumpers και LED

- Το VCCIO and VCCINT Voltage Selection Jumpers, με την ένδειξη VCCIO Selector και VCCINT Selector αντίστοιχα στο ATF15xx-DK3 Development/Programming Kit, επιτρέπουν την επιλογή της παροχής I/O

- τόμtage επίπεδο (VCCIO) και βασική παροχή voltage επίπεδο (VCCINT) που χρησιμοποιούνται για το στόχο CPLD στο κιτ. Μόλις ρυθμιστούν σωστά αυτοί οι βραχυκυκλωτήρες, τα LED (με την ετικέτα VCCINT LED και VCCIO LED) θα ανάψουν. ωστόσο, σε χαμηλότερη προσφορά voltagεπίπεδα (δηλαδή 2.5 V ή χαμηλότερα), τα LED μπορεί να είναι πολύ αμυδρά.

- Για CPLD ATF15xxAS/ASL (5.0V), τόσο οι βραχυκυκλωτήρες VCCIO Selector όσο και VCCINT Selector πρέπει να ρυθμιστούν στα 5.0V.

- Για ATF15xxASV/ASVL (3.3V) CPLD, τόσο ο Επιλογέας VCCIO όσο και ο Επιλογέας VCCINT πρέπει να ρυθμιστούν μόνο σε 3.3 V.

- Η τροφοδοσία του κιτ ανάπτυξης/προγραμματιστή CPLD πρέπει να απενεργοποιηθεί όταν αλλάζετε τη θέση του VCCIO ή του VCCINT Voltage Jumper επιλογής (επιλογέας VCCIO ή επιλογέας VCCINT).

- ICCIO και ICCINT Jumpers

- Οι βραχυκυκλωτήρες ICCIO και ICCINT μπορούν να αφαιρεθούν και να χρησιμοποιηθούν ως σημεία μέτρησης ICC. Όταν αφαιρεθούν οι βραχυκυκλωτήρες, οι μετρητές ρεύματος μπορούν να συνδεθούν στους στύλους για τη μέτρηση της τρέχουσας κατανάλωσης του στοχευόμενου CPLD. Όταν οι χρήστες δεν χρησιμοποιούν αυτούς τους βραχυκυκλωτήρες για να μετρήσουν το ρεύμα, αυτοί οι βραχυκυκλωτήρες πρέπει να ρυθμιστούν για να λειτουργούν το κιτ και το CPLD.

- Τομtage Ρυθμιστές

- Δύο τόμtagΟι ρυθμιστές e, με τις ετικέτες VR1 και VR2, χρησιμοποιούνται για να παράγουν και να ρυθμίζουν ανεξάρτητα

- VCCINT και VCCIO τομtagείναι από το τροφοδοτικό 9VDC. Για λεπτομέρειες, δείτε το σχηματικό κιτ ATF15xx-DK3, Εικόνα 12.

- Διακόπτης τροφοδοσίας και LED τροφοδοσίας

- Ο διακόπτης τροφοδοσίας, με την ένδειξη POWER SWITCH, μπορεί να αλλάξει στη θέση ενεργοποίησης ή απενεργοποίησης, η οποία χρησιμοποιείται για την ενεργοποίηση ή απενεργοποίηση της πλακέτας ATF15xx-DK3 αντίστοιχα. Επιτρέπει το 9VDC voltagε στην υποδοχή τροφοδοσίας για να περάσετε στον τόμtage ρυθμιστές όταν είναι στη θέση on. Όταν ο διακόπτης τροφοδοσίας είναι ενεργοποιημένος, το LED τροφοδοσίας (με την ένδειξη POWER LED) θα ανάψει για να υποδείξει ότι το κιτ ATF15xx-DK3 τροφοδοτείται με ρεύμα.

- Υποδοχή τροφοδοτικού και κεφαλίδα τροφοδοτικού

- Η πλακέτα ATF15xx-DK3 περιέχει δύο διαφορετικούς τύπους υποδοχών τροφοδοσίας με την ένδειξη JPower και JP Power. Οποιοσδήποτε από αυτούς τους συνδέσμους τροφοδοσίας μπορεί να χρησιμοποιηθεί για τη σύνδεση μιας πηγής τροφοδοσίας 9VDC στο κιτ. Ο πρώτος σύνδεσμος τροφοδοσίας με την ένδειξη JPower, είναι μια υποδοχή τροφοδοσίας κάννης με στύλο διαμέτρου 2.1 mm και συνδυάζεται με θηλυκό βύσμα 2.1 mm (εσωτερική διάμετρος) x 5.5 mm (εξωτερική διάμετρος). Η δεύτερη κεφαλίδα τροφοδοτικού με την ένδειξη JP Power, είναι μια αρσενική κεφαλίδα 4 ακίδων 0.100″ με τετράγωνους στύλους 0.025″. Η διαθεσιμότητα αυτών των δύο τύπων υποδοχών τροφοδοσίας επιτρέπει στους χρήστες να επιλέξουν τον τύπο εξοπλισμού τροφοδοσίας που θα χρησιμοποιήσουν για το κιτ ανάπτυξης/προγραμματιστή ATF15xx-DK3.

- Μόνο ένας από αυτούς τους δύο συνδέσμους τροφοδοτικού θα πρέπει να τροφοδοτείται με πηγή 9VDC αλλά όχι και τα δύο ταυτόχρονα.

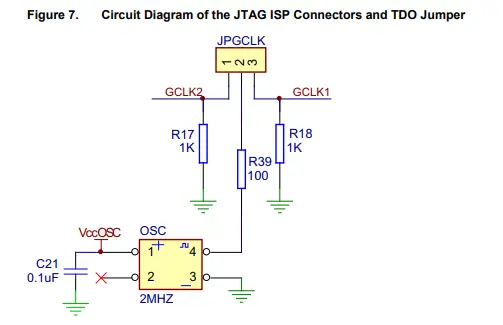

- JTAG ISP Connector και TDO Selection Jumper

- Το JTAG Υποδοχή ISP με την ένδειξη JTAG-IN, χρησιμοποιείται για τη σύνδεση του ATF15xx JTAG ακροδέκτες θύρας (TCK, TDI, TMS και TDO) μέσω του καλωδίου λήψης ISP στη θύρα παράλληλου εκτυπωτή (LPT) ενός υπολογιστή για JTAG Προγραμματισμός ISP της συσκευής ATF15xx. Οι πολωμένες υποδοχές χρησιμοποιούνται στο ATF15xx-DK3 και στο καλώδιο λήψης ISP για την ελαχιστοποίηση των προβλημάτων σύνδεσης. Η ετικέτα PIN1 στο κάτω μέρος του JTAG Η υποδοχή ISP υποδεικνύει τη θέση ακίδας 1 της κεφαλίδας 10 ακίδων και μειώνει περαιτέρω την πιθανότητα εσφαλμένης σύνδεσης του καλωδίου λήψης ISP.

- Στα αριστερά του JTAG-Σύνδεσμος IN, υπάρχουν δύο στήλες vias και φέρουν την ετικέτα JTAG-ΕΞΩ. Σκοπός τους είναι να επιτρέπουν στους χρήστες να δημιουργήσουν ένα JTAG αλυσίδα μαργαρίτα για να εκτελέσει το JTAG λειτουργίες σε πολλές συσκευές. Οι χρήστες θα πρέπει να κολλήσουν τον ίδιο τύπο συνδετήρα με αυτόν που χρησιμοποιείται για το JTAG-ΜΕΣΑ στο JTAG- Θέση OUT για να χρησιμοποιήσετε αυτήν τη διαθέσιμη δυνατότητα.

- Για να δημιουργήσετε ένα JTAG Η αλυσίδα μαργαρίτα που χρησιμοποιεί πολλαπλές πλακέτες ATF15xx-DK3, ο βραχυκυκλωτήρας επιλογής TDO, με την ένδειξη JP-TDO, πρέπει να ρυθμιστεί στην κατάλληλη θέση. Για όλες τις συσκευές στην αλυσίδα της μαργαρίτας εκτός από την τελευταία συσκευή, αυτός ο βραχυκυκλωτήρας πρέπει να ρυθμιστεί στη θέση ΣΤΗΝ ΕΠΟΜΕΝΗ ΣΥΣΚΕΥΗ. Για την τελευταία συσκευή στην αλυσίδα, αυτός ο βραχυκυκλωτήρας πρέπει να ρυθμιστεί στη θέση TO ISP CABLE. Όταν αυτός ο βραχυκυκλωτήρας βρίσκεται στη θέση ΣΤΗΝ ΕΠΟΜΕΝΗ ΣΥΣΚΕΥΗ, το TDO του συγκεκριμένου JTAG συσκευή θα συνδεθεί στο TDI του επόμενου

- JTAG συσκευή στην αλυσίδα. Όταν αυτός ο βραχυκυκλωτήρας βρίσκεται στη θέση TO ISP CABLE, το TDO αυτής της συσκευής θα συνδεθεί στο TDO του JTAG Υποδοχή 10 ακίδων, η οποία θα επιτρέψει στο σήμα TDO της συγκεκριμένης συσκευής στην αλυσίδα να μεταδοθεί πίσω στον κεντρικό υπολογιστή με το λογισμικό ISP. Το παρακάτω σχήμα είναι ένα διάγραμμα κυκλώματος του

- JTAG συνδέσμους και το βραχυκυκλωτήρα JP-TDO. Ο παρακάτω πίνακας παραθέτει τους αριθμούς ακίδων των τεσσάρων JTAG pins για τη συσκευή ATF15xx σε όλα τα διαθέσιμα πακέτα.

Για μια μεμονωμένη ρύθμιση συσκευής, η θέση του βραχυκυκλωτήρα JP-TDO πρέπει να ρυθμιστεί σε TO ISP CABLE.

Εικόνα 7. Διάγραμμα κυκλώματος του JTAG ISP Connectors και TDO Jumper

- Πίνακας 7.Pin Numbers of JTAG Σήματα λιμένων

| TQFP 44 ακίδων | PLCC 44 ακίδων | PLCC 84 ακίδων | TQFP 100 ακίδων | |

| TDI | 1 | 7 | 14 | 4 |

| TDO | 32 | 38 | 71 | 73 |

| TMS | 7 | 13 | 23 | 15 |

| TCK | 26 | 32 | 62 | 62 |

Ο αλγόριθμος ISP ελέγχεται από το λογισμικό ATMISP, το οποίο εκτελείται στον υπολογιστή. Οι τέσσερις ΤζTAG Τα σήματα δημιουργούνται από τη θύρα LPT και αποθηκεύονται στην προσωρινή μνήμη από το καλώδιο λήψης του ISP πριν μεταβούν στη συσκευή ATF15xx στην πλακέτα CPLD Development/Programmer. Το 10-pin JTAG Το pinout Port Header στην πλακέτα CPLD Development/Programmer φαίνεται στο Σχήμα 8 και οι διαστάσεις αυτού του αρσενικού J 10 ακίδωνTAG Η κεφαλίδα φαίνεται στο σχήμα 9.

Εικόνα 8. 10 ακίδων JTAG Port Header Pinout

- Το 10-pin JTAG Το pinout Port Header είναι συμβατό με το καλώδιο που βασίζεται στη θύρα ATDH1150PC/VPC LPT και το καλώδιο που βασίζεται στη θύρα USB ATDH1150USB, καθώς και με το Altera

- Καλώδια βασισμένα σε θύρες ByteBlaster/MV/II LPT. Επιπλέον, το λογισμικό ATMISP v6.7 επιτρέπει τη χρήση είτε του Atmel

- Καλώδιο ATDH1150PC/VPC/USB ή το καλώδιο ByteBlaster/MV/II για την υλοποίηση του ISP.

- Το ATMISP v7.0 υποστηρίζει μόνο το καλώδιο ATDH1150USB.

- Πλακέτα προσαρμογέα υποδοχής

- Οι πλακέτες προσαρμογέα υποδοχής ανάπτυξης/προγραμματιστή ATF15xx-DK3 CPLD (ATF15xx-DK3-XXXXXXX) είναι πλακέτες κυκλωμάτων που διασυνδέονται με την πλακέτα ανάπτυξης/προγραμματιστή ATF15xx-DK3 CPLD. Χρησιμοποιούνται σε συνδυασμό με τον πίνακα ανάπτυξης/προγραμματιστή ATF15xx-DK3 CPLD για την αξιολόγηση ή τον προγραμματισμό συσκευών ATF15xx ISP CPLD σε διαφορετικούς τύπους πακέτων. Υπάρχουν τέσσερις πλακέτες προσαρμογέα υποδοχής για το ATF15xx-DK3 που καλύπτουν τα 44-TQFP, 44-PLCC, 84-PLCC και 100-

- Τύποι πακέτων TQFP στην οικογένεια CPLD ATF15xx.

- Κάθε πλακέτα προσαρμογέα υποδοχής περιέχει μια υποδοχή για τη συσκευή ATF15xx και έχει αρσενικές κεφαλίδες στην κάτω πλευρά, με τις ετικέτες JP1 και JP2. Οι κεφαλίδες στην κάτω πλευρά συνδυάζονται με τις θηλυκές κεφαλίδες στην πλακέτα ATF15xx-DK3, με τις ετικέτες JP4 και JP3. Οι τέσσερις οθόνες 7 τμημάτων, οι διακόπτες με κουμπιά,

- JTAG Τα σήματα θύρας, ο ταλαντωτής, το VCCINT, το VCCIO και το GND στην πλακέτα ανάπτυξης/προγραμματιστή CPLD συνδέονται με τη συσκευή ATF15xx στην πλακέτα προσαρμογέα υποδοχής μέσω αυτών των δύο σετ υποδοχών.

- Στο επάνω μέρος του προσαρμογέα υποδοχής 44-TQFP, υπάρχουν τέσσερις υποδοχές 10 ακίδων με τις ίδιες διαστάσεις με το JTAG Υποδοχή ISP. Οι ακίδες αυτών των τεσσάρων βυσμάτων συνδέονται με τους ακροδέκτες εισόδου και εισόδου/εξόδου (εκτός από τα τέσσερα JTAG καρφίτσες) της συσκευής στόχου CPLD. Μπορούν να χρησιμοποιηθούν για σύνδεση σε παλμογράφο ή λογικό αναλυτή για την καταγραφή των δραστηριοτήτων των ακίδων εισόδου και εισόδου/εξόδου του CPLD. Μπορούν επίσης να χρησιμοποιηθούν για τη σύνδεση των ακίδων εισόδου και εισόδου/εξόδου του CPLD σε άλλες εξωτερικές πλακέτες ή συσκευές για αξιολόγηση ή δοκιμή επιπέδου συστήματος.

- Καλώδιο λήψης ISP Atmel ATF15xx

- Το καλώδιο λήψης ISP ATF15xx (P/N: ATDH1150VPC) συνδέει τη θύρα LPT του υπολογιστή με το J 10 ακίδωνTAG κεφαλίδα στην πλακέτα ανάπτυξης/προγραμματιστή CPLD ή σε μια προσαρμοσμένη πλακέτα κυκλώματος. Αυτό φαίνεται στην Εικόνα 10. Αυτό το καλώδιο ISP λειτουργεί ως buffer για την προσωρινή αποθήκευση του JTAG σήματα μεταξύ της θύρας LPT του υπολογιστή και του ATF15xx στην πλακέτα κυκλώματος. Η λυχνία LED ενεργοποίησης στο πίσω μέρος του περιβλήματος του αρσενικού βύσματος 25 ακίδων υποδεικνύει ότι το καλώδιο έχει συνδεθεί σωστά.

- Βεβαιωθείτε ότι αυτή η λυχνία LED είναι ενεργοποιημένη πριν χρησιμοποιήσετε το λογισμικό Atmel CPLD ISP (ATMISP).

- Αυτό το καλώδιο ISP αποτελείται από έναν αρσενικό σύνδεσμο 25 ακίδων (DB25), ο οποίος είναι συνδεδεμένος στη θύρα LPT ενός υπολογιστή. Το θηλυκό βύσμα 10 ακίδων συνδέεται με το αρσενικό J 10 ακίδωνTAG κεφαλίδα στην πλακέτα κυκλώματος ISP. Η κόκκινη χρωματική λωρίδα στο καλώδιο της κορδέλας υποδεικνύει τον προσανατολισμό του πείρου 1 του θηλυκού βύσματος. Ο αρσενικός 10 ακίδων JTAG κεφαλίδα στο CPLD

- Η πλακέτα ανάπτυξης/προγραμματιστή είναι πολωμένη για να εμποδίζει τους χρήστες να εισάγουν το θηλυκό βύσμα σε λάθος προσανατολισμό.

- Τα κιτ ανάπτυξης/προγραμματιστή CPLD περιλαμβάνουν το καλώδιο λήψης ISP ATF15xx

(ATDH1150VPC); Ωστόσο, μπορούν να χρησιμοποιηθούν και άλλα υποστηριζόμενα καλώδια ISP. Τα καλώδια ATDH1150VPC, ATDH1150USB, ByteBlasterMV και ByteBlasterII μπορούν να χρησιμοποιηθούν για τις συσκευές ATF15xx/ASL (5V) και ATF15xxASV/ASVL (3.3V), ενώ οι παλαιότερες συσκευές ATDH1150ByTASF μπορούν να χρησιμοποιηθούν για το ATDH15 (5V) μόνο.

- Το σχήμα 11 απεικονίζει το θηλυκό pinout κεφαλίδας 10 ακίδων για το καλώδιο λήψης ISP ATF15xx. Το αρσενικό pinout κεφαλίδας 10 ακίδων στην πλακέτα του υπολογιστή (εάν χρησιμοποιείται για ISP) πρέπει να ταιριάζει με αυτό το pinout.

- Σημείωμα: Η πλακέτα κυκλώματος πρέπει να παρέχει VCC και GND στο καλώδιο ISP CPLD μέσω της αρσενικής κεφαλίδας 10 ακίδων.

Σχηματικά Διαγράμματα

Αναφορές και Υποστήριξη

Για πρόσθετες αναφορές λογισμικού σχεδιασμού PLD και υποστήριξη, τεκμηρίωση όπως βοήθεια files, σεμινάρια, σημειώσεις/συνοπτικές πληροφορίες για την εφαρμογή και οδηγούς χρήσης είναι διαθέσιμα στη διεύθυνση www.atmel.com.

Atmel ProChip Designer Software

Πίνακας 8. Αναφορές και υποστήριξη σχεδιαστή ProChip

| Σχεδιαστής ProChip | Από το κύριο μενού του παραθύρου ProChip… |

| Βοήθεια | Επιλέγω Βοήθεια > Βοήθεια Prochip Designer. |

| Φροντιστήρια | Επιλέγω Βοήθεια > Φροντιστήρια. |

| Γνωστά προβλήματα και λύσεις | Επιλέγω Βοήθεια > Review KPS. |

Λογισμικό Atmel WinCUPL

Πίνακας 9. Αναφορές και υποστήριξη WinCUPL

| WinCUPL | Από το κύριο μενού παραθύρου WinCUPL… |

| Βοήθεια | Επιλέγω Βοήθεια > Περιεχόμενα. |

| Οδηγός αναφοράς προγραμματιστών CUPL | Επιλέγω Βοήθεια > Αναφορά προγραμματιστών CUPL. |

| Φροντιστήρια | Επιλέγω Βοήθεια > Πληροφορίες Atmel > Tutorial1.pdf. |

| Γνωστά προβλήματα και λύσεις | Επιλέγω Βοήθεια > Πληροφορίες Atmel > CUPL_BUG.pdf. |

Λογισμικό Atmel ATMISP

Πίνακας 10. Αναφορές και υποστήριξη ATMISP

| ATMISP | Από το κύριο μενού παραθύρου ATMISP… |

| Βοήθεια Files | Επιλέγω Βοήθεια > Βοήθεια ISP. |

| Φροντιστήρια | Επιλέγω Βοήθεια > ATMISP Tutorial. |

| Γνωστά προβλήματα και λύσεις | Χρησιμοποιώντας το πρόγραμμα περιήγησης Windows Explorer, εντοπίστε το φάκελο ATMISP και ανοίξτε το readme.txt file με ένα πρόγραμμα επεξεργασίας κειμένου ASCII. |

Λογισμικό μετατροπής Atmel POF2JED

Πίνακας 11. Αναφορές και υποστήριξη POF2JED

| POF2JED | Από το κύριο μενού παραθύρου POF2JED… |

| Σύνοψη εφαρμογής μετατροπής ATF15xx | Επιλέγω Βοήθεια > Επιλογές μετατροπής. |

Τεχνική Υποστήριξη

- Για τεχνική υποστήριξη σε θέματα που σχετίζονται με το Atmel PLD, επικοινωνήστε με την ομάδα εφαρμογών Atmel PLD στη διεύθυνση:

- E-mail pld@atmel.com

- Γραμμή επικοινωνίας (+1)408-436-4333

- Ηλεκτρονική φόρμα υποστήριξης http://support.atmel.com/bin/customer.exe

Ιστορικό αναθεώρησης

| Αναθεώρηση | Ημερομηνία | Περιγραφή |

| 3605C | 06/2014 | Ενημερώστε τα σχήματα, το πρότυπο, τα λογότυπα και τη σελίδα αποποίησης ευθύνης. Προσθέστε την ενότητα Ιστορικό αναθεωρήσεων. |

| 3605Β | 05/2008 |

- Atmel Corporation 1600 Technology Drive, San Jose, CA 95110 USA T: (+1)(408) 441.0311 F: (+1)(408) 436.4200 | www.atmel.com

- © 2014 Atmel Corporation. / Αναθ.: Atmel-3605C-CPLD-ATF15xx-DK3-Development-Kit-UserGuide_062014.

- Το Atmel®, το λογότυπο Atmel και συνδυασμοί τους, το Enabling Unlimited Possibilities και άλλα είναι σήματα κατατεθέντα ή εμπορικά σήματα της Atmel Corporation στις ΗΠΑ και

άλλες χώρες. Άλλοι όροι και ονόματα προϊόντων μπορεί να είναι εμπορικά σήματα άλλων. - ΑΡΝΗΣΗ: Οι πληροφορίες σε αυτό το έγγραφο παρέχονται σε σχέση με τα προϊόντα της Atmel. Καμία άδεια, ρητή ή σιωπηρή, με estoppel ή με άλλο τρόπο, για οποιοδήποτε δικαίωμα πνευματικής ιδιοκτησίας δεν χορηγείται από αυτό το έγγραφο ή σε σχέση με την πώληση προϊόντων Atmel.

- ΕΚΤΟΣ ΟΣΟΝ ΔΙΑΘΕΤΕΙ ΣΤΟΥΣ ΟΡΟΥΣ ΚΑΙ ΠΡΟΫΠΟΘΕΣΕΙΣ ΠΩΛΗΣΕΩΝ ATMEL ΠΟΥ ΕΝΤΟΠΙΖΟΝΤΑΙ ΣΤΟ ATMEL WEBΗ ΙΣΤΟΣΕΛΙΔΑ, Η ATMEL ΔΕΝ ΑΝΑΛΑΜΒΑΝΕΙ ΚΑΜΙΑ ΕΥΘΥΝΗ ΚΑΙ ΑΠΟΠΟΙΕΙΤΑΙ ΟΠΟΙΑΔΗΠΟΤΕ ΡΗΤΗ, ΣΙΩΠΗΡΗ Ή ΝΟΜΙΚΕΣ ΕΓΓΥΗΣΗ ΣΧΕΤΙΚΑ ΜΕ ΤΑ ΠΡΟΪΟΝΤΑ ΤΟΥ ΣΥΜΠΕΡΙΛΑΜΒΑΝΟΜΕΝΩΝ, ΑΛΛΑ ΔΕΝ ΠΕΡΙΟΡΙΣΤΟΥΝ, ΤΗΝ ΣΙΩΠΗΡΗ ΕΓΓΥΗΣΗ ΤΗΣ ΕΓΓΥΗΣΗΣ, ΠΑΡΑΒΑΣΗ. ΣΕ

- ΚΑΝΕΝΑ ΓΕΓΟΝΟΣ ΔΕΝ ΕΧΕΙ ΕΥΘΥΝΗ ΓΙΑ ΟΠΟΙΑΔΗΠΟΤΕ ΑΜΕΣΗ, ΕΜΜΕΣΗ, ΕΠΑΓΓΕΛΜΑΤΙΚΗ, ΤΙΜΩΡΙΚΗ, ΕΙΔΙΚΕΣ Ή ΣΥΜΠΙΤΙΚΕΣ ΖΗΜΙΕΣ (ΣΥΜΠΕΡΙΛΑΜΒΑΝΟΜΕΝΩΝ, ΧΩΡΙΣ ΠΕΡΙΟΡΙΣΜΟ, ΖΗΜΙΕΣ ΓΙΑ ΑΠΩΛΕΙΑ ΚΑΙ ΚΕΡΔΗ, ΑΠΟΤΕΛΕΣΜΑΤΑ). ΤΗΣ ΧΡΗΣΗΣ Ή ΑΔΥΝΑΜΙΑΣ ΧΡΗΣΗΣ ΑΥΤΟ ΤΟ ΕΓΓΡΑΦΟ, ΑΚΟΜΑ ΚΑΙ ΑΝ Η ATMEL ΕΧΕΙ ΕΝΗΜΕΡΩΘΕΙ ΓΙΑ ΤΗΝ ΠΙΘΑΝΟΤΗΤΑ ΤΕΤΟΙΩΝ ΖΗΜΙΩΝ.

- Η Atmel δεν παρέχει καμία δήλωση ή εγγύηση σχετικά με την ακρίβεια ή την πληρότητα του περιεχομένου αυτού

τεκμηριώνει και διατηρεί το δικαίωμα να κάνει αλλαγές στις προδιαγραφές και τις περιγραφές των προϊόντων ανά πάσα στιγμή χωρίς προειδοποίηση. Η Atmel δεν δεσμεύεται να ενημερώσει τις πληροφορίες που περιέχονται στο παρόν. Εκτός εάν ορίζεται διαφορετικά, τα προϊόντα της Atmel δεν είναι κατάλληλα και δεν πρέπει να χρησιμοποιούνται σε εφαρμογές αυτοκινήτων. Τα προϊόντα Atmel δεν προορίζονται, εγκρίνονται ή καλύπτονται από εγγύηση για χρήση ως εξαρτήματα σε εφαρμογές που προορίζονται για υποστήριξη ή διατήρηση ζωής. - ΑΠΟΠΟΙΗΣΗ ΕΥΘΥΝΗΣ ΕΦΑΡΜΟΓΩΝ ΑΣΦΑΛΕΙΑΣ ΚΡΙΣΙΜΕΣ, ΣΤΡΑΤΙΩΤΙΚΕΣ ΚΑΙ ΑΥΤΟΚΙΝΗΤΟΥ: Τα προϊόντα Atmel δεν έχουν σχεδιαστεί και δεν θα χρησιμοποιηθούν σε σχέση με εφαρμογές όπου η αποτυχία τέτοιων προϊόντων αναμένεται εύλογα να οδηγήσει σε σημαντικό τραυματισμό ή θάνατο («Ασφαλείς-Κρίσιμες Εφαρμογές») χωρίς τη συγκεκριμένη γραπτή δήλωση αξιωματικού της Atmel

- συγκατάθεση. Οι κρίσιμες για την ασφάλεια Εφαρμογές περιλαμβάνουν, χωρίς περιορισμό, συσκευές υποστήριξης ζωής και συστήματα, εξοπλισμό ή συστήματα για τη λειτουργία πυρηνικών εγκαταστάσεων και οπλικών συστημάτων.

- Τα προϊόντα της Atmel δεν έχουν σχεδιαστεί ούτε προορίζονται για χρήση σε στρατιωτικές ή αεροδιαστημικές εφαρμογές ή περιβάλλοντα, εκτός εάν ορίζονται ρητά από την Atmel ως στρατιωτικής ποιότητας. Τα προϊόντα της Atmel δεν έχουν σχεδιαστεί ούτε προορίζονται για χρήση σε εφαρμογές αυτοκινήτων, εκτός εάν ορίζονται ρητά από την Atmel ως αυτοκινητοβιομηχανίας.

- Λήψη από: Arrow.com.

Έγγραφα / Πόροι

|

Κιτ ανάπτυξης/προγραμματιστή Atmel ATF15xx-DK3 CPLD [pdf] Οδηγός χρήστη ATF15xx-DK3 CPLD Development Programmer Kit, ATF15xx-DK3, CPLD Development Programmer Kit, Development Programmer Kit, Programmer Kit |