Atmel ATF15xx-DK3 CPLD ຊຸດພັດທະນາ/ໂປຣແກຣມເມີ

ແນະນຳ

Atmel® ATF15xx-DK3 Complex Programmable Logic Device (CPLD) Development/Programmer Kit is a complete development system and an in-System Programming (ISP) programmer for the Atmel ATF15xx Family of Industry standard pin compatible CPLDs with Logic Doubling® features. ຊຸດນີ້ໃຫ້ນັກອອກແບບເປັນວິທີທີ່ງ່າຍ ແລະໄວຫຼາຍໃນການພັດທະນາຕົ້ນແບບ ແລະປະເມີນການອອກແບບໃໝ່ດ້ວຍ ATF15xx ISP CPLD. ຄອບຄົວ ATF15xx ຂອງ ISP CPLD ລວມມີ Atmel ATF15xxAS, ATF15xxASL, ATF15xxASV, ແລະ ATF15xxASVL CPLDs. ດ້ວຍຄວາມພ້ອມຂອງກະດານອະແດບເຕີ socket ທີ່ແຕກຕ່າງກັນເພື່ອສະຫນັບສະຫນູນປະເພດແພັກເກັດສ່ວນໃຫຍ່ (1) ທີ່ສະເຫນີຢູ່ໃນຄອບຄົວ ATF15xx ຂອງ ISP CPLDs, ຊຸດນີ້ສາມາດຖືກນໍາໃຊ້ເປັນໂປລແກລມ ISP ເພື່ອດໍາເນີນໂຄງການ ATF15xx ISP CPLDs ໃນສ່ວນໃຫຍ່ຂອງປະເພດແພັກເກັດທີ່ມີຢູ່. (1) ຜ່ານມາດຕະຖານອຸດສາຫະກໍາ JTAG ການໂຕ້ຕອບ (IEEE 1149.1).

ເນື້ອໃນຊຸດ

- ຄະນະກໍາມະການພັດທະນາ/ນັກຂຽນໂປຣແກຣມ Atmel CPLD (P/N: ATF15xx-DK3)

- Atmel 44-pin TQFP Socket Adapter Board (P/N: ATF15xx-DK3-SAA44)(2)

- Atmel ATF15xx LPT-based JTAG ສາຍດາວໂຫຼດ ISP (P/N: ATDH1150VPC)

- ສອງ Atmel 44-pin TQFP Sample ອຸປະກອນ

ຮອງຮັບອຸປະກອນ

ATF15xx-DK3 CPLD Development/Programmer Kit ຮອງຮັບອຸປະກອນຕໍ່ໄປນີ້ໃນທຸກເກຣດ ແລະແພັກເກັດຄວາມໄວ Atmel ທີ່ມີຢູ່ໃນປັດຈຸບັນ (ຍົກເວັ້ນ 100-PQFP):

- ATF1502AS/ASL

- ATF1504AS/ASL

- ATF1508ASV/ASVL

- ATF1502ASV

- ATF1504ASV/ASVL

- ATF1508AS/ASL

- ກະດານອະແດບເຕີຊັອກເກັດບໍ່ໄດ້ຖືກສະຫນອງໃຫ້ສໍາລັບ PQFP 100-pin.

- ມີແຕ່ກະດານອະແດບເຕີຊ່ອງສຽບ TQFP 44-pin ເທົ່ານັ້ນທີ່ລວມຢູ່ໃນຊຸດນີ້. ກະດານອະແດບເຕີ socket ອື່ນໆແມ່ນຂາຍແຍກຕ່າງຫາກ. ເບິ່ງພາກ, “ລາຍລະອຽດຂອງຮາດແວ” ສໍາລັບຂໍ້ມູນເພີ່ມເຕີມກ່ຽວກັບ socket adapter board ordering codes.i

ຄຸນນະສົມບັດຊຸດ

CPLD ຄະນະພັດທະນາ/ນັກຂຽນໂປຣແກຣມ

- 10-pin JTAG- ຜອດ ISP

- ຄວບຄຸມວົງຈອນການສະຫນອງພະລັງງານສໍາລັບແຫຼ່ງພະລັງງານ 9VDC

- ເລືອກໄດ້ 5V, 3.3V, 2.5V, ຫຼື 1.8VI/O Voltage ການສະ ໜອງ

- ເລືອກໄດ້ 1.8V, 3.3V, ຫຼື 5.0V Core Voltage ການສະ ໜອງ

- ກະດານອະແດບເຕີຊັອກເກັດ TQFP 44-pin

- ສ່ວນຫົວສຳລັບ I/O Pins ຂອງອຸປະກອນ ATF15xx

- 2MHz Crystal Oscillator

- ຈໍສະແດງຜົນ LED 7 ຕອນ XNUMX ອັນ

- ແປດ LEDs ສ່ວນບຸກຄົນ

- ປຸ່ມກົດປຸ່ມແປດ

- Global Clear ແລະ Output ເປີດໃຊ້ປຸ່ມກົດປຸ່ມ

- Jumpers ການວັດແທກປະຈຸບັນ

Logic ເພີ່ມ CPLDs ສອງເທົ່າ

ATF15xx ISP CPLD ກັບ Logic Doubling Architecture

- ສາຍດາວໂຫຼດ ATF15xx ISP

- 5V, 3.3V, 2.5V, ຫຼື 1.8V ISP ສາຍດາວໂຫຼດສໍາລັບ PC Parallel Printer (LPT) Port

- ຊອບແວພັດທະນາ PLD

- ເຄື່ອງມືຊອຟແວການພັດທະນາ Atmel PLD ແມ່ນມີຢູ່ໃນອອນໄລນ໌ສໍາລັບການນໍາໃຊ້ຂອງຜູ້ອອກແບບ PLD ຂອງ ATF15xx ISP CPLDs. ກະລຸນາອ້າງອິງ Overview ເອກະສານ, “PLD

- ຊອບແວອອກແບບຫຼາຍກວ່າview"ມີຢູ່:

- http://www.atmel.com/images/atmel-3629-pld-design-software-overview.pdf

ຄວາມຕ້ອງການລະບົບ

- ຮາດແວ ແລະ ຊອບແວຂັ້ນຕ່ຳທີ່ຕ້ອງການເພື່ອຂຽນໂປຣແກຣມອຸປະກອນ ATF15xx ISP CPLD ເຊິ່ງຖືກອອກແບບໂດຍໃຊ້ຊອບແວອອກແບບ Atmel ProChip ເທິງກະດານພັດທະນາ/ໂປຣແກຣມ CPLD ຜ່ານ Atmel ATMISP v6.x (ATF15xx CPLD ISP Software) ແມ່ນ:

- x86 ຄອມພິວເຕີທີ່ໃຊ້ Microprocessor

- Windows XP®, Windows® 98, Windows NT® 4.0, ຫຼື Windows 2000

- RAM 128-MByte

- ພື້ນທີ່ຮາດດິດຟຣີ 500-MByte

- ຫນູທີ່ຮອງຮັບ Windows

- ພອດເຄື່ອງພິມຂະໜານ (LPT) ທີ່ມີຢູ່

- ການສະຫນອງພະລັງງານ 9VDC ກັບ 500mA ຂອງກະແສໄຟຟ້າ

- ຈໍພາບ SVGA (800 x 600 ຄວາມລະອຽດ)

ຂໍ້ມູນການສັ່ງຊື້

| ເລກສ່ວນ Atmel | ລາຍລະອຽດ |

| ATF15xx-DK3 | ຊຸດການພັດທະນາ/ໂປຣແກຣມເມີ CPLD (ລວມທັງ ATF15xxDK3-SAA44*) |

| ATF15xxDK3-SAA100 | 100-pin TQFP Socket Adapter Board ສໍາລັບ DK3 Board |

| ATF15xxDK3-SAJ44 | 44-pin PLCC Socket Adapter Board ສໍາລັບ DK3 Board |

| ATF15xxDK3-SAJ84 | 84-pin PLCC Socket Adapter Board ສໍາລັບ DK3 Board |

| ATF15xxDK3-SAA44* | 44-pin TQFP Socket Adapter Board ສໍາລັບ DK3 Board |

ລາຍລະອຽດຮາດແວ

CPLD ຄະນະພັດທະນາ/ນັກຂຽນໂປຣແກຣມ

- CPLD Development/Programmer and Socket Adapter Boards ທີ່ສະແດງຢູ່ໃນຮູບຂ້າງລຸ່ມນີ້ປະກອບດ້ວຍຄຸນສົມບັດທີ່ເປັນປະໂຫຍດສໍາລັບການພັດທະນາ, prototyping, ຫຼືການປະເມີນຜົນ.

- ການອອກແບບ ATF15xx CPLD. ຄຸນນະສົມບັດທີ່ເຮັດໃຫ້ນີ້ເປັນຊຸດເລີ່ມຕົ້ນ / ການພັດທະນາທີ່ຫລາກຫລາຍແລະເປັນໂປລແກລມ ISP ສໍາລັບຄອບຄົວ ATF15xx ຂອງ J.TAG-ISP CPLDs ປະກອບມີ:

- ປຸ່ມກົດປຸ່ມ

- ໄຟ LED

- ການສະແດງ 7 ຕອນ

- 2MHz Crystal Oscillator

- 5V, 3.3V, 2.5V, ຫຼື 1.8V VCCIO ເລືອກ

- 1.8V, 3.3V, ຫຼື 5.0V VCCINT Selector

- JTAG ຜອດ ISP

- Socket Adapters

- 7-segment displays with selectable jumpers

- ຄະນະກໍາມະການພັດທະນາ / ໂປລແກລມ CPLD ມີສີ່ສະແດງ 7 ພາກສ່ວນທີ່ອະນຸຍາດໃຫ້ສັງເກດເຫັນຜົນໄດ້ຮັບຂອງ ATF15xx CPLD. ຈໍສະແດງຜົນທັງສີ່ອັນນີ້ຖືກຕິດສະຫຼາກເປັນ DSP1, DSP2, DSP3, ແລະ DSP4. ຈໍສະແດງຜົນ 7-segment ມີ LED anode ທົ່ວໄປທີ່ມີສາຍ anode ທົ່ວໄປທີ່ເຊື່ອມຕໍ່ກັບ VCCIO (I/O supply voltage ສໍາລັບ CPLD) ຜ່ານຊຸດຂອງຕົວຕ້ານທານທີ່ມີ jumpers ທີ່ສາມາດເລືອກໄດ້ທີ່ມີປ້າຍຊື່ JPDSP1, JPDSP2, JPDSP3, ແລະ JPDSP4. jumpers ເຫຼົ່ານີ້ສາມາດໄດ້ຮັບການໂຍກຍ້າຍອອກ

ປິດການໃຊ້ງານຈໍສະແດງຜົນໂດຍການຖອນການເຊື່ອມຕໍ່ VCCIO ກັບຈໍສະແດງຜົນ. ສາຍ cathode ສ່ວນບຸກຄົນແມ່ນເຊື່ອມຕໍ່ກັບ pins I/O ຂອງ ATF15xx CPLD ໃນ CPLD - ຊຸດພັດທະນາ/ໂປຣແກຣມເມີ. ເພື່ອເປີດພາກສ່ວນໃດນຶ່ງ, ລວມທັງ DOT ຂອງຈໍສະແດງຜົນ, PIN I/O ATF15xx ທີ່ສອດຄ້ອງກັນທີ່ເຊື່ອມຕໍ່ກັບພາກສ່ວນ LED ນີ້ຈະຕ້ອງຢູ່ໃນສະຖານະຕ່ໍາຕາມເຫດຜົນກັບຊຸດ jumper ເລືອກທີ່ສອດຄ້ອງກັນ; ດັ່ງນັ້ນ, ຜົນໄດ້ຮັບຂອງອຸປະກອນ ATF15xx ຈະຮຽກຮ້ອງໃຫ້ມີການຕັ້ງຄ່າສໍາລັບຜົນຜະລິດຕ່ໍາໃນການອອກແບບ. file. ຈໍສະແດງຜົນເຮັດວຽກດີທີ່ສຸດຢູ່ທີ່ 2.5V VCCIO ຫຼືສູງກວ່າ.

- ແຕ່ລະພາກສ່ວນຂອງແຕ່ລະຈໍສະແດງຜົນແມ່ນເຊື່ອມຕໍ່ຍາກກັບ PIN I/O ສະເພາະຂອງອຸປະກອນ ATF15xx. ສຳລັບອຸປະກອນນັບ PIN ທີ່ສູງກວ່າ (100-pin ແລະໃຫຍ່ກວ່າ), ທັງໝົດເຈັດສ່ວນ ແລະພາກສ່ວນ DOT ຂອງຈໍສະແດງຜົນທັງ 15 ແມ່ນເຊື່ອມຕໍ່ກັບ PIN I/O; ຢ່າງໃດກໍຕາມ, ສໍາລັບອຸປະກອນນັບ PIN ຕ່ໍາ, ພຽງແຕ່ຊຸດຍ່ອຍຂອງຈໍສະແດງຜົນ, ຈໍສະແດງຜົນທໍາອິດແລະສີ່, ແມ່ນເຊື່ອມຕໍ່ກັບ PINs I/O ຂອງອຸປະກອນ ATF1xx. ຕາຕະລາງ 2 ແລະ 7 ສະແດງການເຊື່ອມຕໍ່ແພັກເກັດສະແດງ 15 ສ່ວນກັບອຸປະກອນ ATFXNUMXxx. ຕາຕະລາງວົງຈອນຂອງຈໍສະແດງຜົນແລະ jumpers ແມ່ນສະແດງຢູ່ໃນຮູບຂ້າງລຸ່ມນີ້.

ຮູບທີ 2. ແຜນວາດວົງຈອນຂອງຈໍສະແດງຜົນ 7 ພາກສ່ວນ ແລະ Jumpers

ຕາຕະລາງ 1.ATF15xx 44-pin ການເຊື່ອມຕໍ່ກັບ 7-segment Displays

| 44-pin TQFP | |||

| DSP/Segment | PLD Pin | DSP/Segment | PLD Pin |

| 1/ກ | 27 | 3/ກ | NC |

| 1/B | 33 | 3/B | NC |

| 1/ຄ | 30 | 3/ຄ | NC |

| 1/ງ | 21 | 3/ງ | NC |

| 1/ສ | 18 | 3/ສ | NC |

| 1/F | 23 | 3/F | NC |

| 1/G | 20 | 3/G | NC |

| 1/DOT | 31 | 3/DOT | NC |

| 2/ກ | NC | 4/ກ | 3 |

| 2/B | NC | 4/B | 10 |

| 2/ຄ | NC | 4/ຄ | 6 |

| 2/ງ | NC | 4/ງ | 43 |

| 2/ສ | NC | 4/ສ | 35 |

| 2/F | NC | 4/F | 42 |

| 2/G | NC | 4/G | 34 |

| 2/DOT | NC | 4/DOT | 11 |

| 44-pin PLCC | |||

| DSP/Segment | PLD Pin | DSP/Segment | PLD Pin |

| 1/ກ | 33 | 3/ກ | NC |

| 1/B | 39 | 3/B | NC |

| 1/ຄ | 36 | 3/ຄ | NC |

| 1/ງ | 27 | 3/ງ | NC |

| 1/ສ | 24 | 3/ສ | NC |

| 1/F | 29 | 3/F | NC |

| 1/G | 26 | 3/G | NC |

| 1/DOT | 37 | 3/DOT | NC |

| 2/ກ | NC | 4/ກ | 9 |

| 2/B | NC | 4/B | 16 |

| 2/ຄ | NC | 4/ຄ | 12 |

| 2/ງ | NC | 4/ງ | 5 |

| 2/ສ | NC | 4/ສ | 41 |

| 2/F | NC | 4/F | 4 |

| 2/G | NC | 4/G | 40 |

| 2/DOT | NC | 4/DOT | 17 |

ຕາຕະລາງ 2.ATF15xx 84-pin ແລະ 100-pin ການເຊື່ອມຕໍ່ກັບການສະແດງ 7-segment

| 84-pin PLCC | |||

| DSP/Segment | PLD Pin | DSP/Segment | PLD Pin |

| 1/ກ | 68 | 3/ກ | 22 |

| 1/B | 74 | 3/B | 28 |

| 1/ຄ | 70 | 3/ຄ | 25 |

| 1/ງ | 63 | 3/ງ | 21 |

| 1/ສ | 58 | 3/ສ | 16 |

| 1/F | 65 | 3/F | 17 |

| 1/G | 61 | 3/G | 12 |

| 1/DOT | 73 | 3/DOT | 29 |

| 2/ກ | 52 | 4/ກ | 5 |

| 2/B | 57 | 4/B | 10 |

| 2/ຄ | 55 | 4/ຄ | 8 |

| 2/ງ | 48 | 4/ງ | 79 |

| 2/ສ | 41 | 4/ສ | 76 |

| 2/F | 50 | 4/F | 77 |

| 2/G | 45 | 4/G | 75 |

| 2/DOT | 50 | 4/DOT | 11 |

| 100-pin TQFP | |||

| DSP/Segment | PLD Pin | DSP/Segment | PLD Pin |

| 1/ກ | 67 | 3/ກ | 13 |

| 1/B | 71 | 3/B | 19 |

| 1/ຄ | 69 | 3/ຄ | 16 |

| 1/ງ | 61 | 3/ງ | 8 |

| 1/ສ | 57 | 3/ສ | 83 |

| 1/F | 64 | 3/F | 6 |

| 1/G | 60 | 3/G | 92 |

| 1/DOT | 75 | 3/DOT | 20 |

| 2/ກ | 52 | 4/ກ | 100 |

| 2/B | 54 | 4/B | 94 |

| 2/ຄ | 47 | 4/ຄ | 97 |

| 2/ງ | 41 | 4/ງ | 81 |

| 2/ສ | 46 | 4/ສ | 76 |

| 2/F | 40 | 4/F | 80 |

| 2/G | 45 | 4/G | 79 |

| 2/DOT | 56 | 4/DOT | 93 |

LEDs ມີ Jumpers ເລືອກ

ຄະນະບໍລິຫານການພັດທະນາ / ໂຄງການ CPLD ມີແປດ LEDs ບຸກຄົນ, ເຊິ່ງອະນຸຍາດໃຫ້ຜູ້ອອກແບບເພື່ອສະແດງສັນຍານຜົນຜະລິດຈາກ I/Os ຜູ້ໃຊ້ຂອງອຸປະກອນ ATF15xx. ໄຟ LED ທັງ 1 ອັນນີ້ຖືກຕິດສະຫຼາກ LED8 ເຖິງ LED1 ຢູ່ໃນກະດານພັດທະນາ / Programmer CPLD. cathode ຂອງແຕ່ລະ LED ແມ່ນເຊື່ອມຕໍ່ກັບ Ground (GND) ຜ່ານ resistor ຊຸດ, ໃນຂະນະທີ່ anode ຂອງແຕ່ລະ LED ແມ່ນເຊື່ອມຕໍ່ກັບຜູ້ໃຊ້ I/O pin ຂອງ CPLD ຜ່ານ JPL2/3/4/5/6/7/8. /XNUMX jumper ເລືອກ. jumpers ເຫຼົ່ານີ້ສາມາດໄດ້ຮັບການໂຍກຍ້າຍອອກເພື່ອປິດການໃຊ້ງານ LEDs ໂດຍການຖອນການເຊື່ອມຕໍ່ anodes ຂອງ LEDs ກັບ I/O pins ຂອງ CPLD ໄດ້. ຮູບຂ້າງລຸ່ມນີ້ສະແດງໃຫ້ເຫັນແຜນວາດວົງຈອນຂອງ LEDs ກັບ jumpers ການຄັດເລືອກ.

ເພື່ອເປີດໄຟ LED ໂດຍສະເພາະ, PIN I/O ATF15xx ທີ່ສອດຄ້ອງກັນທີ່ເຊື່ອມຕໍ່ກັບ LED ຕ້ອງຢູ່ໃນສະຖານະສູງຕາມເຫດຜົນກັບຊຸດ jumper ທີ່ສອດຄ້ອງກັນ; ດັ່ງນັ້ນ, ຜົນໄດ້ຮັບຂອງອຸປະກອນ ATF15xx ຈະຕ້ອງຖືກຕັ້ງຄ່າເປັນຜົນຜະລິດສູງທີ່ມີການເຄື່ອນໄຫວ. LEDs ເຮັດວຽກທີ່ດີທີ່ສຸດຢູ່ທີ່ 2.5V VCCIO ຫຼືສູງກວ່າ.

ອຸປະກອນນັບ pin ຕ່ໍາ (44-pin) ພຽງແຕ່ສີ່ I/Os ເຊື່ອມຕໍ່ກັບ LED1/2/3/4. ສໍາລັບອຸປະກອນນັບ PIN ທີ່ສູງກວ່າ (100-pin ແລະໃຫຍ່ກວ່າ), LEDs ທັງແປດແມ່ນເຊື່ອມຕໍ່ກັບ I/Os ຂອງອຸປະກອນ. ຕາຕະລາງ 3 ສະແດງໃຫ້ເຫັນການເຊື່ອມຕໍ່ແພັກເກັດທີ່ແຕກຕ່າງກັນຂອງ CPLD I/Os ກັບ LEDs.

ຕາຕະລາງ 3.ATF15xx ການເຊື່ອມຕໍ່ກັບ LEDs

| 44-pin TQFP | |

| LED | PLD Pin |

| LED1 | 28 |

| LED2 | 25 |

| LED3 | 22 |

| LED4 | 19 |

| 44-pin PLCC | |

| LED | PLD Pin |

| LED1 | 34 |

| LED2 | 31 |

| LED3 | 28 |

| LED4 | 25 |

| 84-pin PLCC | |

| LED | PLD Pin |

| LED1 | 69 |

| LED2 | 67 |

| LED3 | 64 |

| LED4 | 60 |

| LED5 | 27 |

| LED6 | 24 |

| LED7 | 18 |

| LED8 | 15 |

| 100-pin TQFP | |

| LED | PLD Pin |

| LED1 | 68 |

| LED2 | 65 |

| LED3 | 63 |

| LED4 | 58 |

| LED5 | 17 |

| LED6 | 14 |

| LED7 | 10 |

| LED8 | 9 |

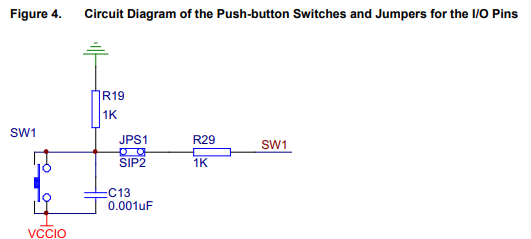

ສະວິດປຸ່ມກົດທີ່ມີ Jumpers ເລືອກໄດ້ສໍາລັບ I/O Pins

- ຄະນະພັດທະນາ / ໂຄງການ CPLD ປະກອບດ້ວຍປຸ່ມກົດປຸ່ມແປດສະຫຼັບ, ທີ່ເຊື່ອມຕໍ່ກັບ I/O pins ຂອງ CPLD ໄດ້. ສະວິດຈະສົ່ງສັນຍານເຫດຜົນການປ້ອນຂໍ້ມູນໄປຫາ PIN I/O ຜູ້ໃຊ້ຂອງອຸປະກອນ ATF15xx. ສະວິດເຫຼົ່ານີ້ຖືກຕິດສະຫຼາກ SW1 ຫາ SW8 ໃນ CPLD Development/Programmer

ກະດານ. ສົ້ນໜຶ່ງຂອງປຸ່ມກົດປຸ່ມປ້ອນເຂົ້າແຕ່ລະອັນແມ່ນເຊື່ອມຕໍ່ກັບ VCCIO, ໃນຂະນະທີ່ອີກສົ້ນໜຶ່ງຂອງປຸ່ມກົດປຸ່ມແຕ່ລະແມ່ນເຊື່ອມຕໍ່ກັບຕົວຕ້ານທານແບບດຶງລົງ ແລະຈາກນັ້ນເຊື່ອມຕໍ່ກັບ I/O pin ສະເພາະຂອງ CPLD ຜ່ານ JPS1/2. /3/4/5/6/7/8 jumper ເລືອກ. - ຖ້າຫນຶ່ງຂອງປຸ່ມກົດເຫຼົ່ານີ້ແລະ jumper ທີ່ສອດຄ້ອງກັນໄດ້ຖືກຕັ້ງ, PIN I/O ສະເພາະຂອງອຸປະກອນຈະຖືກຂັບເຄື່ອນໄປສູ່ສະຖານະສູງຕາມເຫດຜົນໂດຍການສົ່ງອອກຂອງວົງຈອນສະຫຼັບ. ເນື່ອງຈາກປຸ່ມກົດແຕ່ລະປຸ່ມຍັງເຊື່ອມຕໍ່ກັບຕົວຕ້ານທານແບບດຶງລົງ, ວັດສະດຸປ້ອນຈະມີເຫດຜົນຕ່ໍາຖ້າສະຫຼັບບໍ່ໄດ້ກົດດັນກັບຊຸດ jumper ທີ່ສອດຄ້ອງກັນ. ຖ້າປຸ່ມກົດປຸ່ມກົດບໍ່ໄດ້ຕັ້ງ, pin ທີ່ສອດຄ້ອງກັນຈະຖືກປະຕິບັດເປັນ pin ທີ່ບໍ່ໄດ້ເຊື່ອມຕໍ່. ຮູບທີ 4 ແມ່ນແຜນວາດວົງຈອນຂອງປຸ່ມກົດປຸ່ມ ແລະ jumper ທີ່ສາມາດເລືອກໄດ້. ຕາຕະລາງ 4 ສະແດງໃຫ້ເຫັນການເຊື່ອມຕໍ່ຂອງປຸ່ມກົດປຸ່ມແປດເຫຼົ່ານີ້ໄປຫາ pin CPLD I/O ໃນປະເພດແພັກເກັດທີ່ແຕກຕ່າງກັນ.

ຕາຕະລາງ 4.ATF15xx ການເຊື່ອມຕໍ່ກັບ I/O Pin Switches

| 44-pin TQFP | |

| ປຸ່ມກົດ | PLD Pin |

| SW1 | 15 |

| SW2 | 14 |

| SW3 | 13 |

| SW4 | 12 |

| SW5 | 8 |

| SW6 | 5 |

| SW7 | 2 |

| SW8 | 44 |

| 44-pin PLCC | |

| ປຸ່ມກົດ | PLD Pin |

| SW1 | 21 |

| SW2 | 20 |

| SW3 | 19 |

| SW4 | 18 |

| SW5 | 14 |

| SW6 | 11 |

| SW7 | 8 |

| SW8 | 6 |

| 84-pin PLCC | |

| ປຸ່ມກົດ | PLD Pin |

| SW1 | 54 |

| SW2 | 51 |

| SW3 | 49 |

| SW4 | 44 |

| SW5 | 9 |

| SW6 | 6 |

| SW7 | 4 |

| SW8 | 80 |

| 100-pin TQFP | |

| ປຸ່ມກົດ | PLD Pin |

| SW1 | 48 |

| SW2 | 36 |

| SW3 | 44 |

| SW4 | 37 |

| SW5 | 96 |

| SW6 | 98 |

| SW7 | 84 |

| SW8 | 99 |

ສະວິດປຸ່ມກົດທີ່ມີ jumpers ທີ່ເລືອກໄດ້ສໍາລັບ GCLR ແລະ OE1 Pins

ກະດານພັດທະນາ / ໂປລແກລມ CPLD ມີສອງປຸ່ມກົດປຸ່ມສໍາລັບ Global Clear (GCLR) ແລະ Output Enable (OE1) pins ຂອງ CPLD. ສະວິດຄວບຄຸມສະຖານະຕາມເຫດຜົນຂອງວັດສະດຸປ້ອນ OE1 ແລະ GCLR ຂອງອຸປະກອນ ATF15xx. ປຸ່ມສະຫຼັບເຫຼົ່ານີ້ແມ່ນມີປ້າຍຊື່ SW-GCLR ແລະ SW-GOE1 ຢູ່ເທິງກະດານ. ປາຍໜຶ່ງຂອງປຸ່ມກົດປຸ່ມປ້ອນຂໍ້ມູນ SW-GCLR ແມ່ນເຊື່ອມຕໍ່ກັບ GND. ທ້າຍອື່ນໆຂອງ

ປຸ່ມກົດແມ່ນເຊື່ອມຕໍ່ກັບຕົວຕ້ານທານກັບ VCCIO ແລະຫຼັງຈາກນັ້ນເຊື່ອມຕໍ່ກັບ GCLR ຂາເຂົ້າທີ່ອຸທິດຕົນຂອງອຸປະກອນ ATF15xx. ມັນມີຈຸດປະສົງເພື່ອຖືກນໍາໃຊ້ເປັນສັນຍານການຕັ້ງໃຫມ່ທີ່ມີການເຄື່ອນໄຫວຕ່ໍາເພື່ອປັບການລົງທະບຽນໃນອຸປະກອນ ATF15xx ກັບຊຸດ jumper ເລືອກ JPGCLR. ເຊັ່ນດຽວກັນ, ປາຍຫນຶ່ງຂອງປຸ່ມກົດປຸ່ມປ້ອນຂໍ້ມູນ SW-GOE1 ແມ່ນເຊື່ອມຕໍ່ກັບ GND. ປາຍອື່ນໆຂອງປຸ່ມກົດດັນ

ເຊື່ອມຕໍ່ກັບຕົວຕ້ານທານແບບດຶງກັບ VCCIO ແລະຫຼັງຈາກນັ້ນເຊື່ອມຕໍ່ກັບ OE1 ຂາເຂົ້າທີ່ອຸທິດຕົນຂອງອຸປະກອນ ATF15xx. ມັນມີຈຸດປະສົງເພື່ອໃຊ້ເປັນສັນຍານການເປີດໃຊ້ງານທີ່ມີການເຄື່ອນໄຫວຕໍ່າເພື່ອຄວບຄຸມການເປີດໃຊ້ງານ / ປິດການໃຊ້ງານຂອງ buffers ຜົນຜະລິດ tri-state ໃນ ATF15xx ກັບຊຸດ jumper ເລືອກ JPGOE. ຮູບທີ 5 ແມ່ນແຜນວາດວົງຈອນຂອງປຸ່ມກົດປຸ່ມ ແລະ jumpers ສໍາລັບ pins GCLR ແລະ OE1.

ຖ້າປຸ່ມກົດປຸ່ມໃດນຶ່ງເຫຼົ່ານີ້ຖືກກົດດັນ ແລະ jumper ທີ່ສອດຄ້ອງກັນຖືກຕັ້ງ, I/O ສະເພາະຂອງ CPLD ຈະຖືກຂັບເຄື່ອນໄປສູ່ສະຖານະຕ່ຳຕາມເຫດຜົນ. ເນື່ອງຈາກປຸ່ມກົດແຕ່ລະອັນຍັງເຊື່ອມຕໍ່ກັບຕົວຕ້ານທານແບບດຶງຂຶ້ນ, ວັດສະດຸປ້ອນ CPLD ທີ່ສອດຄ້ອງກັນຈະມີເຫດຜົນສູງຖ້າປຸ່ມກົດປຸ່ມກົດບໍ່ໄດ້ຖືກກົດດ້ວຍຊຸດ jumper ທີ່ສາມາດເລືອກໄດ້ທີ່ສອດຄ້ອງກັນ. ຖ້າ jumper ທີ່ສາມາດເລືອກໄດ້ບໍ່ໄດ້ຖືກຕັ້ງ, pin ປ້ອນຂໍ້ມູນສະເພາະທີ່ສອດຄ້ອງກັນຂອງ CPLD ສາມາດຖືວ່າເປັນ PIN No Connect (NC). ຕາຕະລາງ 5 ສະແດງຕົວເລກ PIN ຂອງ GCLR ແລະ OE1 ຂາເຂົ້າທີ່ອຸທິດຕົນຂອງອຸປະກອນ ATF15xx ໃນທຸກປະເພດແພັກເກດທີ່ມີຢູ່.

ຮູບທີ 5. ແຜນຜັງວົງຈອນຂອງປຸ່ມກົດປຸ່ມ ແລະ jumpers ທີ່ເລືອກໄດ້ສຳລັບ GCLR ແລະ OE1

ຕາຕະລາງ 5.Pin ຈໍານວນ GCLR ແລະ OE1

| 44-pin TQFP | 44-pin PLCC | 84-pin PLCC | 100-pin TQFP | |

| GCLR | 39 | 1 | 1 | 89 |

| OE1 | 38 | 44 | 84 | 88 |

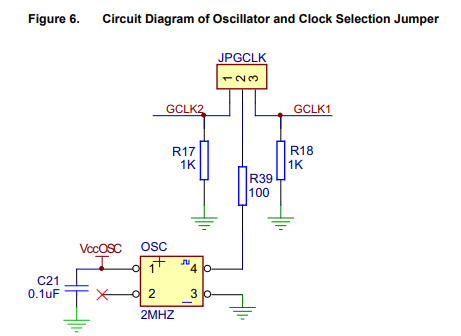

2MHz Oscillator ແລະ Jumper ເລືອກໂມງ

Jumper ການເລືອກໂມງທີ່ຕິດສະຫຼາກ JP-GCLK ຢູ່ໃນກະດານພັດທະນາ / Programmer CPLD ແມ່ນ jumper ສອງຕໍາແຫນ່ງທີ່ອະນຸຍາດໃຫ້ຜູ້ໃຊ້ສາມາດເລືອກ GCLK ທີ່ອຸທິດໃສ່ຂາເຂົ້າ (ບໍ່ວ່າຈະ GCLK1 ຫຼື GCLK2) ຂອງອຸປະກອນ ATF15xx ຄວນເຊື່ອມຕໍ່ກັບຜົນຜະລິດຂອງ. 2MHz oscillator. ນອກຈາກນັ້ນ, jumper ສາມາດຖອດອອກໄດ້ເພື່ອອະນຸຍາດໃຫ້ແຫຼ່ງໂມງພາຍນອກເຊື່ອມຕໍ່ກັບ GCLK1 ແລະ/ຫຼື GCLK2 ຂອງອຸປະກອນ ATF15xx. ຮູບທີ 6 ແມ່ນຮູບຕົວຢ່າງຂອງແຜນວາດວົງຈອນຂອງ oscillator ແລະ jumper ການເລືອກ. ຕາຕະລາງ 6 ສະແດງຕົວເລກ PIN ສໍາລັບ GCLK1 ແລະ GCLK2 ຂາເຂົ້າທີ່ອຸທິດຕົນຂອງອຸປະກອນ ATF15xx ໃນທຸກປະເພດແພັກເກດທີ່ມີຢູ່.

ຖ້າ jumper GCLK1 ຖືກຕັ້ງ, jumper ຈະຕັ້ງຢູ່ທາງຂ້າງຂອງກະດານ. ໃນທາງກົງກັນຂ້າມ, ຖ້າ GCLK2 jumper ຖືກກໍານົດ, jumper ຈະຕັ້ງຢູ່ກາງກະດານ.

ຕາຕະລາງ 6.Pin ຈໍານວນ GCLK1 ແລະ GCLK2

| 44-pin TQFP | 44-pin PLCC | 84-pin PLCC | 100-pin TQFP | |

| GCLK1 | 37 | 43 | 83 | 87 |

| GCLK2 | 40 | 2 | 2 | 90 |

VCCIO ແລະ VCCINT Voltage ເລືອກ Jumpers ແລະ LEDs

- The VCCIO ແລະ VCCINT Voltage Selection Jumpers, ຕິດສະຫຼາກ VCCIO Selector ແລະ VCCINT Selector ຕາມລໍາດັບໃນ ATF15xx-DK3 Development/Programming Kit, ອະນຸຍາດໃຫ້ເລືອກການສະໜອງ I/O.

- voltage ລະດັບ (VCCIO) ແລະການສະຫນອງຫຼັກ voltage ລະດັບ (VCCINT) ທີ່ໃຊ້ສໍາລັບ CPLD ເປົ້າຫມາຍໃນຊຸດ. ເມື່ອ jumpers ເຫຼົ່ານີ້ຖືກຕັ້ງຢ່າງຖືກຕ້ອງ, LEDs (ຕິດປ້າຍ VCCINT LED ແລະ VCCIO LED) ຈະເປີດ; ຢ່າງໃດກໍຕາມ, ຢູ່ໃນການສະຫນອງຕ່ໍາ voltage ລະດັບ (ເຊັ່ນ: 2.5V ຫຼືຕ່ໍາກວ່າ), LEDs ອາດຈະມືດມົວຫຼາຍ.

- ສໍາລັບ ATF15xxAS/ASL (5.0V) CPLDs, ທັງຕົວເລືອກ VCCIO ແລະ VCCINT Selector jumpers ຕ້ອງຖືກຕັ້ງເປັນ 5.0V.

- ສໍາລັບ ATF15xxASV/ASVL (3.3V) CPLDs, ທັງ VCCIO Selector ແລະ VCCINT Selector Jumpers ຕ້ອງຖືກຕັ້ງເປັນ 3.3V ເທົ່ານັ້ນ.

- ພະລັງງານຂອງ CPLD Development/Programmer Kit ຈະຕ້ອງຖືກປິດເມື່ອປ່ຽນຕໍາແຫນ່ງຂອງ VCCIO ຫຼື VCCINT Voltage Selection Jumper (ຕົວເລືອກ VCCIO ຫຼື VCCINT Selector).

- ICCIO ແລະ ICCINT Jumpers

- ເຄື່ອງ jumpers ICCIO ແລະ ICCINT ສາມາດຖອດອອກແລະໃຊ້ເປັນຈຸດວັດແທກ ICC. ເມື່ອ jumpers ຖືກໂຍກຍ້າຍ, ແມັດປະຈຸບັນສາມາດເຊື່ອມຕໍ່ກັບເສົາເພື່ອວັດແທກການບໍລິໂພກໃນປະຈຸບັນຂອງ CPLD ເປົ້າຫມາຍ. ເມື່ອຜູ້ໃຊ້ບໍ່ໄດ້ໃຊ້ jumpers ເຫຼົ່ານີ້ເພື່ອວັດແທກກະແສ, jumpers ເຫຼົ່ານີ້ຕ້ອງຖືກຕັ້ງເພື່ອໃຫ້ຊຸດແລະ CPLD ເຮັດວຽກ.

- ສະບັບtage ລະບຽບ

- ສອງ voltage regulators, ຕິດສະຫຼາກ VR1 ແລະ VR2, ຖືກນໍາໃຊ້ເພື່ອສ້າງເອກະລາດແລະຄວບຄຸມ

- VCCINT ແລະ VCCIO voltages ຈາກການສະຫນອງພະລັງງານ 9VDC. ສໍາລັບລາຍລະອຽດ, ກະລຸນາເບິ່ງຕາຕະລາງຊຸດ ATF15xx-DK3, ຮູບ 12.

- ສະວິດການສະຫນອງພະລັງງານແລະໄຟ LED

- ສະວິດການສະຫນອງພະລັງງານ, ມີປ້າຍຊື່ POWER SWITCH, ສາມາດສະຫຼັບກັບຕໍາແຫນ່ງເປີດຫຼືປິດ, ເຊິ່ງຖືກນໍາໃຊ້ເພື່ອເປີດຫຼືປິດພະລັງງານຂອງກະດານ ATF15xx-DK3 ຕາມລໍາດັບ. ມັນອະນຸຍາດໃຫ້ 9VDC voltage ຢູ່ທີ່ Power Supply Jack ເພື່ອຜ່ານໄປຫາ voltage ຜູ້ຄວບຄຸມໃນເວລາທີ່ມັນຢູ່ໃນຕໍາແຫນ່ງ. ເມື່ອສະວິດການສະຫນອງພະລັງງານເປີດ, ໄຟ LED (ມີປ້າຍກຳກັບ POWER LED) ຈະສະຫວ່າງຂຶ້ນເພື່ອຊີ້ບອກວ່າຊຸດ ATF15xx-DK3 ຖືກສະໜອງໃຫ້ພະລັງງານ.

- Power Supply Jack ແລະ Power Supply Header

- ກະດານ ATF15xx-DK3 ມີສອງປະເພດທີ່ແຕກຕ່າງກັນຂອງຕົວເຊື່ອມຕໍ່ການສະຫນອງພະລັງງານທີ່ມີປ້າຍຊື່ JPower ແລະ JP Power. ຫນຶ່ງໃນຕົວເຊື່ອມຕໍ່ການສະຫນອງພະລັງງານເຫຼົ່ານີ້ສາມາດຖືກນໍາໃຊ້ເພື່ອເຊື່ອມຕໍ່ແຫຼ່ງພະລັງງານ 9VDC ກັບຊຸດ. ຕົວເຊື່ອມຕໍ່ສາຍໄຟທຳອິດທີ່ມີປ້າຍຊື່ JPower, ແມ່ນປລັກສຽບໄຟຂອງຖັງທີ່ມີເສັ້ນຜ່າສູນກາງ 2.1 ມມ, ແລະມັນເຂົ້າກັນໄດ້ກັບປລັກສຽບເພດຍິງ ຂະໜາດ 2.1 ມມ (ເສັ້ນຜ່າກາງພາຍໃນ) x 5.5 ມມ (ເສັ້ນຜ່າກາງນອກ) ເພດຍິງ. ສ່ວນຫົວການສະຫນອງພະລັງງານທີສອງທີ່ມີປ້າຍຊື່ JP Power, ແມ່ນຫົວ 4-pin ຜູ້ຊາຍ 0.100″ ທີ່ມີ 0.025″ ຮຽບຮ້ອຍ. ຄວາມພ້ອມຂອງອຸປະກອນເຊື່ອມຕໍ່ສາຍໄຟສອງປະເພດນີ້ເຮັດໃຫ້ຜູ້ໃຊ້ສາມາດເລືອກປະເພດຂອງອຸປະກອນການສະຫນອງພະລັງງານເພື່ອໃຊ້ສໍາລັບ ATF15xx-DK3 Development/Programmer Kit.

- ພຽງແຕ່ຫນຶ່ງໃນສອງຕົວເຊື່ອມຕໍ່ການສະຫນອງພະລັງງານນີ້ຄວນໃຊ້ກັບແຫຼ່ງ 9VDC ແຕ່ບໍ່ແມ່ນທັງສອງໃນເວລາດຽວກັນ.

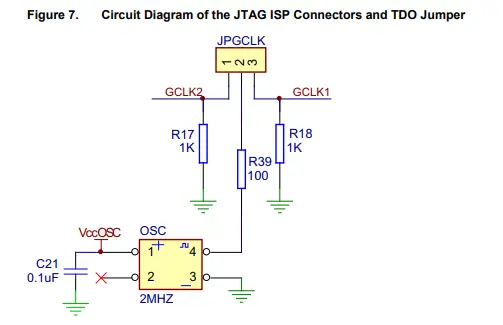

- JTAG ຕົວເຊື່ອມຕໍ່ ISP ແລະ TDO Selection Jumper

- ເຈTAG ISP Connector ທີ່ມີປ້າຍຊື່ JTAG-IN, ຖືກນໍາໃຊ້ເພື່ອເຊື່ອມຕໍ່ ATF15xx JTAG port pins (TCK, TDI, TMS, ແລະ TDO) ຜ່ານສາຍດາວໂຫຼດ ISP ໄປຫາພອດເຄື່ອງພິມຂະຫນານ (LPT) ຂອງ PC ສໍາລັບ JTAG ການຂຽນໂປລແກລມ ISP ຂອງອຸປະກອນ ATF15xx. ໂຕເຊື່ອມຕໍ່ຂົ້ວໂລກຖືກໃຊ້ຢູ່ໃນສາຍດາວໂຫຼດ ATF15xx-DK3 ແລະ ISP ເພື່ອຫຼຸດຜ່ອນບັນຫາການເຊື່ອມຕໍ່. ປ້າຍ PIN1 ຢູ່ດ້ານລຸ່ມຂອງ JTAG ຕົວເຊື່ອມຕໍ່ ISP ຊີ້ບອກຕຳແໜ່ງ pin 1 ຂອງຫົວ 10-pin ແລະຫຼຸດໂອກາດໃນການເຊື່ອມຕໍ່ ISP Download Cable ບໍ່ຖືກຕ້ອງ.

- ໄປທາງຊ້າຍຂອງ JTAG-IN connector, ມີສອງຖັນຂອງ vias, ແລະເຂົາເຈົ້າໄດ້ຖືກຕິດສະຫຼາກ JTAG- ອອກ. ພວກເຂົາມີຈຸດປະສົງເພື່ອໃຫ້ຜູ້ໃຊ້ສ້າງ JTAG ຕ່ອງໂສ້ daisy ເພື່ອປະຕິບັດ JTAG ການດໍາເນີນງານກັບອຸປະກອນຫຼາຍ. ຜູ້ໃຊ້ຈະຈໍາເປັນຕ້ອງໄດ້ solder ປະເພດດຽວກັນຂອງຕົວເຊື່ອມຕໍ່ກັບການນໍາໃຊ້ສໍາລັບ JTAG-IN ເຂົ້າໄປໃນ JTAG-OUT ຕໍາແຫນ່ງເພື່ອນໍາໃຊ້ຄຸນນະສົມບັດທີ່ມີຢູ່ນີ້.

- ເພື່ອສ້າງ JTAG ລະບົບຕ່ອງໂສ້ daisy ໂດຍໃຊ້ກະດານ ATF15xx-DK3 ຫຼາຍໆແຜ່ນ, TDO Selection Jumper, ປ້າຍຊື່ JP-TDO, ຕ້ອງໄດ້ຮັບການຕັ້ງຢູ່ໃນຕໍາແຫນ່ງທີ່ເຫມາະສົມ. ສໍາລັບອຸປະກອນທັງໝົດໃນສາຍໂສ້ daisy ຍົກເວັ້ນອຸປະກອນສຸດທ້າຍ, jumper ນີ້ຈະຕ້ອງຖືກຕັ້ງເປັນຕໍາແຫນ່ງອຸປະກອນຕໍ່ໄປ. ສໍາລັບອຸປະກອນສຸດທ້າຍໃນລະບົບຕ່ອງໂສ້, jumper ນີ້ຕ້ອງຖືກຕັ້ງເປັນຕໍາແຫນ່ງ TO ISP CABLE. ເມື່ອ jumper ນີ້ຢູ່ໃນຕໍາແຫນ່ງ TO NEXT Device, TDO ຂອງ JTAG ອຸປະກອນຈະເຊື່ອມຕໍ່ກັບ TDI ຕໍ່ໄປ

- JTAG ອຸປະກອນໃນລະບົບຕ່ອງໂສ້. ເມື່ອ jumper ນີ້ຢູ່ໃນຕໍາແຫນ່ງ TO ISP CABLE, TDO ຂອງອຸປະກອນນັ້ນຈະເຊື່ອມຕໍ່ກັບ TDO ຂອງ J.TAG ຕົວເຊື່ອມຕໍ່ 10-pin, ເຊິ່ງຈະຊ່ວຍໃຫ້ສັນຍານ TDO ຂອງອຸປະກອນນັ້ນຢູ່ໃນລະບົບຕ່ອງໂສ້ຖືກສົ່ງກັບຄືນໄປຫາ PC ເຈົ້າພາບດ້ວຍຊອບແວ ISP. ຮູບຂ້າງລຸ່ມນີ້ແມ່ນແຜນວາດວົງຈອນຂອງ

- JTAG ຕົວເຊື່ອມຕໍ່ ແລະ jumper JP-TDO. ຕາຕະລາງຂ້າງລຸ່ມນີ້ບອກຕົວເລກ PIN ຂອງສີ່ JTAG pins ສໍາລັບອຸປະກອນ ATF15xx ໃນທຸກແພັກເກັດທີ່ມີຢູ່.

ສໍາລັບການຕິດຕັ້ງອຸປະກອນດຽວ, ຕໍາແຫນ່ງຂອງ jumper JP-TDO ຕ້ອງຖືກຕັ້ງເປັນ ISP CABLE.

ຮູບທີ 7. ແຜນວາດວົງຈອນຂອງ JTAG ຕົວເຊື່ອມຕໍ່ ISP ແລະ TDO Jumper

- ຕາຕະລາງ 7.Pin ຈໍານວນ JTAG Port Signals

| 44-pin TQFP | 44-pin PLCC | 84-pin PLCC | 100-pin TQFP | |

| TDI | 1 | 7 | 14 | 4 |

| TDO | 32 | 38 | 71 | 73 |

| TMS | 7 | 13 | 23 | 15 |

| TCK | 26 | 32 | 62 | 62 |

ສູດການຄິດໄລ່ ISP ຖືກຄວບຄຸມໂດຍຊອບແວ ATMISP, ເຊິ່ງເຮັດວຽກຢູ່ໃນ PC. ສີ່ JTAG ສັນຍານຖືກສ້າງຂື້ນໂດຍພອດ LPT, ແລະພວກມັນຖືກ buffed ໂດຍສາຍດາວໂຫຼດ ISP ກ່ອນທີ່ຈະເຂົ້າໄປໃນອຸປະກອນ ATF15xx ຢູ່ໃນກະດານພັດທະນາ / ໂປລແກລມ CPLD. The 10-pin JTAG Port Header pinout ໃນ CPLD Development/Programmer board ແມ່ນສະແດງຢູ່ໃນຮູບ 8, ແລະຂະຫນາດຂອງ 10-pin ເພດຊາຍ JTAG ສ່ວນຫົວແມ່ນສະແດງຢູ່ໃນຮູບ 9.

ຮູບ 8. 10-pin JTAG Port Header Pinout

- The 10-pin JTAG Port Header pinout ແມ່ນເຂົ້າກັນໄດ້ກັບສາຍພອດ ATDH1150PC/VPC LPT ແລະສາຍເຄເບີນທີ່ອີງໃສ່ພອດ USB ATDH1150USB, ເຊັ່ນດຽວກັນກັບ Altera

- ByteBlaster/MV/II ສາຍເຄເບີນທີ່ອີງໃສ່ພອດ LPT. ນອກຈາກນັ້ນ, ຊອບແວ ATMISP v6.7 ອະນຸຍາດໃຫ້ໃຊ້ Atmel ໄດ້

- ສາຍ ATDH1150PC/VPC/USB ຫຼືສາຍ ByteBlaster/MV/II ເພື່ອປະຕິບັດ ISP.

- ATMISP v7.0 ຮອງຮັບສາຍ ATDH1150USB ເທົ່ານັ້ນ.

- Socket Adapter Board

- ATF15xx-DK3 CPLD Development/Programmer Socket Adapter Boards (ATF15xx-DK3-XXXXX) ແມ່ນແຜງວົງຈອນທີ່ມີການໂຕ້ຕອບກັບ ATF15xx-DK3 CPLD Development/Programmer Boards. ພວກມັນຖືກນໍາໃຊ້ຮ່ວມກັນກັບ ATF15xx-DK3 CPLD Development/Programmer Board ເພື່ອປະເມີນຫຼືໂຄງການ ATF15xx ISP CPLD ອຸປະກອນໃນປະເພດແພັກເກັດຕ່າງໆ. ມີກະດານອະແດັບເຕີຊັອກເກັດສີ່ອັນມີໃຫ້ສໍາລັບ ATF15xx-DK3 ກວມເອົາ 44-TQFP, 44-PLCC, 84-PLCC, ແລະ 100-.

- ປະເພດແພັກເກດ TQFP ໃນຄອບຄົວ ATF15xx ຂອງ CPLDs.

- ແຕ່ລະກະດານອະແດບເຕີ socket ມີເຕົ້າສຽບສໍາລັບອຸປະກອນ ATF15xx ແລະມີຫົວຜູ້ຊາຍຢູ່ດ້ານລຸ່ມ, ມີປ້າຍຊື່ JP1 ແລະ JP2. ສ່ວນຫົວຢູ່ທາງລຸ່ມຄູ່ກັບຫົວເພດຍິງຢູ່ໃນກະດານ ATF15xx-DK3, ມີປ້າຍຊື່ JP4 ແລະ JP3. ຈໍສະແດງຜົນ 7 ສີ່ສ່ວນ, ສະຫຼັບປຸ່ມກົດ,

- JTAG ສັນຍານພອດ, oscillator, VCCINT, VCCIO, ແລະ GND ຢູ່ໃນກະດານພັດທະນາ / Programmer CPLD ແມ່ນເຊື່ອມຕໍ່ກັບອຸປະກອນ ATF15xx ໃນ Socket Adapter Board ຜ່ານສອງຊຸດຂອງຕົວເຊື່ອມຕໍ່ນີ້.

- ຢູ່ເທິງສຸດຂອງອະແດບເຕີຊັອກເກັດ 44-TQFP, ມີສີ່ຕົວເຊື່ອມຕໍ່ 10-pin ທີ່ມີຂະຫນາດດຽວກັນກັບ J.TAG ຕົວເຊື່ອມຕໍ່ ISP. pins ຂອງສີ່ຕົວເຊື່ອມຕໍ່ເຫຼົ່ານີ້ແມ່ນເຊື່ອມຕໍ່ກັບ input ແລະ I / O pins (ຍົກເວັ້ນສີ່ JTAG pins) ຂອງອຸປະກອນ CPLD ເປົ້າໝາຍ. ພວກມັນສາມາດໃຊ້ເພື່ອເຊື່ອມຕໍ່ກັບ oscilloscope ຫຼືເຄື່ອງວິເຄາະເຫດຜົນເພື່ອບັນທຶກການເຄື່ອນໄຫວຂອງ input ແລະ I/O pins ຂອງ CPLD. ພວກເຂົາເຈົ້າຍັງສາມາດຖືກນໍາໃຊ້ເພື່ອເຊື່ອມຕໍ່ input ແລະ I/O pins ຂອງ CPLD ກັບກະດານພາຍນອກອື່ນໆຫຼືອຸປະກອນສໍາລັບການປະເມີນລະດັບລະບົບຫຼືການທົດສອບ.

- ສາຍດາວໂຫຼດ Atmel ATF15xx ISP

- ສາຍດາວໂຫຼດ ATF15xx ISP (P/N: ATDH1150VPC) ເຊື່ອມຕໍ່ພອດ LPT ຂອງ PC ກັບ 10-pin J.TAG header ໃນ CPLD Development/Programmer Board ຫຼືກະດານວົງຈອນແບບກຳນົດເອງ. ນີ້ແມ່ນສະແດງຢູ່ໃນຮູບ 10. ສາຍ ISP ນີ້ເຮັດຫນ້າທີ່ເປັນ buffer ເພື່ອ buffer J.TAG ສັນຍານລະຫວ່າງພອດ LPT ຂອງ PC ແລະ ATF15xx ຢູ່ໃນກະດານວົງຈອນ. LED Power-On ຢູ່ດ້ານຫຼັງຂອງຕົວເຊື່ອມຕໍ່ເພດຊາຍ 25-pin ສະແດງວ່າສາຍໄດ້ຖືກເຊື່ອມຕໍ່ຢ່າງຖືກຕ້ອງ.

- ໃຫ້ແນ່ໃຈວ່າໄຟ LED ນີ້ເປີດກ່ອນທີ່ຈະໃຊ້ Atmel CPLD ISP Software (ATMISP).

- ສາຍ ISP ນີ້ປະກອບດ້ວຍຕົວເຊື່ອມຕໍ່ຊາຍ 25-pin (DB25), ເຊິ່ງເຊື່ອມຕໍ່ກັບພອດ LPT ຂອງເຄື່ອງຄອມພິວເຕີ. ສຽບເພດຍິງ 10 pin ເຊື່ອມຕໍ່ກັບ 10 pin ເພດຊາຍ JTAG header ເທິງກະດານວົງຈອນ ISP. ແຖບສີແດງຢູ່ສາຍໂບຊີ້ບອກທິດທາງຂອງ PIN 1 ຂອງປລັກເພດຍິງ. ປະເພດ 10 ເພດຊາຍ JTAG ຫົວຂໍ້ກ່ຽວກັບ CPLD

- ກະດານພັດທະນາ / ໂປລແກລມແມ່ນ polarized ເພື່ອປ້ອງກັນບໍ່ໃຫ້ຜູ້ໃຊ້ສຽບສຽບເພດຍິງໃນທິດທາງທີ່ບໍ່ຖືກຕ້ອງ.

- ຊຸດການພັດທະນາ/ໂປຣແກຣມເມີຂອງ CPLD ລວມມີສາຍດາວໂຫຼດ ATF15xx ISP

(ATDH1150VPC); ແນວໃດກໍ່ຕາມ, ສາຍ ISP ທີ່ຮອງຮັບອື່ນໆຍັງສາມາດຖືກນໍາໃຊ້. ສາຍ ATDH1150VPC, ATDH1150USB, ByteBlasterMV, ແລະ ByteBlasterII ສາມາດໃຊ້ກັບອຸປະກອນ ATF15xx/ASL (5V) ແລະ ATF15xxASV/ASVL (3.3V), ໃນຂະນະທີ່ ATDH1150PC ເກົ່າແກ່ ແລະ ByteBlaster ສາຍ ATF15xx/ASL (5V) ສາມາດນຳໃຊ້ໄດ້. ເທົ່ານັ້ນ.

- ຮູບທີ 11 ສະແດງເຖິງ 10-pin header pinout ເພດຍິງ ສໍາລັບສາຍ ATF15xx ISP ດາວໂລດ. pinout ຫົວຫົວຜູ້ຊາຍ 10-pin ໃນກະດານ PC (ຖ້າໃຊ້ສໍາລັບ ISP) ຕ້ອງກົງກັບ pinout ນີ້.

- ໝາຍເຫດ: ກະດານວົງຈອນຕ້ອງສະຫນອງ VCC ແລະ GND ໃຫ້ກັບສາຍ CPLD ISP ຜ່ານຫົວຂອງຜູ້ຊາຍ 10-pin.

ແຜນວາດແຜນວາດ

ເອກະສານອ້າງອີງແລະສະຫນັບສະຫນູນ

ສໍາລັບການອ້າງອິງຊອບແວການອອກແບບ PLD ເພີ່ມເຕີມແລະການສະຫນັບສະຫນູນ, ເອກະສານເຊັ່ນ: ການຊ່ວຍເຫຼືອ files, tutorials, ບັນທຶກຄໍາຮ້ອງສະຫມັກ / ໂດຍຫຍໍ້, ແລະຄູ່ມືຜູ້ໃຊ້ແມ່ນມີຢູ່ໃນ www.atmel.com.

ຊອບແວອອກແບບ Atmel ProChip

ຕາຕະລາງ 8.ProChip Designer References and Support

| ຜູ້ອອກແບບ ProChip | ຈາກເມນູຫຼັກຂອງໜ້າຕ່າງ ProChip… |

| ຊ່ວຍເຫຼືອ | ເລືອກ ຊ່ວຍເຫຼືອ > ຊ່ວຍເຫຼືອຜູ້ອອກແບບ Prochip. |

| ການສອນສອນ | ເລືອກ ຊ່ວຍເຫຼືອ > ການສອນສອນ. |

| ຮູ້ບັນຫາແລະວິທີແກ້ໄຂ | ເລືອກ ຊ່ວຍເຫຼືອ > Review ກປ. |

ຊອບແວ Atmel WinCUPL

ຕາຕະລາງ 9. WinCUPL References and Support

| WinCUPL | ຈາກເມນູ WinCUPL ຫຼັກ... |

| ຊ່ວຍເຫຼືອ | ເລືອກ ຊ່ວຍເຫຼືອ > ເນື້ອໃນ. |

| ຄູ່ມືການອ້າງອິງ Programmers CUPL | ເລືອກ ຊ່ວຍເຫຼືອ > CUPL Programmers ອ້າງອິງ. |

| ການສອນສອນ | ເລືອກ ຊ່ວຍເຫຼືອ > ຂໍ້ມູນ Atmel > Tutorial1.pdf. |

| ຮູ້ບັນຫາແລະວິທີແກ້ໄຂ | ເລືອກ ຊ່ວຍເຫຼືອ > ຂໍ້ມູນ Atmel > CUPL_BUG.pdf. |

ຊອບແວ Atmel ATMISP

ຕາຕະລາງ 10. ເອກະສານອ້າງອີງ ແລະ ການຊ່ວຍເຫຼືອຂອງ ATMISP

| ATMISP | ຈາກເມນູ ATMISP ຫຼັກ... |

| ຊ່ວຍເຫຼືອ Files | ເລືອກ ຊ່ວຍເຫຼືອ > ຊ່ວຍເຫຼືອ ISP. |

| ການສອນສອນ | ເລືອກ ຊ່ວຍເຫຼືອ > ການສອນ ATMISP. |

| ຮູ້ບັນຫາແລະວິທີແກ້ໄຂ | ການນໍາໃຊ້ຕົວທ່ອງເວັບຂອງ Windows Explorer, ຊອກຫາໂຟນເດີ ATMISP ແລະເປີດ readme.txt file ດ້ວຍຕົວແກ້ໄຂຂໍ້ຄວາມ ASCII. |

ຊອບແວການແປງ Atmel POF2JED

ຕາຕະລາງ 11. ການອ້າງອິງ POF2JED ແລະການສະຫນັບສະຫນູນ

| POF2JED | ຈາກເມນູ POF2JED ຕົ້ນຕໍ... |

| ຫຍໍ້ຄໍາຮ້ອງສະຫມັກການແປງ ATF15xx | ເລືອກ ຊ່ວຍເຫຼືອ > ຕົວເລືອກການແປງ. |

ສະຫນັບສະຫນູນດ້ານວິຊາການ

- ສໍາລັບການສະຫນັບສະຫນູນດ້ານວິຊາການກ່ຽວກັບບັນຫາທີ່ກ່ຽວຂ້ອງກັບ Atmel PLD, ຕິດຕໍ່ Atmel PLD Applications Group ທີ່:

- ອີເມວ pld@atmel.com

- ສາຍດ່ວນ (+1)408-436-4333

- ແບບຟອມສະຫນັບສະຫນູນອອນໄລນ໌ http://support.atmel.com/bin/customer.exe

ປະຫວັດການແກ້ໄຂ

| ການທົບທວນ | ວັນທີ | ລາຍລະອຽດ |

| 3605C | 06/2014 | ອັບເດດ schematics, ແມ່ແບບ, ໂລໂກ້, ແລະຫນ້າປະຕິເສດ. ເພີ່ມພາກປະຫວັດການດັດແກ້. |

| 3605 ບ | 05/2008 |

- Atmel Corporation 1600 Technology Drive, San Jose, CA 95110 USA T: (+1)(408) 441.0311 F: (+1)(408) 436.4200 | www.atmel.com

- © 2014 Atmel Corporation. / Rev.: Atmel-3605C-CPLD-ATF15xx-DK3-Development-Kit-UserGuide_062014.

- Atmel®, ໂລໂກ້ Atmel ແລະການປະສົມປະສານຂອງມັນ, ເຮັດໃຫ້ຄວາມເປັນໄປໄດ້ບໍ່ຈໍາກັດ, ແລະອື່ນໆແມ່ນເຄື່ອງຫມາຍການຄ້າຫຼືເຄື່ອງຫມາຍການຄ້າຂອງບໍລິສັດ Atmel Corporation ໃນສະຫະລັດແລະ

ປະເທດອື່ນໆ. ຂໍ້ກໍານົດແລະຊື່ຜະລິດຕະພັນອື່ນໆອາດຈະເປັນເຄື່ອງຫມາຍການຄ້າຂອງຄົນອື່ນ. - ການປະຕິເສດຄວາມຮັບຜິດຊອບ: ຂໍ້ມູນໃນເອກະສານນີ້ແມ່ນໃຫ້ຢູ່ໃນການເຊື່ອມໂຍງກັບຜະລິດຕະພັນ Atmel. ບໍ່ມີໃບອະນຸຍາດ, ສະແດງອອກຫຼືໂດຍຄວາມຫມາຍ, ໂດຍ estoppel ຫຼືຖ້າບໍ່ດັ່ງນັ້ນ, ສິດທິຊັບສິນທາງປັນຍາແມ່ນໄດ້ຮັບການອະນຸຍາດຈາກເອກະສານນີ້ຫຼືກ່ຽວຂ້ອງກັບການຂາຍຜະລິດຕະພັນ Atmel.

- ຍົກເວັ້ນຕາມທີ່ກຳນົດໄວ້ໃນເງື່ອນໄຂ ແລະເງື່ອນໄຂຂອງການຂາຍທີ່ຕັ້ງຢູ່ໃນ ATMEL WEBເວັບໄຊ, ATMEL ຖືວ່າບໍ່ມີຄວາມຮັບຜິດຊອບອັນໃດກໍຕາມ ແລະປະຕິເສດການຢືນຢັນໃດໆກໍຕາມ, ໂດຍຫຍໍ້, ຫຼືການຮັບປະກັນຕາມກົດໝາຍທີ່ກ່ຽວຂ້ອງກັບຜະລິດຕະພັນຂອງມັນລວມທັງ, ແຕ່ບໍ່ຈຳກັດການຮັບປະກັນ, ການຮັບປະກັນ, ການສະໜອງສິນຄ້າ. ການລະເມີດ. IN

- ບໍ່ມີເຫດການໃດຫນຶ່ງທີ່ ATMEL ຈະຮັບຜິດຊອບສໍາລັບຄວາມເສຍຫາຍໂດຍກົງ, ທາງອ້ອມ, ຜົນສະທ້ອນ, ການລົງໂທດ, ພິເສດ, ຫຼືຄວາມເສຍຫາຍໂດຍບັງເອີນ (ລວມທັງ, ໂດຍບໍ່ມີການຈໍາກັດ, ຄວາມເສຍຫາຍສໍາລັບການສູນເສຍແລະຜົນກໍາໄລ, ການນໍາໃຊ້ລະຫວ່າງການທຸລະກິດ) ຫຼືບໍ່ສາມາດນຳໃຊ້ໄດ້ ເອກະສານນີ້, ເຖິງແມ່ນວ່າ ATMEL ໄດ້ຮັບການແນະນໍາກ່ຽວກັບຄວາມເປັນໄປໄດ້ຂອງຄວາມເສຍຫາຍດັ່ງກ່າວ.

- Atmel ບໍ່ມີການເປັນຕົວແທນຫຼືການຮັບປະກັນກ່ຽວກັບຄວາມຖືກຕ້ອງຫຼືຄວາມສົມບູນຂອງເນື້ອໃນຂອງເລື່ອງນີ້

ເອກະສານ ແລະສະຫງວນສິດໃນການປ່ຽນແປງສະເພາະ ແລະລາຍລະອຽດຂອງຜະລິດຕະພັນໄດ້ທຸກເວລາໂດຍບໍ່ຕ້ອງແຈ້ງໃຫ້ຮູ້. Atmel ບໍ່ໄດ້ໃຫ້ຄໍາໝັ້ນສັນຍາທີ່ຈະປັບປຸງຂໍ້ມູນທີ່ມີຢູ່ໃນນີ້. ເວັ້ນເສຍແຕ່ໄດ້ສະຫນອງໃຫ້ໂດຍສະເພາະຖ້າບໍ່ດັ່ງນັ້ນ, ຜະລິດຕະພັນ Atmel ແມ່ນບໍ່ເຫມາະສົມສໍາລັບ, ແລະຈະບໍ່ຖືກນໍາໃຊ້ໃນ, ຄໍາຮ້ອງສະຫມັກລົດຍົນ. ຜະລິດຕະພັນ Atmel ບໍ່ໄດ້ມີຈຸດປະສົງ, ອະນຸຍາດ, ຫຼືຮັບປະກັນສໍາລັບການນໍາໃຊ້ເປັນອົງປະກອບໃນຄໍາຮ້ອງສະຫມັກທີ່ມີຈຸດປະສົງເພື່ອສະຫນັບສະຫນູນຫຼືຍືນຍົງຊີວິດ. - ຄໍາຮ້ອງສະຫມັກດ້ານຄວາມປອດໄພ, ທະຫານ, ແລະລົດຍົນ ປະຕິເສດຄວາມຮັບຜິດຊອບ: ຜະລິດຕະພັນຂອງ Atmel ບໍ່ໄດ້ອອກແບບມາເພື່ອ ແລະ ຈະບໍ່ຖືກນຳໃຊ້ໃນການພົວພັນກັບແອັບພລິເຄຊັນໃດໆ ທີ່ຄວາມລົ້ມເຫຼວຂອງຜະລິດຕະພັນດັ່ງກ່າວຄາດວ່າຈະສົ່ງຜົນໃຫ້ເກີດການບາດເຈັບ ຫຼື ເສຍຊີວິດ ("Safety-Critical Applications") ໂດຍບໍ່ມີການຂຽນສະເພາະຂອງເຈົ້າໜ້າທີ່ Atmel.

- ຍິນຍອມ. ຄໍາຮ້ອງສະຫມັກຄວາມປອດໄພ-ທີ່ສໍາຄັນປະກອບມີ, ໂດຍບໍ່ມີການຈໍາກັດ, ອຸປະກອນສະຫນັບສະຫນູນຊີວິດ, ແລະລະບົບ, ອຸປະກອນຫຼືລະບົບສໍາລັບການດໍາເນີນງານຂອງສະຖານທີ່ນິວເຄລຍແລະລະບົບອາວຸດ.

- ຜະລິດຕະພັນຂອງ Atmel ບໍ່ໄດ້ຖືກອອກແບບ ຫຼືມີຈຸດປະສົງເພື່ອໃຊ້ໃນການນຳໃຊ້ທາງທະຫານ ຫຼືອາວະກາດ ຫຼືສະພາບແວດລ້ອມຕ່າງໆ ເວັ້ນເສຍແຕ່ວ່າ Atmel ໄດ້ຖືກກຳນົດໂດຍສະເພາະເປັນຊັ້ນທະຫານ. ຜະລິດຕະພັນຂອງ Atmel ບໍ່ໄດ້ຖືກອອກແບບ ຫຼືມີຈຸດປະສົງເພື່ອໃຊ້ໃນການນຳໃຊ້ລົດຍົນ ເວັ້ນເສຍແຕ່ໄດ້ກຳນົດສະເພາະໂດຍ Atmel ເປັນລົດຍົນ.

- ດາວໂຫຼດຈາກ: Arrow.com.

ເອກະສານ / ຊັບພະຍາກອນ

|

Atmel ATF15xx-DK3 CPLD ຊຸດພັດທະນາ/ໂປຣແກຣມເມີ [pdf] ຄູ່ມືຜູ້ໃຊ້ ATF15xx-DK3 CPLD Development Programmer Kit, ATF15xx-DK3, ຊຸດໂປຣແກຣມເມີເມີພັດທະນາ CPLD, ຊຸດໂປຣແກຣມເມີພັດທະນາ, ຊຸດໂປຣແກຣມເມີ |