ບໍລິສັດ Intel, ປະຫວັດສາດ — Intel Corporation, ຮູບແບບເປັນ intel, ແມ່ນບໍລິສັດບໍລິສັດແລະເຕັກໂນໂລຢີຫຼາຍຊາດຂອງອາເມລິກາທີ່ມີສໍານັກງານໃຫຍ່ຢູ່ໃນ Santa Clara ຢ່າງເປັນທາງການຂອງພວກເຂົາ. webເວັບໄຊແມ່ນ Intel.com.

ໄດເລກະທໍລີຂອງຄູ່ມືຜູ້ໃຊ້ແລະຄໍາແນະນໍາສໍາລັບຜະລິດຕະພັນ Intel ສາມາດພົບໄດ້ຂ້າງລຸ່ມນີ້. ຜະລິດຕະພັນ Intel ໄດ້ຮັບສິດທິບັດແລະເຄື່ອງຫມາຍການຄ້າພາຍໃຕ້ຍີ່ຫໍ້ຂອງ ບໍລິສັດ Intel.

ຂໍ້ມູນຕິດຕໍ່:

ທີ່ຢູ່: 2200 Mission College Blvd, Santa Clara, CA 95054, United States

ສ້າງຕັ້ງຂຶ້ນ: ວັນທີ 18 ກໍລະກົດ 1968

ຜູ້ກໍ່ຕັ້ງ: Gordon Moore, Robert Noyce ແລະ Andrew Grove

ບຸກຄົນສຳຄັນ: Andy D. Bryant, Reed E. Hundt

ຮຽນຮູ້ວິທີການປະຕິບັດການປັບປຸງ hitless ໂດຍໃຊ້ພາຍໃນ JTAG ການໂຕ້ຕອບສໍາລັບອຸປະກອນທາງເລືອກຄຸນສົມບັດ Intel® MAX® 10 DD ທີ່ມີຄູ່ມືຜູ້ໃຊ້ AN-963 MAX 10 Hitless. ຄົ້ນພົບຄໍາແນະນໍາສໍາລັບການສັງເກດແລະການຄວບຄຸມສັນຍານທີ່ສໍາຄັນໂດຍບໍ່ມີການຂັດຂວາງ. ອັບເກຣດປະສິດທິພາບຂອງອຸປະກອນຂອງທ່ານດ້ວຍຄວາມສະດວກສະບາຍ.

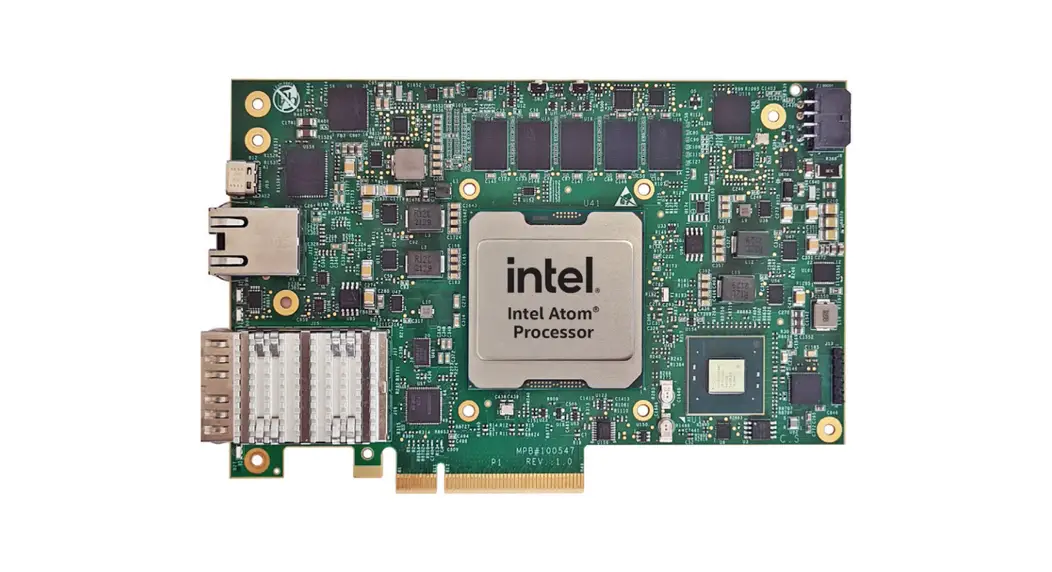

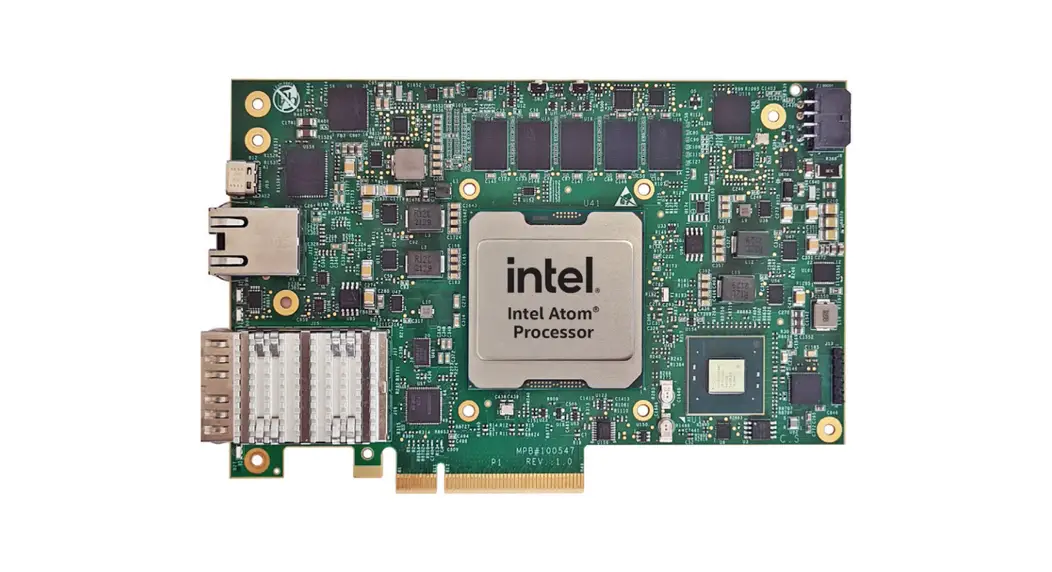

ຮຽນຮູ້ວິທີທີ່ Intel's NetSec Accelerator Reference Design, ເປັນບັດເພີ່ມ PCIe, ເລັ່ງການເຮັດວຽກຂອງເຄືອຂ່າຍ ແລະຄວາມປອດໄພທີ່ສໍາຄັນເຊັ່ນ: IPsec, SSL/TLS, firewall, SASE, ການວິເຄາະ ແລະ inferencing. ເຫມາະສໍາລັບສະພາບແວດລ້ອມທີ່ແຈກຢາຍຈາກຂອບໄປຫາຟັງ, ການອອກແບບການອ້າງອີງນີ້ປັບປຸງປະສິດທິພາບແລະປະສິດທິພາບສໍາລັບລູກຄ້າ. ຄົ້ນພົບວ່າຮູບແບບການບໍລິການການເຂົ້າເຖິງທີ່ປອດໄພ (SASE) ຕອບສະໜອງໄດ້ຄວາມຕ້ອງການຄວາມປອດໄພໃໝ່ແນວໃດໃນສະພາບແວດລ້ອມທີ່ກຳນົດໄວ້ໂດຍຊອບແວແບບເຄື່ອນໄຫວ, ໂດຍການລວມເອົາໜ້າທີ່ຂອງຄວາມປອດໄພທີ່ກຳນົດໄວ້ໂດຍຊອບແວ ແລະ WAN ເຂົ້າໃນຊຸດບໍລິການທີ່ສົ່ງຜ່ານຄລາວ.

ຮຽນຮູ້ກ່ຽວກັບ Intel® Agilex™ Logic Array Blocks (LABs) ແລະ Adaptive Logic Modules (ALMs) ໃນຄູ່ມືຜູ້ໃຊ້ນີ້. ຄົ້ນພົບວິທີຕັ້ງຄ່າ LABs ແລະ ALMs ສໍາລັບຟັງຊັນຕາມເຫດຜົນ, ເລກເລກ ແລະລົງທະບຽນ. ຊອກຫາຂໍ້ມູນເພີ່ມເຕີມກ່ຽວກັບສະຖາປັດຕະຍະກໍາຫຼັກ Intel Hyperflex™ ແລະ Hyper-Registers ທີ່ມີຢູ່ໃນທຸກພາກສ່ວນເສັ້ນທາງເຊື່ອມຕໍ່ກັນໃນທົ່ວເນື້ອຜ້າຫຼັກ. ຄົ້ນຫາວິທີການເຮັດວຽກຂອງ Intel Agilex LAB ແລະ ALM Architecture, ລວມທັງ MLAB, ເຊິ່ງເປັນ superset ຂອງ LAB.

ຮຽນຮູ້ວິທີການສ້າງ ແລະທົດສອບ HDMI PHY FPGA IP Design Example ສໍາລັບອຸປະກອນ Intel Arria 10 ດ້ວຍຄູ່ມືເລີ່ມຕົ້ນໄວນີ້. ຄູ່ມືການນໍາໃຊ້ນີ້ປະກອບມີຄໍາແນະນໍາເປັນບາດກ້າວສໍາລັບການສ້າງການອອກແບບແລະລັກສະນະການອອກແບບ retransmit ທີ່ສະຫນັບສະຫນູນ HDMI 2.0 RX-TX. ທີ່ສົມບູນແບບສໍາລັບທຸກຄົນທີ່ຊອກຫາເພື່ອປັບປຸງທັກສະການອອກແບບ FPGA IP ຂອງເຂົາເຈົ້າ.

ຄູ່ມືຜູ້ໃຊ້ນີ້ໃຫ້ຂໍ້ມູນລະອຽດກ່ຽວກັບ Fronthaul Compression FPGA IP, ຮຸ່ນ 1.0.1, ອອກແບບມາສໍາລັບ Intel® Quartus® Prime Design Suite 21.4. IP ສະຫນອງການບີບອັດແລະການບີບອັດສໍາລັບຂໍ້ມູນ U-plane IQ, ສະຫນັບສະຫນູນການບີບອັດ µ-law ຫຼື block floating-point compression. ມັນຍັງປະກອບມີຕົວເລືອກການຕັ້ງຄ່າແບບຄົງທີ່ ແລະແບບເຄື່ອນໄຫວສຳລັບຮູບແບບ IQ ແລະສ່ວນຫົວການບີບອັດ. ຄູ່ມືນີ້ແມ່ນຊັບພະຍາກອນທີ່ມີຄຸນຄ່າສໍາລັບທຸກຄົນທີ່ໃຊ້ FPGA IP ນີ້ສໍາລັບສະຖາປັດຕະຍະກໍາລະບົບແລະການສຶກສາການນໍາໃຊ້ຊັບພະຍາກອນ, ການຈໍາລອງ, ແລະອື່ນໆ.

ຮຽນຮູ້ວິທີການໃຊ້ Interlaken 2nd Generation Agilex FPGA IP Design Example ກັບຄູ່ມືຜູ້ໃຊ້ນີ້. ຄູ່ມືປະກອບມີຄູ່ມືເລີ່ມຕົ້ນໄວ, ແຜນວາດບລັອກລະດັບສູງ, ແລະຄວາມຕ້ອງການຮາດແວແລະຊອບແວ. ຄົ້ນພົບເຄື່ອງຈຳລອງທີ່ຮອງຮັບ ແລະການຕັ້ງຄ່າຮາດແວສຳລັບ Intel IP design exampເລ.

ຄູ່ມືຜູ້ໃຊ້ນີ້ໃຫ້ຄໍາແນະນໍາສໍາລັບ F-Tile DisplayPort FPGA IP Design Example, ມີການຈໍາລອງແລະການທົດສອບຮາດແວສໍາລັບ Intel Quartus Prime Design Suite. ຄູ່ມືປະກອບມີຂໍ້ມູນການເລີ່ມຕົ້ນໄວແລະການພັດທະນາ stages ສໍາລັບການອອກແບບ loopback ຂະຫນານ DisplayPort SST examples. ອັບເດດສໍາລັບ IP ເວີຊັນ 21.0.1 ແລະເຂົ້າກັນໄດ້ກັບ Intel Agilex, ຄູ່ມືນີ້ສະເຫນີໂຄງສ້າງໄດເລກະທໍລີລາຍລະອຽດແລະອົງປະກອບ. files ສໍາລັບການທົດສອບຮາດແວສົບຜົນສໍາເລັດ.

ຮຽນຮູ້ວິທີການໃຊ້ Chip ID Intel FPGA IP cores ເພື່ອອ່ານລະຫັດຊິບ 64-bit ທີ່ເປັນເອກະລັກຂອງອຸປະກອນ Intel FPGA ທີ່ຮອງຮັບຂອງທ່ານສໍາລັບການກໍານົດ. ຄູ່ມືຜູ້ໃຊ້ນີ້ກວມເອົາຄໍາອະທິບາຍທີ່ເປັນປະໂຫຍດ, ພອດ, ແລະຂໍ້ມູນທີ່ກ່ຽວຂ້ອງສໍາລັບ Chip ID Intel Stratix 10, Arria 10, Cyclone 10 GX, ແລະ MAX 10 FPGA IP cores. ເໝາະສຳລັບວິສະວະກອນ ແລະນັກອອກແບບທີ່ຊອກຫາເພື່ອເພີ່ມປະສິດທິພາບ FPGA IP cores ຂອງເຂົາເຈົ້າ.

ຮຽນຮູ້ວິທີການໃຊ້ Mailbox Client ກັບ Avalon Streaming Interface FPGA IP (Mailbox Client with Avalon ST Client IP) ເພື່ອຕິດຕໍ່ສື່ສານກັບຜູ້ຈັດການອຸປະກອນທີ່ປອດໄພ (SDM) ໃນຄູ່ມືຜູ້ໃຊ້ນີ້. ຄົ້ນພົບວິທີທີ່ເຫດຜົນແບບກຳນົດເອງຂອງທ່ານສາມາດເຂົ້າເຖິງ Chip ID, ເຊັນເຊີອຸນຫະພູມ, Voltage Sensor ແລະ Quad SPI flash memory. ຄູ່ມືນີ້ຍັງກວມເອົາຄໍານິຍາມລະດັບການສະຫນັບສະຫນູນຂອງຄອບຄົວສໍາລັບ Intel FPGA IPs.

FPGA IP Design Example ຄູ່ມືຜູ້ໃຊ້ແມ່ນສໍາລັບການອອກແບບ F-Tile 25G Ethernet Intel FPGA IP, ປັບປຸງສໍາລັບ Intel Quartus Prime Design Suite ຮຸ່ນ 22.3. ຄູ່ມືສະຫນອງການເລີ່ມຕົ້ນໄວແລະໂຄງສ້າງໄດເລກະທໍລີສໍາລັບການສ້າງການອອກແບບຮາດແວ examples ແລະ testbenches. ມັນປະກອບມີ file ຄໍາອະທິບາຍ, ພາບຫນ້າຈໍບັນນາທິການພາລາມິເຕີ, ແລະຂັ້ນຕອນເພື່ອສ້າງໂຄງການ Quartus Prime ໃໝ່.