MICROCHIP PTP キャリブレーション構成ガイド

導入

この構成ガイドでは、ポート間および 1PPS キャリブレーションを実行して、入力/出力レイテンシを調整することでタイミングを改善する方法について説明します。

機能の説明

キャリブレーション結果の持続性

以下で説明するキャリブレーションの実行結果はフラッシュに保存されるため、デバイスの電源を入れ直したり、再起動したりしても結果は保持されます。

reload-defaults への永続性

以下で説明するキャリブレーションを実行した結果は、リロードのデフォルト設定後も持続します。 reload-defaults がキャリブレーションを組み込みのデフォルトにリセットする必要がある場合は、これを reload-defaults のパラメーターとして指定する必要があります。

時刻の自動調整amp 平面参照

CLI には、ループバック モードで PTP ポートの T2-T1 の差を測定し、T2 と T1 が等しくなるようにポートの送信と受信の遅延を自動的に調整するコマンドがあります。 このコマンドによって実行されるキャリブレーションは、ポートが実際に実行するように構成されているモードのみを対象としています。 ポートでサポートされているすべてのモードのキャリブレーションを行うには、モードごとにコマンドを繰り返す必要があります。

コマンドの構文は次のとおりです。

オプション「ext」は、外部ループバックが使用されていることを指定します。 「int」オプションを使用すると、ポートは内部ループバック用に構成されます。

注: リンクアップ間の遅延変動が大きいシステム (補正されていないシリアルからパラレルへのバレル シフター位置) では、キャリブレーションがリンクを複数回ダウンさせて、キャリブレーションが中間値 (平均値ではない) に確実に行われるようにします。 .

ポート間キャリブレーション

CLI には、同じスイッチの別の PTP ポート (参照ポート) に対して PTP ポートを調整するためのコマンドがあります。 このコマンドによって実行されるキャリブレーションは、ポートが実際に実行するように構成されているモードのみを対象としています。 ポートでサポートされているすべてのモードのキャリブレーションを行うには、モードごとにコマンドを繰り返す必要があります。

コマンドの構文は次のとおりです。

校正中のポートに関連付けられた PTP スレーブ インスタンスは、PTP 時間が調整されないように、プローブ モードで実行する必要があります。 キャリブレーション手順では、T2-T1 と T4-T3 の差を測定し、ケーブル遅延も考慮して、次の調整を行います。

- T2-T1-cable_latency を使用してポートの入力遅延を調整する

- T4-T3-cable_latency を使用してポートの送信遅延を調整する

注記: リンクアップ間の遅延変動が大きいシステム (シリアルからパラレルへのバレル シフター位置が補償されていない) の場合、キャリブレーションはリンクを複数回ダウンさせて、キャリブレーションが中間値 (平均値ではない) に確実に行われるようにします。

1PPS を使用した外部基準への校正

CLI には、1PPS 信号を使用して外部基準に対して PTP ポートを調整するためのコマンドがあります。 このコマンドによって実行されるキャリブレーションは、ポートが実際に実行するように構成されているモードのみを対象としています。 ポートでサポートされているすべてのモードのキャリブレーションを行うには、モードごとにコマンドを繰り返す必要があります。

コマンドの構文は次のとおりです。

synce オプションは、キャリブレーション中のポートを SyncE を使用してクロック周波数を基準にロックします。 キャリブレーション手順の一部として、キャリブレーション中のポートに関連付けられた PTP スレーブ インスタンスは、その位相を基準にロックします。 PTP スレーブが完全にロックされて安定すると、キャリブレーションによって平均パス遅延が測定され、次の調整が行われます。

- 入力遅延 = 入力遅延 + (MeanPathDelay – cable_latency)/2

- 出力レイテンシ = 出力レイテンシ + (MeanPathDelay – cable_latency)/2

注記: キャリブレーションが成功すると、平均パス遅延はケーブル遅延と等しくなります。

注記: リンクアップ間の遅延変動が大きいシステム (シリアルからパラレルへのバレル シフター位置が補償されていない) の場合、キャリブレーションはリンクを複数回ダウンさせて、キャリブレーションが中間値 (平均値ではない) に確実に行われるようにします。

1PPS スキューのキャリブレーション

「ptp cal port」コマンド (上記) は、1PPS を使用して PTP ポートを外部基準に校正します。 ただし、このキャリブレーションでは、キャリブレーション中のポートの 1PPS 信号の出力遅延は考慮されていません。 キャリブレーション中のデバイスの 1PPS 出力をリファレンスの 1PPS と一致させるには、キャリブレーションで 1PPS スキューを補正する必要があります。 CLI には、1PPS 出力スキューのポート キャリブレーションを調整するためのコマンドがあります。 このコマンドによって実行されるキャリブレーションは、ポートが実際に実行するように構成されているモードのみを対象としています。 ポートでサポートされているすべてのモードのキャリブレーションを行うには、モードごとにコマンドを繰り返す必要があります。

コマンドの構文は次のとおりです。

- ptp 校正ポートオフセット

注記: リンクアップ間の遅延変動が大きいシステム (シリアルからパラレルへのバレル シフター位置が補償されていない) の場合、キャリブレーションはリンクを複数回ダウンさせて、キャリブレーションが中間値 (平均値ではない) に確実に行われるようにします。

1PPS 入力キャリブレーション

CLI には、1PPS 入力遅延のポート キャリブレーションを調整するためのコマンドがあります。

コマンドの構文は次のとおりです。

- ptp cal 1pps

コマンドを発行する前に、遅延がわかっているケーブルを使用して、1PPS 出力を 1PPS 入力に接続する必要があります。 ケーブルはできるだけ短くしてください。 このコマンドは 1PPS 出力を有効にし、amp1PPS 入力の LTC 時間。 sampled LTC 時間は、次のように構成された遅延を反映します。 1PPS 出力バッファ遅延 + 1PPS 入力遅延 + ケーブル遅延 1PPS 出力バッファ遅延は通常、1 ns の範囲です。 1PPS 入力遅延は、PTP が 1PPS 入力を使用しているときに後で使用するために計算して保存する必要があります。

ドキュメントの終わり。

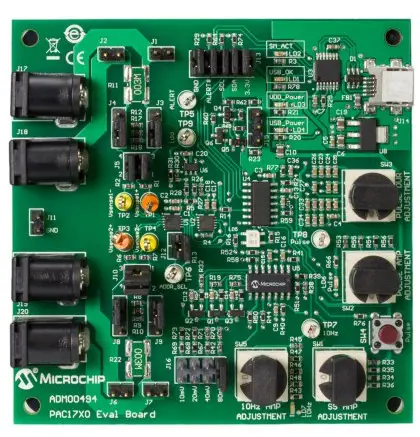

ドキュメント / リソース

|

MICROCHIP PTP キャリブレーション構成ガイド [pdf] ユーザーガイド PTP キャリブレーション構成ガイド |