SmartFusion2 MSS

SmartFusion2 MSS

MSS ஃபேப்ரிக் இடைமுகங்களைப் பயன்படுத்தி ஒரு வடிவமைப்பை உருவாக்குதல்

பயனர் வழிகாட்டி

அறிமுகம்

SmartFusion2 மைக்ரோகண்ட்ரோலர் துணை அமைப்பு (MSS) நான்கு வெவ்வேறு ஃபேப்ரிக் இன்டர்ஃபேஸ் கன்ட்ரோலர்களை (FIC) வழங்குகிறது:

- DDR_FIC

- SMC_FIC

- FIC_0 மற்றும் FIC_1, உங்கள் சாதனத்தைப் பொறுத்து

இந்த இடைமுகத் தொகுதிகள் FPGA ஃபேப்ரிக் மற்றும் வைஸில் செயல்படுத்தப்பட்ட தர்க்கத்துடன் MSS ஐ இடைமுகப்படுத்த உதவுகின்றன.

மாறாக.

நீங்கள் MSS DDR தொகுதியை (MDDR) உள்ளமைக்கும்போது DDR_FIC பயன்படுத்தப்படுகிறது, அதாவது வெளிப்புற DDR

நினைவகத்தை FPGA ஃபேப்ரிக் மாஸ்டரிலிருந்து AXI இடைமுகம் அல்லது 2 AHBLite AMBA இடைமுகங்கள் வழியாக அணுகலாம்.

நீங்கள் MSS DDR பிளாக்கை ஒற்றை தேதி விகிதம் (SDR) முறையில் உள்ளமைக்கும்போது SMC_FIC பயன்படுத்தப்படும். இந்த கட்டமைப்பில், MSS ஆனது CoreSDR_AXI போன்ற FPGA துணியில் நிறுவப்பட்ட மென்மையான நினைவகக் கட்டுப்படுத்தி வழியாக வெளிப்புற ஒற்றை தரவு வீத DRAM அல்லது ஒத்திசைவற்ற நினைவகங்களை அணுகுகிறது. SMC_FIC என்பது AXI அல்லது AHBLite அடிமை AMBA இடைமுகமாகும். DDR_FIC மற்றும் SMC_FIC இடைமுகங்கள் ஒன்றுக்கொன்று பிரத்தியேகமானவை; ஒரு நேரத்தில் ஒன்று மட்டுமே செயலில் உள்ளது.

FIC இடைமுகங்கள் இயற்கையாகவே MSS AMBA பஸ்ஸை FPGA துணியில் நீட்டிக்க உதவுகிறது. தேர்ந்தெடுக்கப்பட்ட சாதனத்தைப் பொறுத்து ஒரு MSS க்கு இரண்டு FIC நிகழ்வுகள் வரை உள்ளன. முதல் நிகழ்வு FIC_0 (இது ஒவ்வொரு சாதனத்திலும் கிடைக்கும்) மற்றும் இரண்டாவது FIC_1 என பெயரிடப்பட்டது (சிறிய சாதனங்களில் இல்லாமல் இருக்கலாம்). உங்கள் வடிவமைப்புத் தேவைகளைப் பொறுத்து நீங்கள் FIC ஐ APB3 அல்லது AHBLite AMBA இடைமுகமாக உள்ளமைக்கலாம். ஒவ்வொரு பயன்முறையிலும், ஒரு மாஸ்டர் மற்றும் ஸ்லேவ் பஸ் இடைமுகம் கிடைக்கிறது. அதாவது, துணியில் உள்ள ஒரு மாஸ்டர் MSS இல் உள்ள ஒரு அடிமைக்கு இடைமுகம் செய்யலாம் மற்றும் MSS இல் ஒரு மாஸ்டர் துணியில் ஒரு அடிமைக்கு இடைமுகம் செய்யலாம்.

ஒவ்வொரு ஃபேப்ரிக் இன்டர்ஃபேஸ் துணை அமைப்பும் வெவ்வேறு கடிகார அதிர்வெண்ணில் செயல்பட முடியும், MSS முக்கிய கடிகாரம் M3_CLK இன் விகிதமாக வரையறுக்கப்படுகிறது.

SmartFusion2 கட்டமைப்பு ஃபேப்ரிக் இடைமுகங்கள் மற்றும் FPGA ஃபேப்ரிக் இடையே க்ளாக்கிங் டொமைன்கள் தொடர்பான விதிகளை விதிக்கிறது. அத்தகைய அமைப்புகளை எவ்வாறு சரியாக உருவாக்குவது என்பது குறித்த வழிகாட்டுதலை இந்த ஆவணம் வழங்குகிறது.

உயர் நிலை View

பல்வேறு ஃபேப்ரிக் இன்டர்ஃபேஸ் கன்ட்ரோலர்கள் (எஃப்ஐசி) வழியாக எஃப்பிஜிஏ துணியுடன் எம்எஸ்எஸ் எவ்வாறு இணைகிறது என்பதை படம் 1 மற்றும் படம் 2 காட்டுகிறது. படம் 1 DDR_FIC பயன்படுத்தப்படும் போது ஒட்டுமொத்த தொகுதி வரைபடத்தைக் காட்டுகிறது (வெளிப்புற DDR நினைவகம்) மற்றும் SMC_FIC பயன்படுத்தும் போது (வெளிப்புற SDR நினைவகம்) ஒரு தொகுதி வரைபடத்தை படம் 2 காட்டுகிறது.

MSS ஐ FPGA துணியுடன் இணைக்க தேவையான MSS துணைத் தொகுதிகளை வரைபடங்கள் காட்டுகின்றன. FIC துணைத் தொகுதி உங்கள் பயன்பாட்டில் பயன்படுத்தப்படலாம் அல்லது பயன்படுத்தப்படாமல் இருக்கலாம். உங்கள் வடிவமைப்பில் DDR_FIC அல்லது SMC_FIC இடைமுகங்களையும் நீங்கள் பயன்படுத்தாமல் இருக்கலாம். இருப்பினும், வடிவமைப்பில் பயன்படுத்தப்படும் ஒன்று அல்லது அதற்கு மேற்பட்ட FIC பிளாக் மூலம் வடிவமைப்பை எவ்வாறு உருவாக்குவது என்பதற்கான ஒட்டுமொத்த தேவைகளை இது மாற்றாது.

படம் 1 • MSS முதல் FPGA ஃபேப்ரிக் பிளாக் வரைபடம் – DDR_FIC பயன்முறை

படம் 1 • MSS முதல் FPGA ஃபேப்ரிக் பிளாக் வரைபடம் – DDR_FIC பயன்முறை  படம் 2 • MSS முதல் FPGA ஃபேப்ரிக் பிளாக் வரைபடம் – SMC_FIC பயன்முறை

படம் 2 • MSS முதல் FPGA ஃபேப்ரிக் பிளாக் வரைபடம் – SMC_FIC பயன்முறை

MSS கொண்டுள்ளது:

- AHB_Bus மேட்ரிக்ஸ்; MSS இல் உள்ள அனைத்து பரிவர்த்தனைகளும் இந்த தொகுதி வழியாக செல்கின்றன.

- DDR கன்ட்ரோலர் - DDR_FIC உடனான இடைமுகங்கள்.

- DDR_FIC (SMC_FIC) துணைத் தொகுதி (நீங்கள் MSS_MDDR உள்ளமைவில் FPGA துணியை DDR பாதையில் இயக்கினால் பயன்படுத்தப்படும்).

- FIC_0 துணைத் தொகுதி.

- FIC_1 துணைத் தொகுதி (பெரிய சாதனங்களில் மட்டும்).

- FIC_2 துணைத் தொகுதி (SERDES மற்றும் வெளிப்புற DDRகளின் APB துவக்கத்திற்காக).

- MSS பிரதான கடிகாரத்துடன் (M3_CLK) தொடர்புடைய FIC கடிகாரங்களை உள்ளமைக்க MSS_CCC துணைத் தொகுதி தேவை.

- MSS இன்டர்னல் ரீசெட்களை உருவாக்கும் MSS_RESET துணைத் தொகுதி மற்றும் FPGA துணியை இயக்கும் MSS_RESET_N_M2F சிக்னல்.

FPGA துணி கொண்டுள்ளது:

- மூன்று FIC துணை அமைப்புகள் (DDR_FIC, FIC_0 மற்றும் FIC_1).

- FPGA ஃபேப்ரிக் FIC துணை அமைப்பு மற்றும் MSS பிளாக்கில் MCCC_CLK_BASE போர்ட்டை இயக்கும் கடிகாரங்களை உருவாக்க Fabric CCC – FAB_CCC – தேவை.

- FAB_CCC குறிப்பு கடிகார சமிக்ஞை - ஆன்-சிப் ஆஸிலேட்டர்களில் ஒன்றாக இருக்கலாம், வெளிப்புற கிரிஸ்டல் ஆஸிலேட்டர், துணிக்கு உள் அல்லது சிப்புக்கு வெளியே இருந்து உருவாக்கப்பட்ட கடிகாரம்.

பிளாக் வரைபடம் கடிகார வலையமைப்பை சிவப்பு நிறத்திலும் மீட்டமைக்கப்பட்ட பிணையத்தை அடர் நீல நிறத்திலும் காட்டுகிறது.

இந்த ஆவணம் இந்த தொகுதிகள் ஒவ்வொன்றையும் விவாதிக்கிறது மற்றும் கடிகாரங்களை எவ்வாறு இணைப்பது மற்றும் மீட்டமைப்பது என்பதை விவரிக்கிறது.

எம்எஸ்எஸ் கட்டமைப்பாளர்

இந்த ஆவணம் சில MSS துணைத் தொகுதிகளைக் குறிக்கிறது, அவை FIC துணைத் தொகுதிகள் வழியாக FPGA துணிக்கு MSS இடைமுகங்களை உருவாக்கும் வடிவமைப்பை உருவாக்கும் பகுதியாக கட்டமைக்கப்பட வேண்டும். அந்தத் தொகுதிகள் படம் 1-1 இல் சிவப்பு நிறத்தில் சிறப்பிக்கப்பட்டுள்ளன.

படம் 1-1 • MSS கன்ஃபிகரேட்டர்

படம் 1-1 • MSS கன்ஃபிகரேட்டர்

ஸ்மார்ட் டிசைன் மற்றும் எம்எஸ்எஸ் கான்ஃபிகரேட்டர் செயல்கள்

இந்த ஆவணத்தில் பல பொதுவான செயல்கள் குறிப்பிடப்பட்டுள்ளன; அவை பின்வரும் பட்டியலில் சுருக்கப்பட்டுள்ளன: SmartDesign மற்றும் MSS பற்றி உங்களுக்குத் தெரிந்திருந்தால் அடுத்த பகுதிக்குச் செல்லலாம்.

ஒரு மையத்தைத் துரிதப்படுத்துதல் - Libero SoC IP அட்டவணையில் இருந்து ஒரு மையத்தைத் தேர்ந்தெடுத்து, அந்த மையத்தை ஸ்மார்ட் டிசைன் கேன்வாஸில் இழுத்து விடுவது.

ஒரு மையத்தை கட்டமைத்தல் - கேன்வாஸில் அந்த மையத்தின் உதாரணத்திற்காக கான்ஃபிகரேட்டரைத் திறக்கும் செயல், ஒரு குறிப்பிட்ட உள்ளமைவைத் தேர்ந்தெடுத்து, உள்ளமைவி உரையாடல் பெட்டியில் சரி என்பதைக் கிளிக் செய்வதன் மூலம் அதைச் செய்வது. அந்த செயலின் விளைவாக, தற்போதைய உள்ளமைவுடன் தொடர்புடைய போர்ட்கள் மட்டுமே தெரியும் மற்றும் பயன்பாட்டிற்கு கிடைக்கும்.

ஒரு கூறுகளை உடனுக்குடன் - Libero SoC வடிவமைப்பு படிநிலையில் ஒரு கூறுகளைத் தேர்ந்தெடுத்து, அந்த கூறுகளை SmartDesign கேன்வாஸில் இழுத்து விடுவது.

தனிப்பயன் AMBA இணக்க கூறுகளை உடனுக்குடன் வழங்குதல் - Libero SoC வடிவமைப்பு படிநிலையில் HDL+ கூறுகளைத் தேர்ந்தெடுத்து, அந்த கூறுகளை SmartDesign Canvas இல் இழுத்து விடுதல்.

HDL+ அம்சத்தைப் பயன்படுத்தி, AMBA இணக்கமான பேருந்து இடைமுகங்களை (BIFs) உங்கள் வழக்கமான HDL தொகுதியில் சேர்க்க உதவுகிறது.

ஒரு கூறுகளை கட்டமைத்தல் - ஒரு ஸ்மார்ட் டிசைன் கேன்வாஸ் அல்லது டிசைன் படிநிலையிலிருந்து ஒரு கூறுக்கான கான்ஃபிகரேட்டரைத் திறக்கும் செயல், ஒரு குறிப்பிட்ட உள்ளமைவைத் தேர்ந்தெடுத்து, கன்ஃபிகரேட்டர் உரையாடல் பெட்டியில் சரி என்பதைக் கிளிக் செய்வதன் மூலம் அதைச் செய்கிறது. அந்தச் செயலின் விளைவாக, Libero SoC திட்டத்தில் அந்தக் கூறுகளின் அனைத்து நிகழ்வுகளும் பாதிக்கப்பட்டுள்ளன, மேலும் அவை புதுப்பிக்கப்பட வேண்டும். சமீபத்திய கூறுகளுடன் ஒரு நிகழ்வு புதுப்பிக்கப்படும் போது, தற்போதைய உள்ளமைவுடன் தொடர்புடைய போர்ட்கள் மட்டுமே தெரியும் மற்றும் பயன்பாட்டிற்கு கிடைக்கும்.

ஒரு MSS துணைத் தொகுதியை இயக்குகிறது - சில MSS துணைத் தொகுதிகளை இயக்கலாம் அல்லது முடக்கலாம், அவை தற்போதைய பயன்பாட்டில் பயன்படுத்தப்படுவதைக் குறிக்கிறது. பயன்படுத்தப்படாத அனைத்து துணைத் தொகுதிகளும் முடக்கப்பட வேண்டும்.

ஒரு MSS துணைத் தொகுதியை கட்டமைத்தல் - எம்எஸ்எஸ் கான்ஃபிகரேட்டரில் அந்த துணைத் தொகுதிக்கான கான்ஃபிகரேட்டரைத் திறந்து, ஒரு குறிப்பிட்ட உள்ளமைவைத் தேர்ந்தெடுத்து, கன்ஃபிகரேட்டர் உரையாடல் பெட்டியில் சரி என்பதைக் கிளிக் செய்வதன் மூலம் அதைச் செய்து, பின்னர் எம்எஸ்எஸ் உள்ளமைவைச் சேமிப்பது. இந்த செயல்களின் விளைவாக, MSS கூறு ஒரு புதிய கட்டமைப்பு மற்றும் புதிய போர்ட் இடைமுகத்தைக் கொண்டுள்ளது. MSS இன் நிகழ்வு சமீபத்திய கூறுகளுடன் புதுப்பிக்கப்படும் போது, தற்போதைய உள்ளமைவுடன் தொடர்புடைய MSS போர்ட்கள் மட்டுமே தெரியும் மற்றும் பயன்பாட்டிற்கு கிடைக்கும்.

FPGA துணி துணை அமைப்பை உருவாக்குதல் - ஒரு ஸ்மார்ட் டிசைன் கேன்வாஸில் உள்ள கோர்கள் மற்றும் கூறுகளை உடனுக்குடன், உள்ளமைத்தல் மற்றும் அவற்றை ஒன்றாக இணைக்கும் மற்றும் குறிப்பிட்ட ஸ்மார்ட் டிசைனில் ஏற்கனவே நிறுவப்பட்ட MSS கூறுகளுடன் இணைக்கும் செயல்.

DDR_FIC துணை அமைப்பை கட்டமைக்கிறது

DDR_FIC துணை அமைப்பை உள்ளமைக்க/உருவாக்க, நீங்கள் கண்டிப்பாக:

- DDR_FIC இடைமுகத்தை வெளிப்படுத்த MSS MDDR ஐ உள்ளமைக்கவும்

- FPGA துணி DDR_FIC துணை அமைப்பை உருவாக்கவும், உடனடி/உள்ளமைவு/இணைப்பு:

- AXI அல்லது AHBLite பேருந்து

– AXI அல்லது AHBLite பஸ் மாஸ்டர்(கள்)

- உங்கள் விண்ணப்பத்தின்படி பேருந்தில் உள்ள பிற மாஸ்டர்கள் மற்றும் சாதனங்கள்

- கடிகாரங்கள் மற்றும் மீட்டமைப்புகள்; பக்கம் 23 இல் "FIC துணை அமைப்பு கடிகாரங்களை உள்ளமைத்தல்" மற்றும் பக்கம் 27 இல் "FIC துணை அமைப்பு மீட்டமைப்பை உள்ளமைத்தல்" என்பதைப் பார்க்கவும்.

இந்த படிகள் கீழே விரிவாக விவரிக்கப்பட்டுள்ளன.

படி 1: DDR_FIC பேருந்து இடைமுகத்தை வெளிப்படுத்த MSS MDDR துணைத் தொகுதியை உள்ளமைக்கவும்

உங்கள் பயன்பாடு FPGA துணியிலிருந்து வெளிப்புற DDR நினைவகத்தை அணுக வேண்டியிருக்கும் போது DDR_FIC இடைமுகம் வெளிப்படும். இந்த கட்டமைப்பில், MDDR துணைத் தொகுதி DDR_FIC இடைமுகத்தை வெளிப்படுத்துகிறது, இது ஒரு அடிமை AXI அல்லது AHBLite பஸ் இடைமுகம் (பிஐஎஃப்) (படம் 3-1).

படம் 3-1 • FPGA ஃபேப்ரிக் மூலம் அணுகலுடன் MSS DDR உள்ளமைவு

படம் 3-1 • FPGA ஃபேப்ரிக் மூலம் அணுகலுடன் MSS DDR உள்ளமைவு

படி 2: FPGA ஃபேப்ரிக் DDR_FIC துணை அமைப்பை உருவாக்கவும்

நீங்கள் தேர்ந்தெடுத்த FPGA பஸ் இணைப்பு வகையின் அடிப்படையில் - AXI, ஒற்றை AHBLite அல்லது இரண்டு AHBLite - உங்கள் தேர்வுக்கு பொருந்தக்கூடிய துணை அமைப்பை நீங்கள் உருவாக்க வேண்டும்.

DDR_FIC/AXI துணை அமைப்பு

- பட்டியல் சாளரத்தில் இருந்து CoreAXI IP மையத்தை உடனடியாக உருவாக்கி உள்ளமைக்கவும். உங்கள் பயன்பாட்டிற்குப் பயன்படுத்தத் திட்டமிடும் ஸ்லாட்டுகளையும் உங்கள் வடிவமைப்புத் தேவைகளுக்குப் பொருந்தக்கூடிய ஸ்லாட்டுக்கான நினைவகத்தின் அளவையும் இயக்கவும். நீங்கள் வெளிப்புற DDR நினைவகத்தை அணுகுவதால், உங்கள் ஸ்லாட் அளவு தேர்வு FPGA ஃபேப்ரிக் மாஸ்டரிடமிருந்து நீங்கள் உரையாற்ற திட்டமிட்டுள்ள இடத்துடன் பொருந்த வேண்டும். (படம் 3-2).

படம் 3-2 • CoreAXI கட்டமைப்பு

படம் 3-2 • CoreAXI கட்டமைப்பு - AMBA AXI-இணக்க மாஸ்டர் கோர் அல்லது AXI பேருந்தில் மாஸ்டர் செய்ய உத்தேசித்துள்ள பாகத்தை உடனடியாக உருவாக்கி உள்ளமைக்கவும். உங்கள் விண்ணப்பத்திற்கு CoreAXI பேருந்தில் ஒன்றுக்கு மேற்பட்ட மாஸ்டர்கள் தேவைப்பட்டால், இரண்டாவது மாஸ்டரையும் உடனடியாக இயக்கவும்.

- துணை அமைப்பை இணைக்கவும்:

– CoreAXI மிரர்டு-மாஸ்டர் பஸ் இன்டர்ஃபேஸ் (BIF) போர்ட் M0 (M1) ஐ உங்கள் முதன்மை மைய நிகழ்வுகளின் (படங்களின்) முதன்மை BIF போர்ட்டுடன் இணைக்கவும் (படம் 3-3).

– MSS DDR_FIC ஸ்லேவ் BIF போர்ட்டை – MDDR_DDR_AXI_SLAVE – உங்கள் நினைவக வரைபடத் தேவையின்படி சரியான CoreAXI பஸ் மிரர்டு-ஸ்லேவ் ஸ்லாட்டுடன் இணைக்கவும். அந்த பேருந்தில் உங்களுக்கு வேறு அடிமைகள் இருந்தால், உங்கள் நினைவக வரைபடத்தின்படி அவர்களையும் இணைக்கவும்.

- கடிகாரங்கள் மற்றும் மீட்டமைப்புகள்; பக்கம் 23 இல் "FIC துணை அமைப்பு கடிகாரங்களை உள்ளமைத்தல்" மற்றும் பக்கம் 27 இல் "FIC துணை அமைப்பு மீட்டமைப்பை உள்ளமைத்தல்" ஆகியவற்றைப் பார்க்கவும்.

படம் 3-3 • DDR_FIC AXI துணை அமைப்பு

படம் 3-3 • DDR_FIC AXI துணை அமைப்பு

DDR_FIC/Single-AHBLite துணை அமைப்பு

- CoreAHBLite IP மையத்தை Catalog இலிருந்து உடனடியாக உருவாக்கவும் மற்றும் உள்ளமைக்கவும். படம் 3-4 இல் காட்டப்பட்டுள்ளபடி உங்கள் பயன்பாட்டிற்கு நீங்கள் பயன்படுத்த திட்டமிட்டுள்ள ஸ்லாட்டுகளை இயக்கவும். இதில் முன்னாள்ample, CoreAHBLite ஆனது மாஸ்டர் M4 இலிருந்து slot0 ஐப் பயன்படுத்தி ஒரு 0GB DDR RAM நினைவக இடத்தைப் பெறுவதற்காக கட்டமைக்கப்பட்டுள்ளது. நீங்கள் வெளிப்புற DDR நினைவகத்தைப் பற்றி பேசுவதால், உங்கள் ஸ்லாட் அளவு தேர்வு FPGA ஃபேப்ரிக் மாஸ்டரிடமிருந்து நீங்கள் தொடர்பு கொள்ளத் திட்டமிடும் DDR நினைவக இடத்தின் அளவோடு பொருந்த வேண்டும்.

படம் 3-4 • கோர் AHBLite - ஒருங்கிணைந்த பகுதி முதன்மை கட்டமைப்பு

படம் 3-4 • கோர் AHBLite - ஒருங்கிணைந்த பகுதி முதன்மை கட்டமைப்பு - CoreAHBLite பேருந்தில் மாஸ்டர் செய்ய நோக்கம் கொண்ட AMBA AHBLite இணக்க மாஸ்டர் கோர் அல்லது பாகத்தை உடனடியாக உருவாக்கி உள்ளமைக்கவும். உங்கள் விண்ணப்பத்திற்கு CoreAHBLite பேருந்தில் ஒன்றுக்கு மேற்பட்ட மாஸ்டர்கள் தேவைப்பட்டால், கூடுதல் மாஸ்டர்களையும் உடனுக்குடன் செலுத்தவும். CoreAHBLite பேருந்தில் நான்கு மாஸ்டர்கள் வரை துணைபுரிகின்றனர்.

- துணை அமைப்பை இணைக்கவும்:

– CoreAHBLite மிரர்டு-மாஸ்டர் பஸ் இன்டர்ஃபேஸ் (BIF) போர்ட் M0 (M1) ஐ உங்கள் மாஸ்டர் கோர் இன்ஸ்டன்ஸ்(களின்) மாஸ்டர் BIF போர்ட்டுடன் இணைக்கவும்.

– MSS DDR_FIC ஸ்லேவ் BIF போர்ட்டை – MDDR_DDR_AHB0_SLAVE – சரியான CoreAHBLite பஸ் மிரர்டு-ஸ்லேவ் ஸ்லாட்டுடன் இணைக்கவும் (இந்த முன்னாள்ample) உங்கள் நினைவக வரைபடத் தேவையின்படி. அந்த பேருந்தில் உங்களுக்கு வேறு அடிமைகள் இருந்தால், உங்கள் நினைவக வரைபடத்தின்படி அவர்களையும் இணைக்கவும்.

- கடிகாரங்கள் மற்றும் மீட்டமைப்புகள்; பக்கம் 23 இல் "FIC துணை அமைப்பு கடிகாரங்களை உள்ளமைத்தல்" மற்றும் பக்கம் 27 இல் "FIC துணை அமைப்பு மீட்டமைப்பை உள்ளமைத்தல்" ஆகியவற்றைப் பார்க்கவும்.

படம் 3-5 • DDR_FIC AHBLite துணை அமைப்பு

படம் 3-5 • DDR_FIC AHBLite துணை அமைப்பு

DDR_FIC/இரண்டு AHBLite துணை அமைப்பு

MDDRக்கான இரண்டு AHBLite இன்டர்ஃபேஸ் விருப்பத்தைத் தேர்ந்தெடுக்கும்போது, புதிய ஸ்லேவ் உடன் இணைக்க, MSS பாகத்தில் கூடுதல் BIF, MDDR_DDR_AHB1_SLAVE BIF வெளிப்படும்.

இந்த உள்ளமைவுக்கு, MSS கூறுகளில் வெளிப்படும் MDDR_DDR_AHB1_SLAVE BIF இடைமுகத்திற்கான ஒற்றை AHBLite உள்ளமைவுக்கான படிகளை மீண்டும் செய்யவும்.

SMC_FIC ஆனது AXI அல்லது AHBLite பஸ் இடைமுகமாகப் பயன்படுத்தப்பட்டாலும், CoreSDR_AXI மையத்துடன் இணைக்க AXI பயன்முறையில் உள்ளமைக்கப்பட்ட SMC_FIC இடைமுகத்தை எவ்வாறு பயன்படுத்துவது என்பதை மட்டுமே இந்த ஆவணம் விவரிக்கிறது. அந்த மையமானது ஒரு AXI-அடிப்படையிலான SDR ரேம் கன்ட்ரோலர் ஆகும், இந்த விஷயத்தில், MSS ஐ வெளிப்புற ஒற்றை தரவு வீத (SDR) நினைவக கூறுகளுடன் இணைக்கப் பயன்படுகிறது. பின்வரும் விளக்கத்திலிருந்து AHBLite இடைமுகத்தை எவ்வாறு பயன்படுத்துவது என்பதை நீங்கள் எளிதாக ஊகிக்க முடியும்; படிகள் மிகவும் ஒத்தவை. AXI இடைமுகம் மிகவும் திறமையான இடைமுகம் மற்றும் விருப்பமான விருப்பமாகும்.

SMC_FIC துணை அமைப்பை உள்ளமைக்க/உருவாக்க, நீங்கள் கண்டிப்பாக:

- SMC_FIC இடைமுகத்தை வெளிப்படுத்த MSS MDDR ஐ உள்ளமைக்கவும்

- FPGA துணி DDR_FIC துணை அமைப்பை உருவாக்கவும், இதில் உடனடி/உள்ளமைவு/இணைப்பு:

- CoreAXI பேருந்து

– CoreSDR_AXI

- உங்கள் விண்ணப்பத்தின்படி பேருந்தில் உள்ள பிற மாஸ்டர்கள் மற்றும் சாதனங்கள்

- கடிகாரங்கள் மற்றும் மீட்டமைப்புகள்; பக்கம் 23 இல் "FIC துணை அமைப்பு கடிகாரங்களை உள்ளமைத்தல்" மற்றும் பக்கம் 27 இல் "FIC துணை அமைப்பு மீட்டமைப்பை உள்ளமைத்தல்" என்பதைப் பார்க்கவும்.

இந்த படிகள் கீழே விரிவாக விவரிக்கப்பட்டுள்ளன.

படி 1: SMC_FIC பஸ் இடைமுகத்தை வெளிப்படுத்த MSS MDDR துணைத் தொகுதியை உள்ளமைக்கவும்

உங்கள் பயன்பாட்டிற்கு FPGA துணி மூலம் வெளிப்புற SDR நினைவகத்தை அணுக வேண்டியிருக்கும் போது SMC_FIC இடைமுகம் வெளிப்படும். இந்த கட்டமைப்பில், MDDR துணைத் தொகுதி SMC_FIC இடைமுகத்தை வெளிப்படுத்துகிறது, இது முதன்மை AXI அல்லது AHBL பஸ் இடைமுகம் (பிஐஎஃப்) (படம் 4-1).

- MSS கான்ஃபிகரேட்டருக்குள் இருக்கும் MDDR கன்ட்ரோலரை வலது கிளிக் செய்து, Configure என்பதைத் தேர்ந்தெடுக்கவும்.

- AXI இடைமுகத்தைப் பயன்படுத்து என்பதைத் தேர்ந்தெடுக்கவும்.

- சரி என்பதைக் கிளிக் செய்யவும்.

படம் 4-1 • MDDR சாஃப்ட் மெமரி கன்ட்ரோலர் உள்ளமைவு

படம் 4-1 • MDDR சாஃப்ட் மெமரி கன்ட்ரோலர் உள்ளமைவு

- மாற்றத்துடன் MSS கூறுகளைப் புதுப்பிக்கவும்.

(எம்எஸ்எஸ் கூறுகளை வலது கிளிக் செய்து, சமீபத்திய கூறுகளுடன் புதுப்பிப்பு நிகழ்வுகளைத் தேர்ந்தெடுக்கவும்). MDDR_SMC_AXI_MASTER ஆனது MSS பாகத்தின் பஸ் இன்டர்ஃபேஸ் போர்ட்டாக வெளிப்படுகிறது.

படி 2: FPGA ஃபேப்ரிக் SMC_FIC துணை அமைப்பை உருவாக்கவும்

- படம் 0-0 இல் காட்டப்பட்டுள்ளபடி, ஸ்லேவ் ஸ்லாட் S4 க்கு முதன்மை ஸ்லாட் M2 இயக்கப்படும் வகையில் CoreAXI ஐ உடனடியாக உருவாக்கி உள்ளமைக்கவும். நீங்கள் ஒரு மென்மையான நினைவகக் கட்டுப்படுத்தி மூலம் வெளிப்புற நினைவகத்தைக் கையாள்வதால், உங்கள் ஸ்லாட் அளவு தேர்வு, நீங்கள் Cortex-M3 செயலி அல்லது MSS DDR பிரிட்ஜ் வழியாக அந்த வெளிப்புற நினைவகத்திற்கு எழுதும் ஏதேனும் வெளிப்புற நினைவக இடத்தின் அளவுடன் பொருந்த வேண்டும்.

படம் 4-2 • CoreAXI கட்டமைப்பு – SMC_FIC பயன்முறை

படம் 4-2 • CoreAXI கட்டமைப்பு – SMC_FIC பயன்முறை - IP அட்டவணையில் இருந்து, CoreSDR_AXI ஐ உடனடியாக உருவாக்கி உங்கள் வெளிப்புற நினைவக அளவுருக்களுடன் பொருந்துமாறு கட்டமைக்கவும்.

- துணை அமைப்பை இணைக்கவும் (படம் 4-3):

– MSS SMC_FIC மாஸ்டர் BIF போர்ட்டை – MDDR_SMC_AXI_MASTER – CoreAXI பஸ் மிரர்டு-மாஸ்டர் M0 உடன் இணைக்கவும்.

– CoreAXI மிரர்டு-ஸ்லேவ் பஸ் இன்டர்ஃபேஸ் (BIF) போர்ட் S0ஐ CoreSDR_AXI கோர் இன்ஸ்டன்ஸ் ஸ்லேவ் BIF போர்ட்டுடன் இணைக்கவும்.

- கடிகாரங்கள் மற்றும் மீட்டமைப்புகள்; பக்கம் 23 இல் "FIC துணை அமைப்பு கடிகாரங்களை உள்ளமைத்தல்" மற்றும் பக்கம் 27 இல் "FIC துணை அமைப்பு மீட்டமைப்பை உள்ளமைத்தல்" ஆகியவற்றைப் பார்க்கவும்.

படம் 4-3 • SMC_FIC துணை அமைப்பு இணைப்புகள்

படம் 4-3 • SMC_FIC துணை அமைப்பு இணைப்புகள்

FIC துணை அமைப்புகளை கட்டமைத்தல்

ஒரு FIC துணை அமைப்பை உள்ளமைக்க/உருவாக்க, நீங்கள் கண்டிப்பாக:

- FIC இடைமுகத்தை வெளிப்படுத்த MSS FIC ஐ கட்டமைக்கவும்

- FPGA துணி FIC துணை அமைப்பை உருவாக்கவும், உடனடி/உள்ளமைவு/இணைப்பு:

- APB3 அல்லது AHBLite பேருந்து

- APB3 மற்றும் AHBLite இணக்க மாஸ்டர் மற்றும்/அல்லது சாதனங்கள் உள்ளமைவு மற்றும் உங்கள் விண்ணப்பத்தின் தேவைக்கேற்ப பஸ்ஸில் இணைப்பு

- கடிகாரங்கள் மற்றும் மீட்டமைப்புகள்; பக்கம் 23 இல் "FIC துணை அமைப்பு கடிகாரங்களை உள்ளமைத்தல்" மற்றும் பக்கம் 27 இல் "FIC துணை அமைப்பு மீட்டமைப்பை உள்ளமைத்தல்" என்பதைப் பார்க்கவும்.

இந்த படிகள் கீழே விரிவாக விவரிக்கப்பட்டுள்ளன.

படி 1: MSS FIC துணைத் தொகுதியை உள்ளமைக்கவும்

- FIC கான்ஃபிகரேட்டரை அழைக்கவும் மற்றும் FIC கான்ஃபிகரேட்டரைத் திறக்க FIC_0 அல்லது FIC_1 மீது வலது கிளிக் செய்யவும்.

- MSS முதல் FPGA ஃபேப்ரிக் இன்டர்ஃபேஸ் உள்ளமைவுக் குழுவிற்கான கான்ஃபிகரேட்டரில் தேர்ந்தெடுக்கவும்:

- AHBLite அல்லது APB3 இடைமுக வகை

- FPGA துணியின் முதன்மையாக இடைமுகத்தைப் பயன்படுத்த விரும்புகிறீர்களா

- FPGA துணியால் தேர்ச்சி பெற்ற அடிமையாக இடைமுகத்தைப் பயன்படுத்த விரும்புகிறீர்களா (படம் 5-1)

படம் 5-1 • MSS முதல் FPGA ஃபேப்ரிக் இன்டர்ஃபேஸ் விருப்பங்கள்

படம் 5-1 • MSS முதல் FPGA ஃபேப்ரிக் இன்டர்ஃபேஸ் விருப்பங்கள் - நீங்கள் AHBLite இடைமுகத்தைப் பயன்படுத்துகிறீர்கள் என்றால், பைபாஸ் பயன்முறையைத் தேர்ந்தெடுக்க மேம்பட்ட AHBLite விருப்பங்களையும் பயன்படுத்தலாம் அல்லது துணியின் மாஸ்டராகச் செயல்பட இடைமுகத்தைத் தேர்ந்தெடுத்தால் மாஸ்டர் ஐடி போர்ட்டை வெளிப்படுத்தலாம் (படம் 5-2).

படம் 5-2 • மேம்பட்ட AHBLite விருப்பங்கள்

படம் 5-2 • மேம்பட்ட AHBLite விருப்பங்கள்

படி 2: FPGA Fabric FIC துணை அமைப்பை உருவாக்கவும்

ஒவ்வொரு FIC இடைமுகம் வெளிப்படும் - மாஸ்டர் மற்றும் ஸ்லேவ், நீங்கள் தேர்ந்தெடுத்த வகையுடன் பொருந்தக்கூடிய ஒரு பஸ்ஸை (CoreAHBLite அல்லது CoreAPB3) உடனடியாக இயக்க வேண்டும். இடைமுகப் பங்கு (மாஸ்டர்/ஸ்லேவ்) மற்றும் வகை (AHBLite/APB3) ஆகியவற்றைப் பொறுத்து, பேருந்து பின்வருமாறு கட்டமைக்கப்பட வேண்டும்:

மாஸ்டர்/AHBLite

CoreAHBLite பேருந்தை பின்வருமாறு கட்டமைக்கவும்:

- உங்கள் தேவைகளுக்குப் பொருந்தும் நினைவக இட விருப்பத்தைத் தேர்ந்தெடுக்கவும்:

– உங்கள் அனைத்து உபகரணங்களிலும் 16 MB க்கும் குறைவான முகவரி இடம் தேவைப்பட்டால், படம் 5-3 இல் காட்டப்பட்டுள்ள விருப்பத்தைத் தேர்ந்தெடுக்கவும். இந்த பயன்முறையானது 16 16MB ஸ்லாட்டுகளை வழங்குகிறது, அவை 16 AHBLite அடிமைகளை இணைக்கப் பயன்படும்.

படம் 5-3 • மாஸ்டர்/ஏஎச்பிலைட் மெமரி ஸ்பேஸ் உள்ளமைவு - ஒரு ஸ்லாட்டுக்கு 16 எம்பி

படம் 5-3 • மாஸ்டர்/ஏஎச்பிலைட் மெமரி ஸ்பேஸ் உள்ளமைவு - ஒரு ஸ்லாட்டுக்கு 16 எம்பி

– உங்களுக்கு 16 MB க்கு மேல் மற்றும் 256 MB க்கும் குறைவான முகவரி இடம் தேவைப்பட்டால், படம் 5-4 இல் காட்டப்பட்டுள்ள விருப்பத்தைத் தேர்ந்தெடுக்கவும். இந்த பயன்முறையானது 16 AHBLite அடிமைகளை இணைக்கப் பயன்படுத்தக்கூடிய 256 16 MB ஸ்லாட்டுகளை வழங்குகிறது.

படம் 5-4 • மாஸ்டர்/ஏஎச்பிலைட் மெமரி ஸ்பேஸ் உள்ளமைவு - ஒரு ஸ்லாட்டுக்கு 256 எம்பி

படம் 5-4 • மாஸ்டர்/ஏஎச்பிலைட் மெமரி ஸ்பேஸ் உள்ளமைவு - ஒரு ஸ்லாட்டுக்கு 256 எம்பி - உங்கள் பயன்பாட்டிற்கு நீங்கள் பயன்படுத்தும் இடங்களை இயக்கவும் (படம் 5-5). பக்கம் 1 இல் படம் 4-2 இல் காட்டப்பட்டுள்ளபடி அணுகல்களை ஸ்லாட் செய்ய M15 ஐப் பயன்படுத்துவது சிறந்த நடைமுறையாகும்.

குறிப்பு: நீங்கள் ஒரு மல்டி மாஸ்டர் துணை அமைப்பை உருவாக்க திட்டமிட்டால் M1 ஐப் பயன்படுத்தவும், அங்கு நீங்கள் துணியில் மாஸ்டர் இருந்தால், அதற்கு ரீமேப் அம்சம் தேவைப்படுகிறது, எனவே M0 உடன் இணைக்கப்பட வேண்டும்.

– நீங்கள் ஒரு ஸ்லாட்டுக்கு 16 MB விருப்பத்தைத் தேர்ந்தெடுத்திருந்தால், எந்த ஸ்லாட்டுகளைப் பயன்படுத்தலாம் என்பதில் எந்தக் கட்டுப்பாடுகளும் இல்லை.

– நீங்கள் ஒரு ஸ்லாட்டுக்கு 256 MB விருப்பத்தைத் தேர்ந்தெடுத்திருந்தால், FIC இன்ஸ்டன்ஸ் ஃபேப்ரிக் மெமரி அட்ரஸ் பிராந்தியங்களின் தேர்வுடன் இணக்கமான ஸ்லாட்டுகளை மட்டுமே பயன்படுத்த முடியும். ஒவ்வொரு FIC நினைவக முகவரி பகுதியும் 256 MB அளவில் உள்ளது. ஆறு FIC நினைவகப் பகுதிகள் அட்டவணை 5 -1 இல் சுருக்கப்பட்டுள்ளன.

அட்டவணை 5-1 • முகவரி பகுதிகள் மற்றும் ஒரு ஸ்லாட் விருப்பத்திற்கு 256 எம்பிக்கு இணக்கமான ஸ்லாட்டுகள்

நினைவக முகவரி மண்டலம் இணக்கமான இடங்கள் 30000000-3FFFFFF 3 50000000-5FFFFFF 5 70000000-7FFFFFF 7 80000000-8FFFFFF 8 90000000-9FFFFFF 9 F0000000-FFFFFFF 15 (F)  படம் 5-5 • Master/AHBLite முதன்மை அணுகல் உள்ளமைவு

படம் 5-5 • Master/AHBLite முதன்மை அணுகல் உள்ளமைவு - AHBLite இணக்கமான புற கோர்கள் மற்றும்/அல்லது தனிப்பயன் AHBLite இணக்க கூறுகளை உடனுக்குடன் மற்றும் உள்ளமைக்கவும்.

- துணை அமைப்பை இணைக்கவும்:

– CoreAHBLite மிரர்டு-மாஸ்டர் பஸ் இன்டர்ஃபேஸ் (BIF) போர்ட் M1 ஐ MSS மாஸ்டர் BIF போர்ட்டுடன் இணைக்கவும் – FIC_0/1_AHB_MASTER – படம் 5-6 இல் காட்டப்பட்டுள்ளது.

- உங்கள் நினைவக வரைபடத் தேவையின்படி AHBLite அடிமைகளை சரியான ஸ்லாட்டுகளுடன் இணைக்கவும்.

- கடிகாரங்கள் மற்றும் மீட்டமைப்புகள்; பக்கம் 23 இல் "FIC துணை அமைப்பு கடிகாரங்களை உள்ளமைத்தல்" மற்றும் பக்கம் 27 இல் "FIC துணை அமைப்பு மீட்டமைப்பை உள்ளமைத்தல்" ஆகியவற்றைப் பார்க்கவும்.

படம் 5-6 • FIC மாஸ்டர்/AHBLite துணை அமைப்பு

படம் 5-6 • FIC மாஸ்டர்/AHBLite துணை அமைப்பு

மாஸ்டர்/APB3

CoreAPB3 பஸ்ஸை பின்வருமாறு கட்டமைக்கவும்:

- படம் 5-7 இல் காட்டப்பட்டுள்ளபடி முகவரி கட்டமைப்பு விருப்பங்களைத் தேர்ந்தெடுக்கவும். இந்த பயன்முறை பதினாறு 16MB ஸ்லாட்டுகளை வழங்குகிறது, அவை பதினாறு APB3 இணக்கமான அடிமைகளை இணைக்கப் பயன்படும். அதிக நினைவகத்துடன் கூடிய ஸ்லாட்டுகள் உங்களுக்குத் தேவைப்பட்டால், பெரிய ஸ்லாட்டை உருவாக்க பல அடிமைகளை இணைக்கலாம். இந்த விருப்பத்தைப் பற்றிய கூடுதல் விவரங்களுக்கு CoreAPB3 பயனர் வழிகாட்டியைப் பார்க்கவும்.

படம் 5-7 • முதன்மை/APB3 முகவரி கட்டமைப்பு

படம் 5-7 • முதன்மை/APB3 முகவரி கட்டமைப்பு - படம் 5-8 இல் காட்டப்பட்டுள்ளபடி, உங்கள் பயன்பாட்டிற்கு நீங்கள் பயன்படுத்தும் ஸ்லாட்டுகளை இயக்கவும்.

படம் 5-8 • மாஸ்டர்/ஏபிபி3 ஸ்லேவ் ஸ்லாட்டுகள் உள்ளமைவு

படம் 5-8 • மாஸ்டர்/ஏபிபி3 ஸ்லேவ் ஸ்லாட்டுகள் உள்ளமைவு - APB3 இணக்கமான புற கோர்கள் மற்றும்/அல்லது தனிப்பயன் APB3 இணக்க கூறுகளை உடனடி மற்றும் உள்ளமைக்கவும்.

- துணை அமைப்பை இணைக்கவும்:

– CoreAPB3 மிரர்டு-மாஸ்டர் பஸ் இன்டர்ஃபேஸ் (BIF) போர்ட்டை MSS மாஸ்டர் BIF போர்ட்டுடன் இணைக்கவும் FIC_0/1_APB_MASTER – படம் 5-9 இல் காட்டப்பட்டுள்ளது.

- உங்கள் நினைவக வரைபடத் தேவையின்படி APB3 அடிமைகளை சரியான இடங்களுடன் இணைக்கவும்.

- கடிகாரங்கள் மற்றும் மீட்டமைப்புகள்; பக்கம் 23 இல் "FIC துணை அமைப்பு கடிகாரங்களை உள்ளமைத்தல்" மற்றும் பக்கம் 27 இல் "FIC துணை அமைப்பு மீட்டமைப்பை உள்ளமைத்தல்" ஆகியவற்றைப் பார்க்கவும்.

படம் 5-9 • FIC மாஸ்டர்/APB3 துணை அமைப்பு

படம் 5-9 • FIC மாஸ்டர்/APB3 துணை அமைப்பு

அடிமை/AHBLite

இந்த நேரத்தில் கிடைக்கவில்லை.

அடிமை/APB3

இந்த நேரத்தில் கிடைக்கவில்லை.

FIC துணை அமைப்பு கடிகாரங்களை கட்டமைக்கிறது

சரியான கடிகார கட்டமைப்பு மற்றும் இணைப்பை உருவாக்க, நீங்கள் கண்டிப்பாக:

- MSS CCC FIC கடிகாரங்களை உள்ளமைக்கவும்

- FPGA ஃபேப்ரிக் CCC மையத்தை உடனடியாக உருவாக்கி உள்ளமைக்கவும்

- ஒவ்வொரு FIC துணை அமைப்புக்கும் கடிகார நெட்வொர்க்குகளை இணைக்கவும்

- MSS CLK_BASE போர்ட்டை சரியான FPGA துணி FIC துணை அமைப்பு கடிகார நெட்வொர்க்குடன் இணைக்கவும்

SmartFusion2 கட்டமைப்பானது MSS லாஜிக் மற்றும் FPGA ஃபேப்ரிக் லாஜிக் ஆகியவற்றிற்கு இடையே சரியாக தொடர்பு கொள்ள அனைத்து FIC துணை அமைப்புகளுக்கும் பின்பற்ற வேண்டிய பல விதிகளை விதிக்கிறது. இந்த விதிகள் கீழே வரையறுக்கப்பட்டு படம் 6-1 இல் காட்டப்பட்டுள்ளன.

- ஒவ்வொரு FPGA ஃபேப்ரிக் FIC துணை அமைப்பும் MSS CCC கன்ஃபிகரேட்டரில் குறிப்பிட்ட துணை அமைப்பில் வரையறுக்கப்பட்ட அதிர்வெண்ணுடன் பொருந்தக்கூடிய கடிகார அதிர்வெண்ணால் இயக்கப்பட வேண்டும்.

- அனைத்து FPGA துணி FIC துணை அமைப்பு கடிகாரங்கள் துல்லியமாக சீரமைக்கப்பட வேண்டும்; கடிகாரங்கள் வெவ்வேறு அலைவரிசைகளில் இருக்கலாம், ஆனால் மெதுவான கடிகாரங்களின் உயரும் விளிம்புகள் வேகமான கடிகாரங்களின் உயரும் விளிம்புகளுடன் சீரமைக்கப்பட வேண்டும்.

- மிகச்சிறிய அதிர்வெண் கொண்ட FPGA துணி FIC துணை அமைப்பு கடிகாரம் MSS CLK_BASE ஐ இயக்க வேண்டும்.

- துணி கடிகாரங்கள் துணி CCC இலிருந்து பெறப்பட்டால் (PLL உடன்), துணி CCC LOCK வெளியீடு MSS_CCC_CLK_BASE_PLL_LOCK போர்ட்டுடன் இணைக்கப்பட வேண்டும். MSS CCC Fabric Alignment Circuitry (FACC) ஆனது CLK_BASE PLL LOCK சிக்னலைக் கண்காணித்து, CLK_BASE ஆனது காத்திருப்பு கடிகாரத்திலிருந்து (சாதனத்தை துவக்கும் போது பயன்படுத்தப்படும் கடிகாரம்) CLK_BASE இலிருந்து பெறப்பட்ட பயனர் உள்ளமைக்கப்பட்ட கடிகாரத்திற்கு மாறுவதற்கு முன், CLK_BASE நிலையானது என்பதை உறுதிப்படுத்துகிறது.

படம் 6-1 • துணை அமைப்பு கடிகார விதிகள்

படம் 6-1 • துணை அமைப்பு கடிகார விதிகள்

உங்கள் அனைத்து FIC துணை அமைப்புகளுக்கும் கடிகார நெட்வொர்க்குகளை உள்ளமைக்க கீழே உள்ள படிகளைப் பின்பற்றவும்.

படி 1: MSS CCC துணைத் தொகுதியை உள்ளமைக்கவும்

உங்கள் வடிவமைப்பில் பயன்படுத்தப்படும் ஒவ்வொரு FIC தொகுதிக்கும் (FIC_0, FIC_1 மற்றும் DDR_FIC/SMC_FIC), படம் 6-2 இல் காட்டப்பட்டுள்ளபடி MSS கடிகார கட்டமைப்பில் (MSS_CCC) கடிகார வகுப்பிகளைத் தேர்ந்தெடுக்கவும். படம் 6-2 • MSS CCC FIC கடிகார கட்டமைப்பு

படம் 6-2 • MSS CCC FIC கடிகார கட்டமைப்பு

குறிப்பு CLK_BASE புலம் திருத்த முடியாதது. SmartFusion2 கட்டமைப்பால் விதிக்கப்பட்ட CLK_BASE அதிர்வெண் அனைத்து FIC கடிகார அதிர்வெண்களின் குறைந்தபட்ச அதிர்வெண்ணாக இருக்க வேண்டும் மற்றும் MSS CCC கட்டமைப்பாளரால் தானாகவே கணக்கிடப்படும். CLK_BASE உள்ளமைவு பற்றிய கூடுதல் விவரங்களுக்கு பக்கம் 3 இல் உள்ள “படி 25: FPGA Fabric FIC துணை அமைப்புகள் கடிகார நெட்வொர்க்குகளை இணைக்கவும்” என்பதைப் பார்க்கவும்.

படி 2: FPGA ஃபேப்ரிக் FIC கடிகாரங்களை உள்ளமைக்கவும்

ஒரு துணி CCC ஐ (PLL உடன்) உடனடியாக உருவாக்கி, பக்கம் 23 இல் விவரிக்கப்பட்டுள்ள FIC துணை அமைப்பு கடிகார விதிகளைப் பூர்த்தி செய்ய அதை உள்ளமைக்கவும். நீங்கள் பொதுவாக ஒவ்வொரு FIC கடிகாரத்திற்கும் உலகளாவிய வெளியீட்டை (GLx) இணைக்க வேண்டும், ஒவ்வொரு வெளியீட்டிற்கும் அதன் அதிர்வெண்ணைக் குறிப்பிடவும் ( MSS CCC இல் வரையறுக்கப்பட்ட அதிர்வெண்களுடன் பொருந்துகிறது) மற்றும் பிஎல்எல் வெளியீட்டில் இருந்து பெறப்பட்ட அனைத்து உலகளாவிய வெளியீடுகளையும் கட்ட சீரமைப்புக்கு உத்தரவாதம் அளிக்க வேண்டும் (படம் 6-3 இல் காட்டப்பட்டுள்ளது).

குறிப்பு: இரண்டு FIC துணை அமைப்புகள் ஒரே அதிர்வெண்களைக் கொண்டிருந்தால், CCC துணியிலிருந்து இரண்டு சுயாதீன உலகளாவிய வெளியீடுகளை நீங்கள் உருவாக்க வேண்டியதில்லை; ஒன்று போதுமானது. படம் 6-3 • PLL உடன் Fabric CCC

படம் 6-3 • PLL உடன் Fabric CCC

படி 3: FPGA Fabric FIC துணை அமைப்புகள் கடிகாரத்தை இணைக்கவும் நெட்வொர்க்குகள்

ஒவ்வொரு துணி CCC உலகளாவிய வெளியீடு GLx ஐயும் அது தொடர்புடைய FIC துணை அமைப்புடன் இணைக்கவும்.

படி 4: MSS CLK_BASE போர்ட்டை இணைக்கவும்

மெதுவான துணி CCC உலகளாவிய வெளியீடு GLx ஐ MSS CLK_BASE போர்ட்டுடன் இணைக்கவும்.

படி 5: MSS MCCC_CLK_BASE_PLL_LOCK போர்ட்டை இணைக்கவும்

துணி CCC LOCK வெளியீட்டை MSS MCCC_CLK_BASE_PLL_LOCK போர்ட்டுடன் இணைக்கவும்.

நேர பகுப்பாய்வு தேவைகள்

MSS CCC மற்றும் FPGA ஃபேப்ரிக் CCC கட்டமைப்புகளில் வரையறுக்கப்பட்ட நேரத் தேவைகளை வடிவமைப்பு பூர்த்திசெய்கிறதா என்பதை உறுதிசெய்ய பிந்தைய தளவமைப்பு நிலையான நேரப் பகுப்பாய்வைச் செய்யவும். நிலையான நேர பகுப்பாய்வைக் கடக்கும் வடிவமைப்பைப் பெற நீங்கள் M3_CLK ஐ மாற்ற வேண்டும் அல்லது MSS மற்றும் துணிக்கு இடையே கடிகார விகிதத்தை அதிகரிக்க வேண்டும்.

FIC துணை அமைப்பு மீட்டமைப்பை கட்டமைக்கிறது

FIC துணை அமைப்பு மீட்டமைப்பை உள்ளமைக்க:

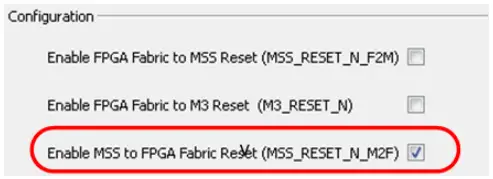

- MSS கான்ஃபிகரேட்டரில் இருந்து, MSS_RESET_N_M2F போர்ட்டை வெளிப்படுத்த MSS ரீசெட் துணைத் தொகுதியை உள்ளமைக்கவும்.

படம் 7-1 • MSS மீட்டமைப்பு துணைத் தொகுதியை உள்ளமைக்கவும்

படம் 7-1 • MSS மீட்டமைப்பு துணைத் தொகுதியை உள்ளமைக்கவும் - MSS_RESET_N_M2F போர்ட்டை அனைத்து FPGA ஃபேப்ரிக் FIC துணை அமைப்புகளின் மீட்டமைப்பு போர்ட்களுடன் இணைக்கவும்.

கணினி நினைவக வரைபடத்தை கட்டமைக்கிறது

ஒவ்வொரு புறமும் (AMBA AXI, AHBLite மற்றும் APB3 அடிமைகள்) FIC துணை அமைப்பின் முதன்மை புள்ளியிலிருந்து ஒரு முகவரி மூலம் அடையாளம் காணப்படுகின்றன. view. ஒரு துணை அமைப்பின் எஜமானர்கள் மற்றும் அடிமைகளுக்கு இடையிலான ஒட்டுமொத்த உறவுகளை அந்த துணை அமைப்பின் நினைவக வரைபடமாக நாங்கள் பொதுவாகக் குறிப்பிடுகிறோம். துணை அமைப்பின் நினைவக வரைபடத்தை SmartDesign இல் திருத்தலாம். உங்களாலும் முடியும் view முழு கணினியையும் உருவாக்கும் போது உங்கள் கணினியின் இறுதி நினைவக வரைபடம். நினைவக வரைபடம் என்பது உங்கள் வடிவமைப்பின் 'ரூட்'க்காக உருவாக்கப்பட்ட தரவுத்தாளின் ஒரு பகுதியாகும்.

நினைவக வரைபடத்தை கட்டமைத்தல் (பொதுவான ஸ்மார்ட் டிசைன் நடத்தை)

SmartDesign இல், துணை அமைப்பில் உள்ள பேருந்தின் அடிப்படை முகவரி மற்றும் அந்த பேருந்தின் ஸ்லாட் எண்ணின் ஸ்லாட் அளவைக் கொண்டு ஒரு பேருந்தில் ஒரு புற முகவரி ஒதுக்கப்படும். எனவே ஒரு புறத்திற்கான ஸ்லாட் எண்ணை மாற்றுவது அதன் முகவரியை அதற்கேற்ப பாதிக்கிறது. கேன்வாஸில் கிடைக்கும் SmartDesign இணைப்புக் கருவிகளைப் பயன்படுத்தி, ஒரு குறிப்பிட்ட பஸ் மிரர்டு ஸ்லேவ் BIF (ஸ்லாட்) உடன் பெரிஃபெரலின் ஸ்லேவ் BIFஐ கைமுறையாக இணைப்பதன் மூலம் பெரிஃபெரலுக்கான ஸ்லாட் ஒதுக்கீட்டை மாற்றலாம். படம் 8-1 இல் காட்டப்பட்டுள்ளபடி, மாற்றியமைக்கும் நினைவக வரைபடத்தைப் பயன்படுத்தி நினைவக வரைபடத்தைத் திருத்துவதன் மூலமும் இதைச் செய்யலாம். படம் 8-1 • SmartDesign Canvas இலிருந்து நினைவக வரைபடத்தை மாற்றவும்

படம் 8-1 • SmartDesign Canvas இலிருந்து நினைவக வரைபடத்தை மாற்றவும்

நினைவக வரைபடத்தை மாற்றுவதற்கான உரையாடல் பெட்டி தோன்றும் (படம் 8-2). படம் 8-2 • நினைவக வரைபட உரையாடல் பெட்டியை மாற்றவும்

படம் 8-2 • நினைவக வரைபட உரையாடல் பெட்டியை மாற்றவும்

FIC இடைமுகங்களுக்கான நினைவகப் பகுதிகளை கட்டமைத்தல் (MSS Master View)

MSS நினைவக வரைபடத்தில் ஆறு 256 MB பகுதிகள் FIC பகுதிகள் 0 முதல் 5 வரை வரையறுக்கப்பட்டுள்ளன. இந்தப் பகுதிகள் ஒவ்வொன்றும் FIC_0 அல்லது FIC_1 ஸ்லேவ் இடைமுகங்களுக்கு பரஸ்பர பிரத்தியேக பாணியில் ஒதுக்கப்படலாம். FPGA Fabric Address Regions (MSS Master) பகுதியில் உள்ள ஒவ்வொரு பகுதிக்கும் அடுத்துள்ள ரேடியோ பட்டனைப் பயன்படுத்தி எந்த FIC (0 அல்லது 1) ஸ்லேவ் இன்டர்ஃபேஸுக்கு அந்த பகுதிகளை ஒதுக்குகிறீர்கள் என்பதை நீங்கள் தேர்ந்தெடுக்கலாம். View) குழு பெட்டி (படம் 8-3).  படம் 8-3 • FPGA ஃபேப்ரிக் முகவரி பகுதிகள் (MSS மாஸ்டர் View)

படம் 8-3 • FPGA ஃபேப்ரிக் முகவரி பகுதிகள் (MSS மாஸ்டர் View)

நினைவக வரைபடம் கணக்கீடு பொது சூத்திரம்

FIC துணி இடைமுகங்களுக்கான சாத்தியமான அடிப்படை முகவரிகள் 0x30000000, 0x50000000, 0x70000000, 0x80000000, 0x90000000 மற்றும் 0xF0000000 ஆகும். ஒவ்வொரு FIC நிகழ்வையும் இந்த முகவரிகளுக்கு வரைபடமாக்குவது எப்படி என்பது பற்றிய விவரங்களுக்கு பக்கம் 17 இல் உள்ள "FIC துணை அமைப்புகளை உள்ளமைத்தல்" என்பதைப் பார்க்கவும்.

AHBLiteக்கு, ஸ்லாட்டின் அளவு 16 MB (0x01000000) அல்லது 256 MB (0x10000000) ஆக இருக்கலாம்.

ஒரு ஸ்லாட்டுக்கு 16 MB ஐப் பயன்படுத்தும் போது, 0 முதல் 16 வரையிலான அனைத்து ஸ்லாட்டுகளையும் பயன்படுத்தலாம்; கிளையன்ட் பெரிஃபெரலின் முகவரியை FIC நினைவகப் பகுதியின் அடிப்படை முகவரி + (ஸ்லாட் எண் * 0x01000000) என கணக்கிடலாம். இந்த கட்டமைப்பில், AHBLite கோர் முகவரி பிட்களை டிகோட் செய்யாததால், எல்லா பகுதிகளும் உண்மையில் ஒருவருக்கொருவர் மாற்றுப்பெயர்களாகும் [31:28]; ஸ்லாட்டுகள் முகவரி பிட்களைப் பயன்படுத்தி டிகோட் செய்யப்படுகின்றன [27:24].

ஒரு ஸ்லாட்டுக்கு 256 MB ஐப் பயன்படுத்தும் போது, 3, 5, 7, 8, 9 மற்றும் F ஸ்லாட்டுகளை மட்டுமே பயன்படுத்த முடியும்; கிளையன்ட் பெரிஃபெரலின் முகவரியை FIC நினைவகப் பகுதியின் அடிப்படை முகவரி + (ஸ்லாட் எண் * 0x10000000) என கணக்கிடலாம். இந்த கட்டமைப்பில், AHBLite கோர் முகவரி பிட்களைப் பயன்படுத்தி ஸ்லாட்களை டிகோட் செய்வதால், எல்லாப் பகுதிகளும் வெவ்வேறு ஸ்லாட்டுகளை தனித்தனியாகக் குறிப்பிடுகின்றன [31:28]. இந்த கட்டமைப்பில், நினைவக வரைபட சமன்பாட்டை எளிதாக்க, அடிப்படை முகவரி 0x00000000 ஆகும், அதற்கு பதிலாக மேலே வரையறுக்கப்பட்ட ஆறு நிலையான முகவரிகளில் ஒன்று.

Example 1 (16 MB ஸ்லாட் உள்ளமைவு):

நினைவகப் பகுதி 0x50000000 ஐப் பயன்படுத்தி, புற ஸ்லாட் எண் 7 இல் இருந்தால், அதன் முகவரி: 0x50000000 + (0x7 * 0x01000000) = 0x57000000

Example 2 (256 MB ஸ்லாட் உள்ளமைவு):

நினைவகப் பகுதி 0x50000000 ஐப் பயன்படுத்தி, புற ஸ்லாட் எண் 15 இல் இருந்தால், அதன் முகவரி: 0x00000000 + (0xF * 0x10000000) = 0xF0000000

Viewஇறுதி நினைவக வரைபடத்தில்

இந்த நேரத்தில், SmartFusion2 MSS ஐப் பயன்படுத்தும் கணினிகளுக்கான சரியான நினைவக வரைபடத்தை Libero SoC உருவாக்கவில்லை.

தயாரிப்பு ஆதரவு

மைக்ரோசெமி SoC தயாரிப்புகள் குழு அதன் தயாரிப்புகளை வாடிக்கையாளர் சேவை, வாடிக்கையாளர் தொழில்நுட்ப ஆதரவு மையம் உள்ளிட்ட பல்வேறு ஆதரவு சேவைகளுடன் ஆதரிக்கிறது. webதளம், மின்னணு அஞ்சல் மற்றும் உலகளாவிய விற்பனை அலுவலகங்கள். இந்த பின்னிணைப்பில் மைக்ரோசெமி SoC தயாரிப்புகள் குழுவைத் தொடர்புகொள்வது மற்றும் இந்த ஆதரவு சேவைகளைப் பயன்படுத்துவது பற்றிய தகவல்கள் உள்ளன.

வாடிக்கையாளர் சேவை

தயாரிப்பு விலை, தயாரிப்பு மேம்படுத்தல்கள், புதுப்பித்தல் தகவல், ஆர்டர் நிலை மற்றும் அங்கீகாரம் போன்ற தொழில்நுட்பமற்ற தயாரிப்பு ஆதரவுக்கு வாடிக்கையாளர் சேவையைத் தொடர்புகொள்ளவும்.

வட அமெரிக்காவிலிருந்து, அழைக்கவும் 800.262.1060

உலகின் பிற பகுதிகளிலிருந்து, அழைக்கவும் 650.318.4460

தொலைநகல், உலகில் எங்கிருந்தும், 408.643.6913

வாடிக்கையாளர் தொழில்நுட்ப ஆதரவு மையம்

மைக்ரோசெமி SoC தயாரிப்புகள் குழுவானது அதன் வாடிக்கையாளர் தொழில்நுட்ப ஆதரவு மையத்தில் மிகவும் திறமையான பொறியாளர்களைக் கொண்டுள்ளது. வாடிக்கையாளர் தொழில்நுட்ப ஆதரவு மையம் பயன்பாட்டுக் குறிப்புகள், பொதுவான வடிவமைப்பு சுழற்சி கேள்விகளுக்கான பதில்கள், அறியப்பட்ட சிக்கல்களின் ஆவணங்கள் மற்றும் பல்வேறு FAQகளை உருவாக்குவதற்கு அதிக நேரத்தைச் செலவிடுகிறது. எனவே, நீங்கள் எங்களைத் தொடர்புகொள்வதற்கு முன், எங்கள் ஆன்லைன் ஆதாரங்களைப் பார்வையிடவும். உங்கள் கேள்விகளுக்கு நாங்கள் ஏற்கனவே பதிலளித்திருக்க வாய்ப்புள்ளது.

தொழில்நுட்ப ஆதரவு

வாடிக்கையாளர் ஆதரவைப் பார்வையிடவும் webதளம் (www.microsemi.com/soc/support/search/default.aspx) மேலும் தகவல் மற்றும் ஆதரவிற்கு. தேடக்கூடியவற்றில் பல பதில்கள் கிடைக்கும் web ஆதாரத்தில் வரைபடங்கள், விளக்கப்படங்கள் மற்றும் பிற ஆதாரங்களுக்கான இணைப்புகள் ஆகியவை அடங்கும் webதளம்.

Webதளம்

நீங்கள் SoC முகப்புப் பக்கத்தில் பல்வேறு தொழில்நுட்ப மற்றும் தொழில்நுட்பம் அல்லாத தகவல்களை உலாவலாம் www.microsemi.com/soc.

வாடிக்கையாளர் தொழில்நுட்ப ஆதரவு மையத்தைத் தொடர்புகொள்ளவும்

மிகவும் திறமையான பொறியாளர்கள் தொழில்நுட்ப ஆதரவு மையத்தில் பணியாற்றுகின்றனர். தொழில்நுட்ப ஆதரவு மையத்தை மின்னஞ்சல் மூலமாகவோ அல்லது மைக்ரோசெமி SoC தயாரிப்புகள் குழு மூலமாகவோ தொடர்பு கொள்ளலாம் webதளம்.

மின்னஞ்சல்

உங்களின் தொழில்நுட்பக் கேள்விகளை எங்கள் மின்னஞ்சல் முகவரிக்கு நீங்கள் தொடர்பு கொள்ளலாம் மற்றும் மின்னஞ்சல், தொலைநகல் அல்லது தொலைபேசி மூலம் பதில்களைப் பெறலாம். மேலும், உங்களுக்கு வடிவமைப்பு சிக்கல்கள் இருந்தால், உங்கள் வடிவமைப்பை மின்னஞ்சல் செய்யலாம் fileஉதவி பெற கள். மின்னஞ்சல் கணக்கை நாள் முழுவதும் தொடர்ந்து கண்காணிக்கிறோம். உங்கள் கோரிக்கையை எங்களுக்கு அனுப்பும்போது, உங்கள் கோரிக்கையை திறம்படச் செயல்படுத்த உங்கள் முழுப்பெயர், நிறுவனத்தின் பெயர் மற்றும் உங்கள் தொடர்புத் தகவலைச் சேர்க்க மறக்காதீர்கள்.

தொழில்நுட்ப ஆதரவு மின்னஞ்சல் முகவரி soc_tech@microsemi.com.

எனது வழக்குகள்

மைக்ரோசெமி SoC ப்ராடக்ட்ஸ் குரூப் வாடிக்கையாளர்கள் ஆன்லைனில் சென்று தொழில்நுட்ப வழக்குகளை சமர்ப்பிக்கலாம் மற்றும் கண்காணிக்கலாம் எனது வழக்குகள்.

அமெரிக்காவிற்கு வெளியே

அமெரிக்க நேர மண்டலங்களுக்கு வெளியே உதவி தேவைப்படும் வாடிக்கையாளர்கள் மின்னஞ்சல் வழியாக தொழில்நுட்ப ஆதரவைத் தொடர்பு கொள்ளலாம் (soc_tech@microsemi.com) அல்லது உள்ளூர் விற்பனை அலுவலகத்தை தொடர்பு கொள்ளவும். விற்பனை அலுவலகப் பட்டியல்களை இங்கே காணலாம் www.microsemi.com/soc/company/contact/default.aspx.

ITAR தொழில்நுட்ப ஆதரவு

ஆர்ஹெச் மற்றும் ஆர்டி எஃப்பிஜிஏக்களுக்கான தொழில்நுட்ப ஆதரவுக்கு, சர்வதேச போக்குவரத்து ஆயுத ஒழுங்குமுறைகளால் (ITAR) கட்டுப்படுத்தப்படுகிறது. soc_tech_itar@microsemi.com. மாற்றாக, எனது வழக்குகளுக்குள், ITAR கீழ்தோன்றும் பட்டியலில் ஆம் என்பதைத் தேர்ந்தெடுக்கவும். ITAR-ஒழுங்குபடுத்தப்பட்ட மைக்ரோசெமி FPGAகளின் முழுமையான பட்டியலுக்கு, ITAR ஐப் பார்வையிடவும் web பக்கம்.

மைக்ரோசெமி கார்ப்பரேஷன் (NASDAQ: MSCC) செமிகண்டக்டரின் விரிவான போர்ட்ஃபோலியோவை வழங்குகிறது இதற்கான தீர்வுகள்: விண்வெளி, பாதுகாப்பு மற்றும் பாதுகாப்பு; நிறுவனம் மற்றும் தகவல் தொடர்பு; மற்றும் தொழில்துறை மற்றும் மாற்று ஆற்றல் சந்தைகள். தயாரிப்புகளில் உயர் செயல்திறன், அதிக நம்பகத்தன்மை கொண்ட அனலாக் மற்றும் RF சாதனங்கள், கலப்பு சமிக்ஞை மற்றும் RF ஒருங்கிணைந்த சுற்றுகள், தனிப்பயனாக்கக்கூடிய SoCகள், FPGAகள் மற்றும் முழுமையான துணை அமைப்புகள் ஆகியவை அடங்கும். மைக்ரோசெமியின் தலைமையகம் அலிசோ விஜோ, கலிஃபோர்னியாவில் உள்ளது. மேலும் அறிக www.microsemi.com.

© 2014 மைக்ரோசெமி கார்ப்பரேஷன். அனைத்து உரிமைகளும் பாதுகாக்கப்பட்டவை. மைக்ரோசெமி மற்றும் மைக்ரோசெமி லோகோ ஆகியவை மைக்ரோசெமி கார்ப்பரேஷனின் வர்த்தக முத்திரைகள். மற்ற அனைத்து வர்த்தக முத்திரைகள் மற்றும் சேவை முத்திரைகள் அந்தந்த உரிமையாளர்களின் சொத்து.

5-02-00370-1/08.14

மைக்ரோசெமி நிறுவன தலைமையகம்

மைக்ரோசெமி நிறுவன தலைமையகம்

ஒன் எண்டர்பிரைஸ், அலிசோ விஜோ CA 92656 USA

அமெரிக்காவிற்குள்: +1 949-380-6100

விற்பனை: +1 949-380-6136

தொலைநகல்: +1 949-215-4996

ஆவணங்கள் / ஆதாரங்கள்

|

மைக்ரோசெமி ஸ்மார்ட்ஃப்யூஷன்2 எம்எஸ்எஸ் வடிவமைப்பை உருவாக்குகிறது [pdf] பயனர் வழிகாட்டி SmartFusion2 MSS வடிவமைப்பை உருவாக்குகிறது |