SmartFusion2 MSS

SmartFusion2 MSS

የ MSS የጨርቅ በይነገጽን በመጠቀም ንድፍ መፍጠር

የተጠቃሚ መመሪያ

መግቢያ

የ SmartFusion2 ማይክሮ መቆጣጠሪያ ንዑስ ስርዓት (ኤምኤስኤስ) አራት የተለያዩ የጨርቅ በይነገጽ መቆጣጠሪያዎችን (FIC) ያቀርባል፡-

- DDR_FIC

- SMC_FIC

- FIC_0 እና FIC_1፣ እንደ መሳሪያዎ ይወሰናል

እነዚህ የበይነገጽ ብሎኮች ኤምኤስኤስ በFPGA ጨርቅ ውስጥ ከተተገበረ አመክንዮ ጋር እንዲገናኝ ያስችለዋል።

በተቃራኒው።

የ DDR_FIC ጥቅም ላይ የሚውለው የኤምኤስኤስ DDR ብሎክን (MDDR)ን እንደ ውጫዊው DDR ሲያዋቅሩት ነው።

ማህደረ ትውስታን ከ FPGA የጨርቅ ማስተር በ AXI በይነገጽ ወይም በ 2 AHBlite AMBA መገናኛዎች በኩል ማግኘት ይቻላል ።

SMC_FIC ጥቅም ላይ የሚውለው MSS DDR Blockን በነጠላ ቀን ተመን (ኤስዲአር) ሁነታ ሲያዋቅሩት ነው። በዚህ ውቅር ውስጥ፣ ኤምኤስኤስ ውጫዊ ነጠላ ዳታ ተመን DRAM ወይም ያልተመሳሰሉ ትውስታዎችን በFPGA ጨርቅ ውስጥ በቅጽበት በተሰራ ለስላሳ ማህደረ ትውስታ መቆጣጠሪያ በኩል እንደ CoreSDR_AXI ይደርሳል። SMC_FIC የ AXI ወይም AHBlite ባሪያ AMBA በይነገጽ ነው። የ DDR_FIC እና SMC_FIC በይነገጾች እርስ በርስ የሚጣረሱ ናቸው; በአንድ ጊዜ የሚሠራው አንድ ብቻ ነው።

የFIC በይነገጽ MSS AMBA አውቶብስን ወደ FPGA ጨርቅ ለማራዘም ያስችሎታል። በተመረጠው መሣሪያ ላይ በመመስረት በአንድ MSS እስከ ሁለት የFIC አጋጣሚዎች አሉ። የመጀመሪያው ምሳሌ FIC_0 (በእያንዳንዱ መሳሪያ ላይ ይገኛል) እና ሁለተኛው FIC_1 ይባላል (በትንንሽ መሳሪያዎች ላይ ላይገኝ ይችላል)። እንደ የንድፍ ፍላጎቶችዎ FIC ን እንደ APB3 ወይም AHBlite AMBA በይነገጽ ማዋቀር ይችላሉ። በእያንዳንዱ ሁነታ, ዋና እና የባሪያ አውቶቡስ በይነገጽ ይገኛል. ይኸውም በጨርቁ ውስጥ ያለ ጌታ በኤምኤስኤስ ውስጥ ካለ ባሪያ እና በኤምኤስኤስ ውስጥ ያለ ጌታ በጨርቅ ውስጥ ካለው ባሪያ ጋር መገናኘት ይችላል።

እያንዳንዱ የጨርቅ በይነገጽ ንዑስ ስርዓት እንደ MSS ዋና ሰዓት M3_CLK ጥምርታ በተለየ የሰዓት ድግግሞሽ ላይ ሊሠራ ይችላል።

የSmartFusion2 አርክቴክቸር በFabric Interfaces እና በFPGA ጨርቅ መካከል ጎራዎችን ከሰዓት ከማድረግ ጋር የተያያዙ ህጎችን ያወጣል። ይህ ሰነድ እንደነዚህ ያሉትን ስርዓቶች እንዴት በትክክል መገንባት እንደሚቻል መመሪያ ይሰጣል.

ከፍተኛ ደረጃ View

ምስል 1 እና ምስል 2 ኤምኤስኤስ ከ FPGA ጨርቅ ጋር በተለያዩ የጨርቃጨርቅ በይነገጽ መቆጣጠሪያዎች (FIC) እንዴት እንደሚገናኝ ያሳያሉ። ምስል 1 DDR_FIC ጥቅም ላይ በሚውልበት ጊዜ አጠቃላይ የማገጃ ዲያግራም ያሳያል (ውጫዊ የ DDR ማህደረ ትውስታ) እና ስእል 2 SMC_FIC ጥቅም ላይ ሲውል የማገጃ ንድፍ ያሳያል (ውጫዊ SDR ማህደረ ትውስታ)።

ስዕሎቹ ኤምኤስኤስን ከ FPGA ጨርቅ ጋር ለማገናኘት አስፈላጊ የሆኑትን የ MSS ንዑስ ብሎኮች ያሳያሉ። የFIC ንዑስ እገዳ በማመልከቻዎ ውስጥ ጥቅም ላይ ሊውል ወይም ላይጠቀም ይችላል። እንዲሁም በንድፍዎ ውስጥ የ DDR_FIC ወይም SMC_FIC በይነገጾችን እየተጠቀሙ ላይሆኑ ይችላሉ። ሆኖም ይህ በንድፍ ውስጥ ጥቅም ላይ የዋለው አንድ ወይም ከዚያ በላይ የ FIC ብሎክ ንድፍ እንዴት እንደሚፈጠር አጠቃላይ መስፈርቶችን አይለውጥም ።

ምስል 1 • ኤምኤስኤስ ወደ FPGA የጨርቅ ማገጃ ንድፍ - DDR_FIC ሁነታ

ምስል 1 • ኤምኤስኤስ ወደ FPGA የጨርቅ ማገጃ ንድፍ - DDR_FIC ሁነታ  ምስል 2 • ኤምኤስኤስ ወደ FPGA የጨርቅ እገዳ ንድፍ - SMC_FIC ሁነታ

ምስል 2 • ኤምኤስኤስ ወደ FPGA የጨርቅ እገዳ ንድፍ - SMC_FIC ሁነታ

ኤምኤስኤስ የሚከተሉትን ያካትታል:

- AHB_Bus ማትሪክስ; በ MSS ውስጥ ያሉ ሁሉም ግብይቶች በዚህ ብሎክ ያልፋሉ።

- DDR መቆጣጠሪያ - ከ DDR_FIC ጋር በይነገጾች.

- DDR_FIC (SMC_FIC) ንዑስ-ብሎክ (የ FPGA ጨርቁን ወደ DDR መንገድ በ MSS_MDDR አዋቅር ውስጥ ካነቁ ጥቅም ላይ ይውላል)።

- FIC_0 ንዑስ እገዳ።

- FIC_1 ንዑስ እገዳ (በትልልቅ መሳሪያዎች ብቻ)።

- FIC_2 ንዑስ-ብሎክ (ለ APB የ SERDES እና የውጭ DDRs ማስጀመሪያ)።

- የFIC ሰዓቶችን ከኤምኤስኤስ ዋና ሰዓት (M3_CLK) አንፃር ለማዋቀር የ MSS_CCC ንዑስ ብሎክ ያስፈልጋል።

- MSS_RESET ንዑስ-ብሎክ የኤምኤስኤስ የውስጥ ዳግም ማስጀመሪያዎችን እንዲሁም የFPGA ጨርቁን የሚነዳ የ MSS_RESET_N_M2F ምልክት።

የ FPGA ጨርቅ የሚከተሉትን ያጠቃልላል

- ሶስት የFIC ንዑስ ስርዓቶች (DDR_FIC፣ FIC_0 እና FIC_1)።

- ጨርቅ CCC - FAB_CCC - የ FPGA ጨርቃጨርቅ FIC ንዑስ ስርዓትን እንዲሁም የMCCC_CLK_BASE ወደብ በኤምኤስኤስ ብሎክ ላይ የሚነዱትን ሰዓቶች ለማመንጨት ያስፈልጋል።

- FAB_CCC የማመሳከሪያ ሰዓት ምልክት - በቺፕ ኦስሲሊተሮች ውስጥ አንዱ ሊሆን ይችላል, ውጫዊ ክሪስታል oscillator, ከውስጥ ወደ ጨርቁ ወይም ከቺፑ ውጭ የተፈጠረ ሰዓት.

የብሎክ ሥዕላዊ መግለጫው የሰዓት ኔትወርክን በቀይ እና ዳግም ማስጀመሪያውን በሰማያዊ ሰማያዊ ያሳያል።

ይህ ሰነድ ስለ እያንዳንዳቸው ብሎኮች ያብራራል እና ሰዓቶቹን እና ዳግም ማስጀመሪያዎችን እንዴት ማገናኘት እንደሚቻል ይገልጻል።

የኤምኤስኤስ ማዋቀሪያ

ይህ ሰነድ ኤምኤስኤስ በFIC ንዑስ ብሎኮች በኩል ወደ FPGA ጨርቅ የሚገናኝበት እንደ ንድፍ የመፍጠር አካል ሆነው መዋቀር ያለባቸውን የተወሰኑ የኤምኤስኤስ ንዑስ ብሎኮችን ይመለከታል። እነዚያ ብሎኮች በስእል 1-1 ላይ በቀይ ደመቅተዋል።

ምስል 1-1 • የኤምኤስኤስ ማዋቀር

ምስል 1-1 • የኤምኤስኤስ ማዋቀር

SmartDesign እና MSS Configurator Actions

በዚህ ሰነድ ውስጥ የተጠቀሱ በርካታ የተለመዱ ድርጊቶች አሉ; በሚከተለው ዝርዝር ውስጥ ተጠቃለዋል. SmartDesign እና MSS የምታውቁት ከሆነ ወደሚቀጥለው ክፍል መዝለል ይችላሉ።

አንኳርን ማነሳሳት - ከLibo SoC IP ካታሎግ አንድ ኮር የመምረጥ፣ ያንን ኮር ወደ SmartDesign Canvas የመጎተት እና የመጣል ተግባር።

ኮርን በማዋቀር ላይ - በሸራው ላይ ለዚያ አንኳር ምሳሌ አወቃቀሩን የመክፈት፣ የተለየ ውቅር በመምረጥ እና በማዋቀሪያው የንግግር ሳጥን ውስጥ እሺን ጠቅ በማድረግ የመፈጸም ተግባር። በዚያ ድርጊት ምክንያት፣ ከአሁኑ ውቅር ጋር የሚዛመዱ ወደቦች ብቻ የሚታዩ እና ለአገልግሎት ዝግጁ ናቸው።

አንድ አካል ማቋቋም- በLibo SoC Design Hierarchy ውስጥ አንድ አካል የመምረጥ፣ ያንን አካል ወደ SmartDesign ሸራ የመጎተት እና የመጣል ተግባር።

ብጁ የ AMBA ታዛዥ አካልን ማፋጠን - በLibo SoC ንድፍ ተዋረድ ውስጥ HDL+ አካልን የመምረጥ ተግባር፣ ያንን አካል ወደ SmartDesign Canvas በመጎተት እና በመጣል።

የኤችዲኤል+ ባህሪን በመጠቀም AMBA የሚያሟሉ የአውቶቡስ በይነገጽ (BIFs) ወደ መደበኛ የኤችዲኤል ሞጁል እንዲያክሉ ያስችልዎታል።

አንድ አካል ማዋቀር- በSmartDesign Canvas ላይ ወይም ከንድፍ ተዋረድ በቅጽበት ለተሰራ አካል አወቃቀሩን የመክፈት ተግባር፣ የተለየ ውቅር በመምረጥ እና በማዋቀሪያው የንግግር ሳጥን ውስጥ እሺን ጠቅ በማድረግ ተግባራዊ ይሆናል። በዚያ ድርጊት ምክንያት፣ በLibo SoC ፕሮጀክት ውስጥ በዚያ አካል ላይ ያሉ ሁሉም አጋጣሚዎች ተጎድተዋል እናም መዘመን አለባቸው። አንድ ምሳሌ ከቅርብ ጊዜው አካል ጋር ሲዘምን ከአሁኑ ውቅር ጋር የተገናኙ ወደቦች ብቻ ናቸው የሚታዩት እና ለአገልግሎት ይገኛሉ።

የኤምኤስኤስ ንዑስ እገዳን ማንቃት - አንዳንድ የኤምኤስኤስ ንዑስ ብሎኮች ሊነቁ ወይም ሊሰናከሉ ይችላሉ፣ ይህም አሁን ባለው መተግበሪያ ውስጥ ጥቅም ላይ እንደዋሉ ያሳያል። ሁሉም ጥቅም ላይ ያልዋሉ ንዑስ ብሎኮች መሰናከል አለባቸው።

የ MSS ንዑስ እገዳን በማዋቀር ላይ - ለዚያ ንዑስ ብሎክ ማዋቀሩን በኤምኤስኤስ አወቃቀሩ ውስጥ የመክፈት ተግባር ፣ የተወሰነ ውቅር በመምረጥ እና በማዋቀሪያው ሳጥን ውስጥ እሺን ጠቅ በማድረግ እና በመቀጠል የ MSS ውቅረትን በማስቀመጥ። በነዚህ ድርጊቶች ምክንያት፣ የኤምኤስኤስ አካል አዲስ ውቅር እና አዲስ የወደብ በይነገጽ አለው። የኤምኤስኤስ ምሳሌ ከቅርብ ጊዜው አካል ጋር ሲዘምን አሁን ካለው ውቅር ጋር የተያያዙ የኤምኤስኤስ ወደቦች ብቻ ናቸው የሚታዩት እና ለአገልግሎት ይገኛሉ።

የ FPGA ጨርቅ ንዑስ ስርዓት መፍጠር - በSmartDesign Canvas ውስጥ ኮሮችን እና አካላትን የማፍጠን ፣ የማዋቀር እና በአንድ ላይ እና ከኤምኤስኤስ አካል ጋር የማገናኘት ተግባር ቀድሞውኑ በዚያው SmartDesign ውስጥ ታይቷል።

የ DDR_FIC ንዑስ ስርዓትን በማዋቀር ላይ

የ DDR_FIC ንዑስ ስርዓትን ለማዋቀር/ለመፍጠር የሚከተሉትን ማድረግ አለብዎት:

- የ DDR_FIC በይነገጽን ለማጋለጥ MSS MDRን ያዋቅሩ

- ፈጣን/ማዋቀር/ግንኙነትን ጨምሮ የFPGA ጨርቅ DDR_FIC ንዑስ ስርዓትን ይፍጠሩ ለ፡-

- AXI ወይም AHBlite አውቶቡስ

- AXI ወይም AHBLite አውቶቡስ ዋና(ዎች)

- በማመልከቻዎ እንደአስፈላጊነቱ በአውቶቡስ ላይ ያሉ ሌሎች ጌቶች እና መለዋወጫዎች

- ሰዓቶች እና ዳግም ማስጀመር; በገጽ 23 ላይ ያለውን “የFIC ንዑስ ስርዓት ሰዓቶችን ማዋቀር” እና “የFIC ንዑስ ስርዓት ዳግም ማስጀመርን ማዋቀር” በገጽ 27 ላይ ይመልከቱ።

እነዚህ እርምጃዎች ከዚህ በታች በዝርዝር ተገልጸዋል.

ደረጃ 1 የDDR_FIC አውቶቡስ በይነገጽን ለማጋለጥ የ MSS MDR ንዑስ እገዳን ያዋቅሩ

የDDR_FIC በይነገጽ ይጋለጣል የእርስዎ መተግበሪያ ከFPGA ጨርቅ ውጫዊውን የ DDR ማህደረ ትውስታ መድረስ ሲፈልግ። በዚህ ውቅር ውስጥ፣ የMDR ንኡስ እገዳ የ DDR_FIC በይነገጽን ያጋልጣል፣ እሱም ባሪያ AXI ወይም AHBlite Bus Interface (BIF) (ምስል 3-1)።

ምስል 3-1 • የኤምኤስኤስ DDR ውቅር ከ FPGA ጨርቅ ተደራሽነት ጋር

ምስል 3-1 • የኤምኤስኤስ DDR ውቅር ከ FPGA ጨርቅ ተደራሽነት ጋር

ደረጃ 2፡ የFPGA ጨርቅ DDR_FIC ንዑስ ስርዓት ይፍጠሩ

በመረጡት የFPGA አውቶቡስ ግንኙነት አይነት - AXI፣ Single AHBlite ወይም Two AHBLite - ከመረጡት ምርጫ ጋር የሚስማማ ንዑስ ስርዓት መፍጠር አለብዎት።

DDR_FIC / AXI ንዑስ ስርዓት

- ከካታሎግ መስኮቱ የCoreAXI IP ኮርን ያፋጥኑ እና ያዋቅሩት። ለመተግበሪያዎ ሊጠቀሙባቸው ያቀዱትን ክፍተቶች እና በእያንዳንዱ ስፔል የማህደረ ትውስታ መጠን ከንድፍ መስፈርቶችዎ ጋር የሚስማማውን ያንቁ። ውጫዊ የ DDR ማህደረ ትውስታን እየፈቱ ስለሆነ፣ የቦታ መጠን ምርጫዎ ከ FPGA የጨርቃጨርቅ ማስተር ለማነጋገር ካቀዱት ቦታ ጋር መዛመድ አለበት። (ምስል 3-2).

ምስል 3-2 • CoreAXI ውቅር

ምስል 3-2 • CoreAXI ውቅር - የAMBA AXIን የሚያከብር ዋና ኮር ወይም የ AXI አውቶብስን ለመቆጣጠር የታሰበውን አካል ያፋጥኑ እና ያዋቅሩት። መተግበሪያዎ በCoreAXI አውቶቡስ ላይ ከአንድ በላይ ማስተር የሚፈልግ ከሆነ፣ ሁለተኛውን ማስተርም ያፋጥኑ።

- ንዑስ ስርዓቱን ያገናኙ;

– የCoreAXI መስተዋት-ማስተር አውቶቡስ በይነገጽ (ቢአይኤፍ) ወደብ M0 (M1) ከዋና ዋና ዋና (ዎች) ዋና ቢአይኤፍ ወደብ ጋር ያገናኙ (ምስል 3-3)።

– የኤምኤስኤስ DDR_FIC ባሪያ BIF ወደብ – MDDR_DDR_AXI_SLAVE – ወደ ትክክለኛው የCoreAXI አውቶብስ መስታወት-ባሪያ ማስገቢያ እንደ የማስታወሻ ካርታ መስፈርት ያገናኙ። በዚያ አውቶቡስ ላይ ሌሎች ባሮች ካሉዎት፣ እንደ ማህደረ ትውስታ ካርታዎ እንዲሁ ያገናኙዋቸው።

- ሰዓቶች እና ዳግም ማስጀመር; በገጽ 23 ላይ ያለውን "የFIC ንዑስ ስርዓት ሰዓቶችን ማዋቀር" እና በገጽ 27 ላይ ያለውን "የFIC ንዑስ ስርዓት ዳግም ማስጀመር" የሚለውን ይመልከቱ።

ምስል 3-3 • DDR_FIC AXI ንዑስ ስርዓት

ምስል 3-3 • DDR_FIC AXI ንዑስ ስርዓት

DDR_FIC / ነጠላ-AHBlite ንዑስ ስርዓት

- ከካታሎግ የCoreAHBlite IP ኮርን ያፋጥኑ እና ያዋቅሩት። በስእል 3-4 ላይ እንደሚታየው ለመተግበሪያዎ ለመጠቀም ያቀዷቸውን ቦታዎች ያንቁ። በዚህ የቀድሞample, CoreAHBlite ከማስተር ኤም 4 ስፕ 0ን በመጠቀም አንድ ባለ 0GB DDR RAM ማህደረ ትውስታ ቦታን ለመቅረፍ ተዋቅሯል። ውጫዊ የ DDR ማህደረ ትውስታን እየፈቱ ስለሆነ፣ የቦታ መጠን ምርጫዎ ከFPGA የጨርቃጨርቅ ማስተር ለመቅረፍ ካቀዱት የ DDR ማህደረ ትውስታ ቦታ መጠን ጋር መዛመድ አለበት።

ምስል 3-4 • ኮር AHBLite - የተቀናጀ ክልል ማስተር ውቅር

ምስል 3-4 • ኮር AHBLite - የተቀናጀ ክልል ማስተር ውቅር - ወደ CoreAHBLite አውቶብስ ለመቆጣጠር የታሰበውን AMBA AHBLite compliant master core ወይም አካልን ያፋጥኑ እና ያዋቅሩት። መተግበሪያዎ በCoreAHBLite አውቶብስ ላይ ከአንድ በላይ ማስተር የሚፈልግ ከሆነ ተጨማሪ ማስተሮችንም ያፋጥኑ። በCoreAHBLite አውቶቡስ ላይ እስከ አራት ማስተርስ ይደገፋሉ።

- ንዑስ ስርዓቱን ያገናኙ;

– የCoreAHBlite የሚንጸባረቅበት-ማስተር አውቶቡስ በይነገጽ (ቢአይኤፍ) ወደብ M0 (M1) ከዋና ዋና ዋና (ዎች) ዋና ቢአይኤፍ ወደብ ጋር ያገናኙ።

– የኤምኤስኤስ DDR_FIC ባሪያ BIF ወደብ – MDR_DDR_AHB0_slave – ከትክክለኛው የCoreAHBLite አውቶብስ መስታወታዊ-ባሪያ ማስገቢያ ጋር ያገናኙ (በዚህ የቀድሞ ውስጥ S0ample) እንደ የማስታወሻ ካርታዎ ፍላጎት። በዚያ አውቶቡስ ላይ ሌሎች ባሮች ካሉዎት፣ እንዲሁም እንደ ማህደረ ትውስታ ካርታዎ ያገናኙዋቸው።

- ሰዓቶች እና ዳግም ማስጀመር; በገጽ 23 ላይ ያለውን "የFIC ንዑስ ስርዓት ሰዓቶችን ማዋቀር" እና በገጽ 27 ላይ ያለውን "የFIC ንዑስ ስርዓት ዳግም ማስጀመር" የሚለውን ይመልከቱ።

ምስል 3-5 • DDR_FIC AHBLite ንዑስ ስርዓት

ምስል 3-5 • DDR_FIC AHBLite ንዑስ ስርዓት

DDR_FIC/ሁለት AHBLite ንዑስ ስርዓት

ለMDR ሁለቱን የ AHBlite በይነገጽ አማራጮችን ሲመርጡ፣ ተጨማሪ BIF፣ MDDR_DDR_AHB1_SLAVE BIF፣ ከአዲሱ ባሪያ ጋር ለመገናኘት በኤምኤስኤስ አካል ይገለጣል።

ለዚህ ውቅር፣ ለአንድ የ AHBlite ውቅር ለMDR_DDR_AHB1_SLAVE BIF በይነገጽ በኤምኤስኤስ አካል ላይ የተጋለጠውን ደረጃ ይድገሙ።

ምንም እንኳን SMC_FIC እንደ AXI ወይም AHBlite አውቶቡስ በይነገጽ መጠቀም ቢቻልም፣ ይህ ሰነድ በAXI ሁነታ የተዋቀረውን የSMC_FIC በይነገጽ ከCoreSDR_AXI ኮር ጋር እንዴት መጠቀም እንደሚቻል ብቻ ይገልጻል። ያ ኮር በAXI ላይ የተመሰረተ ኤስዲአር ራም መቆጣጠሪያን ለማገናኘት የሚያገለግል ሲሆን በዚህ አጋጣሚ ኤምኤስኤስ ወደ ውጫዊ ነጠላ ዳታ ተመን (ኤስዲአር) ማህደረ ትውስታ ክፍል። የ AHBLite በይነገጽን እንዴት እንደሚጠቀሙ ከሚከተለው መግለጫ በቀላሉ መረዳት ይችላሉ; ደረጃዎቹ በጣም ተመሳሳይ ናቸው. የ AXI በይነገጽ የበለጠ ቀልጣፋ በይነገጽ ነው እና ተመራጭ አማራጭ ነው።

የSMC_FIC ንዑስ ስርዓትን ለማዋቀር/ለመፍጠር የሚከተሉትን ማድረግ አለብዎት:

- የSMC_FIC በይነገጽን ለማጋለጥ የኤምኤስኤስ ኤምዲአርን ያዋቅሩ

- ፈጣን/ማዋቀር/ግንኙነትን ጨምሮ የFPGA ጨርቅ DDR_FIC ንዑስ ስርዓትን ይፍጠሩ ለ፡

- CoreAXI አውቶቡስ

- CoreSDR_AXI

- በማመልከቻዎ እንደአስፈላጊነቱ በአውቶቡስ ላይ ያሉ ሌሎች ጌቶች እና መለዋወጫዎች

- ሰዓቶች እና ዳግም ማስጀመር; በገጽ 23 ላይ ያለውን “የFIC ንዑስ ስርዓት ሰዓቶችን ማዋቀር” እና “የFIC ንዑስ ስርዓት ዳግም ማስጀመርን ማዋቀር” በገጽ 27 ላይ ይመልከቱ።

እነዚህ እርምጃዎች ከዚህ በታች በዝርዝር ተገልጸዋል.

ደረጃ 1፡ የSMC_FIC አውቶቡስ በይነገጽን ለማጋለጥ የ MSS MDR ንዑስ እገዳን አዋቅር

የSMC_FIC በይነገጽ የሚጋለጠው መተግበሪያዎ በFPGA ጨርቅ በኩል ውጫዊ የኤስዲአር ማህደረ ትውስታን መድረስ ሲፈልግ ነው። በዚህ ውቅር ውስጥ፣ የMDR ንኡስ እገዳ የ SMC_FIC በይነገጽን ያጋልጣል፣ እሱም ዋና AXI ወይም AHBL Bus Interface (BIF) ነው (ምስል 4-1)።

- በኤምኤስኤስ አወቃቀሩ ውስጥ ያለውን የኤምዲአር መቆጣጠሪያን በቀኝ ጠቅ ያድርጉ እና አዋቅርን ይምረጡ።

- የ AXI በይነገጽ ተጠቀም የሚለውን ይምረጡ።

- እሺን ጠቅ ያድርጉ።

ምስል 4-1 • የMDR Soft Memory Controller ውቅር

ምስል 4-1 • የMDR Soft Memory Controller ውቅር

- የኤምኤስኤስ ክፍሉን ከለውጡ ጋር ያዘምኑ።

(የኤምኤስኤስ አካልን በቀኝ ጠቅ ያድርጉ እና ሁኔታዎችን ከቅርብ ጊዜ አካላት ጋር አዘምን የሚለውን ይምረጡ)። MDR_SMC_AXI_MASTER እንደ MSS አካል የአውቶቡስ በይነገጽ ወደብ ተጋልጧል።

ደረጃ 2፡ የFPGA ጨርቅ SMC_FIC ንዑስ ስርዓት ይፍጠሩ

- በስእል 0-0 እንደሚታየው ዋና ማስገቢያ M4 ለባሪያው ማስገቢያ S2 እንዲነቃ CoreAXI ን ያፋጥኑ እና ያዋቅሩ። ውጫዊ ማህደረ ትውስታን በሶፍት ሜሞሪ መቆጣጠሪያ በኩል እያነጋገሩ ያሉት እንደመሆኑ መጠን የቦታ መጠን ምርጫዎ ከ Cortex-M3 ፕሮሰሰር ወይም ማንኛውም ዋና ወደ ውጫዊ ማህደረ ትውስታ በ MSS DDR ድልድይ በኩል ለመፃፍ ካቀዱት የውጭ ማህደረ ትውስታ ቦታ መጠን ጋር መዛመድ አለበት።

ምስል 4-2 • CoreAXI ውቅር - SMC_FIC ሁነታ

ምስል 4-2 • CoreAXI ውቅር - SMC_FIC ሁነታ - ከአይፒ ካታሎግ ላይ፣ CoreSDR_AXIን ከውጫዊ ማህደረ ትውስታ መለኪያዎችዎ ጋር ለማዛመድ ያፋጥኑ እና ያዋቅሩ።

- ንዑስ ስርዓቱን ያገናኙ (ምስል 4-3)

– የኤምኤስኤስ SMC_FIC ዋና BIF ወደብ – MDR_SMC_AXI_MASTER – ከCoreAXI አውቶብስ መስታወት-ማስተር ኤም 0 ጋር ያገናኙ።

– የCoreAXI አንጸባራቂ-ባሪያ አውቶቡስ በይነገጽ (BIF) ወደብ S0ን ከCoreSDR_AXI ኮር ምሳሌ ባሪያ BIF ወደብ ያገናኙ።

- ሰዓቶች እና ዳግም ማስጀመር; በገጽ 23 ላይ ያለውን "የFIC ንዑስ ስርዓት ሰዓቶችን ማዋቀር" እና በገጽ 27 ላይ ያለውን "የFIC ንዑስ ስርዓት ዳግም ማስጀመር" የሚለውን ይመልከቱ።

ምስል 4-3 • SMC_FIC ንዑስ ስርዓት ግንኙነቶች

ምስል 4-3 • SMC_FIC ንዑስ ስርዓት ግንኙነቶች

የFIC ንዑስ ስርዓቶችን በማዋቀር ላይ

የFIC ንዑስ ስርዓትን ለማዋቀር/ለመፍጠር የሚከተሉትን ማድረግ አለብዎት:

- የFIC በይነገጽን ለማጋለጥ MSS FICን ያዋቅሩ

- ፈጣን/ማዋቀር/ግንኙነትን ጨምሮ የFPGA ጨርቅ FIC ንዑስ ስርዓትን ይፍጠሩ ለ፡-

- APB3 ወይም AHBLite አውቶቡስ

- APB3 እና AHBLite የሚያከብር ማስተር እና/ወይም ተያያዥ ውቅር እና በመተግበሪያዎ በሚጠይቀው መሰረት በአውቶቡስ ላይ ግንኙነት

- ሰዓቶች እና ዳግም ማስጀመር; በገጽ 23 ላይ ያለውን “የFIC ንዑስ ስርዓት ሰዓቶችን ማዋቀር” እና “የFIC ንዑስ ስርዓት ዳግም ማስጀመርን ማዋቀር” በገጽ 27 ላይ ይመልከቱ።

እነዚህ እርምጃዎች ከዚህ በታች በዝርዝር ተገልጸዋል.

ደረጃ 1፡ የ MSS FIC ንዑስ እገዳን አዋቅር

- የFIC Configuratorን ጥራ እና በFIC_0 ወይም FIC_1 ላይ በቀኝ ጠቅ በማድረግ የFIC ውቅረትን ለመክፈት።

- ለኤምኤስኤስ ወደ FPGA የጨርቅ በይነገጽ ውቅር ቡድን አዋቅር ውስጥ የሚከተለውን ይምረጡ፡-

- የ AHBlite ወይም APB3 በይነገጽ አይነት

- በይነገጹን እንደ የ FPGA ጨርቅ ዋና ለመጠቀም አስበዋል

በይነገጹን በFPGA ጨርቅ እንደተረዳ ባሪያ ለመጠቀም አስበህ እንደሆነ (ምስል 5-1)

ምስል 5-1 • MSS ወደ FPGA የጨርቅ በይነገጽ አማራጮች

ምስል 5-1 • MSS ወደ FPGA የጨርቅ በይነገጽ አማራጮች - የ AHBlite በይነገጽን እየተጠቀሙ ከሆነ ማለፊያ ሁነታን ለመምረጥ የላቀ AHBLite አማራጮችን መጠቀም ወይም የጨርቁን ዋና ስራ ለመስራት በይነገጽ ከመረጡ ዋና መታወቂያውን ማጋለጥ ይችላሉ (ምስል 5-2)።

ምስል 5-2 • የላቁ AHBLite አማራጮች

ምስል 5-2 • የላቁ AHBLite አማራጮች

ደረጃ 2፡ የFPGA ጨርቅ FIC ንዑስ ስርዓት ይፍጠሩ

ለእያንዳንዱ የFIC በይነገጽ - ጌታ እና ባሪያ፣ እርስዎ ከመረጡት አይነት ጋር የሚዛመድ አውቶቡስ (CoreAHBlite ወይም CoreAPB3) ማፋጠን አለብዎት። እንደ በይነገጽ ሚና (ዋና/ባሪያ) እና ዓይነት (AHBLite/APB3) አውቶቡሱ እንደሚከተለው መዋቀር አለበት።

ማስተር / AHBlite

የCoreAHBLite አውቶብሱን በሚከተለው መልኩ ያፋጥኑ እና ያዋቅሩት፡

- ከእርስዎ መስፈርቶች ጋር የሚዛመድ የማህደረ ትውስታ ቦታ ምርጫን ይምረጡ፡-

- ከ16 ሜባ ያነሰ የአድራሻ ቦታ ከፈለጉ የሁሉንም ተጓዳኝ እቃዎች, በስእል 5-3 ላይ እንደሚታየው አማራጩን ይምረጡ. ይህ ሁነታ እስከ 16 AHBLite ባሪያዎችን ለማገናኘት የሚያገለግሉ 16 16MB ቦታዎችን ይሰጣል።

ምስል 5-3 • Master/AHBlite የማህደረ ትውስታ ቦታ ውቅር - 16 ሜባ በአንድ ማስገቢያ

ምስል 5-3 • Master/AHBlite የማህደረ ትውስታ ቦታ ውቅር - 16 ሜባ በአንድ ማስገቢያ

- ለማንኛውም ተጓዳኝ እቃዎችዎ ከ 16 ሜባ በላይ እና ከ 256 ሜባ ያነሰ የአድራሻ ቦታ ከፈለጉ በስእል 5-4 ላይ እንደሚታየው አማራጩን ይምረጡ. ይህ ሁነታ እስከ 16 AHBLite ባሪያዎችን ለማገናኘት የሚያገለግሉ 256 16 ሜባ ቦታዎችን ይሰጣል።

ምስል 5-4 • Master/AHBlite የማህደረ ትውስታ ቦታ ውቅር - 256 ሜባ በአንድ ማስገቢያ

ምስል 5-4 • Master/AHBlite የማህደረ ትውስታ ቦታ ውቅር - 256 ሜባ በአንድ ማስገቢያ - ለመተግበሪያዎ የሚጠቀሙባቸውን ቦታዎች ያንቁ (ምስል 5-5)። በጣም ጥሩው ልምምድ በገጽ 1 ላይ በስእል 4-2 እንደሚታየው ኤም 15 ወደ ማስገቢያ መዳረሻዎችን መጠቀም ነው።

ማስታወሻ፡- ባለብዙ ማስተር ንዑስ ስርዓት ለመፍጠር ካቀዱ M1 ን ይጠቀሙ እና በጨርቁ ውስጥ የማሳያ ባህሪን የሚፈልግ እና ከ M0 ጋር መገናኘት ያለበት ዋና ጌታ ካለዎት።

- በአንድ ማስገቢያ ምርጫ 16 ሜባ ከመረጡ ፣ የትኞቹ ቦታዎች ጥቅም ላይ እንደሚውሉ ምንም ገደቦች የሉም።

- በአንድ ማስገቢያ ምርጫ 256 ሜባ ከመረጡ ፣ ከ FIC ለምሳሌ የጨርቅ ማህደረ ትውስታ አድራሻ ክልሎች ምርጫ ጋር ተኳሃኝ የሆኑ ክፍተቶች ብቻ ጥቅም ላይ ሊውሉ ይችላሉ። እያንዳንዱ የFIC ማህደረ ትውስታ አድራሻ ክልል መጠኑ 256 ሜባ ነው። ስድስቱ የኤፍአይሲ ማህደረ ትውስታ ክልሎች በሰንጠረዥ 5-1 ውስጥ ተጠቃለዋል.

ሠንጠረዥ 5-1 • የአድራሻ ክልሎች እና ተስማሚ ቦታዎች ለ 256 ሜባ በአንድ ማስገቢያ አማራጭ

የማህደረ ትውስታ አድራሻ ክልል ተኳሃኝ ቦታዎች 30000000-3FFFFFFFF 3 50000000-5FFFFFFFF 5 70000000-7FFFFFFFF 7 80000000-8FFFFFFFF 8 90000000-9FFFFFFFF 9 F0000000-FFFFFFFF 15 (ፋ)  ምስል 5-5 • Master/AHBlite Master Access Configuration

ምስል 5-5 • Master/AHBlite Master Access Configuration - ፈጣን እና አዋቅር AHBLite ታዛዥ ተጓዳኝ ኮሮች እና/ወይም ብጁ AHBLite ታዛዥ ክፍሎችን።

- ንዑስ ስርዓቱን ያገናኙ;

– የCoreAHBlite መስታወት ማስተር አውቶቡስ በይነገጽ (BIF) ወደብ M1ን ከኤምኤስኤስ ማስተር BIF ወደብ - FIC_0/1_AHB_MASTER - በስእል 5-6 እንደሚታየው ያገናኙ።

- እንደ የማስታወሻ ካርታ ፍላጎትዎ የ AHBlite ባሪያዎችን ከትክክለኛዎቹ ቦታዎች ጋር ያገናኙ ።

- ሰዓቶች እና ዳግም ማስጀመር; በገጽ 23 ላይ ያለውን "የFIC ንዑስ ስርዓት ሰዓቶችን ማዋቀር" እና በገጽ 27 ላይ ያለውን "የFIC ንዑስ ስርዓት ዳግም ማስጀመር" የሚለውን ይመልከቱ።

ምስል 5-6 • FIC Master/AHBlite ንዑስ-ስርዓት

ምስል 5-6 • FIC Master/AHBlite ንዑስ-ስርዓት

ማስተር/APB3

የCoreAPB3 አውቶቡሱን በሚከተለው መልኩ ያፋጥኑ እና ያዋቅሩት፡

- በስእል 5-7 እንደሚታየው የአድራሻ ውቅር አማራጮችን ይምረጡ። ይህ ሁነታ እስከ አስራ ስድስት APB16 የሚያከብር ባሪያዎችን ለማገናኘት አስራ ስድስት 3 ሜባ ቦታዎችን ይሰጣል። ተጨማሪ ማህደረ ትውስታ ያላቸው ክፍተቶች ከፈለጉ ትልቅ ማስገቢያ ለመገንባት ብዙ ባሮችን ማጣመር ይችላሉ። ስለዚህ አማራጭ ተጨማሪ ዝርዝሮችን ለማግኘት የCoreAPB3 የተጠቃሚ መመሪያን ይመልከቱ።

ምስል 5-7 • Master/APB3 የአድራሻ ውቅር

ምስል 5-7 • Master/APB3 የአድራሻ ውቅር - በስእል 5-8 ላይ እንደሚታየው ለመተግበሪያዎ የሚጠቀሙባቸውን ቦታዎች ያንቁ።

ምስል 5-8 • ማስተር/APB3 የስላቭ ማስገቢያ ውቅር

ምስል 5-8 • ማስተር/APB3 የስላቭ ማስገቢያ ውቅር - APB3 ታዛዥ ተጓዳኝ ኮሮች እና/ወይም ብጁ APB3 ታዛዥ ክፍሎችን ያፋጥኑ እና ያዋቅሩ።

- ንዑስ ስርዓቱን ያገናኙ;

– የCoreAPB3 መስተዋት-ማስተር አውቶቡስ በይነገጽ (BIF) ወደብ ከኤምኤስኤስ ዋና ቢኤፍኤፍ ወደብ FIC_0/1_APB_MASTER ጋር ያገናኙ - በስእል 5-9 እንደሚታየው።

- እንደ የማስታወሻ ካርታ ፍላጎትዎ የ APB3 ባሪያዎችን ከትክክለኛዎቹ ቦታዎች ጋር ያገናኙ ።

- ሰዓቶች እና ዳግም ማስጀመር; በገጽ 23 ላይ ያለውን "የFIC ንዑስ ስርዓት ሰዓቶችን ማዋቀር" እና በገጽ 27 ላይ ያለውን "የFIC ንዑስ ስርዓት ዳግም ማስጀመር" የሚለውን ይመልከቱ።

ምስል 5-9 • FIC Master/APB3 ንዑስ ስርዓት

ምስል 5-9 • FIC Master/APB3 ንዑስ ስርዓት

ባሪያ/AHBlite

በዚህ ጊዜ አይገኝም።

ባሪያ/APB3

በዚህ ጊዜ አይገኝም።

የFIC ንዑስ ስርዓት ሰዓቶችን በማዋቀር ላይ

ትክክለኛውን የሰዓት አወቃቀር እና ግንኙነት ለመፍጠር የሚከተሉትን ማድረግ አለብዎት:

- የ MSS CCC FIC ሰዓቶችን ያዋቅሩ

- የ FPGA ጨርቅ CCC ኮርን ያፋጥኑ እና ያዋቅሩ

- ለእያንዳንዱ የFIC ንዑስ ስርዓት የሰዓት ኔትወርኮችን ያገናኙ

- የኤምኤስኤስ CLK_BASE ወደብ ከትክክለኛው የFPGA ጨርቅ FIC ንዑስ ስርዓት የሰዓት አውታር ጋር ያገናኙ

የSmartFusion2 አርክቴክቸር ሁሉም የFIC ንዑስ ስርዓቶች በኤምኤስኤስ አመክንዮ እና በ FPGA የጨርቃጨርቅ አመክንዮ መካከል በትክክል መስተጋብር እንዲፈጥሩ መከተል ያለባቸውን በርካታ ህጎች ያስገድዳል። እነዚህ ደንቦች ከዚህ በታች ተገልጸዋል እና በስእል 6-1 ይታያሉ.

- እያንዳንዱ የ FPGA ጨርቅ FIC ንዑስ ስርዓት የሰዓቱ ድግግሞሹ ከተገለፀው ድግግሞሹ ጋር በሚመሳሰል ሰዓት መንዳት አለበት ፣ለዚያ የተለየ ንዑስ ስርዓት ፣ በኤምኤስኤስ ሲሲሲ አዋቅር።

- ሁሉም የ FPGA ጨርቅ FIC ንዑስ-ስርዓት ሰዓቶች በትክክል መገጣጠም አለባቸው; ሰዓቶቹ የተለያዩ ድግግሞሾች ሊሆኑ ይችላሉ፣ ነገር ግን የቀዘቀዙ ሰዓቶች ወደ ላይ የሚወጡት ጫፎች በጣም ፈጣን ከሆኑ የሰዓታት ጫፎች ጋር መመሳሰል አለባቸው።

- ትንሹ ድግግሞሽ ያለው የFPGA ጨርቅ FIC ንዑስ ስርዓት ሰዓት MSS CLK_BASE መንዳት አለበት።

- የጨርቁ ሰአቶች ከጨርቃ ጨርቅ ሲሲሲ (ከ PLL) የተወሰዱ ከሆነ የጨርቁ CCC LOCK ውፅዓት ከ MSS_CCC_CLK_BASE_PLL_LOCK ወደብ ጋር መያያዝ አለበት። የኤምኤስኤስ ሲ ሲሲሲ ጨርቅ አሰላለፍ ሰዓት ሰርቪስ (FACC) CLK_BASE PLL LOCK ሲግናል ከተጠባባቂ ሰዓቱ (በመሣሪያ በሚነሳበት ጊዜ ጥቅም ላይ የሚውለው ሰዓት) ከCLK_BASE ወደሚገኘው ተጠቃሚ የተዋቀረ ሰዓት ከመቀየሩ በፊት CLK_BASE የተረጋጋ መሆኑን ለማረጋገጥ የ CLK_BASE PLL LOCK ምልክትን ይከታተላል።

ምስል 6-1 • ንዑስ-ስርዓት የሰዓት ህጎች

ምስል 6-1 • ንዑስ-ስርዓት የሰዓት ህጎች

ለሁሉም የFIC ንዑስ ስርዓቶችዎ የሰዓት ኔትወርኮችን ለማዋቀር ከዚህ በታች ያሉትን ደረጃዎች ይከተሉ።

ደረጃ 1፡ የኤምኤስኤስ ሲሲሲ ንዑስ እገዳን አዋቅር

ለእያንዳንዱ የFIC ብሎክ (FIC_0፣ FIC_1 እና DDR_FIC/SMC_FIC) በስእል 6-2 እንደሚታየው በኤምኤስኤስ ሰዓት አዋቅር (MSS_CCC) ውስጥ የሰዓት አካፋዮችን ይምረጡ። ምስል 6-2 • MSS CCC FIC የሰዓት ማዋቀር

ምስል 6-2 • MSS CCC FIC የሰዓት ማዋቀር

ማስታወሻ የCLK_BASE መስኩ ሊስተካከል የማይችል መሆኑን የCLK_BASE ፍሪኩዌንሲ፣ በSmartFusion2 አርክቴክቸር የተጫነው፣ የሁሉም የFIC የሰዓት ድግግሞሾች ዝቅተኛው ድግግሞሽ መሆን አለበት እና በራስ ሰር በኤምኤስኤስ ሲሲሲ አዋቅር ይሰላል። ስለ CLK_BASE ውቅር ተጨማሪ ዝርዝሮችን ለማግኘት "ደረጃ 3፡ የFPGA ጨርቅ FIC ንዑስ ስርዓቶች የሰዓት አውታረ መረቦችን ያገናኙ" በገጽ 25 ላይ ይመልከቱ።

ደረጃ 2፡ የFPGA ጨርቅ FIC ሰዓቶችን ያዋቅሩ

የጨርቅ ሲሲሲሲ (ከ PLL) ጋር ያዋቅሩት እና በገጽ 23 ላይ የተገለጹትን የFIC ንዑስ ስርዓት የሰዓት ደንቦችን ለማርካት ያዋቅሩት። በተለምዶ ለእያንዳንዱ የFIC ሰዓቶች አለምአቀፍ ውፅዓት (GLx) ማገናኘት ያስፈልግዎታል፣ ለእያንዳንዱ ውፅዓት ድግግሞሹን ይግለጹ () በኤምኤስኤስ ሲ ሲ ሲሲሲ ውስጥ ከተገለጹት ድግግሞሾች ጋር የሚዛመድ) እና ሁሉም ዓለም አቀፋዊ ውጤቶች ከ PLL ውፅዓት የተገኙ የደረጃ አሰላለፍ ዋስትና እንዲኖራቸው (በስእል 6-3 እንደሚታየው)።

ማስታወሻ፡- ሁለት የ FIC ንዑስ ስርዓቶች ተመሳሳይ ድግግሞሽ ካላቸው ከጨርቁ CCC ሁለት ገለልተኛ ዓለም አቀፍ ውጤቶችን ማመንጨት አያስፈልግዎትም; አንዱ በቂ ነው። ምስል 6-3 • ጨርቅ CCC ከ PLL

ምስል 6-3 • ጨርቅ CCC ከ PLL

ደረጃ 3፡ የFPGA ጨርቅ FIC ንዑስ ስርዓቶች ሰዓትን ያገናኙ አውታረ መረቦች

እያንዳንዱን የጨርቅ CCC አለምአቀፍ ውፅዓት GLx ከተገናኘው የFIC ንዑስ ስርዓት ጋር ያገናኙ።

ደረጃ 4፡ የኤምኤስኤስ CLK_BASE ወደብን ያገናኙ

የጨርቁን ቀርፋፋ CCC አለምአቀፍ ውፅዓት GLxን ከኤምኤስኤስ CLK_BASE ወደብ ያገናኙ።

ደረጃ 5፡ የኤምኤስኤስ MCCC_CLK_BASE_PLL_LOCK ወደብን ያገናኙ

የጨርቁን CCC LOCK ውጤት ከኤምኤስኤስ MCCC_CLK_BASE_PLL_LOCK ወደብ ጋር ያገናኙት።

የጊዜ ትንተና መስፈርቶች

ዲዛይኑ በኤምኤስኤስ ሲ ሲሲሲ እና በ FPGA ጨርቅ CCC Configurators ውስጥ የተገለጹትን የጊዜ መስፈርቶች ማሟላቱን ለማረጋገጥ ከድህረ-አቀማመጥ የማይለዋወጥ የጊዜ ትንተና ያካሂዱ። Static Timeing Analysis የሚያልፈውን ንድፍ ለማግኘት M3_CLKን መቀየር ወይም በኤምኤስኤስ እና በጨርቁ መካከል ያለውን የሰዓት ጥምርታ መጨመር ሊኖርብዎ ይችላል።

የFIC ንዑስ ስርዓት ዳግም ማስጀመርን በማዋቀር ላይ

የFIC ንዑስ ስርዓት ዳግም ማስጀመርን ለማዋቀር፡-

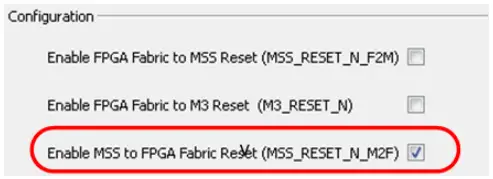

- ከኤምኤስኤስ አወቃቀሪ የ MSS ዳግም አስጀምር ንዑስ እገዳን የ MSS_RESET_N_M2F ወደብ ለማጋለጥ ያዋቅሩት።

ምስል 7-1 • የ MSS ዳግም ማስጀመሪያ ንዑስ እገዳን አዋቅር

ምስል 7-1 • የ MSS ዳግም ማስጀመሪያ ንዑስ እገዳን አዋቅር - የMSS_RESET_N_M2F ወደብ ከሁሉም የFPGA ጨርቅ FIC ንዑስ ስርዓቶች ዳግም ማስጀመሪያ ወደቦች ጋር ያገናኙ።

የስርዓት ማህደረ ትውስታ ካርታ በማዋቀር ላይ

እያንዳንዱ ተጓዳኝ (AMBA AXI፣ AHBlite እና APB3 ባሪያዎች) ከFIC ንዑስ ስርዓት ዋና ነጥብ በአድራሻ ተለይተዋል። view. እኛ ብዙውን ጊዜ የስር ስርአቱ ጌቶች እና ባሪያዎች አጠቃላይ ግንኙነቶችን እንደ የስር ስርዓቱ ትውስታ ካርታ እንጠቅሳለን። የአንድ ንዑስ ስርዓት ማህደረ ትውስታ ካርታ በ SmartDesign ውስጥ ሊስተካከል ይችላል. እርስዎም ይችላሉ view መላውን ስርዓት ሲፈጥሩ የስርዓትዎ የመጨረሻ ማህደረ ትውስታ ካርታ። የማህደረ ትውስታ ካርታው በትውልድ ላይ ለንድፍዎ 'ሥር' የመነጨ የውሂብ ሉህ አካል ነው።

የማህደረ ትውስታ ካርታውን በማዋቀር ላይ (አጠቃላይ ስማርት ዲዛይን ባህሪ)

በSmartDesign ውስጥ፣ ተጓዳኝ አውቶቡስ በአውቶቡስ ላይ ያለው አድራሻ በንዑስ ሲስተም ውስጥ ባለው የዚያ አውቶቡስ መሠረት አድራሻ እና በዚያ አውቶቡስ ላይ ያለው የመግቢያ ቁጥር የቦታው መጠን ይሰጠዋል። ስለዚህ የመግቢያ ቁጥሩን ለቀጣይ ክፍል መለወጥ አድራሻውን ይነካል። በሸራው ውስጥ የሚገኙትን SmartDesign የግንኙነት መሳሪያዎችን በመጠቀም የፔሪፈራል ባሪያ BIFን ከተለየ አውቶብስ መስታወቱ ባርያ BIF (ስሎት) ጋር በማገናኘት ለአንድ አከባቢ የቦታ ምደባን መለወጥ ይቻላል። ይህ ደግሞ በስእል 8-1 እንደሚታየው የማስታወሻ ካርታውን በማስተካከል ሜሞሪ ማፕን በመጠቀም ሊከናወን ይችላል። ምስል 8-1 • የማህደረ ትውስታ ካርታን ከSmartDesign Canvas ቀይር

ምስል 8-1 • የማህደረ ትውስታ ካርታን ከSmartDesign Canvas ቀይር

የማስታወሻ ካርታ ለውጥ የሚለው የንግግር ሳጥን ይታያል (ምስል 8-2)። ምስል 8-2 • የማህደረ ትውስታ ካርታ መገናኛ ሳጥንን ቀይር

ምስል 8-2 • የማህደረ ትውስታ ካርታ መገናኛ ሳጥንን ቀይር

የማህደረ ትውስታ ክልሎችን ለFIC በይነገጾች ማዋቀር (ኤምኤስኤስ ማስተር View)

በኤምኤስኤስ የማስታወሻ ካርታ ውስጥ ስድስት 256 ሜባ ክልሎች FIC ክልሎች ከ 0 እስከ 5 የተገለጹ አሉ። እነዚህ ክልሎች እያንዳንዳቸው ለFIC_0 ወይም FIC_1 የባሪያ በይነገጾች እርስ በርስ በሚስማማ መልኩ ሊመደቡ ይችላሉ። በ FPGA ጨርቅ አድራሻ ክልሎች (ኤምኤስኤስ ማስተር) ውስጥ ከእያንዳንዱ ክልል ቀጥሎ ያለውን የሬዲዮ ቁልፍ በመጠቀም እነዚያን ክልሎች የሚመድቡበት የFIC (0 ወይም 1) የባሪያ በይነገጽ መምረጥ ይችላሉ። View) የቡድን ሳጥን (ምስል 8-3).  ምስል 8-3 • የ FPGA ጨርቅ አድራሻ ክልሎች (MSS Master View)

ምስል 8-3 • የ FPGA ጨርቅ አድራሻ ክልሎች (MSS Master View)

የማህደረ ትውስታ ካርታ ስሌት አጠቃላይ ቀመር

ለ FIC የጨርቅ መገናኛዎች ሊሆኑ የሚችሉ የመሠረት አድራሻዎች 0x30000000, 0x50000000, 0x70000000, 0x80000000, 0x90000000 እና 0xF0000000 ናቸው. እያንዳንዱን የFIC ምሳሌ ወደእነዚህ አድራሻዎች ካርታ እንዴት ማዋቀር እንደሚቻል ለዝርዝር መረጃ በገጽ 17 ላይ ያለውን "የFIC ንዑስ ስርዓቶችን ማዋቀር" የሚለውን ይመልከቱ።

ለ AHBlite፣ የቦታው መጠን 16 ሜባ (0x01000000) ወይም 256 ሜባ (0x10000000) ሊሆን ይችላል።

በአንድ ማስገቢያ 16 ሜባ ሲጠቀሙ ከ 0 እስከ 16 ያሉት ሁሉም ክፍተቶች ጥቅም ላይ ሊውሉ ይችላሉ; የደንበኛ አከባቢ አድራሻ እንደ FIC ማህደረ ትውስታ ክልል መሠረት አድራሻ + (የማስገቢያ ቁጥር * 0x01000000) ሊሰላ ይችላል። በዚህ ውቅር ውስጥ፣ ሁሉም ክልሎች የ AHBLite ኮር የአድራሻ ቢትን ስለማያስተካክል እርስበርስ ተለዋጭ ስሞች ናቸው። መክተቻዎቹ የሚከፈቱት የአድራሻ ቢት በመጠቀም ነው [31፡28]።

በአንድ ማስገቢያ 256 ሜባ ሲጠቀሙ, 3, 5, 7, 8, 9 እና F ቦታዎችን ብቻ መጠቀም ይቻላል; የደንበኛ አከባቢ አድራሻ እንደ FIC ማህደረ ትውስታ ክልል መሠረት አድራሻ + (የማስገቢያ ቁጥር * 0x10000000) ሊሰላ ይችላል። በዚህ ውቅር ውስጥ፣ AHBLite ኮር የአድራሻ ቢት (አድራሻ ቢት) በመጠቀም ክፍተቶችን ሲፈታ ሁሉም ክልሎች በተለየ ሁኔታ የተለያዩ ክፍተቶችን ይያዛሉ [31፡28]። በዚህ ውቅረት፣ የማህደረ ትውስታ ካርታ እኩልታን ለማቃለል፣ ከላይ ከተገለጹት ስድስት ቋሚ አድራሻዎች አንዱ ሳይሆን የመሠረት አድራሻው 0x00000000 ነው።

Example 1 (16 ሜባ ማስገቢያ ውቅር)

የማህደረ ትውስታ ክልልን በመጠቀም 0x50000000 ፣ ተጓዳኝ ክፍሉ በስፖት ቁጥር 7 ከሆነ ፣ አድራሻው 0x50000000 + (0x7 * 0x01000000) = 0x57000000 ነው።

Example 2 (256 ሜባ ማስገቢያ ውቅር)

የማስታወሻ ክልልን 0x50000000 በመጠቀም ፣ ተጓዳኝ ክፍሉ በ 15 ቁጥር ከሆነ ፣ አድራሻው 0x00000000 + (0xF * 0x10000000) = 0xF0000000 ነው።

Viewየመጨረሻው ማህደረ ትውስታ ካርታ

በዚህ ጊዜ ሊቦሮ ሶሲ SmartFusion2 MSS ን ለሚጠቀሙ ስርዓቶች ትክክለኛ የማስታወሻ ካርታ አያመነጭም።

የምርት ድጋፍ

የማይክሮሴሚ ሶሲ ምርቶች ቡድን የደንበኛ አገልግሎትን፣ የደንበኛ ቴክኒካል ድጋፍ ማእከልን ጨምሮ ምርቶቹን በተለያዩ የድጋፍ አገልግሎቶች ይደግፋል። webጣቢያ፣ የኤሌክትሮኒክስ መልእክት እና የአለም አቀፍ የሽያጭ ቢሮዎች። ይህ አባሪ የማይክሮሴሚ ሶሲ ምርቶች ቡድንን ስለማግኘት እና እነዚህን የድጋፍ አገልግሎቶች ስለመጠቀም መረጃ ይዟል።

የደንበኛ አገልግሎት

እንደ የምርት ዋጋ አሰጣጥ፣ የምርት ማሻሻያ፣ የዝማኔ መረጃ፣ የትዕዛዝ ሁኔታ እና ፍቃድ ላሉ ቴክኒካዊ ያልሆኑ የምርት ድጋፍ የደንበኛ አገልግሎትን ያግኙ።

ከሰሜን አሜሪካ, ይደውሉ 800.262.1060

ከተቀረው አለም ይደውሉ 650.318.4460

ፋክስ፣ ከየትኛውም አለም፣ 408.643.6913

የደንበኛ የቴክኒክ ድጋፍ ማዕከል

የማይክሮሴሚ ሶሲ ምርቶች ቡድን የደንበኛ ቴክኒካል ድጋፍ ማእከልን በከፍተኛ ችሎታ ካላቸው መሐንዲሶች ጋር በሰራተኛ ሲሆን እነዚህም የእርስዎን ሃርድዌር፣ ሶፍትዌሮች እና የማይክሮሴሚ ሶሲ ምርቶች የንድፍ ጥያቄዎችን ሊመልሱ ይችላሉ። የደንበኛ ቴክኒካል ድጋፍ ማእከል የማመልከቻ ማስታወሻዎችን፣ ለጋራ የንድፍ ዑደት ጥያቄዎች መልሶችን፣ የታወቁ ጉዳዮችን እና የተለያዩ ተደጋጋሚ ጥያቄዎችን በመፍጠር ብዙ ጊዜ ያሳልፋል። ስለዚህ፣ እኛን ከማነጋገርዎ በፊት፣ እባክዎን የመስመር ላይ ሃብቶቻችንን ይጎብኙ። ለጥያቄዎችህ ቀደም ብለን መልስ ሰጥተናል።

የቴክኒክ ድጋፍ

የደንበኛ ድጋፍን ይጎብኙ webጣቢያ (www.microsemi.com/soc/support/search/default.aspx) ለበለጠ መረጃ እና ድጋፍ። በፍለጋው ላይ ብዙ መልሶች ይገኛሉ web መርጃዎች ንድፎችን, ምሳሌዎችን እና ሌሎች ምንጮችን በ ላይ አገናኞችን ያካትታሉ webጣቢያ.

Webጣቢያ

በ SoC መነሻ ገጽ ላይ የተለያዩ ቴክኒካል እና ቴክኒካዊ ያልሆኑ መረጃዎችን ማሰስ ይችላሉ። www.microsemi.com/soc.

የደንበኛ የቴክኒክ ድጋፍ ማእከልን ማነጋገር

ከፍተኛ ችሎታ ያላቸው መሐንዲሶች የቴክኒክ ድጋፍ ማእከልን ይሠራሉ። የቴክኒክ ድጋፍ ማእከልን በኢሜል ወይም በማይክሮሴሚ ሶሲ ምርቶች ቡድን በኩል ማግኘት ይቻላል webጣቢያ.

ኢሜይል

የቴክኒክ ጥያቄዎችዎን ወደ ኢሜል አድራሻችን መላክ እና መልሶችን በኢሜል፣ በፋክስ ወይም በስልክ ማግኘት ይችላሉ። እንዲሁም የንድፍ ችግሮች ካጋጠሙዎት ንድፍዎን በኢሜል መላክ ይችላሉ files እርዳታ ለመቀበል. ቀኑን ሙሉ የኢሜል መለያውን በቋሚነት እንቆጣጠራለን። ጥያቄዎን ወደ እኛ በሚልኩበት ጊዜ እባክዎን ሙሉ ስምዎን ፣ የኩባንያዎን ስም እና የእውቂያ መረጃዎን ለጥያቄዎ ቀልጣፋ ሂደት ማካተትዎን ያረጋግጡ።

የቴክኒክ ድጋፍ ኢሜይል አድራሻ ነው። soc_tech@microsemi.com.

የእኔ ጉዳዮች

የማይክሮሴሚ ሶሲ ምርቶች ቡድን ደንበኞች ወደ በመሄድ ቴክኒካል ጉዳዮችን በመስመር ላይ ማስገባት እና መከታተል ይችላሉ። የእኔ ጉዳዮች።

ከአሜሪካ ውጪ

ከዩኤስ የሰዓት ሰቆች ውጭ እርዳታ የሚፈልጉ ደንበኞች የቴክኒክ ድጋፍን በኢሜል ማግኘት ይችላሉ (soc_tech@microsemi.com) ወይም የአካባቢውን የሽያጭ ቢሮ ያነጋግሩ። የሽያጭ ቢሮ ዝርዝሮች በ ላይ ይገኛሉ www.microsemi.com/soc/company/contact/default.aspx.

ITAR የቴክኒክ ድጋፍ

በአለምአቀፍ የትራፊክ በጦር መሳሪያ ደንብ (ITAR) የሚተዳደሩ በ RH እና RT FPGAs ላይ ቴክኒካዊ ድጋፍ ለማግኘት በ በኩል ያግኙን soc_tech_itar@microsemi.com. በአማራጭ፣ በእኔ ጉዳዮች ውስጥ፣ በ ITAR ተቆልቋይ ዝርዝር ውስጥ አዎ የሚለውን ይምረጡ። በITAR ቁጥጥር የሚደረግባቸው የማይክሮሴሚ FPGAዎች ዝርዝር ለማግኘት፣ ITARን ይጎብኙ web ገጽ.

የማይክሮሴሚ ኮርፖሬሽን (NASDAQ፡ MSCC) አጠቃላይ የሴሚኮንዳክተር ፖርትፎሊዮ ያቀርባል መፍትሄዎች ለ: ኤሮስፔስ, መከላከያ እና ደህንነት; ኢንተርፕራይዝ እና ግንኙነቶች; እና የኢንዱስትሪ እና አማራጭ የኃይል ገበያዎች. ምርቶች ከፍተኛ አፈጻጸም ያላቸው፣ ከፍተኛ ተዓማኒነት ያላቸው የአናሎግ እና RF መሳሪያዎች፣ የተቀላቀሉ ሲግናል እና RF የተቀናጁ ሰርኮች፣ ሊበጁ የሚችሉ ሶሲዎች፣ FPGAs እና ሙሉ ንዑስ ስርዓቶችን ያካትታሉ። የማይክሮሴሚ ዋና መሥሪያ ቤት በአሊሶ ቪጆ ፣ ካሊፎርኒያ ነው። የበለጠ ይረዱ www.microsemi.com.

© 2014 Microsemi ኮርፖሬሽን. መብቱ በህግ የተጠበቀ ነው. የማይክሮሴሚ እና የማይክሮሴሚ አርማ የማይክሮሴሚ ኮርፖሬሽን የንግድ ምልክቶች ናቸው። ሁሉም ሌሎች የንግድ ምልክቶች እና የአገልግሎት ምልክቶች የየባለቤቶቻቸው ንብረት ናቸው።

5-02-00370-1/08.14

የማይክሮሴሚ ኮርፖሬት ዋና መሥሪያ ቤት

የማይክሮሴሚ ኮርፖሬት ዋና መሥሪያ ቤት

አንድ ድርጅት፣ አሊሶ ቪጆ CA 92656 አሜሪካ

በአሜሪካ ውስጥ፡ +1 949-380-6100

ሽያጮች፡ +1 949-380-6136

ፋክስ፡ +1 949-215-4996

ሰነዶች / መርጃዎች

|

Microsemi SmartFusion2 MSS ንድፍ መፍጠር [pdf] የተጠቃሚ መመሪያ SmartFusion2 MSS ንድፍ መፍጠር |