SmartFusion2 MSS

SmartFusion2 MSS

Стварэнне дызайну з дапамогай інтэрфейсаў MSS Fabric

Кіраўніцтва карыстальніка

Уводзіны

Падсістэма мікракантролера SmartFusion2 (MSS) прапануе чатыры розныя кантролеры інтэрфейсу Fabric (FIC):

- DDR_FIC

- SMC_FIC

- FIC_0 і FIC_1, у залежнасці ад вашай прылады

Гэтыя інтэрфейсныя блокі дазваляюць MSS ўзаемадзейнічаць з логікай, рэалізаванай у структуры FPGA і віцэ

наадварот.

DDR_FIC выкарыстоўваецца, калі вы наладжваеце блок MSS DDR (MDDR), каб знешні DDR

доступ да памяці можна атрымаць з майстра FPGA праз інтэрфейс AXI або 2 інтэрфейсы AHBLite AMBA.

SMC_FIC выкарыстоўваецца, калі вы наладжваеце блок MSS DDR у рэжыме Single Date Rate (SDR). У гэтай канфігурацыі MSS атрымлівае доступ да знешняй памяці DRAM з адной хуткасцю перадачы дадзеных або асінхроннай памяці праз праграмны кантролер памяці, убудаваны ў структуру FPGA, напрыклад CoreSDR_AXI. SMC_FIC - гэта падпарадкаваны інтэрфейс AXI або AHBLite AMBA. Інтэрфейсы DDR_FIC і SMC_FIC з'яўляюцца ўзаемавыключальнымі; толькі адзін актыўны адначасова.

Інтэрфейсы FIC дазваляюць натуральным чынам пашырыць шыну MSS AMBA ў структуру FPGA. Ёсць да двух асобнікаў FIC на MSS у залежнасці ад абранай прылады. Першы асобнік называецца FIC_0 (які даступны на кожнай прыладзе), а другі - FIC_1 (можа не прысутнічаць на меншых прыладах). Вы можаце наладзіць FIC як інтэрфейс APB3 або AHBLite AMBA у залежнасці ад вашых праектных патрэбаў. У кожным рэжыме даступны галоўны і падпарадкаваны інтэрфейс шыны. Гэта значыць, галоўны ў структуры можа ўзаемадзейнічаць з падпарадкаваным у MSS, а галоўны ў MSS можа ўзаемадзейнічаць з падпарадкаваным у структуры.

Кожная падсістэма Fabric Interface можа працаваць на рознай тактавай частаце, вызначанай як стаўленне асноўнага тактавага сігналу MSS M3_CLK.

Архітэктура SmartFusion2 навязвае правілы, звязаныя з даменамі тактавання паміж інтэрфейсамі Fabric і FPGA Fabric. Гэты дакумент дае рэкамендацыі па правільнай канструкцыі такіх сістэм.

Высокі ўзровень View

На малюнках 1 і 2 паказана, як MSS падключаецца да сеткі FPGA праз розныя кантролеры інтэрфейсу Fabric (FIC). Малюнак 1 паказвае агульную блок-схему пры выкарыстанні DDR_FIC (знешняя памяць DDR), а малюнак 2 паказвае блок-схему пры выкарыстанні SMC_FIC (знешняя памяць SDR).

На дыяграмах паказаны падблокі MSS, неабходныя для падключэння MSS да структуры FPGA. Падблок FIC можа выкарыстоўвацца або не выкарыстоўвацца ў вашым дадатку. Вы таксама можаце не выкарыстоўваць інтэрфейсы DDR_FIC або SMC_FIC у сваім дызайне. Аднак гэта не мяняе агульных патрабаванняў да таго, як стварыць дызайн з адным або некалькімі блокамі FIC, якія выкарыстоўваюцца ў дызайне.

Малюнак 1 • Блок-схема структуры MSS у FPGA – рэжым DDR_FIC

Малюнак 1 • Блок-схема структуры MSS у FPGA – рэжым DDR_FIC  Малюнак 2 • Блок-схема структуры MSS у FPGA – рэжым SMC_FIC

Малюнак 2 • Блок-схема структуры MSS у FPGA – рэжым SMC_FIC

MSS змяшчае:

- AHB_Bus матрыца; усе транзакцыі ў MSS праходзяць праз гэты блок.

- Кантролер DDR - інтэрфейсы з DDR_FIC.

- Падблок DDR_FIC (SMC_FIC) (выкарыстоўваецца, калі вы ўключылі шлях FPGA да DDR у канфігуратары MSS_MDDR).

- Субблок FIC_0.

- Падблок FIC_1 (толькі ў вялікіх прыладах).

- Падблок FIC_2 (для ініцыялізацыі APB SERDES і знешніх DDR).

- Падблок MSS_CCC неабходны для канфігурацыі гадзін FIC адносна асноўных гадзіннікаў MSS (M3_CLK).

- Падблок MSS_RESET, які стварае ўнутраныя скіды MSS, а таксама сігнал MSS_RESET_N_M2F, які кіруе структурай FPGA.

Тканіна FPGA змяшчае:

- Тры падсістэмы FIC (DDR_FIC, FIC_0 і FIC_1).

- Fabric CCC – FAB_CCC – патрабуецца для генерацыі гадзіннікаў, якія кіруюць падсістэмай FIC тканіны FPGA, а таксама портам MCCC_CLK_BASE ў блоку MSS.

- Апорны тактавы сігнал FAB_CCC - можа быць адным з убудаваных у мікрасхему асцылятараў, знешнім крышталёвым генератарам, тактавым сігналам, які генеруецца ўнутры мікрасхемы або звонку мікрасхемы.

Блок-схема таксама паказвае тактавую сетку чырвоным колерам і сетку скіду - цёмна-сінім.

У гэтым дакуменце разглядаецца кожны з гэтых блокаў і апісваецца, як падключыць гадзіны і скід.

MSS канфігуратар

У гэтым дакуменце спасылаюцца на пэўныя падблокі MSS, якія неабходна канфігураваць як частку стварэння дызайну, у якім MSS звязваецца са структурай FPGA праз падблокі FIC. На малюнку 1-1 гэтыя блокі вылучаны чырвоным колерам.

Малюнак 1-1 • Канфігуратар MSS

Малюнак 1-1 • Канфігуратар MSS

SmartDesign і дзеянні канфігуратара MSS

У гэтым дакуменце ёсць некалькі агульных дзеянняў; яны абагульнены ў наступным спісе:. Калі вы знаёмыя з SmartDesign і MSS, вы можаце перайсці да наступнага раздзела.

Стварэнне ядра - Дзеянне выбару ядра з IP-каталога Libero SoC, перацягвання гэтага ядра на палатно SmartDesign.

Настройка ядра - Дзеянне адкрыцця канфігуратара для асобніка гэтага ядра на Canvas, выбару канкрэтнай канфігурацыі і яе фіксацыі, націснуўшы OK у дыялогавым акне канфігуратара. У выніку гэтага дзеяння бачныя і даступныя для выкарыстання толькі парты, якія адносяцца да бягучай канфігурацыі.

Стварэнне асобніка кампанента - Дзеянне выбару кампанента ў іерархіі дызайну Libero SoC, перацягвання гэтага кампанента на палатно SmartDesign.

Стварэнне асобніка карыстацкага кампанента, сумяшчальнага з AMBA - дзеянне выбару кампанента HDL+ у іерархіі дызайну Libero SoC, перацягвання гэтага кампанента на палатно SmartDesign.

Выкарыстанне функцыі HDL+ дазваляе дадаваць сумяшчальныя з AMBA інтэрфейсы шыны (BIF) да звычайнага модуля HDL.

Настройка кампанента - Дзеянне адкрыцця канфігуратара для кампанента, створанага на палатне SmartDesign Canvas або з іерархіі дызайну, выбару пэўнай канфігурацыі і яе фіксацыі, націснуўшы OK у дыялогавым акне канфігуратара. У выніку гэтага дзеяння ўсе асобнікі гэтага кампанента ў праекце Libero SoC закрануты і патрабуюць абнаўлення. Калі асобнік абнаўляецца апошнім кампанентам, толькі парты, якія адносяцца да бягучай канфігурацыі, бачныя і даступныя для выкарыстання.

Уключэнне падблока MSS – Некаторыя падблокі MSS можна ўключыць або адключыць, паказваючы, што яны выкарыстоўваюцца ў бягучым дадатку. Усе нявыкарыстаныя падблокі павінны быць адключаныя.

Настройка падблока MSS – Дзеянне адкрыцця канфігуратара для гэтага падблока ў канфігуратары MSS, выбару канкрэтнай канфігурацыі і яе фіксацыі, націснуўшы кнопку OK у дыялогавым акне канфігуратара, а затым захаванне канфігурацыі MSS. У выніку гэтых дзеянняў кампанент MSS мае новую канфігурацыю і, магчыма, новы інтэрфейс порта. Калі асобнік MSS абнаўляецца апошнім кампанентам, толькі парты MSS, якія адносяцца да бягучай канфігурацыі, бачныя і даступныя для выкарыстання.

Стварэнне падсістэмы FPGA Fabric - Дзеянне стварэння, канфігурацыі ядраў і кампанентаў у SmartDesign Canvas і злучэння іх разам і з кампанентам MSS, створаным ужо ў гэтым канкрэтным SmartDesign.

Наладжванне падсістэмы DDR_FIC

Каб наладзіць/стварыць падсістэму DDR_FIC, вы павінны:

- Наладзьце MSS MDDR, каб адкрыць інтэрфейс DDR_FIC

- Стварыце падсістэму FPGA Fabric DDR_FIC, уключаючы стварэнне/канфігурацыю/злучэнне для:

– Шына AXI або AHBLite

- Майстар(ы) шыны AXI або AHBLite

– Іншыя майстры і перыферыйныя прылады на шыне ў адпаведнасці з патрабаваннямі вашай заяўкі

– Гадзіннік і скід; звярніцеся да «Настройка гадзіннікаў падсістэмы FIC» на старонцы 23 і «Настройка скіду падсістэмы FIC» на старонцы 27

Гэтыя крокі падрабязна апісаны ніжэй.

Крок 1: Наладзьце падблок MSS MDDR для доступу да інтэрфейсу шыны DDR_FIC

Інтэрфейс DDR_FIC адкрыты, калі вашаму прылажэнню патрабуецца доступ да знешняй памяці DDR з сеткі FPGA. У гэтай канфігурацыі падблок MDDR адкрывае інтэрфейс DDR_FIC, які з'яўляецца падпарадкаваным інтэрфейсам шыны AXI або AHBLite (BIF) (малюнак 3-1).

Малюнак 3-1 • Канфігурацыя MSS DDR з доступам з FPGA Fabric

Малюнак 3-1 • Канфігурацыя MSS DDR з доступам з FPGA Fabric

Крок 2: Стварыце падсістэму FPGA Fabric DDR_FIC

У залежнасці ад абранага тыпу злучэння шыны FPGA - AXI, Single AHBLite або Two AHBLite - вы павінны стварыць падсістэму, якая адпавядае вашаму выбару.

Падсістэма DDR_FIC/AXI

- Стварыце і наладзьце ядро CoreAXI IP з акна каталога. Уключыце слоты, якія вы плануеце выкарыстоўваць для вашага прыкладання, а таксама аб'ём памяці на слот, які адпавядае вашым патрабаванням да дызайну. Паколькі вы звяртаецеся да знешняй памяці DDR, ваш выбар памеру слота павінен адпавядаць прасторы, якую вы плануеце адрасаваць з майстра FPGA. (Малюнак 3-2).

Малюнак 3-2 • Канфігурацыя CoreAXI

Малюнак 3-2 • Канфігурацыя CoreAXI - Стварыце і наладзьце AMBA AXI-сумяшчальнае галоўнае ядро або кампанент, які прызначаны для апрацоўкі шыны AXI. Калі для вашага прыкладання патрабуецца больш чым адзін майстар на шыне CoreAXI, стварыце таксама другі майстар.

- Падключыце падсістэму:

– Падключыце порт M0 (M1) люстранога галоўнага інтэрфейсу шыны CoreAXI (BIF) да галоўнага порта BIF вашага экземпляра(аў) галоўнага ядра (малюнак 3-3).

– Падключыце падпарадкаваны порт MSS DDR_FIC BIF – MDDR_DDR_AXI_SLAVE – да адпаведнага люстранога падпарадкаванага слота шыны CoreAXI у адпаведнасці з вашымі патрабаваннямі карты памяці. Калі ў вас ёсць іншыя рабы на гэтай шыне, падключыце іх таксама ў адпаведнасці з вашай картай памяці.

– Гадзіннік і скід; звярніцеся да «Наладжванне гадзіннікаў падсістэмы FIC» на старонцы 23 і «Настройка скіду падсістэмы FIC» на старонцы 27.

Малюнак 3-3 • Падсістэма DDR_FIC AXI

Малюнак 3-3 • Падсістэма DDR_FIC AXI

Падсістэма DDR_FIC/Single-AHBLite

- Стварыце і наладзьце IP-ядро CoreAHBLite з каталога. Уключыце слоты, якія вы плануеце выкарыстоўваць для свайго прыкладання, як паказана на малюнку 3-4. У гэтым эксample, CoreAHBLite сканфігураваны для адрасавання аднаго 4 ГБ памяці DDR RAM з выкарыстаннем слота 0 ад майстра M0. Паколькі вы звяртаецеся да знешняй памяці DDR, ваш выбар памеру слота павінен адпавядаць аб'ёму памяці DDR, да якой вы плануеце звяртацца з майстра FPGA.

Малюнак 3-4 • Ядро AHBLite – камбінаваная галоўная канфігурацыя вобласці

Малюнак 3-4 • Ядро AHBLite – камбінаваная галоўная канфігурацыя вобласці - Стварыце і наладзьце сумяшчальнае з AMBA AHBLite галоўнае ядро або кампанент, які прызначаны для апрацоўкі шыны CoreAHBLite. Калі вашаму прылажэнню патрабуецца больш чым адзін майстар на шыне CoreAHBLite, стварыце асобнік дадатковых майстроў. На шыне CoreAHBLite падтрымліваецца да чатырох майстроў.

- Падключыце падсістэму:

– Падключыце порт M0 (M1) люстранога галоўнага інтэрфейсу шыны CoreAHBLite (BIF) да галоўнага порта BIF вашага асобніка(-аў) галоўнага ядра.

– Падключыце падпарадкаваны порт MSS DDR_FIC BIF – MDDR_DDR_AHB0_SLAVE – да адпаведнага люстранога падпарадкаванага слота шыны CoreAHBLite (S0 у гэтым прыкладзеample) у адпаведнасці з патрабаваннямі вашай карты памяці. Калі ў вас ёсць іншыя рабы на гэтай шыне, падключыце іх, а таксама па вашай карце памяці.

– Гадзіннік і скід; звярніцеся да «Наладжванне гадзіннікаў падсістэмы FIC» на старонцы 23 і «Настройка скіду падсістэмы FIC» на старонцы 27.

Малюнак 3-5 • Падсістэма DDR_FIC AHBLite

Малюнак 3-5 • Падсістэма DDR_FIC AHBLite

DDR_FIC/дзве падсістэмы AHBLite

Калі вы выбіраеце варыянт двух інтэрфейсаў AHBLite для MDDR, дадатковы BIF, MDDR_DDR_AHB1_SLAVE BIF, выстаўляецца ў кампаненце MSS для падлучэння да новага падпарадкаванага.

Для гэтай канфігурацыі паўтарыце крокі для адной канфігурацыі AHBLite для інтэрфейсу MDDR_DDR_AHB1_SLAVE BIF, адкрытага для кампанента MSS.

Хоць SMC_FIC можна выкарыстоўваць як інтэрфейс шыны AXI або AHBLite, у гэтым дакуменце апісваецца толькі тое, як выкарыстоўваць інтэрфейс SMC_FIC, сканфігураваны ў рэжыме AXI, для падлучэння да ядра CoreSDR_AXI. Гэта ядро ўяўляе сабой кантролер аператыўнай памяці SDR на базе AXI, які выкарыстоўваецца для падлучэння, у дадзеным выпадку, MSS да вонкавага кампанента памяці з адзінай хуткасцю перадачы дадзеных (SDR). Вы можаце лёгка зрабіць выснову, як выкарыстоўваць інтэрфейс AHBLite з наступнага апісання; крокі вельмі падобныя. Інтэрфейс AXI з'яўляецца больш эфектыўным інтэрфейсам і з'яўляецца пераважным варыянтам.

Каб наладзіць/стварыць падсістэму SMC_FIC, вы павінны:

- Наладзьце MSS MDDR, каб адкрыць інтэрфейс SMC_FIC

- Стварыце падсістэму FPGA Fabric DDR_FIC, уключаючы стварэнне/канфігурацыю/злучэнне для:

- шына CoreAXI

– CoreSDR_AXI

– Іншыя майстры і перыферыйныя прылады на шыне ў адпаведнасці з патрабаваннямі вашай заяўкі

– Гадзіннік і скід; звярніцеся да «Настройка гадзіннікаў падсістэмы FIC» на старонцы 23 і «Настройка скіду падсістэмы FIC» на старонцы 27

Гэтыя крокі падрабязна апісаны ніжэй.

Крок 1: Наладзьце падблок MSS MDDR, каб адкрыць інтэрфейс шыны SMC_FIC

Інтэрфейс SMC_FIC адкрыты, калі вашай праграме патрабуецца доступ да знешняй памяці SDR праз структуру FPGA. У гэтай канфігурацыі падблок MDDR адкрывае інтэрфейс SMC_FIC, які з'яўляецца галоўным інтэрфейсам шыны AXI або AHBL (BIF) (малюнак 4-1).

- Пстрыкніце правай кнопкай мышы кантролер MDDR у канфігуратару MSS і выберыце «Наладзіць».

- Выберыце Выкарыстоўваць інтэрфейс AXI.

- Націсніце OK.

Малюнак 4-1 • Канфігурацыя праграмнага кантролера памяці MDDR

Малюнак 4-1 • Канфігурацыя праграмнага кантролера памяці MDDR

- Абнавіце кампанент MSS са зменамі.

(Пстрыкніце правай кнопкай мышы кампанент MSS і абярыце Абнавіць асобнікі апошнім кампанентам). MDDR_SMC_AXI_MASTER прадстаўлены як порт інтэрфейсу шыны кампанента MSS.

Крок 2: Стварыце падсістэму FPGA Fabric SMC_FIC

- Стварыце і наладзьце CoreAXI так, каб галоўны слот M0 быў уключаны для падпарадкаванага слота S0, як паказана на малюнку 4-2. Паколькі вы звяртаецеся да знешняй памяці праз праграмны кантролер памяці, ваш выбар памеру слота павінен адпавядаць аб'ёму вонкавай памяці, да якой вы плануеце звяртацца з працэсара Cortex-M3 або любога майстра запісу ў гэтую знешнюю памяць праз мост MSS DDR.

Малюнак 4-2 • Канфігурацыя CoreAXI – рэжым SMC_FIC

Малюнак 4-2 • Канфігурацыя CoreAXI – рэжым SMC_FIC - З IP-каталога стварыце і наладзьце CoreSDR_AXI у адпаведнасці з параметрамі знешняй памяці.

- Падключыце падсістэму (малюнак 4-3):

– Падключыце галоўны порт BIF MSS SMC_FIC – MDDR_SMC_AXI_MASTER – да шыны CoreAXI з адлюстраваннем галоўнага M0.

– Падключыце порт S0 люстранога падпарадкаванага інтэрфейсу шыны CoreAXI (BIF) да падпарадкаванага порта BIF асобніка ядра CoreSDR_AXI.

– Гадзіннік і скід; звярніцеся да «Наладжванне гадзіннікаў падсістэмы FIC» на старонцы 23 і «Настройка скіду падсістэмы FIC» на старонцы 27.

Малюнак 4-3 • Злучэнні падсістэмы SMC_FIC

Малюнак 4-3 • Злучэнні падсістэмы SMC_FIC

Наладжванне падсістэм FIC

Каб наладзіць/стварыць падсістэму FIC, вы павінны:

- Наладзьце MSS FIC, каб адкрыць інтэрфейс FIC

- Стварыце падсістэму FPGA Fabric FIC, уключаючы стварэнне/канфігурацыю/злучэнне для:

– шына APB3 або AHBLite

- APB3 і AHBLite сумяшчальны галоўны і / або канфігурацыя перыферыйных прылад і падключэнне да шыны ў адпаведнасці з вашым дадаткам

– Гадзіннік і скід; звярніцеся да «Настройка гадзіннікаў падсістэмы FIC» на старонцы 23 і «Настройка скіду падсістэмы FIC» на старонцы 27

Гэтыя крокі падрабязна апісаны ніжэй.

Крок 1: Наладзьце падблок MSS FIC

- Выклічце канфігуратар FIC і пстрыкніце правай кнопкай мышы на FIC_0 або FIC_1, каб адкрыць канфігуратар FIC.

- У групе канфігурацыі канфігуратара інтэрфейсу MSS для FPGA выберыце:

– Тып інтэрфейсу AHBLite або APB3

– Ці збіраецеся вы выкарыстоўваць інтэрфейс у якасці майстра структуры FPGA

– Ці збіраецеся вы выкарыстоўваць інтэрфейс у якасці падпарадкаванага, асвоенага структурай FPGA (малюнак 5-1)

Малюнак 5-1 • Варыянты інтэрфейсу MSS да FPGA Fabric

Малюнак 5-1 • Варыянты інтэрфейсу MSS да FPGA Fabric - Калі вы выкарыстоўваеце інтэрфейс AHBLite, вы таксама можаце выкарыстаць дадатковыя параметры AHBLite, каб выбраць рэжым абыходу або адкрыць порт галоўнага ідэнтыфікатара, калі вы выбралі інтэрфейс, які будзе выступаць у якасці майстра структуры (малюнак 5-2).

Малюнак 5-2 • Дадатковыя параметры AHBLite

Малюнак 5-2 • Дадатковыя параметры AHBLite

Крок 2: Стварыце падсістэму FIC Fabric FPGA

Для кожнага адкрытага інтэрфейсу FIC - галоўнага і падпарадкаванага - вы павінны стварыць асобнік шыны (CoreAHBLite або CoreAPB3), якая адпавядае абранаму вамі тыпу. У залежнасці ад ролі інтэрфейсу (галоўны/падпарадкаваны) і тыпу (AHBLite/APB3), шына павінна быць сканфігуравана наступным чынам:

Майстар/AHBLite

Стварыце і наладзьце шыну CoreAHBLite наступным чынам:

- Выберыце опцыю памяці, якая адпавядае вашым патрабаванням:

– Калі вам патрабуецца менш за 16 МБ адраснай прасторы ўсіх вашых перыферыйных прылад, абярыце опцыю, як паказана на малюнку 5-3. Гэты рэжым забяспечвае 16 слотаў па 16 МБ, якія можна выкарыстоўваць для падлучэння да 16 падпарадкаваных AHBLite.

Малюнак 5-3 • Канфігурацыя прасторы памяці Master/AHBLite – 16 МБ на слот

Малюнак 5-3 • Канфігурацыя прасторы памяці Master/AHBLite – 16 МБ на слот

– Калі вам трэба больш за 16 МБ і менш за 256 МБ адраснай прасторы для любой з вашых перыферыйных прылад, абярыце опцыю, як паказана на малюнку 5-4. Гэты рэжым забяспечвае 16 слотаў па 256 МБ, якія можна выкарыстоўваць для падлучэння да 16 падпарадкаваных AHBLite.

Малюнак 5-4 • Канфігурацыя прасторы памяці Master/AHBLite – 256 МБ на слот

Малюнак 5-4 • Канфігурацыя прасторы памяці Master/AHBLite – 256 МБ на слот - Уключыце слоты, якія вы выкарыстоўваеце для вашага прыкладання (малюнак 5-5). Найлепшая практыка - выкарыстоўваць M1 для доступу да слотаў, як паказана на малюнку 4-2 на старонцы 15.

Заўвага: Выкарыстоўвайце M1, калі вы плануеце стварыць падсістэму з некалькімі галоўнымі, дзе ў вас ёсць майстар у структуры, якая патрабуе функцыі пераназначэння і, такім чынам, павінна быць падключана да M0.

– Калі вы абралі опцыю 16 МБ на слот, няма абмежаванняў на тое, якія слоты можна выкарыстоўваць.

– Калі вы абралі опцыю 256 МБ на слот, можна выкарыстоўваць толькі слоты, сумяшчальныя з выбарам рэгіёнаў адрасоў памяці FIC. Кожная вобласць адрасоў памяці FIC мае памер 256 МБ. Шэсць абласцей памяці FIC зведзены ў табліцы 5-1.

Табліца 5-1 • Рэгіёны адрасоў і сумяшчальныя слоты для варыянту 256 МБ на слот

Рэгіён адраса памяці Сумяшчальныя слоты 30000000-3FFFFFFF 3 50000000-5FFFFFFF 5 70000000-7FFFFFFF 7 80000000-8FFFFFFF 8 90000000-9FFFFFFF 9 F0000000-FFFFFFFF 15 (F)  Малюнак 5-5 • Канфігурацыя галоўнага доступу Master/AHBLite

Малюнак 5-5 • Канфігурацыя галоўнага доступу Master/AHBLite - Стварэнне і канфігурацыя перыферыйных ядраў, сумяшчальных з AHBLite, і/або карыстацкіх кампанентаў, сумяшчальных з AHBLite.

- Падключыце падсістэму:

– Падключыце порт M1 люстранога галоўнага інтэрфейсу шыны CoreAHBLite (BIF) да галоўнага порта BIF MSS – FIC_0/1_AHB_MASTER – як паказана на малюнку 5-6.

– Падключыце падпарадкаваныя прылады AHBLite да адпаведных слотаў у адпаведнасці з вашымі патрабаваннямі карты памяці.

– Гадзіннік і скід; звярніцеся да «Наладжванне гадзіннікаў падсістэмы FIC» на старонцы 23 і «Настройка скіду падсістэмы FIC» на старонцы 27.

Малюнак 5-6 • Падсістэма FIC Master/AHBLite

Малюнак 5-6 • Падсістэма FIC Master/AHBLite

Майстар/APB3

Стварыце і наладзьце шыну CoreAPB3 наступным чынам:

- Выберыце параметры канфігурацыі адраса, як паказана на малюнку 5-7. Гэты рэжым забяспечвае шаснаццаць слотаў па 16 МБ, якія можна выкарыстоўваць для падлучэння да шаснаццаці падпарадкаваных сістэм, сумяшчальных з APB3. Калі вам патрэбныя слоты з большай памяццю, вы можаце аб'яднаць некалькі падпарадкаваных, каб пабудаваць большы слот. Больш падрабязную інфармацыю аб гэтай опцыі глядзіце ў Кіраўніцтве карыстальніка CoreAPB3.

Малюнак 5-7 • Канфігурацыя адраса Master/APB3

Малюнак 5-7 • Канфігурацыя адраса Master/APB3 - Уключыце слоты, якія вы выкарыстоўваеце для вашага прыкладання, як паказана на малюнку 5-8.

Малюнак 5-8 • Канфігурацыя галоўных/падпарадкаваных слотаў APB3

Малюнак 5-8 • Канфігурацыя галоўных/падпарадкаваных слотаў APB3 - Стварыце асобнік і наладзьце перыферыйныя ядра, сумяшчальныя з APB3, і/або спецыяльныя сумяшчальныя з APB3 кампаненты.

- Падключыце падсістэму:

– Падключыце порт CoreAPB3 з люстраным галоўным інтэрфейсам шыны (BIF) да галоўнага порта BIF MSS FIC_0/1_APB_MASTER – як паказана на малюнку 5-9.

– Падключыце падпарадкаваныя прылады APB3 да адпаведных слотаў у адпаведнасці з вашымі патрабаваннямі карты памяці.

– Гадзіннік і скід; звярніцеся да «Наладжванне гадзіннікаў падсістэмы FIC» на старонцы 23 і «Настройка скіду падсістэмы FIC» на старонцы 27.

Малюнак 5-9 • Падсістэма FIC Master/APB3

Малюнак 5-9 • Падсістэма FIC Master/APB3

Раб/AHBLite

Зараз недаступна.

Нявольнік/APB3

Зараз недаступна.

Наладжванне гадзіннікаў падсістэмы FIC

Каб стварыць правільную канфігурацыю гадзінніка і падключэнне, вы павінны:

- Наладзьце такты MSS CCC FIC

- Стварыце і наладзьце ядро CCC FPGA

- Падключыце тактавыя сеткі для кожнай падсістэмы FIC

- Падключыце порт MSS CLK_BASE да правільнай тактавай сеткі падсістэмы FIC FPGA

Архітэктура SmartFusion2 навязвае шэраг правілаў, якія неабходна выконваць для ўсіх падсістэм FIC, каб правільна ўзаемадзейнічаць паміж логікай MSS і логікай FPGA. Гэтыя правілы вызначаны ніжэй і паказаны на малюнку 6-1.

- Кожная падсістэма FPGA Fabric FIC павінна кіравацца тактавым сігналам, тактавая частата якога адпавядае частаце, вызначанай для гэтай канкрэтнай падсістэмы ў канфігуратары MSS CCC.

- Усе тактавыя сігналы падсістэмы FIC FPGA павінны быць дакладна выраўнаваны; тактавыя сігналы могуць быць з рознымі частотамі, але нарастаючыя фронты больш павольных тактаў павінны быць выраўнаваны з нарастаючымі фронтамі самых хуткіх тактаў.

- Гадзіннік падсістэмы FPGA Fabric FIC з найменшай частатой павінен кіраваць MSS CLK_BASE.

- Калі тактавыя сігналы атрымліваюцца ад CCC у сеткі (з PLL), выхад CCC LOCK у структуры павінен быць падлучаны да порта MSS_CCC_CLK_BASE_PLL_LOCK. Схема тактавага сігналу MSS CCC Fabric Alignment Clock Circuitry (FACC) кантралюе сігнал CLK_BASE PLL LOCK, каб гарантаваць стабільнасць CLK_BASE перад пераключэннем з рэжыму чакання (гадзіннік, які выкарыстоўваецца падчас загрузкі прылады) на настроены карыстальнікам гадзіннік, атрыманы з CLK_BASE.

Малюнак 6-1 • Правілы падсістэмнага гадзінніка

Малюнак 6-1 • Правілы падсістэмнага гадзінніка

Выканайце наступныя крокі, каб наладзіць сеткі гадзінніка для ўсіх вашых падсістэм FIC.

Крок 1: Наладзьце падблок MSS CCC

Для кожнага блока FIC (FIC_0, FIC_1 і DDR_FIC/SMC_FIC), які выкарыстоўваецца ў вашым дызайне, выберыце дзельнікі тактавага сігналу ў канфігуратару тактавага сігналу MSS (MSS_CCC), як паказана на малюнку 6-2. Малюнак 6-2 • Канфігурацыя гадзінніка MSS CCC FIC

Малюнак 6-2 • Канфігурацыя гадзінніка MSS CCC FIC

Заўвага што поле CLK_BASE нельга рэдагаваць. Частата CLK_BASE, вызначаная архітэктурай SmartFusion2, павінна быць мінімальнай частатой з усіх тактавых частот FIC і аўтаматычна вылічваецца канфігуратарам MSS CCC. Больш падрабязную інфармацыю аб канфігурацыі CLK_BASE глядзіце ў раздзеле «Крок 3: Падключыце тактавыя сеткі падсістэм FPGA Fabric FIC» на старонцы 25.

Крок 2: Наладзьце тактавыя частоты FIC FPGA Fabric

Стварыце асобнік сеткі CCC (з PLL) і наладзьце яе так, каб ён адпавядаў правілам тактавай частоты падсістэмы FIC, апісаным на старонцы 23. Як правіла, вам трэба звязаць глабальны выхад (GLx) для кожнага з тактавых сігналаў FIC, пазначыць для кожнага выхаду яго частату ( адпаведнасць частотам, вызначаным у MSS CCC) і мець усе глабальныя выхады, атрыманыя з выхаду ФАПЧ, каб гарантаваць выраўноўванне фаз (як паказана на малюнку 6-3).

Заўвага: Калі дзве падсістэмы FIC маюць аднолькавыя частоты, вам не трэба генераваць два незалежныя глабальныя выхады з CCC сеткі; аднаго дастаткова. Малюнак 6-3 • Тканкавы CCC з PLL

Малюнак 6-3 • Тканкавы CCC з PLL

Крок 3: Падключыце гадзіннік падсістэмы FPGA Fabric FIC Сеткі

Падключыце кожны глабальны выхад GLx CCC да падсістэмы FIC, з якой ён звязаны.

Крок 4: Падключыце порт MSS CLK_BASE

Падключыце самы павольны глабальны выхад GLx CCC да порта MSS CLK_BASE.

Крок 5: Падключыце порт MSS MCCC_CLK_BASE_PLL_LOCK

Падключыце выхад CCC LOCK да порта MSS MCCC_CLK_BASE_PLL_LOCK.

Патрабаванні да аналізу часу

Выканайце статычны аналіз часу пасля макета, каб пераканацца, што канструкцыя адпавядае патрабаванням да часу, вызначаным у канфігуратары CCC MSS CCC і FPGA. Магчыма, вам прыйдзецца змяніць M3_CLK або павялічыць тактавы каэфіцыент паміж MSS і тканінай, каб атрымаць дызайн, які праходзіць статычны аналіз часу.

Наладжванне скіду падсістэмы FIC

Каб наладзіць скід падсістэмы FIC:

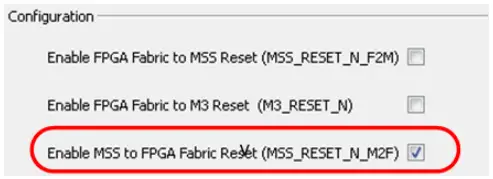

- З канфігуратара MSS наладзьце падблок MSS Reset, каб адкрыць порт MSS_RESET_N_M2F.

Малюнак 7-1 • Наладзьце падблок скіду MSS

Малюнак 7-1 • Наладзьце падблок скіду MSS - Падключыце порт MSS_RESET_N_M2F да ўсіх партоў скіду падсістэм FIC FPGA.

Настройка карты сістэмнай памяці

Кожная перыферыйная прылада (падпарадкаваныя прылады AMBA AXI, AHBLite і APB3) ідэнтыфікуецца адрасам з галоўнай кропкі падсістэмы FIC view. Звычайна мы называем агульныя адносіны паміж гаспадарамі і падпарадкаванымі падсістэмы картай памяці гэтай падсістэмы. Карту памяці падсістэмы можна рэдагаваць у SmartDesign. Вы таксама можаце view канчатковая карта памяці вашай сістэмы пры стварэнні ўсёй сістэмы. Карта памяці з'яўляецца часткай табліцы дадзеных, якая ствараецца для «кораня» вашага дызайну пры генерацыі.

Наладжванне карты памяці (агульнае паводзіны SmartDesign)

У SmartDesign перыферыйнаму прыладзе прысвойваецца адрас на шыне на аснове базавага адраса гэтай шыны ў падсістэме плюс нумар слота на гэтай шыне, памножаны на памер слота. Такім чынам, змяненне нумара слота для перыферыйнага прылады адпаведна ўплывае на яго адрас. Змяніць прызначэнне слота для перыферыйнага прылады можна ўручную падключыць падпарадкаваны BIF перыферыйнага прылады да пэўнага люстранога падпарадкаванага BIF (слота) шыны з дапамогай інструментаў падключэння SmartDesign, даступных у Canvas. Гэта таксама можна зрабіць шляхам рэдагавання карты памяці з дапамогай Modify Memory Map, як паказана на малюнку 8-1. Малюнак 8-1 • Змяніць карту памяці з SmartDesign Canvas

Малюнак 8-1 • Змяніць карту памяці з SmartDesign Canvas

З'явіцца дыялогавае акно «Змяніць карту памяці» (малюнак 8-2). Малюнак 8-2 • Дыялогавае акно змены карты памяці

Малюнак 8-2 • Дыялогавае акно змены карты памяці

Настройка абласцей памяці для інтэрфейсаў FIC (MSS Master View)

У карце памяці MSS ёсць шэсць рэгіёнаў па 256 МБ, вызначаных як рэгіёны FIC ад 0 да 5. Кожны з гэтых рэгіёнаў можа быць размеркаваны падпарадкаваным інтэрфейсам FIC_0 або FIC_1 узаемавыключальным чынам. Вы можаце выбраць, да якога падпарадкаванага інтэрфейсу FIC (0 ці 1) вы прызначыце гэтыя рэгіёны, выкарыстоўваючы перамыкач побач з кожным рэгіёнам у рэгіёнах адрасоў FPGA Fabric (MSS Master View) групавое поле (малюнак 8-3).  Малюнак 8-3 • Рэгіёны адрасоў FPGA Fabric (MSS Master View)

Малюнак 8-3 • Рэгіёны адрасоў FPGA Fabric (MSS Master View)

Агульная формула вылічэння карты памяці

Магчымыя базавыя адрасы для інтэрфейсаў FIC: 0x30000000, 0x50000000, 0x70000000, 0x80000000, 0x90000000 і 0xF0000000. Глядзіце раздзел «Канфігураванне падсістэм FIC» на старонцы 17 для атрымання падрабязнай інфармацыі аб тым, як наладзіць кожны асобнік FIC для супастаўлення з гэтымі адрасамі.

Для AHBLite памер слота можа быць альбо 16 МБ (0x01000000), альбо 256 МБ (0x10000000).

Пры выкарыстанні 16 МБ на слот можна выкарыстоўваць усе слоты ад 0 да 16; адрас кліенцкай перыферыі можа быць вылічаны як базавы адрас вобласці памяці FIC + (нумар слота * 0x01000000). У гэтай канфігурацыі ўсе рэгіёны фактычна з'яўляюцца псеўданімамі адзін аднаго, паколькі ядро AHBLite не дэкадуе біты адраса [31:28]; слоты дэкадуюцца з выкарыстаннем адрасных бітаў [27:24].

Пры выкарыстанні 256 МБ на слот можна выкарыстоўваць толькі слоты 3, 5, 7, 8, 9 і F; адрас кліенцкай перыферыі можа быць вылічаны як базавы адрас вобласці памяці FIC + (нумар слота * 0x10000000). У гэтай канфігурацыі ўсе рэгіёны адназначна адрасуюць розныя слоты, паколькі ядро AHBLite дэкадуе слоты з дапамогай адрасных бітаў [31:28]. У гэтай канфігурацыі, каб спрасціць раўнанне карты памяці, базавы адрас 0x00000000 замест аднаго з шасці фіксаваных адрасоў, вызначаных вышэй.

Example 1 (канфігурацыя слота 16 МБ):

Выкарыстоўваючы вобласць памяці 0x50000000, калі перыферыйнае прылада знаходзіцца ў слоце нумар 7, то яго адрас: 0x50000000 + (0x7 * 0x01000000) = 0x57000000

Example 2 (канфігурацыя слота 256 МБ):

Выкарыстоўваючы вобласць памяці 0x50000000, калі перыферыйнае прылада знаходзіцца ў слоце нумар 15, то яго адрас: 0x00000000 + (0xF * 0x10000000) = 0xF0000000

Viewканчатковую карту памяці

На дадзены момант Libero SoC не стварае правільную карту памяці для сістэм, якія выкарыстоўваюць SmartFusion2 MSS.

Падтрымка прадукту

Microsemi SoC Products Group падтрымлівае сваю прадукцыю рознымі службамі падтрымкі, уключаючы службу падтрымкі кліентаў, цэнтр тэхнічнай падтрымкі кліентаў, webсайт, электронная пошта і офісы продажаў па ўсім свеце. Гэта дадатак утрымлівае інфармацыю аб тым, як звязацца з Microsemi SoC Products Group і выкарыстоўваць гэтыя службы падтрымкі.

Абслугоўванне кліентаў

Звярніцеся ў службу падтрымкі для атрымання нетэхнічнай падтрымкі прадукту, напрыклад, цэнаўтварэння прадукту, абнаўлення прадукту, абнаўлення інфармацыі, статусу заказу і аўтарызацыі.

Тэлефануйце з Паўночнай Амерыкі 800.262.1060

З усяго свету тэлефануйце 650.318.4460

Факс з любой кропкі свету, 408.643.6913

Цэнтр тэхнічнай падтрымкі кліентаў

Microsemi SoC Products Group укамплектоўвае свой Цэнтр тэхнічнай падтрымкі кліентаў высокакваліфікаванымі інжынерамі, якія могуць дапамагчы адказаць на вашыя апаратныя, праграмныя і дызайнерскія пытанні аб прадуктах Microsemi SoC. Цэнтр тэхнічнай падтрымкі кліентаў марнуе шмат часу на стварэнне нататак па прылажэнні, адказаў на агульныя пытанні цыкла праектавання, дакументацыі вядомых праблем і розных часта задаваемых пытанняў. Такім чынам, перш чым звязацца з намі, наведайце нашы інтэрнэт-рэсурсы. Вельмі верагодна, што мы ўжо адказалі на вашы пытанні.

Тэхнічная падтрымка

Наведайце службу падтрымкі кліентаў webсайт (www.microsemi.com/soc/support/search/default.aspx) для атрымання дадатковай інфармацыі і падтрымкі. Многія адказы даступныя ў пошуку web Рэсурс змяшчае дыяграмы, ілюстрацыі і спасылкі на іншыя рэсурсы на webсайт.

Webсайт

Вы можаце праглядаць разнастайную тэхнічную і нетэхнічную інфармацыю на галоўнай старонцы SoC па адрасе www.microsemi.com/soc.

Зварот у Цэнтр тэхнічнай падтрымкі кліентаў

У Цэнтры тэхнічнай падтрымкі працуюць высокакваліфікаваныя інжынеры. З Цэнтрам тэхнічнай падтрымкі можна звязацца па электроннай пошце або праз Microsemi SoC Products Group webсайт.

Электронная пошта

Вы можаце задаць свае тэхнічныя пытанні на наш адрас электроннай пошты і атрымаць адказы па электроннай пошце, факсу або тэлефоне. Акрамя таго, калі ў вас ёсць праблемы з дызайнам, вы можаце адправіць свой дызайн па электроннай пошце files атрымаць дапамогу. Мы пастаянна кантралюем уліковы запіс электроннай пошты на працягу дня. Адпраўляючы нам свой запыт, не забудзьцеся ўказаць сваё поўнае імя, назву кампаніі і кантактную інфармацыю для эфектыўнай апрацоўкі вашага запыту.

Адрас электроннай пошты тэхнічнай падтрымкі soc_tech@microsemi.com.

Мае справы

Кліенты Microsemi SoC Products Group могуць адпраўляць і адсочваць тэхнічныя справы ў Інтэрнэце, перайшоўшы на сайт Мае справы.

За межамі ЗША

Кліенты, якім патрэбна дапамога за межамі гадзінных паясоў ЗША, могуць звязацца са службай тэхнічнай падтрымкі па электроннай пошце (soc_tech@microsemi.com) або звярніцеся ў мясцовы офіс продажаў. Спіс офісаў продажаў можна знайсці па адрасе www.microsemi.com/soc/company/contact/default.aspx.

Тэхнічная падтрымка ITAR

Для атрымання тэхнічнай падтрымкі па RH і RT FPGA, якія рэгулююцца Правіламі міжнароднага гандлю зброяй (ITAR), звяжыцеся з намі праз soc_tech_itar@microsemi.com. Акрамя таго, у раздзеле "Мае справы" выберыце "Так" у выпадальным спісе ITAR. Каб атрымаць поўны спіс рэгулюемых ITAR FPGA Microsemi, наведайце ITAR web старонка.

Карпарацыя Microsemi (NASDAQ: MSCC) прапануе шырокі асартымент паўправаднікоў рашэнні для: аэракасмічная, абарона і бяспека; прадпрыемства і сувязь; і прамысловыя і альтэрнатыўныя рынкі энергіі. Прадукцыя ўключае высокапрадукцыйныя, высоканадзейныя аналагавыя і радыёчастотныя прылады, інтэгральныя схемы са змешаным сігналам і радыёчастотныя схемы, наладжвальныя SoC, FPGA і поўныя падсістэмы. Штаб-кватэра Microsemi знаходзіцца ў Аліса-В'еха, Каліфорнія. Даведайцеся больш на www.microsemi.com.

© 2014 Microsemi Corporation. Усе правы ахоўваюцца. Microsemi і лагатып Microsemi з'яўляюцца гандлёвымі маркамі Microsemi Corporation. Усе іншыя гандлёвыя маркі і знакі абслугоўвання з'яўляюцца ўласнасцю іх адпаведных уладальнікаў.

5-02-00370-1/08.14

Карпаратыўны штаб-кватэра Microsemi

Карпаратыўны штаб-кватэра Microsemi

One Enterprise, Aliso Viejo CA 92656 ЗША

У межах ЗША: +1 949-380-6100

Продажы: +1 949-380-6136

Факс: +1 949-215-4996

Дакументы / Рэсурсы

|

Microsemi SmartFusion2 MSS Стварэнне дызайну [pdfКіраўніцтва карыстальніка SmartFusion2 MSS Стварэнне дызайну |