SmartFusion2 MSS

SmartFusion2 MSS

Crearea unui design folosind interfețele MSS Fabric

Ghidul utilizatorului

Introducere

Subsistemul de microcontroler SmartFusion2 (MSS) oferă patru controlere de interfață fabrică diferite (FIC):

- DDR_FIC

- SMC_FIC

- FIC_0 și FIC_1, în funcție de dispozitivul dvs

Aceste blocuri de interfață permit MSS să interfațeze cu logica implementată în structura FPGA și vice

invers.

DDR_FIC este utilizat când configurați blocul MSS DDR (MDDR) astfel încât DDR extern

memoria poate fi accesată de la un fabric master FPGA printr-o interfață AXI sau 2 interfețe AHBLite AMBA.

SMC_FIC este utilizat când configurați blocul MSS DDR în modul Single Date Rate (SDR). În această configurație, MSS accesează DRAM cu rată de date unică sau memorii asincrone externe printr-un controler de memorie soft instanțiat în structura FPGA, cum ar fi CoreSDR_AXI. SMC_FIC este o interfață slave AXI sau AHBLite AMBA. Interfețele DDR_FIC și SMC_FIC se exclud reciproc; doar unul este activ la un moment dat.

Interfețele FIC vă permit să extindeți în mod natural magistrala MSS AMBA în materialul FPGA. Există până la două instanțe FIC per MSS, în funcție de dispozitivul selectat. Prima instanță se numește FIC_0 (care este disponibilă pe fiecare dispozitiv), iar a doua se numește FIC_1 (poate să nu fie prezentă pe dispozitivele mai mici). Puteți configura FIC ca interfață APB3 sau AHBLite AMBA, în funcție de nevoile dvs. de proiectare. În fiecare mod, sunt disponibile o interfață de magistrală master și slave. Adică, un master din țesătură poate interfața cu un slave din MSS, iar un master din MSS poate interfața cu un slave din țesătură.

Fiecare subsistem Fabric Interface poate funcționa pe o frecvență de ceas diferită, definită ca raport al ceasului principal MSS M3_CLK.

Arhitectura SmartFusion2 impune reguli legate de domeniile de sincronizare între Interfețele Fabric și Fabrica FPGA. Acest document oferă îndrumări despre cum să construiți corect astfel de sisteme.

Nivel inalt View

Figura 1 și Figura 2 arată modul în care MSS se conectează la țesătura FPGA prin intermediul diferitelor controlere de interfață fabrică (FIC). Figura 1 prezintă o diagramă bloc generală atunci când este utilizat DDR_FIC (memorie DDR externă) și Figura 2 prezintă o diagramă bloc pentru când este utilizat SMC_FIC (memorie SDR externă).

Diagramele arată subblocurile MSS esențiale pentru conectarea MSS la țesătura FPGA. Subblocul FIC poate fi sau nu utilizat în aplicația dvs. De asemenea, este posibil să nu utilizați interfețele DDR_FIC sau SMC_FIC în designul dvs. Totuși, acest lucru nu modifică cerințele generale pentru crearea unui design cu unul sau mai multe blocuri FIC utilizate în proiect.

Figura 1 • Diagrama bloc de fabrică MSS la FPGA – Modul DDR_FIC

Figura 1 • Diagrama bloc de fabrică MSS la FPGA – Modul DDR_FIC  Figura 2 • Diagrama bloc de fabrică MSS la FPGA – Modul SMC_FIC

Figura 2 • Diagrama bloc de fabrică MSS la FPGA – Modul SMC_FIC

MSS conține:

- Matricea AHB_Bus; toate tranzacțiile din MSS trec prin acest bloc.

- Controller DDR - interfață cu DDR_FIC.

- Subbloc DDR_FIC (SMC_FIC) (utilizat dacă activați calea fabricii FPGA către DDR în configuratorul MSS_MDDR).

- Subbloc FIC_0.

- Subbloc FIC_1 (numai pentru dispozitivele mai mari).

- Subbloc FIC_2 (pentru inițializarea APB a SERDES și a DDR-urilor externe).

- Subblocul MSS_CCC necesar pentru a configura ceasurile FIC în raport cu ceasul principal MSS (M3_CLK).

- Subbloc MSS_RESET care generează resetările interne MSS, precum și semnalul MSS_RESET_N_M2F care conduce structura FPGA.

Materialul FPGA conține:

- Trei subsisteme FIC (DDR_FIC, FIC_0 și FIC_1).

- Fabric CCC – FAB_CCC – necesar pentru a genera ceasurile care conduc subsistemul FPGA fabric FIC, precum și portul MCCC_CLK_BASE de pe blocul MSS.

- Semnal de ceas de referință FAB_CCC – poate fi unul dintre oscilatorii de pe cip, un oscilator cu cristal extern, un ceas generat intern țesăturii sau din exteriorul cipului.

Diagrama bloc arată, de asemenea, rețeaua ceasului în roșu și rețeaua de resetare în albastru închis.

Acest document discută fiecare dintre aceste blocuri și descrie cum să conectați ceasurile și să resetați.

Configurator MSS

Acest document se referă la anumite sub-blocuri MSS care trebuie configurate ca parte a creării unui design în care MSS se interfață cu structura FPGA prin sub-blocuri FIC. Aceste blocuri sunt evidențiate cu roșu în Figura 1-1.

Figura 1-1 • Configurator MSS

Figura 1-1 • Configurator MSS

Acțiuni SmartDesign și MSS Configurator

Există mai multe acțiuni comune la care se face referire în acest document; sunt rezumate în următoarea listă:. Dacă sunteți familiarizat cu SmartDesign și MSS, puteți sări la secțiunea următoare.

Instanțierea unui nucleu - Acțiunea de a selecta un nucleu din catalogul Libero SoC IP, de a trage și de a plasa acel nucleu pe un SmartDesign Canvas.

Configurarea unui nucleu - Acțiunea de a deschide configuratorul pentru o instanță a acelui nucleu pe Canvas, de a selecta o anumită configurație și de a o confirma făcând clic pe OK în caseta de dialog configurator. Ca urmare a acestei acțiuni, numai porturile relevante pentru configurația curentă sunt vizibile și disponibile pentru utilizare.

Instanțierea unei componente - Acțiunea de a selecta o componentă în ierarhia Libero SoC Design, tragerea și plasarea acelei componente pe o pânză SmartDesign.

Instanțarea unei componente compatibile cu AMBA personalizată – Acțiunea de a selecta o componentă HDL+ în ierarhia de design Libero SoC, tragerea și plasarea acelei componente pe un SmartDesign Canvas.

Utilizarea caracteristicii HDL+ vă permite să adăugați interfețe de magistrală (BIF) compatibile cu AMBA la modulul HDL obișnuit.

Configurarea unei componente - Acțiunea de deschidere a configuratorului pentru o componentă instanțiată pe un SmartDesign Canvas sau din Ierarhia de proiectare, selectând o anumită configurație și angajând-o făcând clic pe OK în caseta de dialog configurator. Ca rezultat al acelei acțiuni, toate instanțele de pe acea componentă din proiectul Libero SoC sunt afectate și trebuie actualizate. Când o instanță este actualizată cu cea mai recentă componentă, numai porturile relevante pentru configurația curentă sunt vizibile și disponibile pentru utilizare.

Activarea unui subbloc MSS – Unele subblocuri MSS pot fi activate sau dezactivate, indicând faptul că sunt utilizate în aplicația curentă. Toate subblocurile neutilizate ar trebui să fie dezactivate.

Configurarea unui subbloc MSS – Acțiunea de a deschide configuratorul pentru acel subbloc în configuratorul MSS, de a selecta o anumită configurație și de a o confirma făcând clic pe OK în caseta de dialog configurator, apoi salvând configurația MSS. Ca rezultat al acestor acțiuni, componenta MSS are o nouă configurație și posibil o nouă interfață de port. Când instanța MSS este actualizată cu cea mai recentă componentă, numai porturile MSS relevante pentru configurația curentă sunt vizibile și disponibile pentru utilizare.

Crearea unui subsistem fabric FPGA – Acțiunea de a instanția, configura nucleele și componentele într-un SmartDesign Canvas și de a le conecta împreună și la componenta MSS instanțiată deja în acel SmartDesign special.

Configurarea subsistemului DDR_FIC

Pentru a configura/crea un subsistem DDR_FIC, trebuie să:

- Configurați MSS MDDR pentru a expune interfața DDR_FIC

- Creați subsistemul FPGA fabric DDR_FIC, inclusiv instanțiere/configurare/conectivitate pentru:

– Autobuz AXI sau AHBLite

– Maeștri de magistrală AXI sau AHBLite

– Alți master și periferice pe autobuz, conform cerințelor aplicației dvs

– Ceasuri și resetări; consultați „Configurarea ceasurilor subsistemului FIC” la pagina 23 și „Configurarea resetarii subsistemului FIC” la pagina 27

Acești pași sunt descriși în detaliu mai jos.

Pasul 1: Configurați subblocul MSS MDDR pentru a expune interfața magistrală DDR_FIC

Interfața DDR_FIC este expusă atunci când aplicația dvs. trebuie să acceseze memoria DDR externă din materialul FPGA. În această configurație, subblocul MDDR expune interfața DDR_FIC, care este un slave AXI sau AHBLite Bus Interface (BIF) (Figura 3-1).

Figura 3-1 • Configurare MSS DDR cu acces din FPGA Fabric

Figura 3-1 • Configurare MSS DDR cu acces din FPGA Fabric

Pasul 2: Creați subsistemul FPGA Fabric DDR_FIC

Pe baza tipului de conexiune magistrală FPGA pe care l-ați selectat – AXI, Single AHBLite sau Two AHBLite – trebuie să creați un subsistem care să se potrivească cu selecția dvs.

Subsistemul DDR_FIC/AXI

- Instanciați și configurați core-ul CoreAXI IP din fereastra Catalog. Activați sloturile pe care intenționați să le utilizați pentru aplicația dvs., precum și cantitatea de memorie per slot care corespunde cerințelor dvs. de proiectare. Deoarece vă adresați unei memorie DDR externe, selecția dvs. de dimensiune a slotului ar trebui să se potrivească cu spațiul pe care intenționați să îl adresați de la FPGA fabric master. (Figura 3-2).

Figura 3-2 • Configurare CoreAXI

Figura 3-2 • Configurare CoreAXI - Instanciați și configurați nucleul sau componenta master compatibil AMBA AXI care este destinat să stăpânească pe magistrala AXI. Dacă aplicația dvs. necesită mai mult de un master pe magistrala CoreAXI, instanțiați și al doilea master.

- Conectați subsistemul:

– Conectați portul M0 (M1) al interfeței de magistrală (BIF) CoreAXI la portul BIF principal al instanțelor dumneavoastră de bază (Figura 3-3).

– Conectați portul BIF slave MSS DDR_FIC – MDDR_DDR_AXI_SLAVE – la slotul corespunzător pentru magistrala oglindă CoreAXI conform cerințelor hărții de memorie. Dacă aveți alți sclavi pe acel autobuz, conectați-i și ei, conform hărții de memorie.

– Ceasuri și resetări; consultați „Configurarea ceasurilor subsistemului FIC” la pagina 23 și „Configurarea resetarii subsistemului FIC” la pagina 27.

Figura 3-3 • Subsistemul DDR_FIC AXI

Figura 3-3 • Subsistemul DDR_FIC AXI

Subsistemul DDR_FIC/Single-AHBLite

- Creați și configurați nucleul IP CoreAHBLite din Catalog. Activați sloturile pe care intenționați să le utilizați pentru aplicația dvs., așa cum se arată în Figura 3-4. În acest exampCoreAHBLite este configurat să abordeze un spațiu de memorie RAM DDR de 4 GB folosind slotul 0 de la master M0. Deoarece vă adresați unei memorie DDR externe, selecția dvs. de dimensiune a slotului ar trebui să se potrivească cu cantitatea de spațiu de memorie DDR pe care intenționați să o adresați de la FPGA fabric master.

Figura 3-4 • Core AHBLite – Configurație Master Regiune Combinată

Figura 3-4 • Core AHBLite – Configurație Master Regiune Combinată - Instanciați și configurați nucleul sau componenta master compatibil AMBA AHBLite care este destinat să stăpânească pe magistrala CoreAHBLite. Dacă aplicația dvs. necesită mai mult de un master pe magistrala CoreAHBLite, instanțiați și masterele suplimentare. Până la patru master sunt acceptate pe magistrala CoreAHBLite.

- Conectați subsistemul:

– Conectați portul M0 (M1) de interfață de magistrală principală (BIF) CoreAHBLite la portul BIF principal al instanțelor dumneavoastră de bază principală.

– Conectați portul BIF slave MSS DDR_FIC – MDDR_DDR_AHB0_SLAVE – la slotul corespunzător coreAHBLite pentru slave în oglindă (S0 în acest example) conform cerințelor hărții de memorie. Dacă aveți alți sclavi pe acel autobuz, conectați-i la fel ca și pe harta de memorie.

– Ceasuri și resetări; consultați „Configurarea ceasurilor subsistemului FIC” la pagina 23 și „Configurarea resetarii subsistemului FIC” la pagina 27.

Figura 3-5 • Subsistem DDR_FIC AHBLite

Figura 3-5 • Subsistem DDR_FIC AHBLite

DDR_FIC/Două subsistem AHBLite

Când selectați cele două interfețe AHBLite pentru MDDR, un BIF suplimentar, MDDR_DDR_AHB1_SLAVE BIF, este expus la componenta MSS pentru a vă conecta la noul slave.

Pentru această configurație, repetați pașii pentru o singură configurație AHBLite pentru interfața BIF MDDR_DDR_AHB1_SLAVE expusă pe componenta MSS.

Deși SMC_FIC poate fi utilizat ca interfață de magistrală AXI sau AHBLite, acest document descrie doar modul de utilizare a interfeței SMC_FIC configurată în modul AXI pentru a se conecta la nucleul CoreSDR_AXI. Acest nucleu este un controler RAM SDR bazat pe AXI, utilizat pentru a conecta, în acest caz, MSS la o componentă externă de memorie SDR (Single Data Rate). Puteți deduce cu ușurință cum să utilizați interfața AHBLite din următoarea descriere; pașii sunt foarte asemănători. Interfața AXI este o interfață mai eficientă și este opțiunea preferată.

Pentru a configura/crea un subsistem SMC_FIC, trebuie să:

- Configurați MSS MDDR pentru a expune interfața SMC_FIC

- Creați subsistemul FPGA fabric DDR_FIC, inclusiv instanțiere/configurare/conectivitate pentru:

– Autobuz CoreAXI

– CoreSDR_AXI

– Alți master și periferice pe autobuz, conform cerințelor aplicației dvs

– Ceasuri și resetări; consultați „Configurarea ceasurilor subsistemului FIC” la pagina 23 și „Configurarea resetarii subsistemului FIC” la pagina 27

Acești pași sunt descriși în detaliu mai jos.

Pasul 1: Configurați subblocul MSS MDDR pentru a expune interfața magistrală SMC_FIC

Interfața SMC_FIC este expusă atunci când aplicația dvs. trebuie să acceseze o memorie SDR externă prin intermediul fabricii FPGA. În această configurație, subblocul MDDR expune interfața SMC_FIC, care este un master AXI sau AHBL Bus Interface (BIF) (Figura 4-1).

- Faceți clic dreapta pe controlerul MDDR din interiorul MSS Configurator și alegeți Configurare.

- Selectați Utilizați o interfață AXI.

- Faceți clic pe OK.

Figura 4-1 • Configurare MDDR Soft Memory Controller

Figura 4-1 • Configurare MDDR Soft Memory Controller

- Actualizați componenta MSS cu modificarea.

(Faceți clic dreapta pe Componenta MSS și alegeți Actualizare instanțe cu cea mai recentă componentă). MDDR_SMC_AXI_MASTER este expus ca un port de interfață magistrală al componentei MSS.

Pasul 2: Creați subsistemul FPGA Fabric SMC_FIC

- Creați și configurați CoreAXI astfel încât slotul master M0 să fie activat pentru slotul slave S0, așa cum se arată în Figura 4-2. Deoarece adresați o memorie externă printr-un controler de memorie soft, selectarea dimensiunii slotului ar trebui să se potrivească cu cantitatea de spațiu de memorie externă pe care intenționați să o adresați de la procesorul Cortex-M3 sau orice scriere master pe acea memorie externă prin podul MSS DDR.

Figura 4-2 • Configurare CoreAXI – Modul SMC_FIC

Figura 4-2 • Configurare CoreAXI – Modul SMC_FIC - Din Catalogul IP, instanțiați și configurați CoreSDR_AXI pentru a se potrivi cu parametrii de memorie externă.

- Conectați subsistemul (Figura 4-3):

– Conectați portul BIF master MSS SMC_FIC – MDDR_SMC_AXI_MASTER – la magistrala CoreAXI mirrored-master M0.

– Conectați portul S0 de interfață magistrală slave în oglindă CoreAXI (BIF) la portul BIF slave al instanței de bază CoreSDR_AXI.

– Ceasuri și resetări; consultați „Configurarea ceasurilor subsistemului FIC” la pagina 23 și „Configurarea resetarii subsistemului FIC” la pagina 27.

Figura 4-3 • Conexiuni la subsistem SMC_FIC

Figura 4-3 • Conexiuni la subsistem SMC_FIC

Configurarea subsistemelor FIC

Pentru a configura/crea un subsistem FIC, trebuie să:

- Configurați MSS FIC pentru a expune interfața FIC

- Creați subsistemul FIC fabric FPGA, inclusiv instanțiere/configurare/conectivitate pentru:

– magistrală APB3 sau AHBlite

– Configurare master și/sau periferice conform APB3 și AHBLite și conexiune la magistrală, conform cerințelor aplicației dvs.

– Ceasuri și resetări; consultați „Configurarea ceasurilor subsistemului FIC” la pagina 23 și „Configurarea resetarii subsistemului FIC” la pagina 27

Acești pași sunt descriși în detaliu mai jos.

Pasul 1: Configurați subblocul MSS FIC

- Invocați FIC Configurator și faceți clic dreapta pe FIC_0 sau FIC_1 pentru a deschide FIC Configurator.

- În grupul de configurare Configurator pentru MSS la FPGA Fabric Interface, selectați:

– Tipul de interfață AHBLite sau APB3

– Dacă intenționați să utilizați interfața ca maestru al fabricii FPGA

– Dacă intenționați să utilizați interfața ca un slave stăpânit de materialul FPGA (Figura 5-1)

Figura 5-1 • Opțiuni de interfață MSS la FPGA Fabric

Figura 5-1 • Opțiuni de interfață MSS la FPGA Fabric - Dacă utilizați o interfață AHBLite, puteți utiliza, de asemenea, Opțiunile avansate AHBLite pentru a selecta modul de ocolire sau pentru a expune portul ID master dacă ați selectat interfața să acționeze ca master al materialului (Figura 5-2).

Figura 5-2 • Opțiuni avansate AHBLite

Figura 5-2 • Opțiuni avansate AHBLite

Pasul 2: Creați subsistemul FPGA Fabric FIC

Pentru fiecare interfață FIC expusă – master și slave, trebuie să instanțiați o magistrală (CoreAHBLite sau CoreAPB3) care se potrivește cu tipul pe care l-ați selectat. În funcție de rolul interfeței (master/slave) și tipul (AHBLite/APB3), magistrala trebuie configurată după cum urmează:

Master/AHBLite

Instanciați și configurați magistrala CoreAHBLite după cum urmează:

- Selectați opțiunea de spațiu de memorie care corespunde cerințelor dvs.:

– Dacă aveți nevoie de mai puțin de 16 MB de spațiu de adresă pentru toate perifericele dvs., selectați opțiunea așa cum se arată în Figura 5-3. Acest mod oferă 16 sloturi de 16 MB care pot fi folosite pentru a conecta până la 16 slave AHBLite.

Figura 5-3 • Configurarea spațiului de memorie Master/AHBLite – 16 MB per slot

Figura 5-3 • Configurarea spațiului de memorie Master/AHBLite – 16 MB per slot

– Dacă aveți nevoie de mai mult de 16 MB și mai puțin de 256 MB de spațiu de adresă pentru oricare dintre perifericele dvs., selectați opțiunea așa cum se arată în Figura 5-4. Acest mod oferă 16 sloturi de 256 MB care pot fi utilizate pentru a conecta până la 16 slave AHBLite.

Figura 5-4 • Configurarea spațiului de memorie Master/AHBLite – 256 MB per slot

Figura 5-4 • Configurarea spațiului de memorie Master/AHBLite – 256 MB per slot - Activați sloturile pe care le utilizați pentru aplicația dvs. (Figura 5-5). Cea mai bună practică este să utilizați M1 pentru a accesa slotul, așa cum se arată în Figura 4-2 de la pagina 15.

Nota: Utilizați M1 dacă intenționați să creați un subsistem multi master în care aveți un master în material care necesită caracteristica de remapare și, prin urmare, trebuie conectat la M0.

– Dacă ați selectat opțiunea 16 MB per slot, nu există restricții privind sloturile care pot fi utilizate.

– Dacă ați selectat opțiunea de 256 MB per slot, pot fi utilizate numai sloturile compatibile cu selecția regiunilor de adrese de memorie fabrică a instanței FIC. Fiecare regiune de adresă de memorie FIC are o dimensiune de 256 MB. Cele șase regiuni de memorie FIC sunt rezumate în Tabelul 5-1.

Tabelul 5-1 • Adresă regiuni și sloturi compatibile pentru opțiunea de 256 MB per slot

Regiune Adresă de memorie Sloturi compatibile 30000000-3FFFFFFF 3 50000000-5FFFFFFF 5 70000000-7FFFFFFF 7 80000000-8FFFFFFF 8 90000000-9FFFFFFF 9 F0000000-FFFFFFFF 15 (F)  Figura 5-5 • Configurarea accesului Master/AHBLite Master

Figura 5-5 • Configurarea accesului Master/AHBLite Master - Creați și configurați nuclee periferice conforme cu AHBLite și/sau componente personalizate compatibile cu AHBLite.

- Conectați subsistemul:

– Conectați portul M1 de interfață magistrală (BIF) CoreAHBLite la portul BIF principal MSS – FIC_0/1_AHB_MASTER – așa cum se arată în Figura 5-6.

– Conectați slavele AHBLite la sloturile corespunzătoare, conform cerințelor hărții de memorie.

– Ceasuri și resetări; consultați „Configurarea ceasurilor subsistemului FIC” la pagina 23 și „Configurarea resetarii subsistemului FIC” la pagina 27.

Figura 5-6 • Subsistem FIC Master/AHBLite

Figura 5-6 • Subsistem FIC Master/AHBLite

Master/APB3

Instanciați și configurați magistrala CoreAPB3 după cum urmează:

- Selectați opțiunile de configurare a adresei așa cum se arată în Figura 5-7. Acest mod oferă șaisprezece sloturi de 16 MB care pot fi utilizate pentru a conecta până la șaisprezece slave compatibile APB3. Dacă aveți nevoie de sloturi cu mai multă memorie, puteți combina mai multe slave pentru a construi un slot mai mare. Consultați Ghidul utilizatorului CoreAPB3 pentru mai multe detalii despre această opțiune.

Figura 5-7 • Configurare Adresă Master/APB3

Figura 5-7 • Configurare Adresă Master/APB3 - Activați sloturile pe care le utilizați pentru aplicația dvs., așa cum se arată în Figura 5-8.

Figura 5-8 • Configurarea sloturilor Master/Sclave APB3

Figura 5-8 • Configurarea sloturilor Master/Sclave APB3 - Instanciați și configurați nuclee periferice compatibile APB3 și/sau componente personalizate compatibile APB3.

- Conectați subsistemul:

– Conectați portul CoreAPB3 de interfață magistrală (BIF) în oglindă la portul BIF principal MSS FIC_0/1_APB_MASTER – așa cum se arată în Figura 5-9.

– Conectați slave APB3 la sloturile corespunzătoare, conform cerințelor hărții de memorie.

– Ceasuri și resetări; consultați „Configurarea ceasurilor subsistemului FIC” la pagina 23 și „Configurarea resetarii subsistemului FIC” la pagina 27.

Figura 5-9 • Subsistem FIC Master/APB3

Figura 5-9 • Subsistem FIC Master/APB3

Slave/AHBLite

Nu este disponibil în acest moment.

Slave/APB3

Nu este disponibil în acest moment.

Configurarea ceasurilor subsistemului FIC

Pentru a crea configurația corespunzătoare a ceasului și conectivitate, trebuie să:

- Configurați ceasurile MSS CCC FIC

- Instanciați și configurați un nucleu CCC fabric FPGA

- Conectați rețelele de ceas pentru fiecare subsistem FIC

- Conectați portul MSS CLK_BASE la rețeaua corectă de ceas al subsistemului FIC FPGA fabric

Arhitectura SmartFusion2 impune o serie de reguli care trebuie urmate pentru ca toate subsistemele FIC să interacționeze corect între logica MSS și logica fabrică FPGA. Aceste reguli sunt definite mai jos și prezentate în Figura 6-1.

- Fiecare subsistem FIC fabric FPGA trebuie să fie condus de un ceas a cărui frecvență de ceas se potrivește cu frecvența definită, pentru acel subsistem particular, în configuratorul MSS CCC.

- Toate ceasurile subsistemului FIC fabric FPGA trebuie să fie aliniate precis; ceasurile pot fi de frecvențe diferite, dar muchiile de creștere ale ceasurilor mai lente trebuie aliniate cu muchiile de creștere ale ceasurilor cele mai rapide.

- Ceasul subsistemului FIC fabric FPGA cu cea mai mică frecvență trebuie să conducă MSS CLK_BASE.

- Dacă ceasurile fabrică sunt derivate dintr-un CCC fabric (cu PLL), ieșirea fabric CCC LOCK trebuie conectată la portul MSS_CCC_CLK_BASE_PLL_LOCK. MSS CCC Fabric Alignment Clock Circuitry (FACC) monitorizează semnalul CLK_BASE PLL LOCK pentru a garanta că CLK_BASE este stabil înainte de a trece de la ceasul de așteptare (ceasul utilizat în timpul pornirii dispozitivului) la ceasul configurat de utilizator derivat din CLK_BASE.

Figura 6-1 • Reguli de ceas subsistem

Figura 6-1 • Reguli de ceas subsistem

Urmați pașii de mai jos pentru a configura rețelele de ceas pentru toate subsistemele dumneavoastră FIC.

Pasul 1: Configurați subblocul MSS CCC

Pentru fiecare bloc FIC (FIC_0, FIC_1 și DDR_FIC/SMC_FIC) utilizat în proiectarea dvs., selectați divizorii de ceas în MSS Clock Configurator (MSS_CCC), așa cum se arată în Figura 6-2. Figura 6-2 • Configurarea ceasului MSS CCC FIC

Figura 6-2 • Configurarea ceasului MSS CCC FIC

Nota că câmpul CLK_BASE nu este editabil. Frecvența CLK_BASE, așa cum este impusă de arhitectura SmartFusion2, trebuie să fie frecvența minimă a tuturor frecvențelor de ceas FIC și este calculată automat de configuratorul MSS CCC. Consultați „Pasul 3: Conectați rețelele de ceas subsisteme FPGA Fabric FIC” la pagina 25 pentru mai multe detalii despre configurarea CLK_BASE.

Pasul 2: Configurați ceasurile FPGA Fabric FIC

Instanciați un CCC fabric (cu PLL) și configurați-l pentru a satisface regulile de ceas al subsistemului FIC descrise la pagina 23. De obicei, trebuie să asociați o ieșire globală (GLx) pentru fiecare dintre ceasurile FIC, specificați pentru fiecare ieșire frecvența acestuia ( potrivirea frecvențelor definite în MSS CCC) și au toate ieșirile globale derivate din ieșirea PLL pentru a garanta alinierea de fază (așa cum se arată în Figura 6-3).

Nota: Dacă două subsisteme FIC au aceleași frecvențe, nu trebuie să generați două ieșiri globale independente din CCC fabric; unul este suficient. Figura 6-3 • Fabric CCC cu PLL

Figura 6-3 • Fabric CCC cu PLL

Pasul 3: Conectați ceasul subsistemelor FPGA Fabric FIC Rețele

Conectați fiecare ieșire globală CCC fabrică GLx la subsistemul FIC cu care este asociat.

Pasul 4: Conectați portul MSS CLK_BASE

Conectați cel mai lent de ieșire globală CCC GLx la portul MSS CLK_BASE.

Pasul 5: Conectați portul MSS MCCC_CLK_BASE_PLL_LOCK

Conectați ieșirea fabric CCC LOCK la portul MSS MCCC_CLK_BASE_PLL_LOCK.

Cerințe de analiză a timpului

Efectuați o analiză de sincronizare statică post-aspect pentru a vă asigura că designul îndeplinește cerințele de sincronizare definite în configuratorii CCC fabric MSS CCC și FPGA. Este posibil să trebuiască să schimbați M3_CLK sau să creșteți raportul de ceas dintre MSS și material pentru a obține un design care să treacă de analiza statică a timpului.

Configurarea resetarii subsistemului FIC

Pentru a configura resetarea subsistemului FIC:

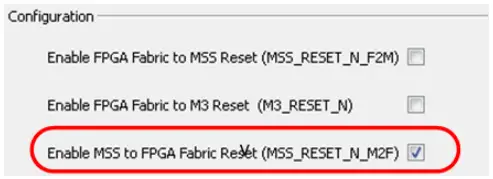

- Din configuratorul MSS, configurați subblocul MSS Reset pentru a expune portul MSS_RESET_N_M2F.

Figura 7-1 • Configurați subblocul MSS Reset

Figura 7-1 • Configurați subblocul MSS Reset - Conectați portul MSS_RESET_N_M2F la toate porturile de resetare a subsistemelor FIC fabric FPGA.

Configurarea hărții memoriei de sistem

Fiecare periferic (sclavi AMBA AXI, AHBLite și APB3) este identificat printr-o adresă de la punctul master al subsistemului FIC. view. De obicei, ne referim la relațiile generale dintre master și slave ale unui subsistem ca harta de memorie a acelui subsistem. Harta de memorie a unui subsistem poate fi editată în SmartDesign. Poti de asemenea view harta de memorie finală a sistemului dvs. atunci când generați întregul sistem. Harta memoriei face parte din fișa de date generată pentru „rădăcina” designului dvs. după generare.

Configurarea hărții de memorie (comportament general SmartDesign)

În SmartDesign, unui periferic i se atribuie o adresă pe o magistrală pe baza adresei de bază a acelei magistrale din subsistem plus numărul slotului de pe acea magistrală înmulțit cu dimensiunea slotului. Deci, schimbarea numărului slotului pentru un periferic afectează adresa acestuia în consecință. Modificarea alocării slotului pentru un periferic se poate face prin conectarea manuală a BIF slave al perifericului la un anumit BIF slave în oglindă de magistrală (slot) folosind instrumentele de conectivitate SmartDesign disponibile în Canvas. Acest lucru se poate face și prin editarea hărții de memorie utilizând Modificarea hărții de memorie, așa cum se arată în Figura 8-1. Figura 8-1 • Modificați harta memoriei din SmartDesign Canvas

Figura 8-1 • Modificați harta memoriei din SmartDesign Canvas

Apare caseta de dialog Modificare hartă memorie (Figura 8-2). Figura 8-2 • Caseta de dialog Modificare hartă memorie

Figura 8-2 • Caseta de dialog Modificare hartă memorie

Configurarea regiunilor de memorie pentru interfețele FIC (MSS Master View)

Există șase regiuni de 256 MB definite ca regiuni FIC de la 0 la 5 în harta memoriei MSS. Fiecare dintre aceste regiuni poate fi alocată interfețelor slave FIC_0 sau FIC_1 într-un mod care se exclude reciproc. Puteți selecta cărei interfețe slave FIC (0 sau 1) alocați acele regiuni utilizând butonul radio de lângă fiecare regiune din FPGA Fabric Address Regions (MSS Master View) caseta de grup (Figura 8-3).  Figura 8-3 • Regiunile FPGA Fabric Address (MSS Master View)

Figura 8-3 • Regiunile FPGA Fabric Address (MSS Master View)

Formula generală de calcul al hărții de memorie

Adresele de bază posibile pentru interfețele fabricii FIC sunt 0x30000000, 0x50000000, 0x70000000, 0x80000000, 0x90000000 și 0xF0000000. Vedeți „Configurarea subsistemelor FIC” la pagina 17 pentru detalii despre cum să configurați fiecare instanță FIC pentru a mapa la aceste adrese.

Pentru AHBLite, dimensiunea slotului poate fi fie de 16 MB (0x01000000) fie de 256 MB (0x10000000).

Când utilizați 16 MB per slot, pot fi utilizate toate sloturile de la 0 la 16; adresa perifericei clientului poate fi calculată ca adresa de bază a regiunii de memorie FIC + (număr slot * 0x01000000). În această configurație, toate regiunile sunt de fapt alias-uri una de cealaltă, deoarece miezul AHBLite nu decodifică biții de adresă [31:28]; sloturile sunt decodate folosind biți de adresă [27:24].

Când utilizați 256 MB per slot, pot fi utilizate numai sloturile 3, 5, 7, 8, 9 și F; adresa perifericei clientului poate fi calculată ca adresa de bază a regiunii de memorie FIC + (număr slot * 0x10000000). În această configurație, toate regiunile se adresează în mod unic sloturilor diferite, deoarece miezul AHBLite decodifică sloturile folosind biți de adresă [31:28]. În această configurație, pentru a simplifica ecuația hărții de memorie, adresa de bază este 0x00000000, în loc de una dintre cele șase adrese fixe definite mai sus.

Example 1 (configurație slot de 16 MB):

Folosind regiunea de memorie 0x50000000, dacă perifericul se află la slotul numărul 7, atunci adresa sa este: 0x50000000 + (0x7 * 0x01000000) = 0x57000000

Example 2 (configurație slot de 256 MB):

Folosind regiunea de memorie 0x50000000, dacă perifericul se află la slotul numărul 15, atunci adresa sa este: 0x00000000 + (0xF * 0x10000000) = 0xF0000000

Viewla Harta memoriei finale

În acest moment, Libero SoC nu generează o hartă de memorie corectă pentru sistemele care utilizează SmartFusion2 MSS.

Suport pentru produse

Microsemi SoC Products Group își susține produsele cu diverse servicii de asistență, inclusiv Serviciul Clienți, Centrul de asistență tehnică pentru clienți, un website, poștă electronică și birouri de vânzări la nivel mondial. Această anexă conține informații despre contactarea Microsemi SoC Products Group și utilizarea acestor servicii de asistență.

Serviciu clienți

Contactați Serviciul Clienți pentru asistență non-tehnică pentru produse, cum ar fi prețul produselor, upgrade-uri ale produsului, informații de actualizare, starea comenzii și autorizare.

Din America de Nord, sunați 800.262.1060

Din restul lumii, sunați 650.318.4460

Fax, de oriunde în lume, 408.643.6913

Centrul de suport tehnic pentru clienți

Microsemi SoC Products Group pune la dispoziție Centrul de asistență tehnică pentru clienți cu ingineri de înaltă calificare care vă pot ajuta să vă răspundă la întrebările dvs. legate de hardware, software și design despre produsele Microsemi SoC. Centrul de asistență tehnică pentru clienți petrece mult timp creând note de aplicație, răspunsuri la întrebări obișnuite ale ciclului de proiectare, documentare a problemelor cunoscute și diverse întrebări frecvente. Prin urmare, înainte de a ne contacta, vă rugăm să vizitați resursele noastre online. Este foarte probabil să ți-am răspuns deja la întrebări.

Suport tehnic

Vizitați Serviciul pentru clienți website (www.microsemi.com/soc/support/search/default.aspx) pentru mai multe informații și asistență. Multe răspunsuri disponibile pe căutare web resursele includ diagrame, ilustrații și link-uri către alte resurse de pe website-ul.

Website-ul

Puteți răsfoi o varietate de informații tehnice și non-tehnice pe pagina de pornire SoC, la www.microsemi.com/soc.

Contactarea Centrului de asistență tehnică pentru clienți

Ingineri cu înaltă calificare personalizează Centrul de asistență tehnică. Centrul de asistență tehnică poate fi contactat prin e-mail sau prin Microsemi SoC Products Group website-ul.

E-mail

Puteți comunica întrebările dumneavoastră tehnice la adresa noastră de e-mail și puteți primi răspunsuri prin e-mail, fax sau telefon. De asemenea, dacă aveți probleme de design, vă puteți trimite prin e-mail designul files pentru a primi asistență. Monitorizăm constant contul de e-mail pe tot parcursul zilei. Când ne trimiteți cererea dvs., vă rugăm să vă asigurați că includeți numele dvs. complet, numele companiei și informațiile dvs. de contact pentru procesarea eficientă a cererii dvs.

Adresa de e-mail a suportului tehnic este soc_tech@microsemi.com.

Cazurile mele

Clienții Microsemi SoC Products Group pot trimite și urmări cazuri tehnice online, accesând Cazurile mele.

În afara SUA

Clienții care au nevoie de asistență în afara fusurilor orare ale SUA pot contacta fie asistența tehnică prin e-mail (soc_tech@microsemi.com) sau contactați un birou local de vânzări. Listările birourilor de vânzări pot fi găsite la www.microsemi.com/soc/company/contact/default.aspx.

Suport tehnic ITAR

Pentru asistență tehnică pentru FPGA RH și RT care sunt reglementate de reglementările internaționale privind traficul de arme (ITAR), contactați-ne prin soc_tech_itar@microsemi.com. Ca alternativă, în Cazurile mele, selectați Da în lista derulantă ITAR. Pentru o listă completă a Microsemi FPGA reglementate de ITAR, vizitați ITAR web pagină.

Microsemi Corporation (NASDAQ: MSCC) oferă un portofoliu cuprinzător de semiconductori solutii pentru: aerospațial, apărare și securitate; întreprinderi și comunicații; și piețele de energie industrială și alternativă. Produsele includ dispozitive analogice și RF de înaltă performanță, de înaltă fiabilitate, circuite integrate de semnal mixt și RF, SoC-uri personalizabile, FPGA-uri și subsisteme complete. Microsemi are sediul în Aliso Viejo, California. Aflați mai multe la www.microsemi.com.

© 2014 Microsemi Corporation. Toate drepturile rezervate. Microsemi și sigla Microsemi sunt mărci comerciale ale Microsemi Corporation. Toate celelalte mărci comerciale și mărci de servicii sunt proprietatea deținătorilor respectivi.

5-02-00370-1/08.14

Sediul Microsemi Corporate

Sediul Microsemi Corporate

One Enterprise, Aliso Viejo CA 92656 SUA

În SUA: +1 949-380-6100

Vânzări: +1 949-380-6136

Fax: +1 949-215-4996

Documente/Resurse

|

Microsemi SmartFusion2 MSS Crearea unui design [pdfGhid de utilizare SmartFusion2 MSS Crearea unui design |