SmartFusion 2 MSS

SmartFusion 2 MSS

Tsim ib qho Tsim Siv MSS Fabric Interfaces

Cov neeg siv phau ntawv qhia

Taw qhia

Lub SmartFusion2 Microcontroller Sub-System (MSS) muaj plaub qhov sib txawv Fabric Interface Controllers (FIC):

- DDR_FIC

- SMC_FIC

- FIC_0 thiab FIC_1, nyob ntawm koj lub cuab yeej

Cov kev cuam tshuam cuam tshuam no ua rau MSS cuam tshuam nrog cov logic siv hauv FPGA ntaub thiab lwm yam

ua versa.

DDR_FIC yog siv thaum koj teeb tsa MSS DDR thaiv (MDDR) xws li cov DDR sab nraud

nco tuaj yeem nkag tau los ntawm FPGA npuag tus tswv ntawm AXI interface lossis 2 AHBLite AMBA interfaces.

SMC_FIC yog siv thaum koj teeb tsa MSS DDR Block nyob rau hauv Ib Hnub Tus Nqi (SDR) hom. Hauv qhov kev teeb tsa no, MSS nkag mus rau sab nraud Ib Leeg Cov Ntaub Ntawv Rate DRAM lossis Asynchronous nco los ntawm lub cim xeeb muag muag tam sim hauv FPGA ntaub, xws li CoreSDR_AXI. SMC_FIC yog AXI lossis AHBLite qhev AMBA interface. DDR_FIC thiab SMC_FIC interfaces yog sib koom ua ke; tsuas yog ib qho ua haujlwm ntawm ib lub sijhawm.

FIC interfaces pab koj kom txuas ntxiv MSS AMBA Bus rau hauv FPGA ntaub. Muaj txog li ob qhov FIC ib zaug hauv MSS nyob ntawm cov khoom xaiv. Thawj qhov piv txwv yog lub npe FIC_0 (uas muaj nyob hauv txhua lub cuab yeej) thiab qhov thib ob yog lub npe FIC_1 (tej zaum yuav tsis muaj nyob hauv cov khoom siv me). Koj tuaj yeem teeb tsa FIC raws li APB3 lossis AHBLite AMBA interface nyob ntawm koj qhov kev xav tau tsim. Nyob rau hauv txhua hom, tus tswv thiab ib tug qhev npav interface muaj. Ntawd yog, tus tswv hauv cov ntaub tuaj yeem cuam tshuam rau tus qhev hauv MSS thiab tus tswv hauv MSS tuaj yeem cuam tshuam rau tus qhev hauv ntaub.

Txhua Fabric Interface sub-system tuaj yeem ua haujlwm ntawm lub sijhawm sib txawv, txhais raws li qhov piv ntawm MSS lub ntsiab moos M3_CLK.

Lub SmartFusion2 architecture tsim cov cai muaj feem xyuam rau clocking domains ntawm Fabric Interfaces thiab FPGA Fabric. Cov ntaub ntawv no muab cov lus qhia txog yuav ua li cas thiaj tsim tau cov tshuab zoo li no.

Qib Siab View

Daim duab 1 thiab daim duab 2 qhia tias MSS txuas mus rau FPGA ntaub li cas ntawm ntau yam Fabric Interface Controllers (FIC). Daim duab 1 qhia txog daim duab thaiv tag nrho thaum DDR_FIC siv (sab nraud DDR nco) thiab daim duab 2 qhia daim duab thaiv rau thaum SMC_FIC siv (sab nraud SDR nco).

Cov duab kos qhia MSS sub-blocks tseem ceeb rau kev txuas MSS rau FPGA ntaub. FIC sub-block yuav lossis tsis siv hauv koj daim ntawv thov. Koj kuj yuav tsis siv DDR_FIC lossis SMC_FIC interfaces hauv koj tus qauv tsim. Txawm li cas los xij, qhov no tsis hloov tag nrho cov kev xav tau ntawm yuav ua li cas los tsim ib qho kev tsim nrog ib lossis ntau FIC thaiv siv hauv kev tsim.

Daim duab 1 • MSS rau FPGA Fabric Block Diagram – DDR_FIC hom

Daim duab 1 • MSS rau FPGA Fabric Block Diagram – DDR_FIC hom  Daim duab 2 • MSS rau FPGA Fabric Block Diagram – SMC_FIC hom

Daim duab 2 • MSS rau FPGA Fabric Block Diagram – SMC_FIC hom

MSS muaj:

- AHB_Bus matrix; tag nrho cov kev pauv hauv MSS mus dhau qhov thaiv no.

- DDR Controller - cuam tshuam nrog DDR_FIC.

- DDR_FIC (SMC_FIC) sub-block (siv yog tias koj qhib FPGA ntaub rau DDR txoj hauv MSS_MDDR configurator).

- FIC_0 sub-block.

- FIC_1 sub-block (hauv cov khoom siv loj dua nkaus xwb).

- FIC_2 sub-block (rau APB pib ntawm SERDES thiab sab nraud DDRs).

- MSS_CCC sub-block xav tau los teeb tsa FIC moos txheeb ze rau MSS lub ntsiab moos (M3_CLK).

- MSS_RESET sub-block uas tsim cov MSS sab hauv rov pib dua nrog rau MSS_RESET_N_M2F teeb liab uas tsav FPGA ntaub.

FPGA ntaub muaj:

- Peb FIC sub-systems (DDR_FIC, FIC_0 thiab FIC_1).

- Npuag CCC - FAB_CCC - yuav tsum tau tsim cov moos uas tsav FPGA ntaub FIC subsystem nrog rau MCCC_CLK_BASE chaw nres nkoj ntawm MSS thaiv.

- FAB_CCC siv lub moos teeb liab - tuaj yeem yog ib qho ntawm cov khoom siv hluav taws xob, ib qho siv lead ua oscillator sab nraud, lub moos tsim tawm sab hauv rau cov ntaub lossis los ntawm sab nraum lub nti.

Daim duab thaiv kuj qhia lub moos network hauv liab thiab rov pib dua lub network hauv xiav tsaus.

Cov ntaub ntawv no tham txog txhua qhov blocks no thiab piav qhia yuav ua li cas txuas cov moos thiab rov pib dua.

MSS Configurator

Cov ntaub ntawv no hais txog qee qhov MSS sub-blocks uas yuav tsum tau teeb tsa ua ib feem ntawm kev tsim qauv uas MSS cuam tshuam rau FPGA ntaub ntawm FIC sub-blocks. Cov blocks no tseem ceeb rau hauv liab hauv daim duab 1-1.

Daim duab 1-1 • MSS Configurator

Daim duab 1-1 • MSS Configurator

SmartDesign thiab MSS Configurator Ua Haujlwm

Muaj ntau ntau yam ua tau hais txog hauv daim ntawv no; lawv tau sau tseg hauv cov npe hauv qab no:. Yog tias koj paub txog SmartDesign thiab MSS koj tuaj yeem hla mus rau ntu tom ntej.

Instantiating ib tug core - Qhov kev txiav txim ntawm kev xaiv cov tub ntxhais kawm los ntawm Libero SoC IP catalog, rub thiab xa cov tub ntxhais mus rau SmartDesign Canvas.

Configuring ib core - Qhov kev txiav txim ntawm qhib lub configurator rau ib qho piv txwv ntawm cov tub ntxhais ntawm Canvas, xaiv ib qho kev teeb tsa tshwj xeeb thiab ua nws los ntawm nias OK nyob rau hauv lub configurator dialog box. Raws li qhov tshwm sim ntawm qhov kev txiav txim, tsuas yog cov chaw nres nkoj cuam tshuam rau qhov kev teeb tsa tam sim no pom thiab muaj rau siv.

Instantiating ib feem - Qhov kev txiav txim ntawm kev xaiv ib feem hauv Libero SoC Design Hierarchy, rub thiab xa cov khoom ntawd mus rau hauv SmartDesign canvas.

Instantiating ib qho kev cai AMBA raws li kev tivthaiv - Qhov kev txiav txim ntawm kev xaiv HDL + tivthaiv hauv Libero SoC Design Hierarchy, rub thiab xa cov khoom ntawd mus rau SmartDesign Canvas.

Siv HDL + feature ua rau koj ntxiv AMBA raws li Bus Interfaces (BIFs) rau koj li HDL module.

Configuring ib feem - Qhov kev txiav txim ntawm qhib lub configurator rau ib feem instantiated ntawm ib tug SmartDesign Canvas los yog los ntawm tus tsim Hierarchy, xaiv ib tug tshwj xeeb configuration thiab ua nws los ntawm txhaj OK nyob rau hauv lub configurator dialog box. Raws li qhov tshwm sim ntawm qhov kev txiav txim, txhua qhov xwm txheej ntawm cov khoom ntawd hauv Libero SoC qhov project raug cuam tshuam thiab yuav tsum tau hloov kho. Thaum ib qho piv txwv tau hloov kho nrog cov khoom siv tshiab, tsuas yog cov chaw nres nkoj cuam tshuam rau qhov kev teeb tsa tam sim no pom thiab muaj rau siv.

Enabling MSS sub-block - Qee qhov MSS sub-blocks tuaj yeem qhib lossis xiam oob qhab, qhia tias lawv tau siv hauv daim ntawv thov tam sim no. Tag nrho cov sub-blocks uas tsis tau siv yuav tsum raug kaw.

Configuring MSS sub-block - Qhov kev txiav txim ntawm kev qhib lub configurator rau qhov sub-block hauv MSS configurator, xaiv ib qho kev teeb tsa tshwj xeeb thiab ua nws los ntawm nias OK nyob rau hauv lub configurator dialog box, ces txuag lub MSS configuration. Raws li qhov tshwm sim ntawm cov kev ua no, MSS tivthaiv muaj kev teeb tsa tshiab thiab muaj peev xwm muaj qhov chaw nres nkoj tshiab. Thaum qhov piv txwv ntawm MSS tau hloov kho nrog qhov tseeb tivthaiv, tsuas yog MSS cov chaw nres nkoj cuam tshuam rau qhov kev teeb tsa tam sim no pom thiab muaj rau siv.

Tsim FPGA ntaub sub-system - Qhov kev txiav txim ntawm instantiating, configuring cores thiab Cheebtsam nyob rau hauv ib tug SmartDesign Canvas thiab txuas lawv ua ke thiab mus rau lub MSS tivthaiv instantiated twb nyob rau hauv uas tshwj xeeb SmartDesign.

Configuring DDR_FIC Sub-System

Txhawm rau teeb tsa / tsim DDR_FIC sub-system, koj yuav tsum:

- Configure MSS MDDR kom nthuav tawm DDR_FIC interface

- Tsim cov FPGA ntaub DDR_FIC sub-system nrog rau instantiation/configuration/connectivity rau:

- AXI lossis AHBLite npav

- AXI lossis AHBLite npav tus tswv

- Lwm tus tswv thiab cov khoom siv hauv lub tsheb npav raws li koj daim ntawv thov

- moos thiab rov pib dua; xa mus rau “Configuring the FIC Sub-System Clocks” ntawm nplooj 23 thiab “Configuring the FIC Sub-System Reset” ntawm nplooj 27

Cov kauj ruam no tau piav qhia hauv qab no.

Kauj Ruam 1: Txhim kho MSS MDDR Sub-block kom nthuav tawm DDR_FIC Bus Interface

DDR_FIC interface raug nthuav tawm thaum koj daim ntawv thov xav tau nkag mus rau sab nraud DDR nco los ntawm FPGA ntaub. Hauv qhov kev teeb tsa no, MDDR sub-block nthuav tawm DDR_FIC interface, uas yog qhev AXI lossis AHBLite Bus Interface (BIF) (Daim duab 3-1).

Daim duab 3-1 • MSS DDR Configuration nrog Access los ntawm FPGA Fabric

Daim duab 3-1 • MSS DDR Configuration nrog Access los ntawm FPGA Fabric

Kauj ruam 2: Tsim FPGA Fabric DDR_FIC Sub-System

Raws li hom kev sib txuas ntawm FPGA tsheb npav uas koj xaiv - AXI, Ib Leeg AHBLite lossis Ob AHBLite - koj yuav tsum tsim cov kab ke uas haum rau koj xaiv.

DDR_FIC/AXI Sub-System

- Instantiate thiab teeb tsa CoreAXI IP core los ntawm Catalog qhov rai. Pab kom cov slots uas koj npaj yuav siv rau koj daim ntawv thov nrog rau tus nqi ntawm lub cim xeeb ntawm ib lub qhov uas phim koj cov kev xav tau tsim. Txij li thaum koj tab tom hais txog lub cim xeeb sab nraud DDR, koj qhov kev xaiv qhov loj me yuav tsum phim qhov chaw uas koj npaj yuav hais los ntawm FPGA npuag tus tswv. (Daim duab 3-2).

Daim duab 3-2 • CoreAXI Configuration

Daim duab 3-2 • CoreAXI Configuration - Instantiate thiab configure lub AMBA AXI-raws li tus tswv core los yog cov khoom uas yog npaj los ua tswv rau lub tsheb npav AXI. Yog tias koj daim ntawv thov xav tau ntau tshaj ib tus tswv rau ntawm lub npav CoreAXI, ua kom tus tswv thib ob thiab.

- Txuas lub sub-system:

- Txuas CoreAXI mirrored-master Bus Interface (BIF) chaw nres nkoj M0 (M1) mus rau tus tswv BIF chaw nres nkoj ntawm koj tus tswv core piv txwv (Daim duab 3-3).

- Txuas MSS DDR_FIC qhev BIF chaw nres nkoj - MDDR_DDR_AXI_SLAVE - mus rau qhov zoo CoreAXI tsheb npav mirrored- qhev qhov raws li koj xav tau daim ntawv qhia kev nco. Yog tias koj muaj lwm tus qhev ntawm lub npav, txuas rau lawv, raws li koj daim ntawv qhia nco.

- moos thiab rov pib dua; xa mus rau “Configuring the FIC Sub-System Clocks” nyob rau nplooj 23 thiab “Configuring the FIC Sub-System Reset” ntawm nplooj 27.

Daim duab 3-3 • DDR_FIC AXI Sub-System

Daim duab 3-3 • DDR_FIC AXI Sub-System

DDR_FIC/Single-AHBLite sub-system

- Instantiate thiab teeb tsa CoreAHBLite IP core los ntawm Catalog. Qhib cov slots uas koj npaj yuav siv rau koj daim ntawv thov raws li qhia hauv daim duab 3-4. Hauv no example, CoreAHBLite tau teeb tsa los hais txog ib qho 4GB ntawm DDR RAM nco qhov chaw siv slot0 los ntawm tus tswv M0. Txij li thaum koj tab tom hais txog lub cim xeeb sab nraud DDR, koj qhov kev xaiv qhov loj me yuav tsum phim qhov DDR nco qhov chaw uas koj npaj yuav hais los ntawm FPGA npuag tus tswv.

Daim duab 3-4 • Core AHBLite – Combined Region Master Configuration

Daim duab 3-4 • Core AHBLite – Combined Region Master Configuration - Instantiate thiab configure AMBA AHBLite raws li tus tswv core lossis cov khoom uas yog npaj los ua tus tswv rau lub npav CoreAHBLite. Yog tias koj daim ntawv thov xav tau ntau tshaj ib tus tswv rau lub npav CoreAHBLite, ua kom cov masters ntxiv ib yam nkaus. Txog li plaub tus tswv tau txais kev txhawb nqa ntawm lub npav CoreAHBLite.

- Txuas lub sub-system:

- Txuas CoreAHBLite mirrored-master Bus Interface (BIF) chaw nres nkoj M0 (M1) mus rau tus tswv BIF chaw nres nkoj ntawm koj tus tswv core piv txwv.

- Txuas MSS DDR_FIC qhev BIF chaw nres nkoj - MDDR_DDR_AHB0_SLAVE - mus rau qhov zoo CoreAHBLite tsheb npav mirrored- qhev qhov (S0 hauv qhov example) raws li koj daim ntawv qhia nco tau. Yog tias koj muaj lwm tus qhev ntawm lub npav, txuas lawv nrog rau koj daim ntawv qhia nco.

- moos thiab rov pib dua; xa mus rau “Configuring the FIC Sub-System Clocks” nyob rau nplooj 23 thiab “Configuring the FIC Sub-System Reset” ntawm nplooj 27.

Daim duab 3-5 • DDR_FIC AHBLite Sub-System

Daim duab 3-5 • DDR_FIC AHBLite Sub-System

DDR_FIC/Ob AHBLite Sub-System

Thaum koj xaiv ob qhov kev xaiv AHBLite Interfaces rau MDDR, ib qho ntxiv BIF, MDDR_DDR_AHB1_SLAVE BIF, raug nthuav tawm ntawm MSS tivthaiv rau koj txuas mus rau tus qhev tshiab.

Rau qhov kev teeb tsa no, rov ua cov kauj ruam rau ib qho AHBLite configuration rau MDDR_DDR_AHB1_SLAVE BIF Interface nthuav tawm ntawm MSS tivthaiv.

Txawm hais tias SMC_FIC tuaj yeem siv los ua AXI lossis AHBLite tsheb npav interface, daim ntawv no tsuas yog piav qhia yuav ua li cas siv SMC_FIC interface teeb tsa hauv AXI hom los txuas rau CoreSDR_AXI core. Cov tub ntxhais ntawd yog AXI-raws li SDR RAM maub los siv los txuas, hauv qhov no, MSS mus rau lwm qhov Ib Leeg Cov Ntaub Ntawv Rate (SDR) lub cim xeeb. Koj tuaj yeem yooj yim infer yuav ua li cas siv AHBLite interface los ntawm cov lus piav qhia hauv qab no; cov kauj ruam zoo sib xws. AXI interface yog ib qho kev sib cuam tshuam zoo dua thiab yog qhov kev xaiv zoo dua.

Txhawm rau teeb tsa / tsim SMC_FIC sub-system, koj yuav tsum:

- Configure MSS MDDR kom nthuav tawm SMC_FIC interface

- Tsim FPGA ntaub DDR_FIC sub-system, suav nrog instantiation/configuration/connectivity rau:

- CoreAXI tsheb npav

- CoreSDR_AXI

- Lwm tus tswv thiab cov khoom siv hauv lub tsheb npav raws li koj daim ntawv thov

- moos thiab rov pib dua; xa mus rau “Configuring the FIC Sub-System Clocks” ntawm nplooj 23 thiab “Configuring the FIC Sub-System Reset” ntawm nplooj 27

Cov kauj ruam no tau piav qhia hauv qab no.

Kauj Ruam 1: Txhim kho MSS MDDR Sub-block kom nthuav tawm SMC_FIC Bus Interface

SMC_FIC interface raug nthuav tawm thaum koj daim ntawv thov xav tau nkag mus rau sab nraud SDR nco los ntawm FPGA ntaub. Hauv qhov kev teeb tsa no, MDDR sub-block nthuav tawm SMC_FIC interface, uas yog tus tswv AXI lossis AHBL Bus Interface (BIF) (Daim duab 4-1).

- Right-click lub MDDR Controller hauv MSS Configurator thiab xaiv Configure.

- Xaiv Siv AXI Interface.

- Nyem OK.

Daim duab 4-1 • MDDR Soft Memory Controller Configuration

Daim duab 4-1 • MDDR Soft Memory Controller Configuration

- Hloov kho MSS tivthaiv nrog kev hloov.

(Right-click the MSS Component thiab xaiv Hloov Kho Cov Txheej Txheem nrog Cov Cheeb Tsam Kawg). Lub MDDR_SMC_AXI_MASTER raug nthuav tawm raws li Bus Interface Chaw nres nkoj ntawm MSS tivthaiv.

Kauj ruam 2: Tsim FPGA Fabric SMC_FIC Sub-System

- Instantiate thiab configure CoreAXI xws li tus tswv qhov M0 yog enabled rau tus qhev qhov S0, raws li qhia nyob rau hauv daim duab 4-2. Txij li thaum koj tab tom hais txog lub cim xeeb sab nraud los ntawm tus tswj hwm lub cim xeeb muag, koj qhov kev xaiv qhov loj me yuav tsum sib npaug ntawm qhov chaw nco sab nraud uas koj npaj yuav hais los ntawm Cortex-M3 processor lossis ib tus tswv sau ntawv rau lub cim xeeb sab nraud ntawm MSS DDR choj.

Daim duab 4-2 • CoreAXI Configuration – SMC_FIC hom

Daim duab 4-2 • CoreAXI Configuration – SMC_FIC hom - Los ntawm IP Catalog, instantiate thiab configure CoreSDR_AXI kom phim koj lub cim xeeb sab nraud.

- Txuas lub sub-system (Daim duab 4-3):

- Txuas MSS SMC_FIC tus tswv BIF chaw nres nkoj - MDDR_SMC_AXI_MASTER - mus rau CoreAXI tsheb npav mirrored-master M0.

- Txuas CoreAXI mirrored-slave Bus Interface (BIF) chaw nres nkoj S0 mus rau qhev BIF chaw nres nkoj ntawm CoreSDR_AXI core piv txwv.

- moos thiab rov pib dua; xa mus rau “Configuring the FIC Sub-System Clocks” nyob rau nplooj 23 thiab “Configuring the FIC Sub-System Reset” ntawm nplooj 27.

Daim duab 4-3 • SMC_FIC Sub-System Connections

Daim duab 4-3 • SMC_FIC Sub-System Connections

Configuring FIC Sub-Systems

Txhawm rau teeb tsa / tsim FIC sub-system, koj yuav tsum:

- Configure MSS FIC kom nthuav tawm FIC interface

- Tsim cov FPGA ntaub FIC sub-system nrog rau instantiation/configuration/connectivity rau:

- APB3 lossis AHBLite npav

- APB3 thiab AHBLite ua raws tus tswv thiab / lossis cov khoom siv txuas ntxiv thiab txuas rau lub tsheb npav raws li koj daim ntawv thov

- moos thiab rov pib dua; xa mus rau “Configuring the FIC Sub-System Clocks” ntawm nplooj 23 thiab “Configuring the FIC Sub-System Reset” ntawm nplooj 27

Cov kauj ruam no tau piav qhia hauv qab no.

Kauj ruam 1: Configure MSS FIC Sub-Block

- Hu rau FIC Configurator thiab right-click ntawm FIC_0 lossis FIC_1 los qhib FIC Configurator.

- Hauv Configurator rau MSS rau FPGA Fabric Interface configuration pab pawg xaiv:

- Hom AHBLite lossis APB3 interface

- Txawm hais tias koj npaj siab yuav siv lub interface ua tus tswv ntawm FPGA ntaub

- Txawm hais tias koj npaj siab yuav siv qhov sib cuam tshuam ua qhev mastered los ntawm FPGA ntaub (Daim duab 5-1)

Daim duab 5-1 • MSS rau FPGA Fabric Interface Options

Daim duab 5-1 • MSS rau FPGA Fabric Interface Options - Yog tias koj siv AHBLite Interface koj tuaj yeem siv AHBLite Advanced Options los xaiv hom bypass, lossis nthuav tawm tus tswv ID chaw nres nkoj yog tias koj xaiv qhov interface los ua tus tswv ntawm cov ntaub (Daim duab 5-2).

Daim duab 5-2 • Advanced AHBLite Options

Daim duab 5-2 • Advanced AHBLite Options

Kauj ruam 2: Tsim FPGA Fabric FIC Sub-System

Rau txhua qhov FIC interface raug nthuav tawm - tus tswv thiab qhev, koj yuav tsum ua kom lub tsheb npav (CoreAHBLite lossis CoreAPB3) uas phim hom koj xaiv. Nyob ntawm lub luag haujlwm interface (tus tswv / qhev) thiab hom (AHBLite / APB3), lub npav yuav tsum tau teeb tsa raws li hauv qab no:

Master/AHBLite

Instantiate thiab teeb tsa lub npav CoreAHBLite raws li hauv qab no:

- Xaiv qhov kev xaiv Memory Space uas phim koj cov kev xav tau:

- Yog tias koj xav tau tsawg dua 16 MB ntawm qhov chaw nyob ntawm tag nrho koj cov khoom siv, xaiv qhov kev xaiv raws li qhia hauv daim duab 5-3. Hom no muab 16 16MB slots uas tuaj yeem siv los txuas mus txog 16 AHBLite qhev.

Daim duab 5-3 • Master/AHBLite Memory Space Configuration – 16 MB ib qhov

Daim duab 5-3 • Master/AHBLite Memory Space Configuration – 16 MB ib qhov

- Yog tias koj xav tau ntau dua 16 MB thiab tsawg dua 256 MB ntawm qhov chaw nyob rau ib qho ntawm koj cov khoom siv, xaiv qhov kev xaiv raws li qhia hauv daim duab 5-4. Hom no muab 16 256 MB slots uas tuaj yeem siv los txuas mus txog 16 AHBLite qhev.

Daim duab 5-4 • Master/AHBLite Memory Space Configuration – 256 MB ib qhov

Daim duab 5-4 • Master/AHBLite Memory Space Configuration – 256 MB ib qhov - Qhib cov slots uas koj siv rau koj daim ntawv thov (Daim duab 5-5). Qhov kev xyaum zoo tshaj plaws yog siv M1 rau qhov nkag tau raws li qhia hauv daim duab 4-2 ntawm nplooj 15.

Nco tseg: Siv M1 yog tias koj npaj yuav tsim ntau tus tswv sub-system uas koj muaj tus tswv hauv cov ntaub uas yuav tsum muaj cov yam ntxwv remap thiab yog li yuav tsum tau txuas nrog M0.

- Yog tias koj tau xaiv 16 MB ib qhov kev xaiv, tsis muaj kev txwv rau qhov twg siv tau.

- Yog tias koj tau xaiv 256 MB ib qhov kev xaiv, tsuas yog cov qhov sib xws nrog FIC piv txwv cov ntaub cim xeeb chaw xaiv cov cheeb tsam tuaj yeem siv. Txhua cheeb tsam FIC nco qhov chaw yog 256 MB loj. Rau FIC lub cim xeeb thaj tsam tau sau tseg hauv Table 5 -1 .

Table 5-1 • Chaw Nyob Hauv Cheeb Tsam thiab Tau Txais Cov Slots rau 256 MB ib qhov Options

Chaw Nyob Memory Region Tau tshaj Slots 30000000-3 FFFFFFF 3 50000000-5 FFFFFFF 5 70000000-7 FFFFFFF 7 80000000-8 FFFFFFF 8 90000000-9 FFFFFFF 9 F0000000-FFFFFFFF 15 (F)  Daim duab 5-5 • Master/AHBLite Master Access Configuration

Daim duab 5-5 • Master/AHBLite Master Access Configuration - Instantiate thiab configure AHBLite raws peripheral cores thiab/los yog kev cai AHBLite raws li cov khoom.

- Txuas lub sub-system:

- Txuas CoreAHBLite mirrored-master Bus Interface (BIF) chaw nres nkoj M1 mus rau MSS master BIF chaw nres nkoj - FIC_0/1_AHB_MASTER - raws li qhia hauv daim duab 5-6.

- Txuas cov AHBLite qhev mus rau qhov tsim nyog raws li koj daim ntawv qhia nco ntsoov.

- moos thiab rov pib dua; xa mus rau “Configuring the FIC Sub-System Clocks” nyob rau nplooj 23 thiab “Configuring the FIC Sub-System Reset” ntawm nplooj 27.

Daim duab 5-6 • FIC Master/AHBLite Sub-System

Daim duab 5-6 • FIC Master/AHBLite Sub-System

Master/APB3

Instantiate thiab teeb tsa lub npav CoreAPB3 raws li hauv qab no:

- Xaiv qhov chaw nyob Configuration xaiv raws li qhia hauv daim duab 5-7. Hom no muab kaum rau 16MB slots uas tuaj yeem siv los txuas mus txog kaum rau APB3 cov tub qhe ua raws. Yog tias koj xav tau cov slots nrog ntau lub cim xeeb, koj tuaj yeem ua ke ntau tus qhev los tsim lub qhov loj dua. Xa mus rau CoreAPB3 Tus Neeg Siv Phau Ntawv Qhia kom paub meej ntxiv txog qhov kev xaiv no.

Daim duab 5-7 • Master/APB3 Chaw Nyob Configuration

Daim duab 5-7 • Master/APB3 Chaw Nyob Configuration - Qhib cov slots uas koj siv rau koj daim ntawv thov, raws li qhia hauv daim duab 5-8.

Daim duab 5-8 • Master/APB3 Slave Slots Configuration

Daim duab 5-8 • Master/APB3 Slave Slots Configuration - Instantiate thiab configure APB3 raws peripheral cores thiab / lossis kev cai APB3 raws li cov khoom.

- Txuas lub sub-system:

– Txuas CoreAPB3 mirrored-master Bus Interface (BIF) chaw nres nkoj mus rau MSS tswv BIF chaw nres nkoj FIC_0/1_APB_MASTER – raws li qhia hauv daim duab 5-9.

- Txuas cov APB3 cov qhev mus rau qhov tsim nyog raws li koj daim ntawv qhia kev nco.

- moos thiab rov pib dua; xa mus rau “Configuring the FIC Sub-System Clocks” nyob rau nplooj 23 thiab “Configuring the FIC Sub-System Reset” ntawm nplooj 27.

Daim duab 5-9 • FIC Master/APB3 Sub-System

Daim duab 5-9 • FIC Master/APB3 Sub-System

qhev/AHBLite

Tsis muaj nyob rau lub sijhawm no.

Slave/APB3

Tsis muaj nyob rau lub sijhawm no.

Configuring FIC Sub-System Clocks

Txhawm rau tsim lub moos tsim nyog thiab kev sib txuas, koj yuav tsum:

- Configure MSS CCC FIC moos

- Instantiate thiab teeb tsa FPGA ntaub CCC core

- Txuas lub moos tes hauj lwm rau txhua qhov FIC sub-system

- Txuas MSS CLK_BASE chaw nres nkoj mus rau qhov tseeb FPGA ntaub FIC sub-system moos network

Lub SmartFusion2 architecture tsim ntau txoj cai uas yuav tsum tau ua raws li tag nrho FIC sub-systems kom muaj kev cuam tshuam zoo ntawm MSS logic thiab FPGA ntaub logic. Cov kev cai no tau teev tseg hauv qab no thiab pom hauv daim duab 6-1.

- Txhua FPGA npuag FIC sub-system yuav tsum tau tsav los ntawm lub moos uas nws lub moos zaus sib tw nrog cov zaus tau hais tseg, rau qhov tshwj xeeb sub-system, hauv MSS CCC configurator.

- Tag nrho FPGA npuag FIC sub-system moos yuav tsum tau ua raws nraim; cov moos yuav muaj ntau zaus, tab sis qhov nce ntawm cov moos qeeb yuav tsum tau ua raws li qhov nce ntawm cov moos ceev tshaj plaws.

- FPGA npuag FIC sub-system moos nrog qhov tsawg tshaj plaws yuav tsum tsav MSS CLK_BASE.

- Yog tias cov ntaub moos tau muab los ntawm cov ntaub CCC (nrog PLL), cov ntaub CCC LOCK cov zis yuav tsum txuas nrog MSS_CCC_CLK_BASE_PLL_LOCK chaw nres nkoj. MSS CCC Fabric Alignment Clock Clock Circuitry (FACC) saib xyuas CLK_BASE PLL LOCK teeb liab los lav tias CLK_BASE ruaj khov ua ntej hloov ntawm lub moos standby ( moos siv thaum lub sijhawm ntaus ntawv boot) mus rau cov neeg siv teeb tsa lub moos tau los ntawm CLK_BASE.

Daim duab 6-1 • Sub-System Clock Rules

Daim duab 6-1 • Sub-System Clock Rules

Ua raws li cov kauj ruam hauv qab no los teeb tsa lub moos tes hauj lwm rau tag nrho koj FIC sub-systems.

Kauj ruam 1: Txhim kho MSS CCC Sub-Block

Rau txhua qhov FIC thaiv (FIC_0, FIC_1, thiab DDR_FIC/SMC_FIC) siv hauv koj tus qauv tsim, xaiv lub moos divisors hauv MSS Clock Configurator (MSS_CCC) raws li qhia hauv daim duab 6-2. Daim duab 6-2 • MSS CCC FIC Clock Configuration

Daim duab 6-2 • MSS CCC FIC Clock Configuration

Nco tseg tias CLK_BASE teb tsis yog kho tau. CLK_BASE zaus, raws li tsim los ntawm SmartFusion2 architecture, yuav tsum yog qhov tsawg kawg nkaus zaus ntawm tag nrho cov FIC moos zaus thiab yuav raug suav los ntawm MSS CCC configurator. Saib “Qeb 3: Txuas FPGA Fabric FIC SubSystems Clock Networks” nyob rau nplooj 25 kom paub meej ntxiv txog CLK_BASE configuration.

Kauj ruam 2: Kho lub FPGA Fabric FIC moos

Instantiate ib daim ntaub CCC (nrog PLL) thiab teeb tsa nws kom ua tau raws li FIC sub-system moos cov cai tau piav qhia nyob rau nplooj 23. Koj feem ntau yuav tsum koom nrog lub ntiaj teb cov zis (GLx) rau txhua lub moos FIC, qhia rau txhua qhov tso zis nws zaus ( sib piv cov zaus uas tau teev tseg hauv MSS CCC) thiab muaj tag nrho cov txiaj ntsig thoob ntiaj teb tau txais los ntawm cov zis ntawm PLL los lav qhov kev sib tw theem (raws li qhia hauv daim duab 6-3).

Nco tseg: Yog hais tias ob lub FIC sub-systems muaj tib zaus, koj tsis tas yuav tsim ob lub ntiaj teb kev ywj pheej tawm los ntawm cov ntaub CCC; ib tug txaus. Daim duab 6-3 • Npuag CCC nrog PLL

Daim duab 6-3 • Npuag CCC nrog PLL

Kauj Ruam 3: Txuas FPGA Fabric FIC Sub-Systems Clock Networks

Txuas txhua daim ntaub CCC thoob ntiaj teb tso zis GLx rau FIC sub-system nws cuam tshuam nrog.

Kauj ruam 4: Txuas MSS CLK_BASE Chaw nres nkoj

Txuas qhov qeeb tshaj plaws ntawm cov ntaub CCC ntiaj teb tso zis GLx rau MSS CLK_BASE chaw nres nkoj.

Kauj ruam 5: Txuas MSS MCCC_CLK_BASE_PLL_LOCK Chaw nres nkoj

Txuas cov ntaub CCC LOCK tso zis rau MSS MCCC_CLK_BASE_PLL_LOCK chaw nres nkoj.

Lub Sijhawm Kev Ntsuam Xyuas Kev Xav Tau

Ua cov txheej txheem tom qab layout zoo li lub sij hawm tsom xam kom paub tseeb tias tus tsim ua tau raws li lub sij hawm yuav tsum tau teev tseg nyob rau hauv MSS CCC thiab FPGA ntaub CCC Configurators. Tej zaum koj yuav tau hloov M3_CLK lossis nce lub moos piv ntawm MSS thiab cov ntaub kom tau txais tus qauv tsim uas dhau qhov Kev Ntsuas Sijhawm Zoo.

Configuring FIC Sub-System Reset

Txhawm rau teeb tsa FIC Sub-System Reset:

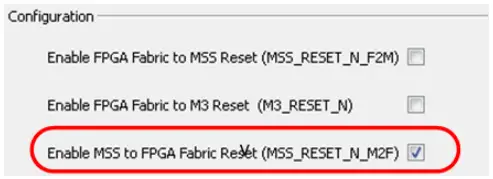

- Los ntawm MSS Configurator, teeb tsa MSS Reset sub-block kom nthuav tawm MSS_RESET_N_M2F chaw nres nkoj.

Daim duab 7-1 • Configure MSS Reset Sub-Block

Daim duab 7-1 • Configure MSS Reset Sub-Block - Txuas MSS_RESET_N_M2F chaw nres nkoj rau tag nrho FPGA ntaub FIC sub-systems rov pib dua cov chaw nres nkoj.

Configuring System Memory Map

Txhua qhov peripheral (AMBA AXI, AHBLite thiab APB3 qhev) raug txheeb xyuas los ntawm qhov chaw nyob los ntawm FIC subsystem tus tswv ntsiab lus ntawm view. Peb feem ntau xa mus rau tag nrho cov kev sib raug zoo ntawm cov tswv thiab cov qhev ntawm ib tug sub-system raws li lub cim xeeb daim ntawv qhia ntawm lub sub-system. Daim ntawv qhia kev nco ntawm lub sub-system tuaj yeem hloov kho hauv SmartDesign. Koj tuaj yeem ua tau view daim ntawv qhia nco kawg ntawm koj lub cev thaum koj tsim tag nrho cov kab ke. Daim ntawv qhia nco yog ib feem ntawm Datasheet generated rau 'hauv paus' ntawm koj tsim raws li tiam.

Configuring the Memory Map (Generic SmartDesign Behavior)

Hauv SmartDesign, lub peripheral tau muab qhov chaw nyob ntawm lub tsheb npav raws li qhov chaw nyob hauv lub tsheb npav hauv lub sub-system ntxiv rau tus lej ntawm lub npav lub sijhawm ntawm qhov loj. Yog li hloov tus lej qhov rau ib qho peripheral cuam tshuam nws qhov chaw nyob raws li. Kev hloov pauv qhov chaw ua haujlwm rau ib qho khoom siv peripheral tuaj yeem ua tau los ntawm kev sib txuas ntawm cov khoom siv hluav taws xob ntawm tus qhev BIF mus rau ib lub tsheb npav tshwj xeeb uas siv cov qhev BIF (slot) siv SmartDesign txuas cov cuab yeej muaj nyob hauv Canvas. Qhov no kuj tseem tuaj yeem ua tau los ntawm kev kho daim ntawv qhia nco siv Hloov Kho Memory Map, raws li pom hauv daim duab 8-1. Daim duab 8-1 • Hloov daim ntawv qhia nco los ntawm SmartDesign Canvas

Daim duab 8-1 • Hloov daim ntawv qhia nco los ntawm SmartDesign Canvas

Qhov Hloov Kho Memory Map dialog box tshwm (Daim duab 8-2). Daim duab 8-2 • Hloov Kho Memory Map Dialog Box

Daim duab 8-2 • Hloov Kho Memory Map Dialog Box

Configuring the Memory Regions rau FIC Interfaces (MSS Master View)

Muaj rau 256 MB cheeb tsam uas txhais tau tias yog FIC Regions 0 txog 5 hauv MSS nco daim ntawv qhia. Txhua cheeb tsam no tuaj yeem faib rau FIC_0 lossis FIC_1 qhev cuam tshuam hauv kev sib koom ua ke. Koj tuaj yeem xaiv qhov twg FIC (0 lossis 1) tus qhev cuam tshuam koj muab cov cheeb tsam ntawd los ntawm kev siv lub xov tooj cua khawm nyob ib sab ntawm txhua cheeb tsam hauv FPGA Fabric Chaw Nyob Thaj Chaw (MSS Master View) pawg lub thawv (Daim duab 8-3).  Daim duab 8-3 • FPGA Fabric Address Regions (MSS Master View)

Daim duab 8-3 • FPGA Fabric Address Regions (MSS Master View)

Memory Map Computation General Formula

Qhov chaw nyob hauv paus rau FIC npuag interfaces yog 0x30000000, 0x50000000, 0x70000000, 0x80000000, 0x90000000 thiab 0xF0000000. Saib “Configuring the FIC Sub-Systems” nyob rau nplooj 17 kom paub meej txog kev teeb tsa FIC li cas los qhia rau cov chaw nyob no.

Rau AHBLite, qhov loj me tuaj yeem yog 16 MB (0x01000000) lossis 256 MB (0x10000000).

Thaum siv 16 MB ib qhov, txhua qhov ntawm 0 txog 16 tuaj yeem siv tau; qhov chaw nyob ntawm tus neeg siv khoom peripheral tuaj yeem suav tau raws li FIC lub cim xeeb thaj tsam chaw nyob + (qhov naj npawb * 0x01000000). Hauv qhov kev teeb tsa no, txhua cheeb tsam yog cov npe ntawm ib leeg vim AHBLite core tsis txiav txim siab qhov chaw nyob [31:28]; cov slots raug txiav txim siv qhov chaw nyob [27:24].

Thaum siv 256 MB ib qhov, tsuas yog qhov 3, 5, 7, 8, 9 thiab F tuaj yeem siv tau; qhov chaw nyob ntawm tus neeg siv khoom peripheral tuaj yeem suav tau raws li FIC lub cim xeeb thaj tsam chaw nyob + (qhov naj npawb * 0x10000000). Hauv qhov kev teeb tsa no, txhua cheeb tsam tshwj xeeb hais txog qhov sib txawv raws li AHBLite core decodes cov slots siv qhov chaw nyob [31:28]. Hauv qhov kev teeb tsa no, txhawm rau ua kom yooj yim ntawm daim duab qhia kev sib npaug, lub hauv paus chaw nyob yog 0x00000000, es tsis yog ib qho ntawm rau qhov chaw nyob ruaj ruaj uas tau teev tseg saum toj no.

Example 1 (16 MB slot configuration):

Siv lub cim xeeb thaj tsam 0x50000000, yog tias lub peripheral nyob ntawm tus lej 7, ces nws qhov chaw nyob yog: 0x50000000 + (0x7 * 0x01000000) = 0x57000000

Example 2 (256 MB slot configuration):

Siv lub cim xeeb thaj tsam 0x50000000, yog tias lub peripheral nyob ntawm qhov chaw 15, ces nws qhov chaw nyob yog: 0x00000000 + (0xF * 0x10000000) = 0xF0000000

Viewnyob rau hauv qhov kawg Memory Map

Lub sijhawm no, Libero SoC tsis tsim daim ntawv qhia kev nco raug rau cov tshuab siv SmartFusion2 MSS.

Khoom txhawb

Microsemi SoC Products Group rov qab nws cov khoom nrog ntau yam kev pabcuam, suav nrog Kev Pabcuam Cov Neeg Siv Khoom, Lub Chaw Pabcuam Cov Neeg Siv Khoom, a website, electronic mail, thiab chaw muag khoom thoob ntiaj teb. Cov ntawv txuas ntxiv no muaj cov ntaub ntawv hais txog kev tiv tauj Microsemi SoC Products Group thiab siv cov kev pabcuam txhawb nqa no.

Kev Pabcuam Cov Neeg Siv Khoom

Hu rau Lub Chaw Pabcuam Cov Neeg Siv Khoom rau kev txhawb nqa cov khoom lag luam uas tsis yog khoom siv, xws li cov nqi khoom, kev hloov khoom dua tshiab, cov ntaub ntawv hloov tshiab, kev txiav txim raws li txoj cai, thiab kev tso cai.

Los ntawm North America, hu 800.262.1060

Los ntawm lwm lub ntiaj teb, hu 650.318.4460

Fax, los ntawm txhua qhov chaw hauv ntiaj teb, 408.643.6913

Customer Technical Support Center

Microsemi SoC Products Group ua haujlwm rau nws Lub Chaw Pabcuam Cov Neeg Siv Khoom nrog cov kws tshaj lij engineers uas tuaj yeem pab teb koj cov khoom kho vajtse, software, thiab tsim cov lus nug txog Microsemi SoC Cov Khoom. Lub Chaw Pabcuam Cov Neeg Siv Khoom siv sijhawm ntau heev los tsim cov ntawv thov, cov lus teb rau cov lus nug txog kev tsim qauv, cov ntaub ntawv ntawm cov teeb meem paub, thiab ntau yam FAQs. Yog li, ua ntej koj tiv tauj peb, thov mus saib peb cov kev pabcuam hauv online. Nws zoo li peb twb tau teb koj cov lus nug.

Kev pab txhawb nqa

Mus ntsib Cov Neeg Siv Khoom webxaib (www.microsemi.com/soc/support/search/default.aspx) kom paub ntau ntxiv thiab kev txhawb nqa. Muaj ntau cov lus teb muaj nyob rau hauv kev tshawb nrhiav web cov ntaub ntawv muaj xws li daim duab, duab, thiab txuas mus rau lwm yam kev pab ntawm lub webqhov chaw.

Webqhov chaw

Koj tuaj yeem xauj ntau yam ntaub ntawv qhia txog kev siv tshuab thiab tsis yog txheej txheem ntawm SoC home page, ntawm www.microsemi.com/soc.

Hu rau Customer Technical Support Center

Cov kws tshaj lij engineers ua haujlwm hauv Technical Support Center. Lub Chaw Pabcuam Kev Pabcuam tuaj yeem tiv tauj los ntawm email lossis los ntawm Microsemi SoC Products Group webqhov chaw.

Email

Koj tuaj yeem sib txuas lus koj cov lus nug txog kev ua haujlwm rau peb qhov chaw nyob email thiab tau txais cov lus teb rov qab los ntawm email, fax, lossis xov tooj. Tsis tas li, yog tias koj muaj teeb meem tsim, koj tuaj yeem xa email rau koj tus qauv tsim files tau txais kev pab. Peb niaj hnub saib xyuas tus email account txhua hnub. Thaum xa koj qhov kev thov rau peb, thov nco ntsoov suav nrog koj lub npe tag nrho, lub tuam txhab npe, thiab koj cov ntaub ntawv tiv toj kom ua tau zoo ntawm koj qhov kev thov.

Cov kev txhawb nqa email chaw nyob yog soc_tech@microsemi.com.

Kuv Cases

Microsemi SoC Products Group cov neeg siv khoom tuaj yeem xa thiab taug qab cov xwm txheej hauv online los ntawm kev mus rau Kuv Cases.

Sab nraum Teb Chaws Asmeskas

Cov neeg siv khoom xav tau kev pab sab nraud Tebchaws Meskas cov sijhawm tuaj yeem hu rau kev txhawb nqa ntawm email (soc_tech@microsemi.com) lossis hu rau lub chaw muag khoom hauv zos. Cov npe chaw muag khoom tuaj yeem nrhiav tau ntawm www.microsemi.com/soc/company/contact/default.aspx.

ITAR Technical Support

Rau kev txhawb nqa ntawm RH thiab RT FPGAs uas tau tswj hwm los ntawm International Traffic in Arms Regulations (ITAR), tiv tauj peb ntawm soc_tech_itar@microsemi.com ua. Xwb, hauv My Cases, xaiv Yes hauv ITAR drop-down list. Rau ib daim ntawv teev tag nrho ntawm ITAR-tswj Microsemi FPGAs, mus saib ITAR web nplooj.

Microsemi Corporation (NASDAQ: MSCC) muab cov ntaub ntawv qhia txog cov khoom siv hluav taws xob semiconductor kev daws teeb meem rau: aerospace, kev tiv thaiv thiab kev ruaj ntseg; kev lag luam thiab kev sib txuas lus; thiab kev lag luam thiab lwm yam kev lag luam hluav taws xob. Cov khoom lag luam suav nrog kev ua haujlwm siab, kev ntseeg siab ntawm cov khoom siv analog thiab RF, cov teeb liab sib xyaw thiab RF kev sib txuas ua ke, kho tau SoCs, FPGAs, thiab ua tiav subsystems. Microsemi yog lub hauv paus hauv Aliso Viejo, Calif. Kawm ntxiv ntawm www.microsemi.com.

© 2014 Microsemi Corporation. Txhua txoj cai. Microsemi thiab Microsemi logo yog cov cim lag luam ntawm Microsemi Corporation. Tag nrho lwm cov cim lag luam thiab cov cim kev pabcuam yog cov cuab yeej ntawm lawv cov tswv.

5-02-00370-1/08.14

Microsemi Corporate Lub Chaw Haujlwm

Microsemi Corporate Lub Chaw Haujlwm

Aliso Viejo CA 92656 USA

Hauv Tebchaws Meskas: +1 949-380-6100 Ib

Kev muag khoom: +1 949-380-6136 Ib

Fax: + 1 949-215-4996 Ib

Cov ntaub ntawv / Cov ntaub ntawv

|

Microsemi SmartFusion2 MSS Tsim Kev Tsim [ua pdf] Cov neeg siv phau ntawv qhia SmartFusion2 MSS Tsim Kev Tsim |