ARTIX-7 FPGA

Bodi ya Core

AC7A200

Mfumo kwenye Moduli

Mwongozo wa Mtumiaji

Rekodi ya Toleo

| Toleo | Tarehe | Kutolewa Na | Maelezo |

| Ufu 1.0 | 28-06-20 | Rachel Zhou | Toleo la Kwanza |

Sehemu ya 1: Utangulizi wa Bodi ya AC7A200

AC7A200 (mfano wa bodi ya msingi, sawa hapa chini) bodi ya msingi ya FPGA, inategemea mfululizo wa XILINX ARTIX-7 100T XC7A200T-2FBG484I. Ni bodi ya msingi ya utendaji wa juu yenye kasi ya juu, bandwidth ya juu na uwezo wa juu. Inafaa kwa mawasiliano ya data ya kasi ya juu, usindikaji wa picha za video, upataji wa data wa kasi n.k.

Bodi hii ya msingi ya AC7A200 hutumia vipande viwili vya chip ya MICRON's MT41J256M16HA-125 DDR3, kila DDR ina uwezo wa 4Gbit; chipsi mbili za DDR zimeunganishwa katika upana wa basi wa data wa 32-bit, na kipimo data cha kusoma/kuandika kati ya FPGA na DDR3 ni hadi 25Gb; usanidi kama huo unaweza kukidhi mahitaji ya usindikaji wa data ya bandwidth ya juu.

Ubao wa msingi wa AC7A200 huongeza bandari 180 za kiwango cha IO za kiwango cha 3.3V, bandari 15 za kawaida za IO za kiwango cha 1.5V, na jozi 4 za mawimbi tofauti ya kasi ya juu ya GTP ya RX/TX. Kwa watumiaji wanaohitaji IO nyingi, bodi hii ya msingi itakuwa chaguo nzuri. Zaidi ya hayo, njia kati ya chip ya FPGA na kiolesura ni urefu sawa na usindikaji tofauti, na ukubwa wa bodi ya msingi ni inchi 2.36 * 2.36 tu, ambayo inafaa sana kwa maendeleo ya pili.

Kielelezo 1-1: Bodi ya Msingi ya AC7A200 (Mbele View)

Kielelezo 1-2: Bodi ya Msingi ya AC7A200 (Nyuma View)

Sehemu ya 2: Chip ya FPGA

Kama ilivyoelezwa hapo juu, mfano wa FPGA tunayotumia ni XC7A200T-2FBG484I, ambayo ni ya mfululizo wa Xilinx's Artix-7. Daraja la kasi ni 2, na daraja la joto ni daraja la sekta. Mfano huu ni kifurushi cha FGG484 chenye pini 484. Sheria za kumtaja chipu Xilinx ARTIX-7 FPGA kama ilivyo hapo chini

Kielelezo 2-1: Ufafanuzi Maalum wa Muundo wa Chip wa Mfululizo wa ARTIX-7

Kielelezo 2-2: Chipu ya FPGA kwenye ubao

Vigezo kuu vya FPGA Chip XC7A200T ni kama ifuatavyo

| Jina | Vigezo maalum |

| Seli za mantiki | 215360 |

| Vipande | 16-02-92 |

| Flip-flops za CLB | 269200 |

| Zuia RAM (kb) | 13140 |

| Vipande vya DSP | 740 |

| PCIe Mwanzo 2 | 1 |

| XADC | 1 XADC, 12bit, 1Mbps AD |

| Transceiver ya GTP | 4 GTP, 6.6Gb/s max |

| Kasi ya Daraja | -2 |

| Daraja la joto | Viwandani |

Mfumo wa usambazaji wa umeme wa FPGA

Vifaa vya umeme vya Artix-7 FPGA ni VCCINT, VCCBRAM, VCCAUX, VCCO, VMGTAVCC na VMGTAVTT. VCCINT ni pini ya msingi ya usambazaji wa nguvu ya FPGA, ambayo inahitaji kuunganishwa kwa 1.0V; VCCBRAM ni pini ya usambazaji wa nguvu ya FPGA Block RAM, kuunganisha kwa 1.0V; VCCAUX ni pini ya umeme ya FPGA, unganisha 1.8V; VCCO ni juzuutage ya kila BENKI ya FPGA, ikijumuisha BANK0, BANK13~16, BANK34~35. Kwenye ubao wa msingi wa AC7A200 FPGA, BANK34 na BANK35 zinahitaji kuunganishwa kwa DDR3, sautitage uhusiano wa BANK ni 1.5V, na voltage ya BENKI nyingine ni 3.3V. VCO ya BANK15 na BANK16 inaendeshwa na LDO, na inaweza kubadilishwa kwa kuchukua nafasi ya chipu ya LDO. VMGTAVCC ni ujazo wa usambazajitage ya transceiver ya ndani ya FPGA ya GTP, iliyounganishwa na 1.0V; VMGTAVTT ni juzuu ya kusitishatage ya transceiver ya GTP, iliyounganishwa na 1.2V.

Mfumo wa Artix-7 FPGA unahitaji kwamba mfuatano wa kuongeza nguvu uwe na nguvu na VCCINT, kisha VCCBRAM, kisha VCCAUX, na hatimaye VCC. Ikiwa VCCINT na VCCBRAM zina ujazo sawatage, zinaweza kuwashwa kwa wakati mmoja. Utaratibu wa madaraka outages ni kinyume. Mlolongo wa kuongeza nguvu wa transceiver ya GTP ni VCCINT, kisha VMGTAVCC, kisha VMGTAVTT. Ikiwa VCCINT na VMGTAVCC zina ujazo sawatage, zinaweza kuwashwa kwa wakati mmoja. Mlolongo wa kuzima ni kinyume tu cha mlolongo wa kuwasha.

Sehemu ya 3: Kioo Amilifu cha Tofauti

Bodi ya msingi ya AC7A200 ina fuwele mbili za tofauti za Sitime, moja ni 200MHz, mfano ni SiT9102-200.00MHz, saa kuu ya mfumo kwa FPGA na kutumika kuzalisha saa ya kudhibiti DDR3; nyingine ni 125MHz, mfano ni SiT9102 -125MHz, pembejeo ya saa ya kumbukumbu kwa transceivers za GTP.

Sehemu ya 3.1: Saa Inayotumika ya Tofauti 200Mhz

G1 kwenye Mchoro 3-1 ni fuwele amilifu ya 200M ambayo hutoa chanzo cha saa ya mfumo wa bodi. Pato la fuwele limeunganishwa na pini ya saa ya kimataifa ya BANK34 MRCC (R4 na T4) ya FPGA. Saa hii ya tofauti ya 200Mhz inaweza kutumika kuendesha mantiki ya mtumiaji katika FPGA. Watumiaji wanaweza kusanidi PLL na DCM ndani ya FPGA ili kuzalisha saa za masafa tofauti.

Kielelezo 3-1: 200Mhz Amilifu Differential Schematic ya Kioo

Kielelezo 3-2: Kioo Inayotumika cha 200Mhz kwenye Ubao wa Msingi

Mgawo wa Pini ya Saa ya 200Mhz Tofauti

| Jina la Ishara | PIN ya FPGA |

| SYS_CLK_P | R4 |

| SYS_CLK_N | T4 |

Sehemu ya 3.2: Kioo Inayotumika cha 125MHz

G2 katika Kielelezo 3-3 ni kioo amilifu cha 125MHz, ambacho ni saa ya uingizaji wa marejeleo inayotolewa kwa moduli ya GTP ndani ya FPGA. Pato la fuwele limeunganishwa kwenye pini za saa za GTP BANK216 MGTREFCLK0P (F6) na MGTREFCLK0N (E6) za FPGA.

Kielelezo 3-3: 125MHz Active Differential Schematic ya Kioo

Kielelezo 3-4: Kioo Inayotumika cha 125MHz kwenye Ubao wa Msingi

Ugawaji wa Pini ya Saa tofauti ya 125MHz

| Jina la Net | PIN ya FPGA |

| MGT_CLK0_P | F6 |

| MGT_CLK0_N | E6 |

Sehemu ya 4: DDR3 DRAM

Bodi ya msingi ya FPGA AC7A200 ina chipsi mbili za Micron 4Gbit (512MB) DDR3 (kabisa 8Gbit), mfano ni MT41J256M16HA-125 (sambamba na MT41K256M16HA-125). DDR3 SDRAM ina kasi ya juu ya uendeshaji ya 400MHz (kiwango cha data 800Mbps). Mfumo wa kumbukumbu wa DDR3 umeunganishwa moja kwa moja na interface ya kumbukumbu ya BANK 34 na BANK35 ya FPGA. Usanidi maalum wa DDR3 SDRAM umeonyeshwa kwenye Jedwali 4-1.

| Nambari kidogo | Mfano wa Chip | Uwezo | Kiwanda |

| U5,U6 | MT41J256M16HA-125 | 256M x 16bit | Mikroni |

Jedwali 4-1: Usanidi wa DDR3 SDRAM

Muundo wa vifaa vya DDR3 unahitaji uzingatiaji mkali wa uadilifu wa ishara. Tumezingatia kikamilifu kipingamizi/kituo kinacholingana, udhibiti wa kizuizi, na ufuatiliaji wa urefu katika muundo wa saketi na muundo wa PCB ili kuhakikisha utendakazi wa kasi ya juu na thabiti wa DDR3. Kielelezo 4-1 kinaelezea muunganisho wa maunzi ya DDR3 DRAM

Kielelezo 4-1: Mpango wa DDR3 DRAM

Kielelezo 4-2: DDR3 kwenye Bodi ya Msingi

Mgawo wa pini ya DDR3 DRAM:

| Jina la Net | Jina la PIN ya FPGA | FPGA P/N |

| DDR3_DQS0_P | IO_L3P_T0_DQS_AD5P_35 | E1 |

| DDR3_DQS0_N | IO_L3N_T0_DQS_AD5N_35 | D1 |

| DDR3_DQS1_P | IO_L9P_T1_DQS_AD7P_35 | K2 |

| DDR3_DQS1_N | IO_L9N_T1_DQS_AD7N_35 | J2 |

| DDR3_DQS2_P | IO_L15P_T2_DQS_35 | M1 |

| DDR3_DQS2_N | IO_L15N_T2_DQS_35 | L1 |

| DDR3_DQS3_P | IO_L21P_T3_DQS_35 | P5 |

| DDR3_DQS3_N | IO_L21N_T3_DQS_35 | P4 |

| DDR3_DQ[0] | IO_L2P_T0_AD12P_35 | C2 |

| DDR3_DQ [1] | IO_L5P_T0_AD13P_35 | G1 |

| DDR3_DQ [2] | IO_L1N_T0_AD4N_35 | A1 |

| DDR3_DQ [3] | IO_L6P_T0_35 | F3 |

| DDR3_DQ [4] | IO_L2N_T0_AD12N_35 | B2 |

| DDR3_DQ [5] | IO_L5N_T0_AD13N_35 | F1 |

| DDR3_DQ [6] | IO_L1P_T0_AD4P_35 | B1 |

| DDR3_DQ [7] | IO_L4P_T0_35 | E2 |

| DDR3_DQ [8] | IO_L11P_T1_SRCC_35 | H3 |

| DDR3_DQ [9] | IO_L11N_T1_SRCC_35 | G3 |

| DDR3_DQ [10] | IO_L8P_T1_AD14P_35 | H2 |

| DDR3_DQ [11] | IO_L10N_T1_AD15N_35 | H5 |

| DDR3_DQ [12] | IO_L7N_T1_AD6N_35 | J1 |

| DDR3_DQ [13] | IO_L10P_T1_AD15P_35 | J5 |

| DDR3_DQ [14] | IO_L7P_T1_AD6P_35 | K1 |

| DDR3_DQ [15] | IO_L12P_T1_MRCC_35 | H4 |

| DDR3_DQ [16] | IO_L18N_T2_35 | L4 |

| DDR3_DQ [17] | IO_L16P_T2_35 | M3 |

| DDR3_DQ [18] | IO_L14P_T2_SRCC_35 | L3 |

| DDR3_DQ [19] | IO_L17N_T2_35 | J6 |

| DDR3_DQ [20] | IO_L14N_T2_SRCC_35 | K3 |

| DDR3_DQ [21] | IO_L17P_T2_35 | K6 |

| DDR3_DQ [22] | IO_L13N_T2_MRCC_35 | J4 |

| DDR3_DQ [23] | IO_L18P_T2_35 | L5 |

| DDR3_DQ [24] | IO_L20N_T3_35 | P1 |

| DDR3_DQ [25] | IO_L19P_T3_35 | N4 |

| DDR3_DQ [26] | IO_L20P_T3_35 | R1 |

| DDR3_DQ [27] | IO_L22N_T3_35 | N2 |

| DDR3_DQ [28] | IO_L23P_T3_35 | M6 |

| DDR3_DQ [29] | IO_L24N_T3_35 | N5 |

| DDR3_DQ [30] | IO_L24P_T3_35 | P6 |

| DDR3_DQ [31] | IO_L22P_T3_35 | P2 |

| DDR3_DM0 | IO_L4N_T0_35 | D2 |

| DDR3_DM1 | IO_L8N_T1_AD14N_35 | G2 |

| DDR3_DM2 | IO_L16N_T2_35 | M2 |

| DDR3_DM3 | IO_L23N_T3_35 | M5 |

| DDR3_A[0] | IO_L11N_T1_SRCC_34 | AA4 |

| DDR3_A[1] | IO_L8N_T1_34 | AB2 |

| DDR3_A[2] | IO_L10P_T1_34 | AA5 |

| DDR3_A[3] | IO_L10N_T1_34 | AB5 |

| DDR3_A[4] | IO_L7N_T1_34 | AB1 |

| DDR3_A[5] | IO_L6P_T0_34 | U3 |

| DDR3_A[6] | IO_L5P_T0_34 | W1 |

| DDR3_A[7] | IO_L1P_T0_34 | T1 |

| DDR3_A[8] | IO_L2N_T0_34 | V2 |

| DDR3_A[9] | IO_L2P_T0_34 | U2 |

| DDR3_A[10] | IO_L5N_T0_34 | Y1 |

| DDR3_A[11] | IO_L4P_T0_34 | W2 |

| DDR3_A[12] | IO_L4N_T0_34 | Y2 |

| DDR3_A[13] | IO_L1N_T0_34 | U1 |

| DDR3_A[14] | IO_L6N_T0_VREF_34 | V3 |

| DDR3_BA[0] | IO_L9N_T1_DQS_34 | AA3 |

| DDR3_BA[1] | IO_L9P_T1_DQS_34 | Y3 |

| DDR3_BA[2] | IO_L11P_T1_SRCC_34 | Y4 |

| DDR3_S0 | IO_L8P_T1_34 | AB3 |

| DDR3_RAS | IO_L12P_T1_MRCC_34 | V4 |

| DDR3_CAS | IO_L12N_T1_MRCC_34 | W4 |

| DDR3_WE | IO_L7P_T1_34 | AA1 |

| DDR3_ODT | IO_L14N_T2_SRCC_34 | U5 |

| DDR3_RESET | IO_L15P_T2_DQS_34 | W6 |

| DDR3_CLK_P | IO_L3P_T0_DQS_34 | R3 |

| DDR3_CLK_N | IO_L3N_T0_DQS_34 | R2 |

| DDR3_CKE | IO_L14P_T2_SRCC_34 | T5 |

Sehemu ya 5: Mwako wa QSPI

Bodi ya msingi ya FPGA AC7A200 ina 128Mbit QSPI FLASH moja, na mfano ni N25Q128, ambayo inatumia 3.3V CMOS vol.tage kiwango. Kutokana na hali isiyo tete ya QSPI FLASH, inaweza kutumika kama kifaa cha kuwasha mfumo kuhifadhi picha ya mfumo wa kuwasha. Picha hizi ni pamoja na FPGA kidogo files, msimbo wa maombi ya ARM, msimbo laini wa maombi ya msingi na data nyingine ya mtumiaji files. Mifano maalum na vigezo vinavyohusiana vya SPI FLASH vinaonyeshwa kwenye Jedwali 5-1.

| Nafasi | Mfano | Uwezo | Kiwanda |

| U8 | N25Q128 | Biti 128M | Numonyx |

Jedwali la 5-1: Maelezo ya QSPI FLASH

QSPI FLASH imeunganishwa kwenye pini maalum za BANK0 na BANK14 za chipu ya FPGA. Pini ya saa imeunganishwa kwa CCLK0 ya BANK0, na data nyingine na mawimbi ya kuchagua chipu yanaunganishwa kwa D00~D03 na pini za FCS za BANK14 mtawalia. Mchoro wa 5-1 unaonyesha muunganisho wa maunzi wa QSPI Flash.

Kielelezo 5-1: Mpangilio wa Mweko wa QSPI

Mgawo wa pini ya QSPI Flash:

| Jina la Net | Jina la PIN ya FPGA | FPGA P/N |

| QSPI_CLK | CCLK_0 | L12 |

| QSPI_CS | IO_L6P_T0_FCS_B_14 | T19 |

| QSPI_DQ0 | IO_L1P_T0_D00_MOSI_14 | P22 |

| QSPI_DQ1 | IO_L1N_T0_D01_DIN_14 | R22 |

| QSPI_DQ2 | IO_L2P_T0_D02_14 | P21 |

| QSPI_DQ3 | IO_L2N_T0_D03_14 | R21 |

Kielelezo 5-2: QSPI FLASH kwenye Bodi ya Msingi

Sehemu ya 6: Mwangaza wa LED kwenye Ubao wa Msingi

Kuna taa 3 nyekundu za LED kwenye ubao wa msingi wa AC7A200 FPGA, moja ambayo ni taa ya kiashiria cha nguvu (PWR), moja ni taa ya LED ya usanidi (IMEFANYIKA), na moja ni taa ya mtumiaji. Wakati bodi ya msingi inatumiwa, kiashiria cha nguvu kitaangaza; FPGA inaposanidiwa, LED ya usanidi itaangazia. Nuru ya LED ya mtumiaji imeunganishwa na IO ya BANK34, mtumiaji anaweza kudhibiti mwanga na kuzima na programu. Wakati IO juzuu yatage kushikamana na mtumiaji LED ni ya juu, mtumiaji LED ni illuminate. Wakati muunganisho wa IO ujazotage ni ya chini, LED ya mtumiaji itazimwa. Mchoro wa mpangilio wa unganisho la vifaa vya taa vya LED umeonyeshwa kwenye Mchoro 6-1:

Kielelezo 6-1: Taa za LED kwenye Mpango wa Bodi ya Msingi

Mchoro 6-2: Taa za LED kwenye Bodi ya Msingi

Mgawo wa Bani wa LED za Mtumiaji

| Jina la Ishara | Jina la siri la FPGA | Nambari ya siri ya FPGA | Maelezo |

| LED1 | IO_L15N_T2_DQS_34 | W5 | Mtumiaji LED |

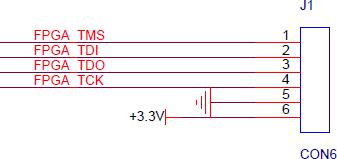

Sehemu ya 7: JTAG Kiolesura

JTAG soketi ya mtihani J1 imehifadhiwa kwenye ubao wa msingi wa AC7A200 kwa JTAG pakua na kurekebisha wakati bodi ya msingi inatumiwa peke yake. Kielelezo 7-1 ni sehemu ya kimuundo ya JTAG bandari, ambayo inahusisha TMS, TDI, TDO, TCK. , GND, +3.3V ishara hizi sita.

Kielelezo 7-1: JTAG Mpangilio wa Kiolesura

JTAG interface J1 kwenye ubao wa msingi wa AC7A200 FPGA hutumia shimo la majaribio la safu mlalo moja la pini 6 la 2.54mm. Ikiwa unahitaji kutumia JTAG kiunganishi ili kurekebisha hitilafu kwenye ubao wa msingi, unahitaji solder kichwa cha pini cha safu mlalo 6.

Kielelezo 7-2 kinaonyesha JTAG interface J1 kwenye ubao wa msingi wa AC7A200 FPGA.

Kielelezo 7-2 JTAG Kiolesura kwenye Bodi ya Msingi

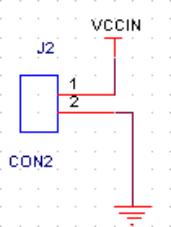

Sehemu ya 8: Kiolesura cha Nishati kwenye Bodi ya Msingi

Ili kufanya ubao wa msingi wa AC7A200 FPGA ufanye kazi peke yake, ubao wa msingi umehifadhiwa kiolesura cha usambazaji wa umeme cha pini 2 J2. Ikiwa mtumiaji anataka kutatua utendakazi wa ubao wa msingi kando (bila ubao wa mtoa huduma), kifaa cha nje kinahitaji kutoa +5V ili kusambaza nguvu kwa ubao msingi.

Kielelezo 8-1:Mchoro wa Kiolesura cha Nguvu kwenye Bodi ya Msingi

Kielelezo 8-2: Kiolesura cha nguvu kwenye Bodi ya Msingi

Sehemu ya 9: Mgawo wa siri wa Ubao kwa Viunganishi vya Bodi

Bodi ya msingi ina jumla ya bodi nne za kasi kwa viunganishi vya bodi.

Ubao wa msingi hutumia viunganishi vinne vya pini 80 ili kuunganisha kwenye ubao wa mtoa huduma. Bandari ya IO ya FPGA imeunganishwa kwa viunganishi vinne kwa njia tofauti. Nafasi ya pini ya viunganishi ni 0.5mm, ingiza kwenye ubao hadi viunganishi vya bodi kwenye ubao wa carrier kwa mawasiliano ya data ya kasi.

Viunganishi vya Ubao hadi Ubao CON1

Ubao wa pini 80 kwenye ubao viunganishi vya CON1, ambavyo hutumika kuunganishwa na usambazaji wa umeme wa VCCIN (+5V) na kusagwa kwenye ubao wa mtoa huduma, kupanua IO za kawaida za FPGA. Ikumbukwe hapa kwamba pini 15 za CON1 zimeunganishwa kwenye bandari ya IO ya BANK34, kwa sababu uhusiano wa BANK34 umeunganishwa na DDR3. Kwa hiyo, juzuu yatage kiwango cha IO zote za BANK34 hii ni 1.5V.

Bandika Ugawaji wa Bodi kwa Viunganishi vya Bodi CON1

| CON1 PIN |

Net Jina |

FPGA PIN |

Voltage Kiwango |

CON1 PIN |

Net Jina |

FPGA PIN |

Voltage Kiwango |

| PIN1 | VCCIN | – | +5V | PIN2 | VCCIN | – | +5V |

| PIN3 | VCCIN | – | +5V | PIN4 | VCCIN | – | +5V |

| PIN5 | VCCIN | – | +5V | PIN6 | VCCIN | – | +5V |

| PIN7 | VCCIN | – | +5V | PIN8 | VCCIN | – | +5V |

| PIN9 | GND | – | Ardhi | PIN10 | GND | – | Ardhi |

| PIN11 | NC | – | NC | PIN12 | NC | – | NC |

| PIN13 | NC | – | NC | PIN14 | NC | – | NC |

| PIN15 | NC | – | NC | PIN16 | B13_L4_P | AA15 | 3.3V |

| PIN17 | NC | – | NC | PIN18 | B13_L4_N | AB15 | 3.3V |

| PIN19 | GND | – | Ardhi | PIN20 | GND | – | Ardhi |

| PIN21 | B13_L5_P | Y13 | 3.3V | PIN22 | B13_L1_P | Y16 | 3.3V |

| PIN23 | B13_L5_N | AA14 | 3.3V | PIN24 | B13_L1_N | AA16 | 3.3V |

| PIN25 | B13_L7_P | AB11 | 3.3V | PIN26 | B13_L2_P | AB16 | 3.3V |

| PIN27 | B13_L7_P | AB12 | 3.3V | PIN28 | B13_L2_N | AB17 | 3.3V |

| PIN29 | GND | – | Ardhi | PIN30 | GND | – | Ardhi |

| PIN31 | B13_L3_P | AA13 | 3.3V | PIN32 | B13_L6_P | W14 | 3.3V |

| PIN33 | B13_L3_N | AB13 | 3.3V | PIN34 | B13_L6_N | Y14 | 3.3V |

| PIN35 | B34_L23_P | Y8 | 1.5V | PIN36 | B34_L20_P | AB7 | 1.5V |

| PIN37 | B34_L23_N | Y7 | 1.5V | PIN38 | B34_L20_N | AB6 | 1.5V |

| PIN39 | GND | – | Ardhi | PIN40 | GND | – | Ardhi |

| PIN41 | B34_L18_N | AA6 | 1.5V | PIN42 | B34_L21_N | V8 | 1.5V |

| PIN43 | B34_L18_P | Y6 | 1.5V | PIN44 | B34_L21_P | V9 | 1.5V |

| PIN45 | B34_L19_P | V7 | 1.5V | PIN46 | B34_L22_P | AA8 | 1.5V |

| PIN47 | B34_L19_N | W7 | 1.5V | PIN48 | B34_L22_N | AB8 | 1.5V |

| PIN49 | GND | – | Ardhi | PIN50 | GND | – | Ardhi |

| PIN51 | XADC_VN | M9 | Analogi | PIN52 | NC | ||

| PIN53 | XADC_VP | L10 | Analogi | PIN54 | B34_L25 | U7 | 1.5V |

| PIN55 | NC | – | NC | PIN56 | B34_L24_P | W9 | 1.5V |

| PIN57 | NC | – | NC | PIN58 | B34_L24_N | Y9 | 1.5V |

| PIN59 | GND | – | Ardhi | PIN60 | GND | – | Ardhi |

| PIN61 | B16_L1_N | F14 | 3.3V | PIN62 | NC | – | NC |

| PIN63 | B16_L1_P | F13 | 3.3V | PIN64 | NC | – | NC |

| PIN65 | B16_L4_N | E14 | 3.3V | PIN66 | NC | – | NC |

| PIN67 | B16_L4_P | E13 | 3.3V | PIN68 | NC | – | NC |

| PIN69 | GND | – | Ardhi | PIN70 | GND | – | Ardhi |

| PIN71 | B16_L6_N | D15 | 3.3V | PIN72 | NC | – | NC |

| PIN73 | B16_L6_P | D14 | 3.3V | PIN74 | NC | – | NC |

| PIN75 | B16_L8_P | C13 | 3.3V | PIN76 | NC | – | NC |

| PIN77 | B16_L8_N | B13 | 3.3V | PIN78 | NC | – | NC |

| PIN79 | NC | – | NC | PIN80 | NC | – | NC |

Kielelezo 9-1: Ubao hadi Viunganishi vya Ubao CON1 kwenye Ubao wa Msingi

Viunganishi vya Ubao hadi Ubao CON2

Kichwa cha muunganisho wa kike cha pini 80 CON2 kinatumika kupanua IO ya kawaida ya BANK13 na BANK14 ya FPGA. Juztage viwango vya BENKI zote mbili ni 3.3V.

Bandika Ugawaji wa Bodi kwa Viunganishi vya Bodi CON2

| CON2 PIN |

Net Jina |

FPGA PIN |

Voltage Kiwango |

CON2 PIN |

Net Jina |

FPGA PIN |

Voltage Kiwango |

| PIN1 | B13_L16_P | W15 | 3.3V | PIN2 | B14_L16_P | V17 | 3.3V |

| PIN3 | B13_L16_N | W16 | 3.3V | PIN4 | B14_L16_N | W17 | 3.3V |

| PIN5 | B13_L15_P | T14 | 3.3V | PIN6 | B13_L14_P | U15 | 3.3V |

| PIN7 | B13_L15_N | T15 | 3.3V | PIN8 | B13_L14_N | V15 | 3.3V |

| PIN9 | GND | – | Ardhi | PIN10 | GND | – | Ardhi |

| PIN11 | B13_L13_P | V13 | 3.3V | PIN12 | B14_L10_P | AB21 | 3.3V |

| PIN13 | B13_L13_N | V14 | 3.3V | PIN14 | B14_L10_N | AB22 | 3.3V |

| PIN15 | B13_L12_P | W11 | 3.3V | PIN16 | B14_L8_N | AA21 | 3.3V |

| PIN17 | B13_L12_N | W12 | 3.3V | PIN18 | B14_L8_P | AA20 | 3.3V |

| PIN19 | GND | – | Ardhi | PIN20 | GND | – | Ardhi |

| PIN21 | B13_L11_P | Y11 | 3.3V | PIN22 | B14_L15_N | AB20 | 3.3V |

| PIN23 | B13_L11_N | Y12 | 3.3V | PIN24 | B14_L15_P | AA19 | 3.3V |

| PIN25 | B13_L10_P | V10 | 3.3V | PIN26 | B14_L17_P | AA18 | 3.3V |

| PIN27 | B13_L10_N | W10 | 3.3V | PIN28 | B14_L17_N | AB18 | 3.3V |

| PIN29 | GND | – | Ardhi | PIN30 | GND | – | Ardhi |

| PIN31 | B13_L9_N | AA11 | 3.3V | PIN32 | B14_L6_N | T20 | 3.3V |

| PIN33 | B13_L9_P | AA10 | 3.3V | PIN34 | B13_IO0 | Y17 | 3.3V |

| PIN35 | B13_L8_N | AB10 | 3.3V | PIN36 | B14_L7_N | W22 | 3.3V |

| PIN37 | B13_L8_P | AA9 | 3.3V | PIN38 | B14_L7_P | W21 | 3.3V |

| PIN39 | GND | – | Ardhi | PIN40 | GND | – | Ardhi |

| PIN41 | B14_L11_N | V20 | 3.3V | PIN42 | B14_L4_P | T21 | 3.3V |

| PIN43 | B14_L11_P | U20 | 3.3V | PIN44 | B14_L4_N | U21 | 3.3V |

| PIN45 | B14_L14_N | V19 | 3.3V | PIN46 | B14_L9_P | Y21 | 3.3V |

| PIN47 | B14_L14_P | V18 | 3.3V | PIN48 | B14_L9_N | Y22 | 3.3V |

| PIN49 | GND | – | Ardhi | PIN50 | GND | – | Ardhi |

| PIN51 | B14_L5_N | R19 | 3.3V | PIN52 | B14_L12_N | W20 | 3.3V |

| PIN53 | B14_L5_P | P19 | 3.3V | PIN54 | B14_L12_P | W19 | 3.3V |

| PIN55 | B14_L18_N | U18 | 3.3V | PIN56 | B14_L13_N | Y19 | 3.3V |

| PIN57 | B14_L18_P | U17 | 3.3V | PIN58 | B14_L13_P | Y18 | 3.3V |

| PIN59 | GND | – | Ardhi | PIN60 | GND | – | Ardhi |

| PIN61 | B13_L17_P | T16 | 3.3V | PIN62 | B14_L3_N | V22 | 3.3V |

| PIN63 | B13_L17_N | U16 | 3.3V | PIN64 | B14_L3_P | U22 | 3.3V |

| PIN65 | B14_L21_N | P17 | 3.3V | PIN66 | B14_L20_N | T18 | 3.3V |

| PIN67 | B14_L21_P | N17 | 3.3V | PIN68 | B14_L20_P | R18 | 3.3V |

| PIN69 | GND | – | Ardhi | PIN70 | GND | – | Ardhi |

| PIN71 | B14_L22_P | P15 | 3.3V | PIN72 | B14_L19_N | R14 | 3.3V |

| PIN73 | B14_L22_N | R16 | 3.3V | PIN74 | B14_L19_P | P14 | 3.3V |

| PIN75 | B14_L24_N | R17 | 3.3V | PIN76 | B14_L23_P | N13 | 3.3V |

| PIN77 | B14_L24_P | P16 | 3.3V | PIN78 | B14_L23_N | N14 | 3.3V |

| PIN79 | B14_IO0 | P20 | 3.3V | PIN80 | B14_IO25 | N15 | 3.3V |

Kielelezo 9-2: Ubao hadi Viunganishi vya Ubao CON2 kwenye Ubao wa Msingi

Viunganishi vya Ubao hadi Ubao CON3

Kiunganishi cha CON80 cha pini 3 kinatumika kupanua IO ya kawaida ya BANK15 na BANK16 ya FPGA. Aidha, wanne JTAG ishara pia zimeunganishwa kwenye ubao wa mtoa huduma kupitia kiunganishi cha CON3. Juztagviwango vya e vya BANK15 na BANK16 vinaweza kurekebishwa na chipu ya LDO. Chaguo-msingi iliyosakinishwa LDO ni 3.3V. Ikiwa unataka kutoa viwango vingine vya kawaida, unaweza kuibadilisha na LDO inayofaa.

Bandika Ugawaji wa Bodi kwa Viunganishi vya Bodi CON3

| CON3 PIN |

Net Jina |

FPGA PIN |

Voltage Kiwango |

CON3 PIN |

Net Jina |

FPGA PIN |

Voltage Kiwango |

| PIN1 | B15_IO0 | J16 | 3.3V | PIN2 | B15_IO25 | M17 | 3.3V |

| PIN3 | B16_IO0 | F15 | 3.3V | PIN4 | B16_IO25 | F21 | 3.3V |

| PIN5 | B15_L4_P | G17 | 3.3V | PIN6 | B16_L21_N | A21 | 3.3V |

| PIN7 | B15_L4_N | G18 | 3.3V | PIN8 | B16_L21_P | B21 | 3.3V |

| PIN9 | GND | – | Ardhi | PIN10 | GND | – | Ardhi |

| PIN11 | B15_L2_P | G15 | 3.3V | PIN12 | B16_L23_P | E21 | 3.3V |

| PIN13 | B15_L2_N | G16 | 3.3V | PIN14 | B16_L23_N | D21 | 3.3V |

| PIN15 | B15_L12_P | J19 | 3.3V | PIN16 | B16_L22_P | E22 | 3.3V |

| PIN17 | B15_L12_N | H19 | 3.3V | PIN18 | B16_L22_N | D22 | 3.3V |

| PIN19 | GND | – | Ardhi | PIN20 | GND | – | Ardhi |

| PIN21 | B15_L11_P | J20 | 3.3V | PIN22 | B16_L24_P | G21 | 3.3V |

| PIN23 | B15_L11_N | J21 | 3.3V | PIN24 | B16_L24_N | G22 | 3.3V |

| PIN25 | B15_L1_N | G13 | 3.3V | PIN26 | B15_L8_N | G20 | 3.3V |

| PIN27 | B15_L1_P | H13 | 3.3V | PIN28 | B15_L8_P | H20 | 3.3V |

| PIN29 | GND | – | Ardhi | PIN30 | GND | – | Ardhi |

| PIN31 | B15_L5_P | J15 | 3.3V | PIN32 | B15_L7_N | H22 | 3.3V |

| PIN33 | B15_L5_N | H15 | 3.3V | PIN34 | B15_L7_P | J22 | 3.3V |

| PIN35 | B15_L3_N | H14 | 3.3V | PIN36 | B15_L9_P | K21 | 3.3V |

| PIN37 | B15_L3_P | J14 | 3.3V | PIN38 | B15_L9_N | K22 | 3.3V |

| PIN39 | GND | – | Ardhi | PIN40 | GND | – | Ardhi |

| PIN41 | B15_L19_P | K13 | 3.3V | PIN42 | B15_L15_N | M22 | 3.3V |

| PIN43 | B15_L19_N | K14 | 3.3V | PIN44 | B15_L15_P | N22 | 3.3V |

| PIN45 | B15_L20_P | M13 | 3.3V | PIN46 | B15_L6_N | H18 | 3.3V |

| PIN47 | B15_L20_N | L13 | 3.3V | PIN48 | B15_L6_P | H17 | 3.3V |

| PIN49 | GND | – | Ardhi | PIN50 | GND | – | Ardhi |

| PIN51 | B15_L14_P | L19 | 3.3V | PIN52 | B15_L13_N | K19 | 3.3V |

| PIN53 | B15_L14_N | L20 | 3.3V | PIN54 | B15_L13_P | K18 | 3.3V |

| PIN55 | B15_L21_P | K17 | 3.3V | PIN56 | B15_L10_P | M21 | 3.3V |

| PIN57 | B15_L21_N | J17 | 3.3V | PIN58 | B15_L10_N | L21 | 3.3V |

| PIN59 | GND | – | Ardhi | PIN60 | GND | – | Ardhi |

| PIN61 | B15_L23_P | L16 | 3.3V | PIN62 | B15_L18_P | N20 | 3.3V |

| PIN63 | B15_L23_N | K16 | 3.3V | PIN64 | B15_L18_N | M20 | 3.3V |

| PIN65 | B15_L22_P | L14 | 3.3V | PIN66 | B15_L17_N | N19 | 3.3V |

| PIN67 | B15_L22_N | L15 | 3.3V | PIN68 | B15_L17_P | N18 | 3.3V |

| PIN69 | GND | – | Ardhi | PIN70 | GND | – | Ardhi |

| PIN71 | B15_L24_P | M15 | 3.3V | PIN72 | B15_L16_P | M18 | 3.3V |

| PIN73 | B15_L24_N | M16 | 3.3V | PIN74 | B15_L16_N | L18 | 3.3V |

| PIN75 | NC | – | PIN76 | NC | – | ||

| PIN77 | FPGA_TCK | V12 | 3.3V | PIN78 | FPGA_TDI | R13 | 3.3V |

| PIN79 | FPGA_TDO | U13 | 3.3V | PIN80 | FPGA_TMS | T13 | 3.3V |

Kielelezo 9-3: Ubao hadi Viunganishi vya Ubao CON3 kwenye Ubao wa Msingi

Viunganishi vya Ubao hadi Ubao CON4

Kiunganishi cha 80-Pin CON4 kinatumika kupanua data ya kawaida ya IO na GTP ya kasi ya juu na ishara za saa za FPGA BANK16. Juztage kiwango cha bandari ya IO cha BANK16 kinaweza kubadilishwa na chipu ya LDO. Chaguo-msingi iliyosakinishwa LDO ni 3.3V. Ikiwa mtumiaji anataka kutoa viwango vingine vya kawaida, inaweza kubadilishwa na LDO inayofaa. Data ya kasi ya juu na ishara za saa za GTP ni tofauti madhubuti zilizoelekezwa kwenye ubao wa msingi. Laini za data ni sawa kwa urefu na huwekwa kwa muda fulani ili kuzuia kuingiliwa kwa mawimbi.

Bandika Ugawaji wa Bodi kwa Viunganishi vya Bodi CON4

| CON4 PIN |

Net Jina |

FPGA PIN |

Voltage Kiwango |

CON4 PIN |

Net Jina |

FPGA PIN |

Voltage Kiwango |

| PIN1 | NC | – | – | PIN2 | – | – | |

| PIN3 | NC | – | – | PIN4 | – | – | |

| PIN5 | NC | – | – | PIN6 | – | – | |

| PIN7 | NC | – | – | PIN8 | – | – | |

| PIN9 | GND | – | Ardhi | PIN10 | GND | – | Ardhi |

| PIN11 | NC | – | – | PIN12 | MGT_TX2_P | B6 | Tofauti |

| PIN13 | NC | – | – | PIN14 | MGT_TX2_N | A6 | Tofauti |

| PIN15 | GND | – | Ardhi | PIN16 | GND | – | Ardhi |

| PIN17 | MGT_TX3_P | D7 | Tofauti | PIN18 | MGT_RX2_P | B10 | Tofauti |

| PIN19 | MGT_TX3_N | C7 | Tofauti | PIN20 | MGT_RX2_N | A10 | Tofauti |

| PIN21 | GND | – | Ardhi | PIN22 | GND | – | Ardhi |

| PIN23 | MGT_RX3_P | D9 | Tofauti | PIN24 | MGT_TX0_P | B4 | Tofauti |

| PIN25 | MGT_RX3_N | C9 | Tofauti | PIN26 | MGT_TX0_N | A4 | Tofauti |

| PIN27 | GND | – | Ardhi | PIN28 | GND | – | Ardhi |

| PIN29 | MGT_TX1_P | D5 | Tofauti | PIN30 | MGT_RX0_P | B8 | Tofauti |

| PIN31 | MGT_TX1_N | C5 | Tofauti | PIN32 | MGT_RX0_N | A8 | Tofauti |

| PIN33 | GND | – | Ardhi | PIN34 | GND | – | Ardhi |

| PIN35 | MGT_RX1_P | D11 | Tofauti | PIN36 | MGT_CLK1_P | F10 | Tofauti |

| PIN37 | MGT_RX1_N | C11 | Tofauti | PIN38 | MGT_CLK1_N | E10 | Tofauti |

| PIN39 | GND | – | Ardhi | PIN40 | GND | – | Ardhi |

| PIN41 | B16_L5_P | E16 | 3.3V | PIN42 | B16_L2_P | F16 | 3.3V |

| PIN43 | B16_L5_N | D16 | 3.3V | PIN44 | B16_L2_N | E17 | 3.3V |

| PIN45 | B16_L7_P | B15 | 3.3V | PIN46 | B16_L3_P | C14 | 3.3V |

| PIN47 | B16_L7_N | B16 | 3.3V | PIN48 | B16_L3_N | C15 | 3.3V |

| PIN49 | GND | – | Ardhi | PIN50 | GND | – | Ardhi |

| PIN51 | B16_L9_P | A15 | 3.3V | PIN52 | B16_L10_P | A13 | 3.3V |

| PIN53 | B16_L9_N | A16 | 3.3V | PIN54 | B16_L10_N | A14 | 3.3V |

| PIN55 | B16_L11_P | B17 | 3.3V | PIN56 | B16_L12_P | D17 | 3.3V |

| PIN57 | B16_L11_N | B18 | 3.3V | PIN58 | B16_L12_N | C17 | 3.3V |

| PIN59 | GND | – | Ardhi | PIN60 | GND | – | Ardhi |

| PIN61 | B16_L13_P | C18 | 3.3V | PIN62 | B16_L14_P | E19 | 3.3V |

| PIN63 | B16_L13_N | C19 | 3.3V | PIN64 | B16_L14_N | D19 | 3.3V |

| PIN65 | B16_L15_P | F18 | 3.3V | PIN66 | B16_L16_P | B20 | 3.3V |

| PIN67 | B16_L15_N | E18 | 3.3V | PIN68 | B16_L16_N | A20 | 3.3V |

| PIN69 | GND | – | Ardhi | PIN70 | GND | – | Ardhi |

| PIN71 | B16_L17_P | A18 | 3.3V | PIN72 | B16_L18_P | F19 | 3.3V |

| PIN73 | B16_L17_N | A19 | 3.3V | PIN74 | B16_L18_N | F20 | 3.3V |

| PIN75 | B16_L19_P | D20 | 3.3V | PIN76 | B16_L20_P | C22 | 3.3V |

| PIN77 | B16_L19_N | C20 | 3.3V | PIN78 | B16_L20_N | B22 | 3.3V |

| PIN79 | NC | – | PIN80 | NC | – |

Kielelezo 9-4: Ubao hadi Viunganishi vya Ubao CON4 kwenye Ubao wa Msingi

Sehemu ya 10: Ugavi wa Nguvu

Ubao wa msingi wa AC7A200 FPGA unaendeshwa na DC5V kupitia bodi ya mtoa huduma, na inaendeshwa na kiolesura cha Mini USB inapotumika peke yake. Tafadhali kuwa mwangalifu usisambaze nishati kwa Mini USB na bodi ya mtoa huduma kwa wakati mmoja ili kuepuka uharibifu. Mchoro wa kubuni wa usambazaji wa nguvu kwenye ubao unaonyeshwa kwenye Mchoro 10-1.

Kielelezo 10-1:Ugavi wa Nguvu kwenye mpangilio wa ubao msingi

Ubao wa msingi unaendeshwa na +5V na kugeuzwa kuwa +3.3V, +1.5V, +1.8V, +1.0V usambazaji wa umeme wa njia nne kupitia chipu tatu za usambazaji umeme za DC/DC TLV62130RGT. Ya sasa ya +1.0V inaweza kuwa hadi 6A, na mikondo mingine mitatu ya pato inaweza kuwa hadi 3A. VCCIO inazalishwa na LDOSPX3819M5-3-3 moja. VCCIO hutoa nishati kwa BANK15 na BANK16 ya FPGA. Watumiaji wanaweza kubadilisha IO ya BANK15,16 hadi juzuu tofautitage viwango kwa kubadilisha chipu yao ya LDO. 1.5V inazalisha ujazo wa VTT na VREFtaginahitajika na DDR3 kupitia TI's TPS51200. Ugavi wa umeme wa 1.8V wa MGTAVTT na MGTAVCC kwa transceiver ya GTP huzalishwa na chip ya TPS74801 ya TI. Kazi za kila usambazaji wa nguvu zinaonyeshwa kwenye jedwali lifuatalo:

| Ugavi wa Nguvu | Kazi |

| +1.0V | FPGA Core Voltage |

| +1.8V | FPGA juzuu msaidizitage, usambazaji wa umeme wa TPS74801 |

| +3.3V | VCCIO ya Bank0,Bank13 na Bank14 ya FPGA,QSIP FLASH, Clock Crystal |

| +1.5V | DDR3, Bank34 na Bank35 ya FPGA |

| VREF,VTT(+0.75V) | DDR3 |

| CCIP(+3.3V) | Benki ya FPGA15, Benki16 |

| MGTAVTT(+1.2V) | GTP Transceiver Bank216 ya FPGA |

| MGTVCC(+1.0V) | GTP Transceiver Bank216 ya FPGA |

Kwa sababu usambazaji wa nguvu wa Artix-7 FPGA una hitaji la mfuatano wa kuwasha umeme, katika muundo wa saketi, tumeunda kulingana na mahitaji ya nguvu ya chipu, na kuwasha ni 1.0V->1.8V->(1.5) V, 3.3V, VCCIO) na 1.0V-> MGTAVCC -> MGTAVTT, muundo wa mzunguko ili kuhakikisha uendeshaji wa kawaida wa chip.

Mzunguko wa nguvu kwenye ubao wa msingi wa AC7A200 FPGA umeonyeshwa kwenye Mchoro 10-2:

Kielelezo 10-2: Ugavi wa Nguvu kwenye Bodi ya Msingi ya AC7A200 FPGA

Sehemu ya 11: Kipimo cha Ukubwa

Kielelezo 11-1: Ubao wa AC7A200 FPGA (Juu View)

Kielelezo 11-2: AC7A200 FPGA Bodi ya Msingi (Chini View)

Nyaraka / Rasilimali

|

Bodi ya Maendeleo ya ALINX AC7A200 ARTIX-7 FPGA [pdf] Mwongozo wa Mtumiaji AC7A200 ARTIX-7 Bodi ya Maendeleo ya FPGA, AC7A200, ARTIX-7 Bodi ya Maendeleo ya FPGA, Bodi ya Maendeleo ya FPGA, Bodi ya Maendeleo, Bodi |