ARTIX-7 FPGA

បន្ទះស្នូល

AC7A200

ប្រព័ន្ធនៅលើម៉ូឌុល

សៀវភៅណែនាំអ្នកប្រើប្រាស់

កំណត់ត្រាកំណែ

| កំណែ | កាលបរិច្ឆេទ | ចេញផ្សាយដោយ | ការពិពណ៌នា |

| បប ១.០ | ៨៦៦-៤៤៧-២១៩៤ | Rachel Zhou | ការចេញផ្សាយដំបូង |

ផ្នែកទី 1៖ ការណែនាំអំពីបន្ទះស្នូល AC7A200

AC7A200 (គំរូក្តារស្នូលដូចគ្នាខាងក្រោម) បន្ទះស្នូល FPGA វាត្រូវបានផ្អែកលើ XILINX's ARTIX-7 ស៊េរី 100T XC7A200T-2FBG484I របស់ XILINX ។ វាជាបន្ទះស្នូលដែលមានសមត្ថភាពខ្ពស់មានល្បឿនលឿន កម្រិតបញ្ជូនខ្ពស់ និងសមត្ថភាពខ្ពស់។ វាសាកសមសម្រាប់ការទំនាក់ទំនងទិន្នន័យល្បឿនលឿន ដំណើរការរូបភាពវីដេអូ ការទិញទិន្នន័យល្បឿនលឿនជាដើម។

បន្ទះស្នូល AC7A200 នេះប្រើពីរបំណែកនៃបន្ទះឈីប MT41J256M16HA-125 DDR3 របស់ MICRON ដែល DDR នីមួយៗមានសមត្ថភាព 4Gbit ។ បន្ទះសៀគ្វី DDR ពីរត្រូវបានបញ្ចូលគ្នាទៅក្នុងទទឹងរថយន្តក្រុងទិន្នន័យ 32 ប៊ីត ហើយកម្រិតបញ្ជូនទិន្នន័យអាន/សរសេររវាង FPGA និង DDR3 គឺរហូតដល់ 25Gb ។ ការកំណត់រចនាសម្ព័ន្ធបែបនេះអាចបំពេញតម្រូវការនៃដំណើរការទិន្នន័យកម្រិតបញ្ជូនខ្ពស់។

បន្ទះស្នូល AC7A200 ពង្រីកច្រក IO ស្តង់ដារចំនួន 180 នៃកម្រិត 3.3V ច្រក IO ស្តង់ដារចំនួន 15 នៃកម្រិត 1.5V និង 4 គូនៃសញ្ញាឌីផេរ៉ង់ស្យែល GTP ល្បឿនលឿន RX/TX ។ សម្រាប់អ្នកប្រើប្រាស់ដែលត្រូវការ IO ច្រើន បន្ទះស្នូលនេះនឹងក្លាយជាជម្រើសដ៏ល្អ។ លើសពីនេះទៅទៀត ការនាំផ្លូវរវាងបន្ទះឈីប FPGA និងចំណុចប្រទាក់គឺមានប្រវែងស្មើគ្នា និងដំណើរការឌីផេរ៉ង់ស្យែល ហើយទំហំបន្ទះស្នូលមានត្រឹមតែ 2.36 អ៊ីញ * 2.36 អ៊ីញ ដែលស័ក្តិសមសម្រាប់ការអភិវឌ្ឍន៍បន្ទាប់បន្សំ។

រូបភាពទី 1-1: បន្ទះស្នូល AC7A200 (ខាងមុខ View)

រូបភាពទី 1-2: បន្ទះស្នូល AC7A200 (ខាងក្រោយ View)

ផ្នែកទី 2៖ បន្ទះឈីប FPGA

ដូចដែលបានរៀបរាប់ខាងលើ ម៉ូដែល FPGA ដែលយើងប្រើគឺ XC7A200T-2FBG484I ដែលជាកម្មសិទ្ធិរបស់ស៊េរី Artix-7 របស់ Xilinx ។ កម្រិតល្បឿនគឺ 2 ហើយកម្រិតសីតុណ្ហភាពគឺជាកម្រិតឧស្សាហកម្ម។ ម៉ូដែលនេះគឺជាកញ្ចប់ FGG484 ដែលមានម្ជុល 484 ។ ច្បាប់ដាក់ឈ្មោះបន្ទះឈីប Xilinx ARTIX-7 FPGA ដូចខាងក្រោម

រូបភាពទី 2-1៖ និយមន័យជាក់លាក់នៃម៉ូដែល Chip នៃស៊េរី ARTIX-7

រូបភាពទី 2-2៖ បន្ទះឈីប FPGA នៅលើយន្តហោះ

ប៉ារ៉ាម៉ែត្រចម្បងនៃបន្ទះឈីប FPGA XC7A200T មានដូចខាងក្រោម

| ឈ្មោះ | ប៉ារ៉ាម៉ែត្រជាក់លាក់ |

| ក្រឡាតក្កវិជ្ជា | 215360 |

| ចំណិត | ៨៦៦-៤៤៧-២១៩៤ |

| ស្បែកជើងផ្ទាត់ CLB | 269200 |

| រារាំង RAM (kb) | 13140 |

| ចំណិត DSP | 740 |

| PCIe Gen2 | 1 |

| XADC | 1 XADC, 12bit, 1Mbps AD |

| ឧបករណ៍បញ្ជូន GTP | 4 GTP, 6.6Gb/s អតិបរមា |

| ល្បឿនថ្នាក់ | -2 |

| កម្រិតសីតុណ្ហភាព | ឧស្សាហកម្ម |

ប្រព័ន្ធផ្គត់ផ្គង់ថាមពល FPGA

ការផ្គត់ផ្គង់ថាមពល Artix-7 FPGA គឺ VCCINT, VCCBRAM, VCCAUX, VCCO, VMGTAVCC និង VMGTAVTT ។ VCCINT គឺជាម្ជុលផ្គត់ផ្គង់ថាមពលស្នូល FPGA ដែលត្រូវការភ្ជាប់ទៅ 1.0V; VCCBRAM គឺជាម្ជុលផ្គត់ផ្គង់ថាមពលរបស់ FPGA Block RAM ភ្ជាប់ទៅ 1.0V; VCCAUX គឺជាម្ជុលផ្គត់ផ្គង់ថាមពលជំនួយ FPGA ភ្ជាប់ 1.8V; VCCO គឺជាវ៉ុលtage នៃធនាគារនីមួយៗនៃ FPGA រួមមាន BANK0, BANK13~16, BANK34~35។ នៅលើបន្ទះស្នូល AC7A200 FPGA BANK34 និង BANK35 ចាំបាច់ត្រូវភ្ជាប់ទៅ DDR3 ដែលជាវ៉ុលtage ការតភ្ជាប់របស់ BANK គឺ 1.5V និងវ៉ុលtage នៃធនាគារផ្សេងទៀតគឺ 3.3V ។ VCCO នៃ BANK15 និង BANK16 ត្រូវបានដំណើរការដោយ LDO ហើយអាចត្រូវបានផ្លាស់ប្តូរដោយការជំនួសបន្ទះឈីប LDO ។ VMGTAVCC គឺជាវ៉ុលផ្គត់ផ្គង់tage នៃឧបករណ៍បញ្ជូន GTP ខាងក្នុង FPGA ភ្ជាប់ទៅ 1.0V; VMGTAVTT គឺជាការបញ្ចប់វ៉ុលtage នៃឧបករណ៍បញ្ជូន GTP ភ្ជាប់ទៅ 1.2V ។

ប្រព័ន្ធ Artix-7 FPGA តម្រូវឱ្យមានលំដាប់ថាមពលឡើងដោយ VCCINT បន្ទាប់មក VCCBRAM បន្ទាប់មក VCCAUX និងចុងក្រោយ VCCO ។ ប្រសិនបើ VCCINT និង VCCBRAM មានវ៉ុលដូចគ្នា។tage ពួកវាអាចបើកបានក្នុងពេលតែមួយ។ លំដាប់នៃអំណាច outages ត្រូវបានបញ្ច្រាស់។ លំដាប់ថាមពលរបស់ឧបករណ៍បញ្ជូន GTP គឺ VCCINT បន្ទាប់មក VMGTAVCC បន្ទាប់មក VMGTAVTT ។ ប្រសិនបើ VCCINT និង VMGTAVCC មានវ៉ុលដូចគ្នា។tage ពួកវាអាចបើកបានក្នុងពេលតែមួយ។ លំដាប់បិទថាមពលគឺផ្ទុយពីលំដាប់បិទថាមពល។

ផ្នែកទី 3៖ គ្រីស្តាល់ឌីផេរ៉ង់ស្យែលសកម្ម

បន្ទះស្នូល AC7A200 ត្រូវបានបំពាក់ដោយគ្រីស្តាល់ឌីផេរ៉ង់ស្យែលសកម្ម Sitime ពីរដែលមួយគឺ 200MHz ម៉ូដែលគឺ SiT9102-200.00MHz ដែលជានាឡិកាសំខាន់របស់ប្រព័ន្ធសម្រាប់ FPGA និងប្រើដើម្បីបង្កើតនាឡិកាបញ្ជា DDR3 ។ មួយទៀតគឺ 125MHz ម៉ូដែលគឺ SiT9102 -125MHz ការបញ្ចូលនាឡិកាយោងសម្រាប់ឧបករណ៍បញ្ជូន GTP ។

ផ្នែកទី 3.1: 200Mhz នាឡិកាឌីផេរ៉ង់ស្យែលសកម្ម

G1 នៅក្នុងរូបភាពទី 3-1 គឺជាគ្រីស្តាល់ឌីផេរ៉ង់ស្យែលសកម្ម 200M ដែលផ្តល់ប្រភពនាឡិកាប្រព័ន្ធក្រុមប្រឹក្សាអភិវឌ្ឍន៍។ ទិន្នផលគ្រីស្តាល់ត្រូវបានភ្ជាប់ទៅម្ជុលនាឡិកាសកល BANK34 MRCC (R4 និង T4) នៃ FPGA ។ នាឡិកាឌីផេរ៉ង់ស្យែល 200Mhz នេះអាចត្រូវបានប្រើដើម្បីជំរុញតក្កវិជ្ជាអ្នកប្រើប្រាស់នៅក្នុង FPGA ។ អ្នកប្រើប្រាស់អាចកំណត់រចនាសម្ព័ន្ធ PLLs និង DCMs នៅខាងក្នុង FPGA ដើម្បីបង្កើតនាឡិកានៃប្រេកង់ផ្សេងៗគ្នា។

រូបភាពទី 3-1: 200Mhz Active Differential Crystal Schematic

រូបភាពទី 3-2: 200Mhz Active Differential Crystal នៅលើបន្ទះស្នូល

ការចាត់ចែងម្ជុលនាឡិកាឌីផេរ៉ង់ស្យែល 200Mhz

| ឈ្មោះសញ្ញា | លេខសម្ងាត់ FPGA |

| SYS_CLK_P | R4 |

| SYS_CLK_N | T4 |

ផ្នែកទី 3.2៖ គ្រីស្តាល់ឌីផេរ៉ង់ស្យែលសកម្ម 125MHz

G2 នៅក្នុងរូបភាពទី 3-3 គឺជាគ្រីស្តាល់ឌីផេរ៉ង់ស្យែលសកម្ម 125MHz ដែលជានាឡិកាបញ្ចូលយោងដែលផ្តល់ទៅឱ្យម៉ូឌុល GTP នៅខាងក្នុង FPGA ។ ទិន្នផលគ្រីស្តាល់ត្រូវបានភ្ជាប់ទៅម្ជុលនាឡិកា GTP BANK216 MGTREFCLK0P (F6) និង MGTREFCLK0N (E6) នៃ FPGA ។

រូបភាពទី 3-3: 125MHz Active Differential Crystal Schematic

រូបភាពទី 3-4: 125MHz Active Differential Crystal នៅលើបន្ទះស្នូល

125MHz ការចាត់ចែងម្ជុលនាឡិកាឌីផេរ៉ង់ស្យែល

| ឈ្មោះសុទ្ធ | លេខសម្ងាត់ FPGA |

| MGT_CLK0_P | F6 |

| MGT_CLK0_N | E6 |

ផ្នែកទី 4៖ DDR3 DRAM

បន្ទះស្នូល FPGA AC7A200 ត្រូវបានបំពាក់ដោយបន្ទះឈីប Micron 4Gbit (512MB) DDR3 ចំនួនពីរ (8Gbit សរុប) ម៉ូដែលគឺ MT41J256M16HA-125 (អាចប្រើបានជាមួយ MT41K256M16HA-125) ។ DDR3 SDRAM មានល្បឿនប្រតិបត្តិការអតិបរមា 400MHz (អត្រាទិន្នន័យ 800Mbps)។ ប្រព័ន្ធអង្គចងចាំ DDR3 ត្រូវបានភ្ជាប់ដោយផ្ទាល់ទៅចំណុចប្រទាក់អង្គចងចាំរបស់ BANK 34 និង BANK35 នៃ FPGA ។ ការកំណត់រចនាសម្ព័ន្ធជាក់លាក់នៃ DDR3 SDRAM ត្រូវបានបង្ហាញនៅក្នុងតារាង 4-1 ។

| លេខប៊ីត | ម៉ូដែលបន្ទះឈីប | សមត្ថភាព | រោងចក្រ |

| U5,U6 | MT41J256M16HA-125 | 256M x 16 ប៊ីត | មីក្រូន |

តារាង 4-1៖ ការកំណត់រចនាសម្ព័ន្ធ DDR3 SDRAM

ការរចនាផ្នែករឹងនៃ DDR3 តម្រូវឱ្យមានការពិចារណាយ៉ាងតឹងរឹងអំពីភាពត្រឹមត្រូវនៃសញ្ញា។ យើងបានពិចារណាយ៉ាងពេញលេញនូវការផ្គូផ្គង resistor/terminal resistance, trace impedance control, និង trace length control in circuit design and PCB design ដើម្បីធានាបាននូវប្រតិបត្តិការដែលមានល្បឿនលឿន និងស្ថេរភាពនៃ DDR3 ។ រូបភាពទី 4-1 លម្អិតអំពីការភ្ជាប់ផ្នែករឹងរបស់ DDR3 DRAM

រូបភាពទី 4-1៖ គ្រោងការណ៍ DDR3 DRAM

រូបភាពទី 4-2៖ DDR3 នៅលើ Core Board

ការកំណត់ម្ជុល DDR3 DRAM៖

| ឈ្មោះសុទ្ធ | ឈ្មោះ FPGA PIN | FPGA P/N |

| DDR3_DQS0_P | IO_L3P_T0_DQS_AD5P_35 | E1 |

| DDR3_DQS0_N | IO_L3N_T0_DQS_AD5N_35 | D1 |

| DDR3_DQS1_P | IO_L9P_T1_DQS_AD7P_35 | K2 |

| DDR3_DQS1_N | IO_L9N_T1_DQS_AD7N_35 | J2 |

| DDR3_DQS2_P | IO_L15P_T2_DQS_35 | M1 |

| DDR3_DQS2_N | IO_L15N_T2_DQS_35 | L1 |

| DDR3_DQS3_P | IO_L21P_T3_DQS_35 | P5 |

| DDR3_DQS3_N | IO_L21N_T3_DQS_35 | P4 |

| DDR3_DQ[0] | IO_L2P_T0_AD12P_35 | C2 |

| DDR3_DQ [1] | IO_L5P_T0_AD13P_35 | G1 |

| DDR3_DQ [2] | IO_L1N_T0_AD4N_35 | A1 |

| DDR3_DQ [3] | IO_L6P_T0_35 | F3 |

| DDR3_DQ [4] | IO_L2N_T0_AD12N_35 | B2 |

| DDR3_DQ [5] | IO_L5N_T0_AD13N_35 | F1 |

| DDR3_DQ [6] | IO_L1P_T0_AD4P_35 | B1 |

| DDR3_DQ [7] | IO_L4P_T0_35 | E2 |

| DDR3_DQ [8] | IO_L11P_T1_SRCC_35 | H3 |

| DDR3_DQ [9] | IO_L11N_T1_SRCC_35 | G3 |

| DDR3_DQ [10] | IO_L8P_T1_AD14P_35 | H2 |

| DDR3_DQ [11] | IO_L10N_T1_AD15N_35 | H5 |

| DDR3_DQ [12] | IO_L7N_T1_AD6N_35 | J1 |

| DDR3_DQ [13] | IO_L10P_T1_AD15P_35 | J5 |

| DDR3_DQ [14] | IO_L7P_T1_AD6P_35 | K1 |

| DDR3_DQ [15] | IO_L12P_T1_MRCC_35 | H4 |

| DDR3_DQ [16] | IO_L18N_T2_35 | L4 |

| DDR3_DQ [17] | IO_L16P_T2_35 | M3 |

| DDR3_DQ [18] | IO_L14P_T2_SRCC_35 | L3 |

| DDR3_DQ [19] | IO_L17N_T2_35 | J6 |

| DDR3_DQ [20] | IO_L14N_T2_SRCC_35 | K3 |

| DDR3_DQ [21] | IO_L17P_T2_35 | K6 |

| DDR3_DQ [22] | IO_L13N_T2_MRCC_35 | J4 |

| DDR3_DQ [23] | IO_L18P_T2_35 | L5 |

| DDR3_DQ [24] | IO_L20N_T3_35 | P1 |

| DDR3_DQ [25] | IO_L19P_T3_35 | N4 |

| DDR3_DQ [26] | IO_L20P_T3_35 | R1 |

| DDR3_DQ [27] | IO_L22N_T3_35 | N2 |

| DDR3_DQ [28] | IO_L23P_T3_35 | M6 |

| DDR3_DQ [29] | IO_L24N_T3_35 | N5 |

| DDR3_DQ [30] | IO_L24P_T3_35 | P6 |

| DDR3_DQ [31] | IO_L22P_T3_35 | P2 |

| DDR3_DM0 | IO_L4N_T0_35 | D2 |

| DDR3_DM1 | IO_L8N_T1_AD14N_35 | G2 |

| DDR3_DM2 | IO_L16N_T2_35 | M2 |

| DDR3_DM3 | IO_L23N_T3_35 | M5 |

| DDR3_A[0] | IO_L11N_T1_SRCC_34 | AA ៦ |

| DDR3_A[1] | IO_L8N_T1_34 | AB2 |

| DDR3_A[2] | IO_L10P_T1_34 | AA ៦ |

| DDR3_A[3] | IO_L10N_T1_34 | AB5 |

| DDR3_A[4] | IO_L7N_T1_34 | AB1 |

| DDR3_A[5] | IO_L6P_T0_34 | U3 |

| DDR3_A[6] | IO_L5P_T0_34 | W1 |

| DDR3_A[7] | IO_L1P_T0_34 | T1 |

| DDR3_A[8] | IO_L2N_T0_34 | V2 |

| DDR3_A[9] | IO_L2P_T0_34 | U2 |

| DDR3_A[10] | IO_L5N_T0_34 | Y1 |

| DDR3_A[11] | IO_L4P_T0_34 | W2 |

| DDR3_A[12] | IO_L4N_T0_34 | Y2 |

| DDR3_A[13] | IO_L1N_T0_34 | U1 |

| DDR3_A[14] | IO_L6N_T0_VREF_34 | V3 |

| DDR3_BA[0] | IO_L9N_T1_DQS_34 | AA ៦ |

| DDR3_BA[1] | IO_L9P_T1_DQS_34 | Y3 |

| DDR3_BA[2] | IO_L11P_T1_SRCC_34 | Y4 |

| DDR3_S0 | IO_L8P_T1_34 | AB3 |

| DDR3_RAS | IO_L12P_T1_MRCC_34 | V4 |

| DDR3_CAS | IO_L12N_T1_MRCC_34 | W4 |

| DDR3_WE | IO_L7P_T1_34 | AA ៦ |

| DDR3_ODT | IO_L14N_T2_SRCC_34 | U5 |

| DDR3_RESET | IO_L15P_T2_DQS_34 | W6 |

| DDR3_CLK_P | IO_L3P_T0_DQS_34 | R3 |

| DDR3_CLK_N | IO_L3N_T0_DQS_34 | R2 |

| DDR3_CKE | IO_L14P_T2_SRCC_34 | T5 |

ផ្នែកទី 5: QSPI Flash

បន្ទះស្នូល FPGA AC7A200 ត្រូវបានបំពាក់ដោយ 128Mbit QSPI FLASH ហើយម៉ូដែលគឺ N25Q128 ដែលប្រើវ៉ុល 3.3V CMOStagអ៊ីស្តង់ដារ។ ដោយសារតែលក្ខណៈមិនប្រែប្រួលនៃ QSPI FLASH វាអាចត្រូវបានប្រើជាឧបករណ៍ចាប់ផ្ដើមសម្រាប់ប្រព័ន្ធដើម្បីរក្សាទុករូបភាពចាប់ផ្ដើមនៃប្រព័ន្ធ។ រូបភាពទាំងនេះភាគច្រើនរួមបញ្ចូល FPGA ប៊ីត files, កូដកម្មវិធី ARM, កូដកម្មវិធីស្នូលទន់ និងទិន្នន័យអ្នកប្រើប្រាស់ផ្សេងទៀត។ fileស. ម៉ូដែលជាក់លាក់ និងប៉ារ៉ាម៉ែត្រពាក់ព័ន្ធនៃ SPI FLASH ត្រូវបានបង្ហាញក្នុងតារាង 5-1 ។

| មុខតំណែង | គំរូ | សមត្ថភាព | រោងចក្រ |

| U8 | N25Q128 | 128M ប៊ីត | ណូម៉ូនីក |

តារាង 5-1: លក្ខណៈបច្ចេកទេស QSPI FLASH

QSPI FLASH ត្រូវបានភ្ជាប់ទៅម្ជុលពិសេសរបស់ BANK0 និង BANK14 នៃបន្ទះឈីប FPGA ។ ម្ជុលនាឡិកាត្រូវបានភ្ជាប់ទៅ CCLK0 នៃ BANK0 ហើយទិន្នន័យ និងសញ្ញាជ្រើសរើសបន្ទះឈីបផ្សេងទៀតត្រូវបានភ្ជាប់ទៅម្ជុល D00~D03 និង FCS របស់ BANK14 រៀងគ្នា។ រូបភាព 5-1 បង្ហាញពីការតភ្ជាប់ផ្នែករឹងរបស់ QSPI Flash ។

រូបភាពទី 5-1៖ គ្រោងការណ៍ QSPI Flash

ការចាត់តាំង QSPI Flash pin៖

| ឈ្មោះសុទ្ធ | ឈ្មោះ FPGA PIN | FPGA P/N |

| QSPI_CLK | CCLK_0 | L12 |

| QSPI_CS | IO_L6P_T0_FCS_B_14 | T19 |

| QSPI_DQ0 | IO_L1P_T0_D00_MOSI_14 | P22 |

| QSPI_DQ1 | IO_L1N_T0_D01_DIN_14 | R22 |

| QSPI_DQ2 | IO_L2P_T0_D02_14 | P21 |

| QSPI_DQ3 | IO_L2N_T0_D03_14 | R21 |

រូបភាពទី 5-2៖ QSPI FLASH នៅលើបន្ទះស្នូល

ផ្នែកទី 6: អំពូល LED នៅលើបន្ទះស្នូល

មានភ្លើង LED ពណ៌ក្រហមចំនួន 3 នៅលើបន្ទះស្នូល AC7A200 FPGA ដែលមួយជាភ្លើងសញ្ញាបង្ហាញថាមពល (PWR) មួយគឺអំពូល LED កំណត់រចនាសម្ព័ន្ធ (DONE) និងមួយទៀតជាអំពូល LED អ្នកប្រើប្រាស់។ នៅពេលដែលបន្ទះស្នូលត្រូវបានផ្តល់ថាមពលសូចនាករថាមពលនឹងបំភ្លឺ; នៅពេលដែល FPGA ត្រូវបានកំណត់រចនាសម្ព័ន្ធ LED នឹងបំភ្លឺ។ អំពូល LED របស់អ្នកប្រើប្រាស់ត្រូវបានភ្ជាប់ទៅ IO របស់ BANK34 អ្នកប្រើប្រាស់អាចគ្រប់គ្រងពន្លឺបើក និងបិទដោយកម្មវិធី។ នៅពេលដែល IO voltage បានភ្ជាប់ទៅ LED របស់អ្នកប្រើគឺខ្ពស់ LED អ្នកប្រើប្រាស់ត្រូវបានបំភ្លឺ។ នៅពេលដែលការតភ្ជាប់ IO voltage ទាប អ្នកប្រើប្រាស់ LED នឹងត្រូវបានពន្លត់។ ដ្យាក្រាមគ្រោងការណ៍នៃការតភ្ជាប់ផ្នែករឹងរបស់អំពូល LED ត្រូវបានបង្ហាញក្នុងរូបភាព 6-1:

រូបភាពទី 6-1: អំពូល LED នៅលើគ្រោងក្តារស្នូល

រូបភាពទី 6-2: អំពូល LED នៅលើបន្ទះស្នូល

ការកំណត់ម្ជុល LEDs អ្នកប្រើប្រាស់

| ឈ្មោះសញ្ញា | ឈ្មោះម្ជុល FPGA | លេខ PIN FPGA | ការពិពណ៌នា |

| LED1 ។ | IO_L15N_T2_DQS_34 | W5 | LED អ្នកប្រើប្រាស់ |

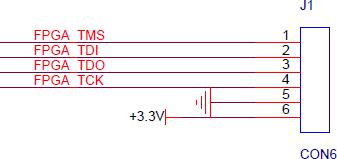

ផ្នែកទី 7: JTAG ចំណុចប្រទាក់

លោក JTAG រន្ធតេស្ត J1 ត្រូវបានបម្រុងទុកនៅលើក្តារស្នូល AC7A200 សម្រាប់ JTAG ទាញយក និងបំបាត់កំហុស នៅពេលដែលបន្ទះស្នូលត្រូវបានប្រើតែម្នាក់ឯង។ រូបភាពទី 7-1 គឺជាផ្នែកគ្រោងការណ៍នៃ JTAG ច្រកដែលពាក់ព័ន្ធនឹង TMS, TDI, TDO, TCK ។ , GND, +3.3V សញ្ញាទាំងប្រាំមួយ។

រូបភាពទី 7-1: JTAG គ្រោងការណ៍ចំណុចប្រទាក់

លោក JTAG ចំណុចប្រទាក់ J1 នៅលើ AC7A200 FPGA core board ប្រើរន្ធ 6-pin 2.54mm pitch single-row test hole។ ប្រសិនបើអ្នកត្រូវការប្រើ JTAG ឧបករណ៍ភ្ជាប់ដើម្បីបំបាត់កំហុសនៅលើក្តារស្នូល អ្នកត្រូវលក់ក្បាលម្ជុលជួរដេកតែមួយ 6-pin ។

រូបភាព 7-2 បង្ហាញ JTAG ចំណុចប្រទាក់ J1 នៅលើបន្ទះស្នូល AC7A200 FPGA ។

រូបភាព 7-2 JTAG ចំណុចប្រទាក់នៅលើ Core Board

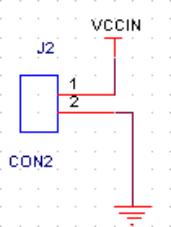

ផ្នែកទី 8៖ ចំណុចប្រទាក់ថាមពលនៅលើបន្ទះស្នូល

ដើម្បីធ្វើឱ្យបន្ទះស្នូល AC7A200 FPGA ដំណើរការតែម្នាក់ឯង បន្ទះស្នូលត្រូវបានបម្រុងទុក 2-pin power supply interface J2 ។ ប្រសិនបើអ្នកប្រើចង់បំបាត់កំហុសមុខងាររបស់បន្ទះស្នូលដោយឡែកពីគ្នា (ដោយគ្មានបន្ទះក្រុមហ៊ុនដឹកជញ្ជូន) ឧបករណ៍ខាងក្រៅត្រូវផ្តល់ +5V ដើម្បីផ្គត់ផ្គង់ថាមពលទៅបន្ទះស្នូល។

រូបភាពទី 8-1៖ គ្រោងការណ៍ចំណុចប្រទាក់ថាមពលនៅលើបន្ទះស្នូល

រូបភាពទី 8-2: ចំណុចប្រទាក់ថាមពលនៅលើបន្ទះស្នូល

ផ្នែកទី 9: ការចាត់តាំង pin board to Board Connectors

បន្ទះស្នូលមានបន្ទះភ្ជាប់ល្បឿនលឿនសរុបចំនួន 4 ទៅកាន់ឧបករណ៍ភ្ជាប់ក្តារ។

បន្ទះស្នូលប្រើឧបករណ៍ភ្ជាប់អន្តរក្តារចំនួន 80-pin ចំនួនបួនដើម្បីភ្ជាប់ទៅក្រុមប្រឹក្សាភិបាល។ ច្រក IO នៃ FPGA ត្រូវបានភ្ជាប់ទៅឧបករណ៍ភ្ជាប់ទាំងបួនដោយការបញ្ជូនតាមឌីផេរ៉ង់ស្យែល។ គម្លាត pin នៃឧបករណ៍ភ្ជាប់គឺ 0.5mm បញ្ចូលទៅក្តារដើម្បីភ្ជាប់ board board នៅលើ carrier board សម្រាប់ការទំនាក់ទំនងទិន្នន័យល្បឿនលឿន។

Board to Board Connectors CON1

បន្ទះ 80-pin to board connectors CON1 ដែលត្រូវបានប្រើដើម្បីភ្ជាប់ជាមួយការផ្គត់ផ្គង់ថាមពល VCCIN (+5V) និងដីនៅលើបន្ទះ carrier ពង្រីក IOs ធម្មតារបស់ FPGA ។ គួរកត់សំគាល់នៅទីនេះថា 15 pins នៃ CON1 ត្រូវបានភ្ជាប់ទៅច្រក IO នៃ BANK34 ព្រោះការភ្ជាប់ BANK34 ត្រូវបានភ្ជាប់ទៅ DDR3។ ដូច្នេះ វ៉ុលtage ស្តង់ដារនៃ IOs ទាំងអស់នៃ BANK34 នេះគឺ 1.5V ។

Pin Assignment of Board to Board Connectors CON1

| CON១០១ លេខសម្ងាត់ |

សុទ្ធ ឈ្មោះ |

FPGA លេខសម្ងាត់ |

វ៉ុលtage កម្រិត |

CON១០១ លេខសម្ងាត់ |

សុទ្ធ ឈ្មោះ |

FPGA លេខសម្ងាត់ |

វ៉ុលtage កម្រិត |

| លេខកូដ PIN1 | VCCIN | – | +5V | លេខកូដ PIN2 | VCCIN | – | +5V |

| លេខកូដ PIN3 | VCCIN | – | +5V | លេខកូដ PIN4 | VCCIN | – | +5V |

| លេខកូដ PIN5 | VCCIN | – | +5V | លេខកូដ PIN6 | VCCIN | – | +5V |

| លេខកូដ PIN7 | VCCIN | – | +5V | លេខកូដ PIN8 | VCCIN | – | +5V |

| លេខកូដ PIN9 | GND | – | ដី | លេខកូដ PIN10 | GND | – | ដី |

| លេខកូដ PIN11 | NC | – | NC | លេខកូដ PIN12 | NC | – | NC |

| លេខកូដ PIN13 | NC | – | NC | លេខកូដ PIN14 | NC | – | NC |

| លេខកូដ PIN15 | NC | – | NC | លេខកូដ PIN16 | B13_L4_P | AA ៦ | 3.3V |

| លេខកូដ PIN17 | NC | – | NC | លេខកូដ PIN18 | B13_L4_N | AB15 | 3.3V |

| លេខកូដ PIN19 | GND | – | ដី | លេខកូដ PIN20 | GND | – | ដី |

| លេខកូដ PIN21 | B13_L5_P | Y13 | 3.3V | លេខកូដ PIN22 | B13_L1_P | Y16 | 3.3V |

| លេខកូដ PIN23 | B13_L5_N | AA ៦ | 3.3V | លេខកូដ PIN24 | B13_L1_N | AA ៦ | 3.3V |

| លេខកូដ PIN25 | B13_L7_P | AB11 | 3.3V | លេខកូដ PIN26 | B13_L2_P | AB16 | 3.3V |

| លេខកូដ PIN27 | B13_L7_P | AB12 | 3.3V | លេខកូដ PIN28 | B13_L2_N | AB17 | 3.3V |

| លេខកូដ PIN29 | GND | – | ដី | លេខកូដ PIN30 | GND | – | ដី |

| លេខកូដ PIN31 | B13_L3_P | AA ៦ | 3.3V | លេខកូដ PIN32 | B13_L6_P | W14 | 3.3V |

| លេខកូដ PIN33 | B13_L3_N | AB13 | 3.3V | លេខកូដ PIN34 | B13_L6_N | Y14 | 3.3V |

| លេខកូដ PIN35 | B34_L23_P | Y8 | 1.5V | លេខកូដ PIN36 | B34_L20_P | AB7 | 1.5V |

| លេខកូដ PIN37 | B34_L23_N | Y7 | 1.5V | លេខកូដ PIN38 | B34_L20_N | AB6 | 1.5V |

| លេខកូដ PIN39 | GND | – | ដី | លេខកូដ PIN40 | GND | – | ដី |

| លេខកូដ PIN41 | B34_L18_N | AA ៦ | 1.5V | លេខកូដ PIN42 | B34_L21_N | V8 | 1.5V |

| លេខកូដ PIN43 | B34_L18_P | Y6 | 1.5V | លេខកូដ PIN44 | B34_L21_P | V9 | 1.5V |

| លេខកូដ PIN45 | B34_L19_P | V7 | 1.5V | លេខកូដ PIN46 | B34_L22_P | AA ៦ | 1.5V |

| លេខកូដ PIN47 | B34_L19_N | W7 | 1.5V | លេខកូដ PIN48 | B34_L22_N | AB8 | 1.5V |

| លេខកូដ PIN49 | GND | – | ដី | លេខកូដ PIN50 | GND | – | ដី |

| លេខកូដ PIN51 | XADC_VN | M9 | អាណាឡូក | លេខកូដ PIN52 | NC | ||

| លេខកូដ PIN53 | XADC_VP | L10 | អាណាឡូក | លេខកូដ PIN54 | B34_L25 | U7 | 1.5V |

| លេខកូដ PIN55 | NC | – | NC | លេខកូដ PIN56 | B34_L24_P | W9 | 1.5V |

| លេខកូដ PIN57 | NC | – | NC | លេខកូដ PIN58 | B34_L24_N | Y9 | 1.5V |

| លេខកូដ PIN59 | GND | – | ដី | លេខកូដ PIN60 | GND | – | ដី |

| លេខកូដ PIN61 | B16_L1_N | F14 | 3.3V | លេខកូដ PIN62 | NC | – | NC |

| លេខកូដ PIN63 | B16_L1_P | F13 | 3.3V | លេខកូដ PIN64 | NC | – | NC |

| លេខកូដ PIN65 | B16_L4_N | អ៊ី២៦ | 3.3V | លេខកូដ PIN66 | NC | – | NC |

| លេខកូដ PIN67 | B16_L4_P | អ៊ី២៦ | 3.3V | លេខកូដ PIN68 | NC | – | NC |

| លេខកូដ PIN69 | GND | – | ដី | លេខកូដ PIN70 | GND | – | ដី |

| លេខកូដ PIN71 | B16_L6_N | D15 | 3.3V | លេខកូដ PIN72 | NC | – | NC |

| លេខកូដ PIN73 | B16_L6_P | D14 | 3.3V | លេខកូដ PIN74 | NC | – | NC |

| លេខកូដ PIN75 | B16_L8_P | C13 | 3.3V | លេខកូដ PIN76 | NC | – | NC |

| លេខកូដ PIN77 | B16_L8_N | B13 | 3.3V | លេខកូដ PIN78 | NC | – | NC |

| លេខកូដ PIN79 | NC | – | NC | លេខកូដ PIN80 | NC | – | NC |

រូបភាព 9-1: Board to Board Connectors CON1 នៅលើ Core Board

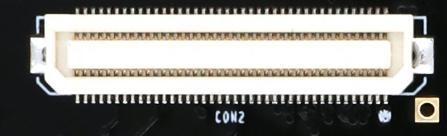

Board to Board Connectors CON2

ក្បាលការតភ្ជាប់ស្រី 80-pin CON2 ត្រូវបានប្រើដើម្បីពង្រីក IO ធម្មតានៃ BANK13 និង BANK14 នៃ FPGA ។ វ៉ុលtagស្តង់ដារ e នៃធនាគារទាំងពីរគឺ 3.3V ។

Pin Assignment of Board to Board Connectors CON2

| CON១០១ លេខសម្ងាត់ |

សុទ្ធ ឈ្មោះ |

FPGA លេខសម្ងាត់ |

វ៉ុលtage កម្រិត |

CON១០១ លេខសម្ងាត់ |

សុទ្ធ ឈ្មោះ |

FPGA លេខសម្ងាត់ |

វ៉ុលtage កម្រិត |

| លេខកូដ PIN1 | B13_L16_P | W15 | 3.3V | លេខកូដ PIN2 | B14_L16_P | វី៣៥ | 3.3V |

| លេខកូដ PIN3 | B13_L16_N | W16 | 3.3V | លេខកូដ PIN4 | B14_L16_N | W17 | 3.3V |

| លេខកូដ PIN5 | B13_L15_P | T14 | 3.3V | លេខកូដ PIN6 | B13_L14_P | U15 | 3.3V |

| លេខកូដ PIN7 | B13_L15_N | T15 | 3.3V | លេខកូដ PIN8 | B13_L14_N | វី៣៥ | 3.3V |

| លេខកូដ PIN9 | GND | – | ដី | លេខកូដ PIN10 | GND | – | ដី |

| លេខកូដ PIN11 | B13_L13_P | វី៣៥ | 3.3V | លេខកូដ PIN12 | B14_L10_P | AB21 | 3.3V |

| លេខកូដ PIN13 | B13_L13_N | វី៣៥ | 3.3V | លេខកូដ PIN14 | B14_L10_N | AB22 | 3.3V |

| លេខកូដ PIN15 | B13_L12_P | W11 | 3.3V | លេខកូដ PIN16 | B14_L8_N | AA ៦ | 3.3V |

| លេខកូដ PIN17 | B13_L12_N | W12 | 3.3V | លេខកូដ PIN18 | B14_L8_P | AA ៦ | 3.3V |

| លេខកូដ PIN19 | GND | – | ដី | លេខកូដ PIN20 | GND | – | ដី |

| លេខកូដ PIN21 | B13_L11_P | Y11 | 3.3V | លេខកូដ PIN22 | B14_L15_N | AB20 | 3.3V |

| លេខកូដ PIN23 | B13_L11_N | Y12 | 3.3V | លេខកូដ PIN24 | B14_L15_P | AA ៦ | 3.3V |

| លេខកូដ PIN25 | B13_L10_P | វី៣៥ | 3.3V | លេខកូដ PIN26 | B14_L17_P | AA ៦ | 3.3V |

| លេខកូដ PIN27 | B13_L10_N | W10 | 3.3V | លេខកូដ PIN28 | B14_L17_N | AB18 | 3.3V |

| លេខកូដ PIN29 | GND | – | ដី | លេខកូដ PIN30 | GND | – | ដី |

| លេខកូដ PIN31 | B13_L9_N | AA ៦ | 3.3V | លេខកូដ PIN32 | B14_L6_N | T20 | 3.3V |

| លេខកូដ PIN33 | B13_L9_P | AA ៦ | 3.3V | លេខកូដ PIN34 | B13_IO0 | Y17 | 3.3V |

| លេខកូដ PIN35 | B13_L8_N | AB10 | 3.3V | លេខកូដ PIN36 | B14_L7_N | W22 | 3.3V |

| លេខកូដ PIN37 | B13_L8_P | AA ៦ | 3.3V | លេខកូដ PIN38 | B14_L7_P | W21 | 3.3V |

| លេខកូដ PIN39 | GND | – | ដី | លេខកូដ PIN40 | GND | – | ដី |

| លេខកូដ PIN41 | B14_L11_N | វី៣៥ | 3.3V | លេខកូដ PIN42 | B14_L4_P | T21 | 3.3V |

| លេខកូដ PIN43 | B14_L11_P | U20 | 3.3V | លេខកូដ PIN44 | B14_L4_N | U21 | 3.3V |

| លេខកូដ PIN45 | B14_L14_N | វី៣៥ | 3.3V | លេខកូដ PIN46 | B14_L9_P | Y21 | 3.3V |

| លេខកូដ PIN47 | B14_L14_P | វី៣៥ | 3.3V | លេខកូដ PIN48 | B14_L9_N | Y22 | 3.3V |

| លេខកូដ PIN49 | GND | – | ដី | លេខកូដ PIN50 | GND | – | ដី |

| លេខកូដ PIN51 | B14_L5_N | R19 | 3.3V | លេខកូដ PIN52 | B14_L12_N | W20 | 3.3V |

| លេខកូដ PIN53 | B14_L5_P | P19 | 3.3V | លេខកូដ PIN54 | B14_L12_P | W19 | 3.3V |

| លេខកូដ PIN55 | B14_L18_N | U18 | 3.3V | លេខកូដ PIN56 | B14_L13_N | Y19 | 3.3V |

| លេខកូដ PIN57 | B14_L18_P | U17 | 3.3V | លេខកូដ PIN58 | B14_L13_P | Y18 | 3.3V |

| លេខកូដ PIN59 | GND | – | ដី | លេខកូដ PIN60 | GND | – | ដី |

| លេខកូដ PIN61 | B13_L17_P | T16 | 3.3V | លេខកូដ PIN62 | B14_L3_N | វី៣៥ | 3.3V |

| លេខកូដ PIN63 | B13_L17_N | U16 | 3.3V | លេខកូដ PIN64 | B14_L3_P | U22 | 3.3V |

| លេខកូដ PIN65 | B14_L21_N | P17 | 3.3V | លេខកូដ PIN66 | B14_L20_N | T18 | 3.3V |

| លេខកូដ PIN67 | B14_L21_P | N17 | 3.3V | លេខកូដ PIN68 | B14_L20_P | R18 | 3.3V |

| លេខកូដ PIN69 | GND | – | ដី | លេខកូដ PIN70 | GND | – | ដី |

| លេខកូដ PIN71 | B14_L22_P | P15 | 3.3V | លេខកូដ PIN72 | B14_L19_N | R14 | 3.3V |

| លេខកូដ PIN73 | B14_L22_N | R16 | 3.3V | លេខកូដ PIN74 | B14_L19_P | P14 | 3.3V |

| លេខកូដ PIN75 | B14_L24_N | R17 | 3.3V | លេខកូដ PIN76 | B14_L23_P | N13 | 3.3V |

| លេខកូដ PIN77 | B14_L24_P | P16 | 3.3V | លេខកូដ PIN78 | B14_L23_N | N14 | 3.3V |

| លេខកូដ PIN79 | B14_IO0 | P20 | 3.3V | លេខកូដ PIN80 | B14_IO25 | N15 | 3.3V |

រូបភាព 9-2: Board to Board Connectors CON2 នៅលើ Core Board

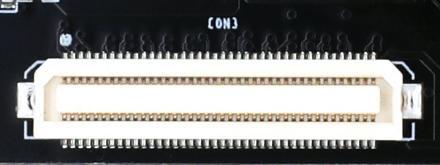

Board to Board Connectors CON3

ឧបករណ៍ភ្ជាប់ 80-pin CON3 ត្រូវបានប្រើដើម្បីពង្រីក IO ធម្មតានៃ BANK15 និង BANK16 នៃ FPGA ។ លើសពីនេះទៀត JTAG សញ្ញាក៏ត្រូវបានភ្ជាប់ទៅក្រុមប្រឹក្សាភិបាលតាមរយៈឧបករណ៍ភ្ជាប់ CON3 ។ វ៉ុលtagស្តង់ដារ e របស់ BANK15 និង BANK16 អាចត្រូវបានកែតម្រូវដោយបន្ទះឈីប LDO ។ LDO ដែលបានដំឡើងលំនាំដើមគឺ 3.3V ។ ប្រសិនបើអ្នកចង់បញ្ចេញកម្រិតស្តង់ដារផ្សេងទៀត អ្នកអាចជំនួសវាដោយ LDO ដែលសមរម្យ។

Pin Assignment of Board to Board Connectors CON3

| CON១០១ លេខសម្ងាត់ |

សុទ្ធ ឈ្មោះ |

FPGA លេខសម្ងាត់ |

វ៉ុលtage កម្រិត |

CON១០១ លេខសម្ងាត់ |

សុទ្ធ ឈ្មោះ |

FPGA លេខសម្ងាត់ |

វ៉ុលtage កម្រិត |

| លេខកូដ PIN1 | B15_IO0 | J16 | 3.3V | លេខកូដ PIN2 | B15_IO25 | M17 | 3.3V |

| លេខកូដ PIN3 | B16_IO0 | F15 | 3.3V | លេខកូដ PIN4 | B16_IO25 | F21 | 3.3V |

| លេខកូដ PIN5 | B15_L4_P | G17 | 3.3V | លេខកូដ PIN6 | B16_L21_N | ក៣១ | 3.3V |

| លេខកូដ PIN7 | B15_L4_N | G18 | 3.3V | លេខកូដ PIN8 | B16_L21_P | B21 | 3.3V |

| លេខកូដ PIN9 | GND | – | ដី | លេខកូដ PIN10 | GND | – | ដី |

| លេខកូដ PIN11 | B15_L2_P | G15 | 3.3V | លេខកូដ PIN12 | B16_L23_P | អ៊ី២៦ | 3.3V |

| លេខកូដ PIN13 | B15_L2_N | G16 | 3.3V | លេខកូដ PIN14 | B16_L23_N | D21 | 3.3V |

| លេខកូដ PIN15 | B15_L12_P | J19 | 3.3V | លេខកូដ PIN16 | B16_L22_P | អ៊ី២៦ | 3.3V |

| លេខកូដ PIN17 | B15_L12_N | H19 | 3.3V | លេខកូដ PIN18 | B16_L22_N | D22 | 3.3V |

| លេខកូដ PIN19 | GND | – | ដី | លេខកូដ PIN20 | GND | – | ដី |

| លេខកូដ PIN21 | B15_L11_P | J20 | 3.3V | លេខកូដ PIN22 | B16_L24_P | G21 | 3.3V |

| លេខកូដ PIN23 | B15_L11_N | J21 | 3.3V | លេខកូដ PIN24 | B16_L24_N | G22 | 3.3V |

| លេខកូដ PIN25 | B15_L1_N | G13 | 3.3V | លេខកូដ PIN26 | B15_L8_N | G20 | 3.3V |

| លេខកូដ PIN27 | B15_L1_P | H13 | 3.3V | លេខកូដ PIN28 | B15_L8_P | H20 | 3.3V |

| លេខកូដ PIN29 | GND | – | ដី | លេខកូដ PIN30 | GND | – | ដី |

| លេខកូដ PIN31 | B15_L5_P | J15 | 3.3V | លេខកូដ PIN32 | B15_L7_N | H22 | 3.3V |

| លេខកូដ PIN33 | B15_L5_N | H15 | 3.3V | លេខកូដ PIN34 | B15_L7_P | J22 | 3.3V |

| លេខកូដ PIN35 | B15_L3_N | H14 | 3.3V | លេខកូដ PIN36 | B15_L9_P | K៦៥៦ | 3.3V |

| លេខកូដ PIN37 | B15_L3_P | J14 | 3.3V | លេខកូដ PIN38 | B15_L9_N | K៦៥៦ | 3.3V |

| លេខកូដ PIN39 | GND | – | ដី | លេខកូដ PIN40 | GND | – | ដី |

| លេខកូដ PIN41 | B15_L19_P | K៦៥៦ | 3.3V | លេខកូដ PIN42 | B15_L15_N | M22 | 3.3V |

| លេខកូដ PIN43 | B15_L19_N | K៦៥៦ | 3.3V | លេខកូដ PIN44 | B15_L15_P | N22 | 3.3V |

| លេខកូដ PIN45 | B15_L20_P | M13 | 3.3V | លេខកូដ PIN46 | B15_L6_N | H18 | 3.3V |

| លេខកូដ PIN47 | B15_L20_N | L13 | 3.3V | លេខកូដ PIN48 | B15_L6_P | H17 | 3.3V |

| លេខកូដ PIN49 | GND | – | ដី | លេខកូដ PIN50 | GND | – | ដី |

| លេខកូដ PIN51 | B15_L14_P | L19 | 3.3V | លេខកូដ PIN52 | B15_L13_N | K៦៥៦ | 3.3V |

| លេខកូដ PIN53 | B15_L14_N | L20 | 3.3V | លេខកូដ PIN54 | B15_L13_P | K៦៥៦ | 3.3V |

| លេខកូដ PIN55 | B15_L21_P | K៦៥៦ | 3.3V | លេខកូដ PIN56 | B15_L10_P | M21 | 3.3V |

| លេខកូដ PIN57 | B15_L21_N | J17 | 3.3V | លេខកូដ PIN58 | B15_L10_N | L21 | 3.3V |

| លេខកូដ PIN59 | GND | – | ដី | លេខកូដ PIN60 | GND | – | ដី |

| លេខកូដ PIN61 | B15_L23_P | L16 | 3.3V | លេខកូដ PIN62 | B15_L18_P | N20 | 3.3V |

| លេខកូដ PIN63 | B15_L23_N | K៦៥៦ | 3.3V | លេខកូដ PIN64 | B15_L18_N | M20 | 3.3V |

| លេខកូដ PIN65 | B15_L22_P | L14 | 3.3V | លេខកូដ PIN66 | B15_L17_N | N19 | 3.3V |

| លេខកូដ PIN67 | B15_L22_N | L15 | 3.3V | លេខកូដ PIN68 | B15_L17_P | N18 | 3.3V |

| លេខកូដ PIN69 | GND | – | ដី | លេខកូដ PIN70 | GND | – | ដី |

| លេខកូដ PIN71 | B15_L24_P | M15 | 3.3V | លេខកូដ PIN72 | B15_L16_P | M18 | 3.3V |

| លេខកូដ PIN73 | B15_L24_N | M16 | 3.3V | លេខកូដ PIN74 | B15_L16_N | L18 | 3.3V |

| លេខកូដ PIN75 | NC | – | លេខកូដ PIN76 | NC | – | ||

| លេខកូដ PIN77 | FPGA_TCK | វី៣៥ | 3.3V | លេខកូដ PIN78 | FPGA_TDI | R13 | 3.3V |

| លេខកូដ PIN79 | FPGA_TDO | U13 | 3.3V | លេខកូដ PIN80 | FPGA_TMS | T13 | 3.3V |

រូបភាព 9-3: Board to Board Connectors CON3 នៅលើ Core Board

Board to Board Connectors CON4

ឧបករណ៍ភ្ជាប់ 80-Pin CON4 ត្រូវបានប្រើដើម្បីពង្រីកទិន្នន័យល្បឿនខ្ពស់ IO និង GTP ធម្មតា និងសញ្ញានាឡិការបស់ FPGA BANK16។ វ៉ុលtage ស្តង់ដារនៃច្រក IO នៃ BANK16 អាចត្រូវបានកែតម្រូវដោយបន្ទះឈីប LDO ។ LDO ដែលបានដំឡើងលំនាំដើមគឺ 3.3V ។ ប្រសិនបើអ្នកប្រើចង់បញ្ចេញកម្រិតស្តង់ដារផ្សេងទៀត វាអាចត្រូវបានជំនួសដោយ LDO ដែលសមរម្យ។ ទិន្នន័យល្បឿនលឿន និងសញ្ញានាឡិការបស់ GTP ត្រូវបានបញ្ជូនតាមឌីផេរ៉ង់ស្យែលយ៉ាងតឹងរ៉ឹងនៅលើបន្ទះស្នូល។ ខ្សែទិន្នន័យមានប្រវែងស្មើគ្នា និងរក្សាទុកនៅចន្លោះពេលជាក់លាក់មួយដើម្បីការពារការជ្រៀតជ្រែកនៃសញ្ញា។

Pin Assignment of Board to Board Connectors CON4

| CON១០១ លេខសម្ងាត់ |

សុទ្ធ ឈ្មោះ |

FPGA លេខសម្ងាត់ |

វ៉ុលtage កម្រិត |

CON១០១ លេខសម្ងាត់ |

សុទ្ធ ឈ្មោះ |

FPGA លេខសម្ងាត់ |

វ៉ុលtage កម្រិត |

| លេខកូដ PIN1 | NC | – | – | លេខកូដ PIN2 | – | – | |

| លេខកូដ PIN3 | NC | – | – | លេខកូដ PIN4 | – | – | |

| លេខកូដ PIN5 | NC | – | – | លេខកូដ PIN6 | – | – | |

| លេខកូដ PIN7 | NC | – | – | លេខកូដ PIN8 | – | – | |

| លេខកូដ PIN9 | GND | – | ដី | លេខកូដ PIN10 | GND | – | ដី |

| លេខកូដ PIN11 | NC | – | – | លេខកូដ PIN12 | MGT_TX2_P | B6 | ភាពខុសគ្នា |

| លេខកូដ PIN13 | NC | – | – | លេខកូដ PIN14 | MGT_TX2_N | A6 | ភាពខុសគ្នា |

| លេខកូដ PIN15 | GND | – | ដី | លេខកូដ PIN16 | GND | – | ដី |

| លេខកូដ PIN17 | MGT_TX3_P | D7 | ភាពខុសគ្នា | លេខកូដ PIN18 | MGT_RX2_P | B10 | ភាពខុសគ្នា |

| លេខកូដ PIN19 | MGT_TX3_N | C7 | ភាពខុសគ្នា | លេខកូដ PIN20 | MGT_RX2_N | ក៣១ | ភាពខុសគ្នា |

| លេខកូដ PIN21 | GND | – | ដី | លេខកូដ PIN22 | GND | – | ដី |

| លេខកូដ PIN23 | MGT_RX3_P | D9 | ភាពខុសគ្នា | លេខកូដ PIN24 | MGT_TX0_P | B4 | ភាពខុសគ្នា |

| លេខកូដ PIN25 | MGT_RX3_N | C9 | ភាពខុសគ្នា | លេខកូដ PIN26 | MGT_TX0_N | A4 | ភាពខុសគ្នា |

| លេខកូដ PIN27 | GND | – | ដី | លេខកូដ PIN28 | GND | – | ដី |

| លេខកូដ PIN29 | MGT_TX1_P | D5 | ភាពខុសគ្នា | លេខកូដ PIN30 | MGT_RX0_P | B8 | ភាពខុសគ្នា |

| លេខកូដ PIN31 | MGT_TX1_N | C5 | ភាពខុសគ្នា | លេខកូដ PIN32 | MGT_RX0_N | A8 | ភាពខុសគ្នា |

| លេខកូដ PIN33 | GND | – | ដី | លេខកូដ PIN34 | GND | – | ដី |

| លេខកូដ PIN35 | MGT_RX1_P | D11 | ភាពខុសគ្នា | លេខកូដ PIN36 | MGT_CLK1_P | F10 | ភាពខុសគ្នា |

| លេខកូដ PIN37 | MGT_RX1_N | C11 | ភាពខុសគ្នា | លេខកូដ PIN38 | MGT_CLK1_N | អ៊ី២៦ | ភាពខុសគ្នា |

| លេខកូដ PIN39 | GND | – | ដី | លេខកូដ PIN40 | GND | – | ដី |

| លេខកូដ PIN41 | B16_L5_P | អ៊ី២៦ | 3.3V | លេខកូដ PIN42 | B16_L2_P | F16 | 3.3V |

| លេខកូដ PIN43 | B16_L5_N | D16 | 3.3V | លេខកូដ PIN44 | B16_L2_N | អ៊ី២៦ | 3.3V |

| លេខកូដ PIN45 | B16_L7_P | B15 | 3.3V | លេខកូដ PIN46 | B16_L3_P | C14 | 3.3V |

| លេខកូដ PIN47 | B16_L7_N | B16 | 3.3V | លេខកូដ PIN48 | B16_L3_N | C15 | 3.3V |

| លេខកូដ PIN49 | GND | – | ដី | លេខកូដ PIN50 | GND | – | ដី |

| លេខកូដ PIN51 | B16_L9_P | ក៣១ | 3.3V | លេខកូដ PIN52 | B16_L10_P | ក៣១ | 3.3V |

| លេខកូដ PIN53 | B16_L9_N | ក៣១ | 3.3V | លេខកូដ PIN54 | B16_L10_N | ក៣១ | 3.3V |

| លេខកូដ PIN55 | B16_L11_P | B17 | 3.3V | លេខកូដ PIN56 | B16_L12_P | D17 | 3.3V |

| លេខកូដ PIN57 | B16_L11_N | B18 | 3.3V | លេខកូដ PIN58 | B16_L12_N | C17 | 3.3V |

| លេខកូដ PIN59 | GND | – | ដី | លេខកូដ PIN60 | GND | – | ដី |

| លេខកូដ PIN61 | B16_L13_P | C18 | 3.3V | លេខកូដ PIN62 | B16_L14_P | អ៊ី២៦ | 3.3V |

| លេខកូដ PIN63 | B16_L13_N | C19 | 3.3V | លេខកូដ PIN64 | B16_L14_N | D19 | 3.3V |

| លេខកូដ PIN65 | B16_L15_P | F18 | 3.3V | លេខកូដ PIN66 | B16_L16_P | B20 | 3.3V |

| លេខកូដ PIN67 | B16_L15_N | អ៊ី២៦ | 3.3V | លេខកូដ PIN68 | B16_L16_N | ក៣១ | 3.3V |

| លេខកូដ PIN69 | GND | – | ដី | លេខកូដ PIN70 | GND | – | ដី |

| លេខកូដ PIN71 | B16_L17_P | ក៣១ | 3.3V | លេខកូដ PIN72 | B16_L18_P | F19 | 3.3V |

| លេខកូដ PIN73 | B16_L17_N | ក៣១ | 3.3V | លេខកូដ PIN74 | B16_L18_N | F20 | 3.3V |

| លេខកូដ PIN75 | B16_L19_P | D20 | 3.3V | លេខកូដ PIN76 | B16_L20_P | C22 | 3.3V |

| លេខកូដ PIN77 | B16_L19_N | C20 | 3.3V | លេខកូដ PIN78 | B16_L20_N | B22 | 3.3V |

| លេខកូដ PIN79 | NC | – | លេខកូដ PIN80 | NC | – |

រូបភាព 9-4: Board to Board Connectors CON4 នៅលើ Core Board

ផ្នែកទី 10៖ ការផ្គត់ផ្គង់ថាមពល

បន្ទះស្នូល AC7A200 FPGA ត្រូវបានបំពាក់ដោយ DC5V តាមរយៈបន្ទះក្រុមហ៊ុនដឹកជញ្ជូន ហើយវាត្រូវបានបំពាក់ដោយចំណុចប្រទាក់ Mini USB នៅពេលវាប្រើតែម្នាក់ឯង។ សូមប្រយ័ត្នកុំផ្គត់ផ្គង់ថាមពលដោយ Mini USB និងបន្ទះក្រុមហ៊ុនដឹកជញ្ជូនក្នុងពេលតែមួយ ដើម្បីជៀសវាងការខូចខាត។ ដ្យាក្រាមរចនាការផ្គត់ផ្គង់ថាមពលនៅលើក្តារត្រូវបានបង្ហាញក្នុងរូបភាព 10-1 ។

រូបភាពទី 10-1: ការផ្គត់ផ្គង់ថាមពលនៅលើក្តារស្នូល

បន្ទះស្នូលត្រូវបានបំពាក់ដោយ +5V និងបំប្លែងទៅជា +3.3V, +1.5V, +1.8V, +1.0V ការផ្គត់ផ្គង់ថាមពលបួនផ្លូវតាមរយៈបន្ទះឈីបផ្គត់ផ្គង់ថាមពល DC/DC ចំនួនបី TLV62130RGT ។ ចរន្តនៃ +1.0V អាចឡើងដល់ 6A ហើយចរន្តទិន្នផលបីផ្សេងទៀតអាចឡើងដល់ 3A។ VCCIO ត្រូវបានបង្កើតឡើងដោយ LDOSPX3819M5-3-3 មួយ។ VCCIO ផ្គត់ផ្គង់ថាមពលជាចម្បងដល់ BANK15 និង BANK16 នៃ FPGA ។ អ្នកប្រើប្រាស់អាចផ្លាស់ប្តូរ IO នៃ BANK15,16 ទៅជាវ៉ុលផ្សេងគ្នាtage ស្តង់ដារដោយការជំនួសបន្ទះឈីប LDO របស់ពួកគេ។ 1.5V បង្កើតវ៉ុល VTT និង VREFtagតម្រូវដោយ DDR3 តាមរយៈ TPS51200 របស់ TI។ ការផ្គត់ផ្គង់ថាមពល 1.8V នៃ MGTAVTT និង MGTAVCC សម្រាប់ឧបករណ៍បញ្ជូន GTP ត្រូវបានបង្កើតឡើងដោយបន្ទះឈីប TPS74801 របស់ TI ។ មុខងារនៃការចែកចាយថាមពលនីមួយៗត្រូវបានបង្ហាញក្នុងតារាងខាងក្រោម៖

| ការផ្គត់ផ្គង់ថាមពល | មុខងារ |

| +1.0V | វ៉ុលស្នូល FPGAtage |

| +1.8V | លេខជំនួយ FPGAtage, ការផ្គត់ផ្គង់ថាមពល TPS74801 |

| +3.3V | VCCIO នៃ Bank0, Bank13 និង Bank14 នៃ FPGA, QSIP FLASH, Clock Crystal |

| +1.5V | DDR3, Bank34 និង Bank35 នៃ FPGA |

| VREF,VTT(+0.75V) | DDR3 |

| CCIP(+3.3V) | ធនាគារ FPGA 15, ធនាគារ 16 |

| MGTAVTT(+1.2V) | GTP Transceiver Bank216 នៃ FPGA |

| MGTVCC(+1.0V) | GTP Transceiver Bank216 នៃ FPGA |

ដោយសារតែការផ្គត់ផ្គង់ថាមពលរបស់ Artix-7 FPGA មានតំរូវការតាមលំដាប់នៃការបើកថាមពល នៅក្នុងការរចនាសៀគ្វី យើងបានរចនាទៅតាមតម្រូវការថាមពលរបស់បន្ទះឈីប ហើយការបើកថាមពលគឺ 1.0V->1.8V->(1.5 V, 3.3V, VCCIO) និង 1.0V-> MGTAVCC -> MGTAVTT ការរចនាសៀគ្វីដើម្បីធានាបាននូវប្រតិបត្តិការធម្មតារបស់បន្ទះឈីប។

សៀគ្វីថាមពលនៅលើបន្ទះស្នូល AC7A200 FPGA ត្រូវបានបង្ហាញក្នុងរូបភាព 10-2៖

រូបភាពទី 10-2៖ ការផ្គត់ផ្គង់ថាមពលនៅលើ AC7A200 FPGA Core Board

ផ្នែកទី 11: វិមាត្រទំហំ

រូបភាពទី 11-1: AC7A200 FPGA Core board (កំពូល View)

រូបភាពទី 11-2: បន្ទះស្នូល AC7A200 FPGA (បាត View)

ឯកសារ/ធនធាន

|

ក្រុមប្រឹក្សាអភិវឌ្ឍន៍ ALINX AC7A200 ARTIX-7 FPGA [pdf] សៀវភៅណែនាំអ្នកប្រើប្រាស់ ក្រុមប្រឹក្សាអភិវឌ្ឍន៍ AC7A200 ARTIX-7 FPGA, AC7A200, ក្រុមប្រឹក្សាអភិវឌ្ឍន៍ ARTIX-7 FPGA, ក្រុមប្រឹក្សាអភិវឌ្ឍន៍ FPGA, ក្រុមប្រឹក្សាអភិវឌ្ឍន៍, ក្រុមប្រឹក្សាភិបាល |