UM11942

UM11942

Warstwa instrukcji PN5190

Kontroler interfejsu NFC

Instrukcja obsługi

PN5190 Kontroler interfejsu NFC

Informacje o dokumencie

| Informacja | Treść |

| Słowa kluczowe | PN5190, NFC, front-end NFC, kontroler, warstwa instrukcji |

| Abstrakcyjny | W tym dokumencie opisano polecenia warstwy instrukcji i odpowiedzi do pracy z kontrolera hosta, w celu oceny działania kontrolera front-end NXP PN5190 NFC. PN5190 to kontroler front-end NFC nowej generacji. Zakres tego dokumentu obejmuje opisanie poleceń interfejsu do pracy z kontrolerem front-end PN5190 NFC. Aby uzyskać więcej informacji na temat działania kontrolera front-end PN5190 NFC, zapoznaj się z arkuszem danych i jego informacjami uzupełniającymi. |

Historia rewizji

| Obrót silnika | Data | Opis |

| 3.7 | 20230525 | • Zmieniono typ i tytuł dokumentu z dodatku do karty danych produktu na instrukcję obsługi • Oczyszczanie redakcyjne • Zaktualizowane warunki redakcyjne dla sygnałów SPI • Dodano polecenie GET_CRC_USER_AREA w Tabeli 8 w Sekcji 4.5.2.3 • Zaktualizowano różne szczegóły różnicowe dla PN5190B1 i PN5190B2 w sekcji 3.4.1 • Zaktualizowana odpowiedź w sekcji 3.4.7 |

| 3.6 | 20230111 | Opis odpowiedzi na ulepszoną kontrolę integralności w sekcji 3.4.7 |

| 3.5 | 20221104 | Sekcja 4.5.4.6.3 „Wydarzenie”: dodano |

| 3.4 | 20220701 | • Dodano polecenie CONFIGURE_MULTIPLE_TESTBUS_DIGITAL w Tabeli 8 w Sekcji 4.5.9.3 • Zaktualizowano sekcję 4.5.9.2.2 |

| 3.3 | 20220329 | Poprawiono opis sprzętu w sekcji 4.5.12.2.1 „Polecenie” i sekcji 4.5.12.2.2 „Odpowiedź” |

| 3.2 | 20210910 | Zaktualizowano numery wersji oprogramowania sprzętowego z 2.1 do 2.01 i z 2.3 do 2.03 |

| 3.1 | 20210527 | Dodano opis polecenia RETRIEVE_RF_FELICA_EMD_DATA |

| 3 | 20210118 | Pierwsza oficjalna wydana wersja |

Wstęp

1.1 Wprowadzenie

W tym dokumencie opisano interfejs hosta PN5190 i interfejsy API. Fizycznym interfejsem hosta używanym w dokumentacji jest SPI. Fizyczna charakterystyka SPI nie jest uwzględniona w dokumencie.

Separacja ramek i kontrola przepływu są częścią tego dokumentu.

1.1.1 Zakres

Dokument opisuje warstwę logiczną, kod instrukcji i interfejsy API istotne dla klienta.

Komunikacja hostaview

PN5190 ma dwa główne tryby pracy umożliwiające komunikację z kontrolerem hosta.

- Komunikacja oparta na protokole HDLL jest wykorzystywana, gdy urządzenie zostanie wywołane w celu wprowadzenia:

a. Tryb szyfrowanego bezpiecznego pobierania w celu aktualizacji oprogramowania układowego - Komunikacja oparta na poleceniach i odpowiedziach TLV (przedstawiona jako przykład)ample).

2.1 Tryb HDLL

Tryb HDLL używany jest do formatu wymiany pakietów, aby mógł współpracować z poniższymi trybami pracy układów scalonych:

- Tryb bezpiecznego pobierania oprogramowania sprzętowego (SFWU), patrz sekcja 3

2.1.1 Opis HDLL

HDLL to warstwa łącza opracowana przez NXP w celu zapewnienia niezawodnego pobierania oprogramowania sprzętowego.

Wiadomość HDLL składa się z 2-bajtowego nagłówka, po którym następuje ramka, zawierająca kod operacji i ładunek polecenia. Każda wiadomość kończy się 16-bitowym CRC, jak opisano na poniższym rysunku: Nagłówek HDLL zawiera:

Nagłówek HDLL zawiera:

- Bit fragmentu. Wskazuje, czy ta wiadomość jest jedynym lub ostatnim fragmentem wiadomości (fragment = 0). Lub czy przynajmniej jeden inny fragment następuje po nim (fragment = 1).

- Długość ładunku zakodowana na 10 bitach. Tak więc ładunek ramki HDLL może mieć do 1023 bajtów.

Kolejność bajtów została zdefiniowana jako big-endian, co oznacza, że najpierw jest bajt.

CRC16 jest zgodny ze standardem X.25 (CRC-CCITT, ISO/IEC13239) z wielomianem x^16 + x^12 + x^5 +1 i wartością wstępnego obciążenia 0xFFFF.

Oblicza się ją dla całej ramki HDLL, tzn. nagłówka i ramki.

SampImplementacja kodu C:

statyczny uint16_t phHal_Host_CalcCrc16(uint8_t* p, uint32_t dwLength)

{

uint32_t i ;

uint16_t crc_new ;

uint16_t crc = 0xffffU;

dla (I = 0; i < dwLength; i++)

{

crc_new = (uint8_t)(crc >> 8) | (crc << 8 );

crc_new ^= p[i];

crc_new ^= (uint8_t)(crc_new & 0xff) >> 4;

crc_new ^= crc_new << 12;

crc_new ^= (crc_new & 0xff) << 5;

crc = crc_nowy;

}

zwrot crc;

}

2.1.2 Mapowanie transportu przez SPI

W przypadku każdego potwierdzenia NTS pierwszym bajtem jest zawsze NAGŁÓWEK (bajt wskazujący przepływ); może to być 0x7F/0xFF w zależności od operacji zapisu/odczytu.

2.1.2.1 Sekwencja zapisu z hosta (kierunek DH => PN5190) 2.1.2.2 Odczyt sekwencji z hosta (kierunek PN5190 => DH)

2.1.2.2 Odczyt sekwencji z hosta (kierunek PN5190 => DH) 2.1.3 Protokół HDLL

2.1.3 Protokół HDLL

HDLL to protokół typu polecenie-odpowiedź. Wszystkie operacje wymienione powyżej są wyzwalane przez określone polecenie i weryfikowane na podstawie odpowiedzi.

Polecenia i odpowiedzi są zgodne ze składnią komunikatów HDLL, polecenie jest wysyłane przez hosta urządzenia, a odpowiedź przez PN5190. Kod operacji wskazuje polecenie i typ odpowiedzi.

Komunikacja oparta na protokole HDLL, używana wyłącznie, gdy PN5190 zostanie uruchomiony w celu przejścia w tryb „Bezpieczne pobieranie oprogramowania sprzętowego”.

2.2 Tryb TLV

TLV oznacza Tag Wartość długości.

2.2.1 Definicja ramki

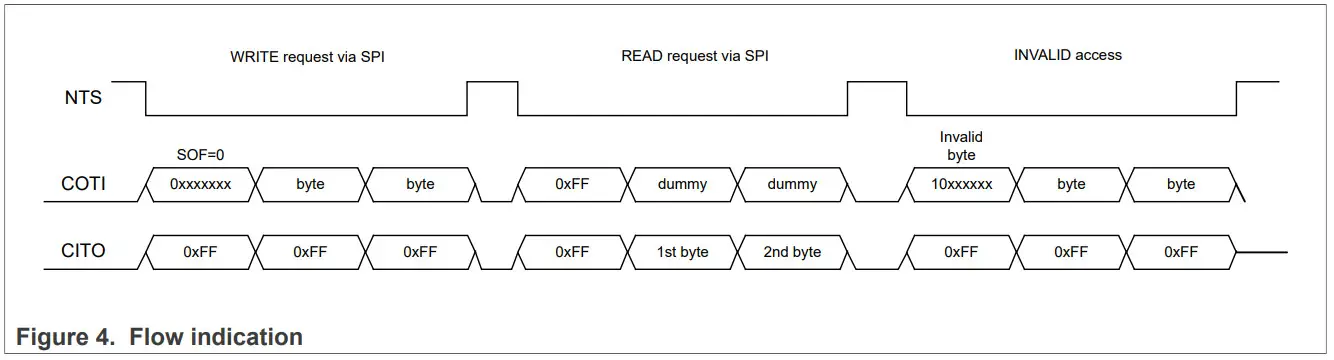

Ramka SPI zaczyna się opadającym zboczem NTS i kończy narastającym zboczem NTS. SPI jest zgodnie z definicją fizyczną pełnym dupleksem, ale PN5190 używa SPI w trybie półdupleksu. Tryb SPI jest ograniczony do CPOL 0 i CPHA 0 z maksymalną prędkością zegara określoną w [2]. Każda ramka SPI składa się z 1-bajtowego nagłówka i n-bajtów treści.

2.2.2 Wskaźnik przepływu HOST zawsze wysyła jako pierwszy bajt bajt wskazujący przepływ, czy chce zapisać, czy odczytać dane z PN5190.

HOST zawsze wysyła jako pierwszy bajt bajt wskazujący przepływ, czy chce zapisać, czy odczytać dane z PN5190.

Jeżeli żądanie odczytu nie zawiera żadnych dostępnych danych, odpowiedź zawiera 0xFF.

Dane następujące po bajcie wskazującym przepływ to jedna lub kilka wiadomości.

W przypadku każdego potwierdzenia NTS pierwszym bajtem jest zawsze NAGŁÓWEK (bajt wskazujący przepływ); może to być 0x7F/0xFF w zależności od operacji zapisu/odczytu.

2.2.3 Typ wiadomości

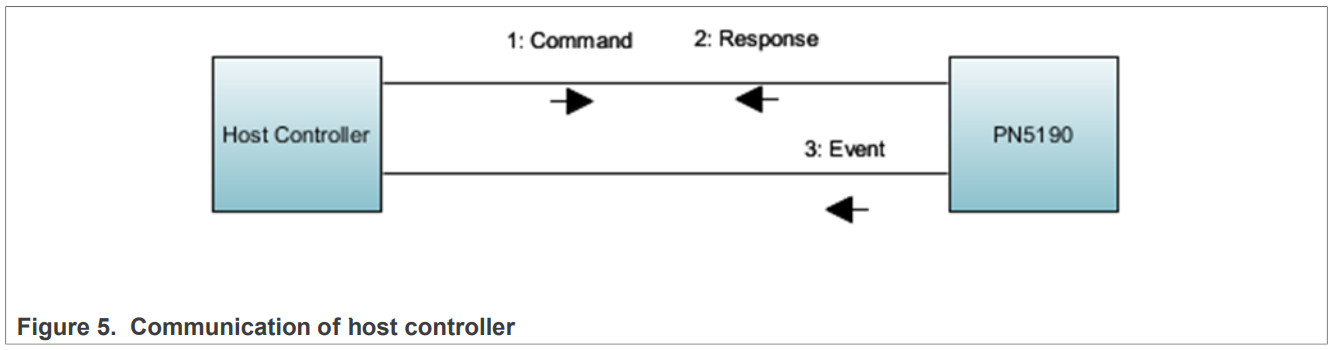

Kontroler hosta powinien komunikować się z PN5190 za pomocą wiadomości transportowanych w ramkach SPI.

Istnieją trzy różne typy wiadomości:

- Rozkaz

- Odpowiedź

- Wydarzenie

Powyższy diagram komunikacji przedstawia dozwolone kierunki dla różnych typów wiadomości, jak poniżej:

Powyższy diagram komunikacji przedstawia dozwolone kierunki dla różnych typów wiadomości, jak poniżej:

- Dowodzenie i reakcja.

- Polecenia są wysyłane tylko z kontrolera hosta do PN5190.

- Odpowiedzi i zdarzenia są wysyłane wyłącznie z PN5190 do kontrolera hosta.

- Odpowiedzi na polecenia są synchronizowane za pomocą pinu IRQ.

- Host może wysyłać polecenia tylko wtedy, gdy IRQ jest niskie.

- Host może odczytać odpowiedź/zdarzenie tylko wtedy, gdy IRQ jest wysokie.

2.2.3.1 Dozwolone sekwencje i reguły Dozwolone sekwencje poleceń, odpowiedzi i zdarzeń

Dozwolone sekwencje poleceń, odpowiedzi i zdarzeń

- Wykonanie polecenia jest zawsze potwierdzane odpowiedzią, zdarzeniem lub jednym i drugim.

- Kontroler hosta nie ma prawa wysłać kolejnego polecenia, dopóki nie otrzyma odpowiedzi na poprzednie polecenie.

- Zdarzenia mogą być wysyłane asynchronicznie w dowolnym momencie (NIE przeplatane w parze polecenie/odpowiedź).

- Wiadomości EVENT nigdy nie są łączone z wiadomościami RESPONSE w jednej ramce.

Notatka: Dostępność komunikatu (RESPONSE lub EVENT) jest sygnalizowana przez przejście IRQ w stan wysoki, od niskiego. IRQ pozostaje wysoki, dopóki nie zostanie odczytana cała ramka odpowiedzi lub zdarzenia. Dopiero gdy sygnał IRQ jest niski, host może wysłać następne polecenie.

2.2.4 Format wiadomości

Każda wiadomość jest kodowana w strukturze TLV z n-bajtowym ładunkiem dla każdej wiadomości, z wyjątkiem polecenia SWITCH_MODE_NORMAL. Każdy TLV składa się z:

Każdy TLV składa się z: Typ (T) => 1 bajt

Typ (T) => 1 bajt

Bit[7] Typ wiadomości

0: Wiadomość COMMAND lub ODPOWIEDŹ

1: Wiadomość ZDARZENIE

Bit[6:0]: Kod instrukcji

Długość (L) => 2 bajty (powinna być w formacie big-endian)

Wartość (V) => N bajtów wartości/danych TLV (parametry polecenia/dane odpowiedzi) w oparciu o pole długości (format big-endian)

2.2.4.1 Podzielona ramka

Wiadomość COMMAND musi zostać wysłana w jednej ramce SPI.

Wiadomości ODPOWIEDZI i ZDARZENIA mogą być odczytywane w wielu ramkach SPI, np. w celu odczytania bajtu długości. Wiadomości ODPOWIEDZI lub ZDARZENIA mogą być odczytywane w pojedynczej ramce SPI, ale opóźniane pomiędzy nimi przez NO-CLOCK, np. w celu odczytania bajtu długości.

Wiadomości ODPOWIEDZI lub ZDARZENIA mogą być odczytywane w pojedynczej ramce SPI, ale opóźniane pomiędzy nimi przez NO-CLOCK, np. w celu odczytania bajtu długości.

Tryb rozruchu operacyjnego IC – bezpieczny tryb pobierania oprogramowania sprzętowego

3.1 Wprowadzenie

Część kodu oprogramowania układowego PN5190 jest trwale przechowywana w pamięci ROM, podczas gdy reszta kodu i danych jest przechowywana w osadzonej pamięci flash. Dane użytkownika są przechowywane w pamięci flash i są chronione przez mechanizmy zapobiegające rozdarciu, które zapewniają integralność i dostępność danych. Aby zapewnić klientom NXP funkcje zgodne z najnowszymi standardami (EMVCo, NFC Forum itd.), zarówno kod, jak i dane użytkownika w pamięci FLASH mogą być aktualizowane.

Autentyczność i integralność zaszyfrowanego oprogramowania sprzętowego jest chroniona przez asymetryczny/symetryczny podpis klucza i mechanizm odwrotnego łańcucha skrótu. Pierwsze polecenie DL_SEC_WRITE zawiera skrót drugiego polecenia i jest chronione przez podpis RSA na ładunku pierwszej ramki. Oprogramowanie sprzętowe PN5190 używa klucza publicznego RSA do uwierzytelnienia pierwszego polecenia. Łańcuch skrótu w każdym poleceniu służy do uwierzytelnienia kolejnego polecenia, aby zapewnić, że kod oprogramowania sprzętowego i dane nie zostaną udostępnione osobom trzecim.

Ładunki poleceń DL_SEC_WRITE są szyfrowane kluczem AES-128. Po uwierzytelnieniu każdego polecenia zawartość ładunku jest odszyfrowywana i zapisywana do pamięci flash przez oprogramowanie układowe PN5190.

W przypadku oprogramowania sprzętowego NXP, firma NXP odpowiada za dostarczanie nowych, bezpiecznych aktualizacji oprogramowania sprzętowego oraz nowych danych użytkownika.

Procedura aktualizacji jest wyposażona w mechanizm chroniący autentyczność, integralność i poufność kodu i danych NXP.

Schemat ramek i pakietów bazujący na HDLL jest używany dla wszystkich poleceń i odpowiedzi w trybie bezpiecznej aktualizacji oprogramowania sprzętowego.

W rozdziale 2.1 podano więcejview użytego schematu pakietu ramki HDLL.

Układy scalone PN5190 obsługują zarówno starszy szyfrowany i bezpieczny protokół pobierania oprogramowania sprzętowego, jak i szyfrowany i bezpieczny protokół pobierania oprogramowania sprzętowego wspomagany sprzętowo, w zależności od użytej wersji.

Istnieją dwa typy:

- Starszy, bezpieczny protokół pobierania oprogramowania sprzętowego, który działa tylko z wersją PN5190 B0/B1 IC.

- Protokół bezpiecznego pobierania oprogramowania sprzętowego wspomagany sprzętowym szyfrowaniem, który działa tylko z wersją układu scalonego PN5190B2, wykorzystującą wbudowane sprzętowe bloki kryptograficzne

Poniższe sekcje wyjaśniają polecenia i odpowiedzi trybu bezpiecznego pobierania oprogramowania sprzętowego.

3.2 Jak uruchomić tryb „Bezpieczne pobieranie oprogramowania układowego”

Poniższy diagram i kolejne kroki pokazują, jak uruchomić tryb bezpiecznego pobierania oprogramowania sprzętowego. Warunek wstępny: PN5190 jest w stanie operacyjnym.

Warunek wstępny: PN5190 jest w stanie operacyjnym.

Główny scenariusz:

- Warunek wejścia, w którym pin DWL_REQ jest używany do wejścia w tryb „Bezpieczne pobieranie oprogramowania sprzętowego”.

a. Urządzenie hosta podnosi pin DWL_REQ do stanu wysokiego (ważne tylko w przypadku bezpiecznej aktualizacji oprogramowania układowego przez pin DWL_REQ) LUB

b. Host urządzenia wykonuje twardy reset w celu uruchomienia PN5190 - Warunek wejścia, w którym pin DWL_REQ nie jest używany do wejścia w tryb „Bezpiecznego pobierania oprogramowania sprzętowego” (pobieranie bez użycia pinu).

a. Host urządzenia wykonuje twardy reset w celu uruchomienia PN5190

b. Host urządzenia wysyła SWITCH_MODE_NORMAL (sekcja 4.5.4.5), aby przejść do normalnego trybu aplikacji.

c. Teraz, gdy IC znajduje się w normalnym trybie aplikacji, host urządzenia wysyła polecenie SWITCH_MODE_DOWNLOAD (sekcja 4.5.4.9), aby przejść do bezpiecznego trybu pobierania. - Urządzenie hosta wysyła polecenie DL_GET_VERSION (sekcja 3.4.4), DL_GET_DIE_ID (sekcja 3.4.6) lub DL_GET_SESSION_STATE (sekcja 3.4.5).

- Host urządzenia odczytuje bieżącą wersję sprzętu i oprogramowania układowego, sesję oraz identyfikator matrycy z urządzenia.

a. Host urządzenia sprawdza stan sesji, jeśli ostatnie pobieranie zostało ukończone

b. Host urządzenia stosuje reguły sprawdzania wersji, aby zdecydować, czy rozpocząć pobieranie, czy je zakończyć. - Urządzenie hosta ładuje się z file kod binarny oprogramowania sprzętowego do pobrania

- Urządzenie hosta udostępnia pierwsze polecenie DL_SEC_WRITE (sekcja 3.4.8), które zawiera:

a. Wersja nowego oprogramowania układowego,

b. 16-bajtowy nonce dowolnych wartości używany do zaciemniania klucza szyfrującego

c. Wartość skrótu następnej klatki,

d. Podpis cyfrowy samej ramki - Urządzenie hostujące ładuje sekwencję protokołu bezpiecznego pobierania do urządzenia PN5190 za pomocą poleceń DL_SEC_WRITE (sekcja 3.4.8)

- Po wysłaniu ostatniego polecenia DL_SEC_WRITE (sekcja 3.4.8) urządzenie hosta wykonuje polecenie DL_CHECK_INTEGRITY (sekcja 3.4.7), aby sprawdzić, czy pamięci zostały pomyślnie zapisane.

- Urządzenie hosta odczytuje nową wersję oprogramowania sprzętowego i sprawdza stan sesji, czy jest zamknięta, w celu przesłania raportu do wyższej warstwy

- Urządzenie hosta ustawia pin DWL_REQ na niski (jeśli pin DWL_REQ jest używany do wejścia w tryb pobierania)

- Host urządzenia wykonuje twardy reset (przełączając pin VEN) na urządzeniu, aby ponownie uruchomić PN5190

Warunek końcowy: Oprogramowanie sprzętowe zostało zaktualizowane; został zgłoszony nowy numer wersji oprogramowania sprzętowego.

3.3 Podpis oprogramowania sprzętowego i kontrola wersji

W trybie pobierania oprogramowania sprzętowego PN5190 mechanizm zapewnia, że tylko oprogramowanie sprzętowe podpisane i dostarczone przez NXP będzie akceptowane jako oprogramowanie sprzętowe NXP.

Poniższe informacje dotyczą wyłącznie szyfrowanego, bezpiecznego oprogramowania sprzętowego NXP.

Podczas sesji pobierania wysyłana jest nowa 16-bitowa wersja oprogramowania sprzętowego. Składa się ona z numeru głównego i numeru podrzędnego:

- Liczba główna: 8 bitów (MSB)

- Liczba drugorzędna: 8 bitów (LSB)

PN5190 sprawdza, czy nowy główny numer wersji jest większy lub równy bieżącemu. Jeśli nie, zabezpieczone pobieranie oprogramowania sprzętowego jest odrzucane, a sesja pozostaje zamknięta.

3.4 Polecenia HDLL dla starszego szyfrowanego pobierania i wspomaganego sprzętowo szyfrowania zaszyfrowane pobieranie

W tej sekcji znajdują się informacje o poleceniach i odpowiedziach użytych w przypadku obu typów pobierania oprogramowania sprzętowego NXP.

3.4.1 Kody OP poleceń HDLL

Notatka: Ramki poleceń HDLL są wyrównane do 4 bajtów. Nieużywane bajty danych są pozostawione jako nil.

Tabela 1. Lista kodów OP poleceń HDLL

| PN5190 B0/ B1 (Pobierz starszą wersję) |

PN5190 B2 (Pobieranie wspomagane przez kryptografię) |

Alias polecenia | Opis |

| 0xF0 | 0xE5 | DL_RESET | Wykonuje miękki reset |

| 0xF1 | 0xE1 | Pobierz wersję DL | Zwraca numery wersji |

| 0xF2 | 0xDB | DL_GET_SESSION_STATATE | Zwraca aktualny stan sesji |

| 0xF4 | 0xDF | DL_GET_DIE_ID | Zwraca identyfikator kostki |

| 0xE0 | 0xE7 | DL_CHECK_INTEGRITY | Sprawdza i zwraca CRC w różnych obszarach, a także flagi statusu zaliczonego/niezaliczonego dla każdego z nich. |

| 0xC0 | 0x8C | DL_SEC_WRITE | Zapisuje x bajtów do pamięci, zaczynając od adresu bezwzględnego y |

3.4.2 Kody operacyjne odpowiedzi HDLL

Notatka: Ramki odpowiedzi HDLL są wyrównane do 4 bajtów. Nieużywane bajty ładunku są pozostawione jako nil. Tylko odpowiedzi DL_OK mogą zawierać wartości ładunku.

Tabela 2. Lista kodów OP odpowiedzi HDLL

| opcode | Alias odpowiedzi | Opis |

| 0x00 | DL_OK | Polecenie przekazane |

| 0x01 | DL_INVALID_ADDR | Adres niedozwolony |

| 0x0B | DL_NIEZNANE_POLECENIE | Nieznane polecenie |

| 0x0C | DL_ANULOWANO_POLECENIE | Sekwencja fragmentów jest zbyt duża |

| 0x1E | Błąd zakresu adresów DL | Adres poza zakresem |

| 0x1F | BŁĄD_BUFORA_DL_OFL | Bufor jest za mały |

| 0x20 | DL_MEM_BSY | Pamięć zajęta |

| 0x21 | BŁĄD_PODPISU_DL | Niezgodność podpisu |

| 0x24 | BŁĄD_WERSJI_OPROGRAMOWANIA_SPRZĘTOWEGO | Obecna wersja równa lub wyższa |

| 0x28 | BŁĄD_PROTOKOŁU_DL | Błąd protokołu |

| 0x2A | DL_SFWU_ZNISZCZONY | Uszkodzenie danych Flash |

| 0x2D | PH_STATUS_DL_PIERWSZY_FRAGMENT | Otrzymano pierwszy kawałek |

| 0x2E | PH_STATUS_DL_NEXT_CHUNK | Poczekaj na następny kawałek |

| 0xC5 | BŁĄD_WEWNĘTRZNY_STATUS_PH_5 | Niezgodność długości |

3.4.3 Polecenie DL_RESET

Wymiana ramek:

PN5190 B0/B1: [HDLL] -> [0x00 0x04 0xF0 0x00 0x00 0x00 0x18 0x5B]

PN5190 B2: [HDLL] -> [0x00 0x04 0xE5 0x00 0x00 0x00 0xBF 0xB9] [HDLL] <- [0x00 0x04 STAT 0x00 CRC16] Reset zapobiega wysłaniu przez PN5190 odpowiedzi DL_STATUS_OK. Dlatego też można odbierać tylko błędne statusy.

STAT jest statusem zwrotu.

3.4.4 Polecenie DL_GET_VERSION

Wymiana ramek:

PN5190 B0/B1: [HDLL] -> [0x00 0x04 0xF1 0x00 0x00 0x00 0x6E 0xEF]

PN5190 B2: [HDLL] -> [0x00 0x04 0xE1 0x00 0x00 0x00 0x75 0x48] [HDLL] <- [0x00 0x08 STAT HW_V RO_V MODEL_ID FM1V FM2V RFU1 RFU2 CRC16] Ramka danych odpowiedzi GetVersion wygląda następująco:

Tabela 3. Odpowiedź na polecenie GetVersion

| Pole | Bajt | Opis |

| STAT | 1 | Status |

| Sprzęt_V | 2 | Wersja sprzętu |

| RO_V | 3 | Kod ROM-u |

| ID_MODELU | 4 | ID modelu |

| FMxV | 5-6 | Wersja oprogramowania sprzętowego (używana do pobrania) |

| RFU1-RFU2 | 7-8 | – |

Oczekiwane wartości różnych pól odpowiedzi i ich mapowanie przedstawiają się następująco:

Tabela 4. Oczekiwane wartości odpowiedzi polecenia GetVersion

| Typ układu scalonego | Wersja HW (hex) | Wersja ROM (hex) | Identyfikator modelu (szesnastkowy) | Wersja FW (hex) |

| PN5190 B0 | 0x51 | 0x02 | 0x00 | xx.yy |

| PN5190 B1 | 0x52 | 0x02 | 0x00 | xx.yy |

| PN5190 B2 | 0x53 | 0x03 | 0x00 | xx.yy |

3.4.5 Polecenie DL_GET_SESSION_STATE

Wymiana ramek:

PN5190 B0/B1: [HDLL] -> [0x00 0x04 0xF2 0x00 0x00 0x00 0xF5 0x33]

PN5190 B2: [HDLL] -> [0x00 0x04 0xDB 0x00 0x00 0x00 0x31 0x0A] [HDLL] <- [0x00 0x04 STAT SSTA RFU CRC16] Ramka danych odpowiedzi GetSession wygląda następująco:

Tabela 5. Odpowiedź na polecenie GetSession

| Pole | Bajt | Opis |

| STAT | 1 | Status |

| SSTA | 2 | Stan sesji • 0x00: zamknięte • 0x01: otwórz • 0x02: zablokowany (dalsze pobieranie nie jest dozwolone) |

| RFU | 3-4 |

3.4.6 Polecenie DL_GET_DIE_ID

Wymiana ramek:

PN5190 B0/B1: [HDLL] -> [0x00 0x04 0xF4 0x00 0x00 0x00 0xD2 0xAA]

PN5190 B2: [HDLL] -> [0x00 0x04 0xDF 0x00 0x00 0x00 0xFB 0xFB] [HDLL] <- [0x00 0x14 STAT 0x00 0x00 0x00 ID0 ID1 ID2 ID3 ID4 ID5 ID6 ID7 ID8 ID9

ID10 ID11 ID12 ID13 ID14 ID15 CRC16] Ramka danych odpowiedzi GetDieId wygląda następująco:

Tabela 6. Odpowiedź na polecenie GetDieId

| Pole | Bajt | Opis |

| STAT | 1 | Status |

| RFU | 2-4 | |

| ZMARŁ | 5-20 | ID kostki (16 bajtów) |

3.4.7 Polecenie DL_CHECK_INTEGRITY

Wymiana ramek:

PN5190 B0/B1: [HDLL] -> [0x00 0x04 0xE0 0x00 0x00 0x00 CRC16]

PN5190 B2: [HDLL] -> [0x00 0x04 0xE7 0x00 0x00 0x00 0x52 0xD1] [HDLL] <- [0x00 0x20 STAT LEN_DATA LEN_CODE 0x00 [CRC_INFO] [CRC32] CRC16] Ramka danych odpowiedzi CheckIntegrity to:

Tabela 7. Odpowiedź na polecenie CheckIntegrity

| Pole | Bajt | Wartość/opis | |

| STAT | 1 | Status | |

| DANE LEN | 2 | Całkowita liczba sekcji danych | |

| KOD LEN | 3 | Całkowita liczba sekcji kodu | |

| RFU | 4 | Skryty | |

| [Informacje o CRC] | 58 | 32 bity (little-endian). Jeśli bit jest ustawiony, CRC odpowiedniej sekcji jest OK, w przeciwnym razie Not OK. | |

| Fragment | Status integralności obszaru | ||

| [31:28] | Zarezerwowane [3] | ||

| [27:23] | Zarezerwowane [1] | ||

| [22] | Zarezerwowane [3] | ||

| [21:20] | Zarezerwowane [1] | ||

| [19] | Obszar konfiguracji RF (PN5190 B0/B1) [2] Zarezerwowany (PN5190 B2) [3] | ||

| [18] | Obszar konfiguracji protokołu (PN5190 B0/B1) [2] Obszar konfiguracji RF (PN5190 B2) [2] | ||

| [17] | Zarezerwowane (PN5190 B0/B1) [3] Obszar konfiguracji użytkownika (PN5190 B2) [2] | ||

| [16:6] | Zarezerwowane [3] | ||

| [5:4] | Zarezerwowane dla PN5190 B0/B1 [3] Zarezerwowane dla PN5190 B2 [1] | ||

| [3:0] | Zarezerwowane [1] | ||

| [CRC32] | 9-136 | CRC32 z 32 sekcji. Każda CRC składa się z 4 bajtów zapisanych w formacie little-endian. Pierwsze 4 bajty CRC to bit CRC_INFO[31], następne 4 bajty CRC to bit CRC_INFO[30] i tak dalej. |

|

- [1] Ten bit musi mieć wartość 1, aby PN5190 działał prawidłowo (z funkcjami i/lub szyfrowanym pobieraniem oprogramowania sprzętowego).

- [2] Ten bit jest domyślnie ustawiony na 1, ale ustawienia zmodyfikowane przez użytkownika unieważniają CRC. Nie ma to wpływu na funkcjonalność PN5190.

- [3] Ta wartość bitowa, nawet jeśli wynosi 0, nie jest istotna. Tę wartość bitową można zignorować.

3.4.8 Polecenie DL_SEC_WRITE

Polecenie DL_SEC_WRITE należy rozpatrywać w kontekście sekwencji bezpiecznych poleceń zapisu: zaszyfrowanego „bezpiecznego pobierania oprogramowania sprzętowego” (często określanego jako eSFWu).

Polecenie Secure Write najpierw otwiera sesję pobierania i przekazuje uwierzytelnianie RSA. Następne przekazują zaszyfrowane adresy i bajty do zapisu w pamięci Flash PN5190. Wszystkie oprócz ostatniego zawierają hash następnego, informując w ten sposób, że nie są ostatnie, i kryptograficznie wiążąc ramki sekwencji.

Inne polecenia (oprócz DL_RESET i DL_CHECK_INTEGRITY) można wstawiać pomiędzy polecenia zapisu zabezpieczonego sekwencji, nie powodując jej przerwania.

3.4.8.1 Pierwsze polecenie DL_SEC_WRITE

Bezpieczne polecenie zapisu jest pierwszym poleceniem wtedy i tylko wtedy, gdy:

- Długość ramki wynosi 312 bajtów

- Od ostatniego resetu nie otrzymano żadnego bezpiecznego polecenia zapisu.

- Podpis osadzony został pomyślnie zweryfikowany przez PN5190.

Odpowiedź na pierwsze polecenie klatki będzie następująca: [HDLL] <- [0x00 0x04 STAT 0x00 0x00 0x00 CRC16] STAT to status zwrotny.

Notatka: Co najmniej jeden fragment danych musi zostać zapisany podczas eSFWu, nawet jeśli zapisane dane mogą mieć długość tylko jednego bajtu. Dlatego pierwsze polecenie zawsze będzie zawierało skrót następnego polecenia, ponieważ będą co najmniej dwa polecenia.

3.4.8.2 Polecenia środkowe DL_SEC_WRITE

Bezpieczne polecenie zapisu jest poleceniem „środkowym” wtedy i tylko wtedy, gdy:

- Kod operacji jest taki, jak opisano w rozdziale 3.4.1 dla polecenia DL_SEC_WRITE.

- Pierwsze bezpieczne polecenie zapisu zostało już odebrane i pomyślnie zweryfikowane

- Od momentu otrzymania pierwszego polecenia bezpiecznego zapisu nie nastąpił żaden reset

- Długość ramki jest równa rozmiarowi danych + rozmiarowi nagłówka + rozmiarowi skrótu: FLEN = ROZMIAR + 6 + 32

- Podsumowanie całej ramki jest równe wartości skrótu otrzymanej w poprzedniej ramce

Odpowiedź na pierwsze polecenie klatki będzie następująca: [HDLL] <- [0x00 0x04 STAT 0x00 0x00 0x00 CRC16] STAT to status zwrotny.

3.4.8.3 Ostatnie polecenie DL_SEC_WRITE

Ostatnie polecenie zapisu jest bezpieczne wtedy i tylko wtedy, gdy:

- Kod operacji jest taki, jak opisano w rozdziale 3.4.1 dla polecenia DL_SEC_WRITE.

- Pierwsze bezpieczne polecenie zapisu zostało już odebrane i pomyślnie zweryfikowane

- Od momentu otrzymania pierwszego polecenia bezpiecznego zapisu nie nastąpił żaden reset

- Długość ramki jest równa rozmiarowi danych + rozmiarowi nagłówka: FLEN = ROZMIAR + 6

- Podsumowanie całej ramki jest równe wartości skrótu otrzymanej w poprzedniej ramce

Odpowiedź na pierwsze polecenie klatki będzie następująca: [HDLL] <- [0x00 0x04 STAT 0x00 0x00 0x00 CRC16] STAT to status zwrotny.

Tryb rozruchu układu scalonego IC – tryb normalnej pracy

4.1 Wprowadzenie

Zazwyczaj układ PN5190 IC musi znajdować się w normalnym trybie pracy, aby można było korzystać z funkcjonalności NFC.

Podczas rozruchu układ PN5190 IC zawsze czeka na otrzymanie poleceń od hosta w celu wykonania operacji, chyba że zdarzenia wygenerowane w układzie PN5190 IC spowodowały rozruch układu PN5190 IC.

4.2 Lista poleceń powyżejview

Tabela 8. Lista poleceń PN5190

| Kod rozkazu | Nazwa polecenia |

| 0x00 | ZAPISZ_REJESTRUJ |

| 0x01 | WRITE_REGISTER_OR_MASK |

| 0x02 | Zapis_rejestru_i_maski |

| 0x03 | WRITE_REGISTER_MULTIPLE |

| 0x04 | CZYTAJ_ZAREJESTRUJ SIĘ |

| 0x05 | REJESTRACJA_WIELOKROTNA |

| 0x06 | Zapisz_E2PROM |

| 0x07 | ODCZYTAJ_E2PROM |

| 0x08 | TRANSMISJA_DANYCH_RF |

| 0x09 | POBIERZ_DANE_RF |

| 0x0A | WYMIANA_DANYCH_RF |

| 0x0B | Uwierzytelnianie MFC |

| 0x0C | EPC_GEN2_INWENTARYZACJA |

| 0x0D | WCZYTAJ KONFIGURACJĘ RF |

| 0x0E | AKTUALIZACJA_KONFIGURACJA_RF |

| 0x0F | POBIERZ_KONFIGURACJĘ_RF |

| 0x10 | RF_WŁĄCZONY |

| 0x11 | RF_WYŁ |

| 0x12 | KONFIGURACJA TESTBUS_DIGITAL |

| 0x13 | KONFIGURACJA_TAG_ANALOGOWA_BUS |

| 0x14 | WŁĄCZENIE CTS |

| 0x15 | KONFIGURACJA CTS |

| 0x16 | Dziennik_powrotu_CTS |

| 0x17-0x18 | RFU |

| 0x19 | do FW v2.01: RFU |

| od wersji FW 2.03: RETRIEVE_RF_FELICA_EMD_DATA | |

| 0x1A | ODBIERZ_DANE_RF |

| 0x1B-0x1F | RFU |

| 0x20 | TRYB_PRZEŁĄCZANIA_NORMALNY |

| 0x21 | AUTOMATYCZNE_PRZEŁĄCZANIE_TRYBU |

| 0x22 | TRYB_PRZEŁĄCZANIA_CZUWANIE |

| 0x23 | TRYB_PRZEŁĄCZANIA_LPCD |

| 0x24 | RFU |

| 0x25 | POBIERANIE_TRYBU_PRZEŁĄCZANIA |

| 0x26 | POBIERZ_ID_ŚMIERCI |

| 0x27 | GET_VERSION |

| 0x28 | RFU |

| 0x29 | do FW v2.05: RFU |

| od wersji FW 2.06: GET_CRC_USER_AREA | |

| 0x2A | do FW v2.03: RFU |

| od wersji FW 2.05: KONFIGURACJA_WIELOKROTNEJ_BUS_TESTOWEJ_CYFROWEJ | |

| 0x2B-0x3F | RFU |

| 0x40 | ANTENNA_SELF_TEST (nieobsługiwane) |

| 0x41 | Test PRBS |

| 0x42-0x4F | RFU |

4.3 Wartości statusu odpowiedzi

Poniżej znajdują się wartości statusu odpowiedzi, które są zwracane jako część odpowiedzi z PN5190 po uruchomieniu polecenia.

Tabela 9. Wartości statusu odpowiedzi PN5190

| Stan odpowiedzi | Wartość statusu odpowiedzi | Opis |

| PN5190_STATUS_POWODZENIE | 0x00 | Oznacza, że operacja zakończyła się pomyślnie |

| PN5190_STATUS_TIMEOUT | 0x01 | Oznacza, że wykonanie polecenia spowodowało przekroczenie limitu czasu |

| PN5190_BŁĄD_INTEGRITY_STATUS | 0x02 | Oznacza, że wykonanie polecenia spowodowało błąd integralności danych RF |

| PN5190_STATUS_RF_COLLISION_ERROR | 0x03 | Oznacza, że wykonanie polecenia spowodowało błąd kolizji RF |

| PN5190_STATUS_RFU1 | 0x04 | Skryty |

| PN5190_STATUS_NIEWAŻNY_POLECENIE | 0x05 | Oznacza, że podane polecenie jest nieprawidłowe/nie zostało zaimplementowane |

| PN5190_STATUS_RFU2 | 0x06 | Skryty |

| PN5190_STATUS_AUTH_ERROR | 0x07 | Oznacza, że uwierzytelnianie MFC nie powiodło się (odmowa dostępu) |

| PN5190_BŁĄD_STATUSU_PAMIĘCI | 0x08 | Oznacza, że wykonanie polecenia spowodowało błąd programowania lub błąd pamięci wewnętrznej |

| PN5190_STATUS_RFU4 | 0x09 | Skryty |

| PN5190_STATUS_NO_RF_FIELD | 0x0A | Oznacza brak lub błąd obecności wewnętrznego pola RF (dotyczy tylko trybu inicjatora/czytnika) |

| PN5190_STATUS_RFU5 | 0x0B | Skryty |

| PN5190_STATUS_SYNTAX_ERROR | 0x0C | Oznacza, że otrzymano nieprawidłową długość ramki polecenia |

| PN5190_BŁĄD_ZASOBU_STATUSU | 0x0D | Oznacza, że wystąpił wewnętrzny błąd zasobu |

| PN5190_STATUS_RFU6 | 0x0E | Skryty |

| PN5190_STATUS_RFU7 | 0x0F | Skryty |

| PN5190_STATUS_NO_EXTERNAL_RF_FIELD | 0x10 | Oznacza, że podczas wykonywania polecenia nie występuje żadne zewnętrzne pole RF (dotyczy tylko trybu karty/celu) |

| PN5190_STATUS_RX_TIMEOUT | 0x11 | Oznacza, że dane nie zostały odebrane po zainicjowaniu RFExchange i upłynął limit czasu odbioru RX. |

| PN5190_STATUS_UŻYTKOWNIK_ANULOWANY | 0x12 | Oznacza, że bieżące polecenie w toku zostało przerwane |

| PN5190_STATUS_PREVENT_STANDBY | 0x13 | Oznacza, że PN5190 nie może przejść w tryb gotowości |

| PN5190_STATUS_RFU9 | 0x14 | Skryty |

| PN5190_BŁĄD_STATUSU_ZEGARA | 0x15 | Oznacza, że zegar do CLIF nie został uruchomiony |

| PN5190_STATUS_RFU10 | 0x16 | Skryty |

| PN5190_STATUS_PRBS_BŁĄD | 0x17 | Oznacza, że polecenie PRBS zwróciło błąd |

| PN5190_BŁĄD_INSTR_STATUS | 0x18 | Oznacza, że wykonanie polecenia nie powiodło się (może to obejmować błąd w parametrach instrukcji, błąd składni, błąd w samej operacji, niespełnione wymagania wstępne dla instrukcji itp.) |

| PN5190_STATUS_DOSTĘP_ODMOWA | 0x19 | Oznacza, że dostęp do pamięci wewnętrznej jest zabroniony |

| PN5190_STATUS_TX_BŁĄD | 0x1A | Oznacza, że TX przez RF nie powiodło się |

| PN5190_STATUS_BEZ_ANTENY | 0x1B | Oznacza, że antena nie jest podłączona/nie ma jej w pobliżu |

| PN5190_STATUS_TXLDO_BŁĄD | 0x1C | Oznacza, że w TXLDO wystąpił błąd, gdy VUP jest niedostępny, a RF jest włączony. |

| PN5190_STATUS_RFCFG_NIE_ZASTOSOWANY | 0x1D | Oznacza, że konfiguracja RF nie jest ładowana po włączeniu RF |

| PN5190_STATUS_TIMEOUT_WITH_EMD_ERROR | 0x1E | do FW 2.01: nieoczekiwane |

| od FW 2.03: Oznacza, że podczas wymiany z ustawionym bitem LOG ENABLE w rejestrze FeliCa EMD zaobserwowano błąd FeliCa EMD |

||

| PN5190_STATUS_BŁĄD_WEWNĘTRZNY | 0x7F | Oznacza, że operacja NVM nie powiodła się |

| PN5190_STATUS_SUKCES_ŁAŃCUCHOWY | 0xAF | Oznacza, że dane oczekują na odczyt |

4.4 Wydarzenia powyżejview

Istnieją dwa sposoby powiadamiania hosta o zdarzeniach.

4.4.1 Zdarzenia normalne na pinie IRQ

Wydarzenia te należą do poniższych kategorii:

- Zawsze włączone – Host jest zawsze powiadamiany

- Sterowane przez hosta – host jest powiadamiany, jeśli odpowiedni bit włączania zdarzeń jest ustawiony w rejestrze (EVENT_ENABLE (01h)).

Przerwania niskiego poziomu z peryferyjnych adresów IP, w tym CLIF, muszą być w całości obsługiwane przez oprogramowanie sprzętowe, a host musi być powiadamiany wyłącznie o zdarzeniach wymienionych w sekcji zdarzeń.

Oprogramowanie sprzętowe implementuje dwa rejestry zdarzeń jako rejestry RAM, które można zapisywać i odczytywać za pomocą poleceń podanych w rozdziale 4.5.1.1/rozdział 4.5.1.5.

Rejestr EVENT_ENABLE (0x01) => Włącz powiadomienia o określonych/wszystkich zdarzeniach.

Rejestr EVENT_STATUS (0x02) => Część ładunku komunikatu zdarzenia.

Zdarzenia zostaną usunięte przez hosta po odczytaniu przez niego komunikatu o zdarzeniu.

Zdarzenia mają charakter asynchroniczny i są powiadamiane o nich hosta, jeżeli zostaną włączone w rejestrze EVENT_ENABLE.

Poniżej znajduje się lista zdarzeń, które będą dostępne dla gospodarza jako część komunikatu o zdarzeniu.

Tabela 10. Wydarzenia PN5190 (zawartość EVENT_STATUS)

| Bit – zakres | Pole [1] | Zawsze Włączone (T/N) | |

| 31 | 12 | RFU | NA |

| 11 | 11 | ZDARZENIE_CTS [2] | N |

| 10 | 10 | ZDARZENIE_BEZCZYNNE | Y |

| 9 | 9 | LPCD_CALIBRATION_DONE_EVENT | Y |

| 8 | 8 | ZDARZENIE_LPCD | Y |

| 7 | 7 | AUTOCOLL_EVENT | Y |

| 6 | 6 | ZDARZENIE_TIMER0 | N |

| 5 | 5 | ZDARZENIE_PRZECIĄŻENIA_TX | N |

| 4 | 4 | RFON_DET_ZDARZENIE [2] | N |

| 3 | 3 | RFOFF_DET_ZDARZENIE [2] | N |

| 2 | 2 | STANDBY_PREV_EVENT | Y |

| 1 | 1 | OGÓLNE_ZDARZENIE_BŁĘDU | Y |

| 0 | 0 | ZDARZENIE_BOOT | Y |

- Należy zauważyć, że nie ma dwóch zdarzeń łączonych, z wyjątkiem błędów. W przypadku błędów podczas operacji, zdarzenie funkcjonalne (np. BOOT_EVENT, AUTOCALL_EVENT itd.) i GENERAL_ERROR_EVENT zostaną ustawione.

- To zdarzenie zostanie automatycznie wyłączone po opublikowaniu go u hosta. Host powinien ponownie włączyć te zdarzenia, jeśli chce, aby były mu o nich powiadamiane.

4.4.1.1 Formaty komunikatów o zdarzeniach

Format komunikatu o zdarzeniu różni się w zależności od wystąpienia zdarzenia i stanu urządzenia PN5190.

Gospodarz musi przeczytać tag (T) i długość wiadomości (L), a następnie odczytaj odpowiadającą jej liczbę bajtów jako wartość (V) zdarzeń.

Ogólnie rzecz biorąc, komunikat zdarzenia (patrz rysunek 12) zawiera parametr EVENT_STATUS zdefiniowany w tabeli 11, a dane zdarzenia odpowiadają odpowiedniemu bitowi zdarzenia ustawionemu w parametrze EVENT_STATUS.

Notatka:

W przypadku niektórych zdarzeń ładunek nie istnieje. Np. jeśli TIMER0_EVENT jest wyzwalany, tylko EVENT_STATUS jest dostarczany jako część komunikatu zdarzenia.

Tabela 11 zawiera także informacje o tym, czy dane zdarzenia są obecne dla odpowiadającego mu zdarzenia w komunikacie zdarzenia. GENERAL_ERROR_EVENT może również wystąpić w połączeniu z innymi zdarzeniami.

GENERAL_ERROR_EVENT może również wystąpić w połączeniu z innymi zdarzeniami.

W tym scenariuszu komunikat zdarzenia (patrz rysunek 13) zawiera parametr EVENT_STATUS zdefiniowany w tabeli 11 i parametr GENERAL_ERROR_STATUS_DATA zdefiniowany w tabeli 14, a następnie dane zdarzenia odpowiadają odpowiedniemu bitowi zdarzenia ustawionemu w parametrze EVENT_STATUS zdefiniowanym w tabeli 11. Notatka:

Notatka:

Dopiero po zdarzeniu BOOT_EVENT lub po POR, STANDBY, ULPCD host będzie mógł pracować w normalnym trybie, wydając polecenia wymienione powyżej.

W przypadku przerwania istniejącego polecenia, dopiero po wystąpieniu zdarzenia IDLE_EVENT, host będzie mógł pracować w normalnym trybie, wydając polecenia wymienione powyżej.

4.4.1.2 Różne definicje statusu ZDARZENIA

4.4.1.2.1 Definicje bitów dla EVENT_STATUS

Tabela 11. Definicje bitów EVENT_STATUS

| Bit (Do – Od) | Wydarzenie | Opis | Dane zdarzenia odpowiadającego zdarzeniu (jeśli istnieje) |

|

| 31 | 12 | RFU | Skryty | |

| 11 | 11 | ZDARZENIE_CTS | Ten bit jest ustawiany, gdy generowane jest zdarzenie CTS. | Tabela 86 |

| 10 | 10 | ZDARZENIE_BEZCZYNNE | Ten bit jest ustawiony, gdy trwające polecenie zostanie anulowane z powodu wydania polecenia SWITCH_MODE_NORMAL. | Brak danych o wydarzeniu |

| 9 | 9 | KALIBRACJA_LPCD_GOTOWA_ WYDARZENIE |

Ten bit jest ustawiany, gdy generowane jest zdarzenie kalibracji LPCD. | Tabela 16 |

| 8 | 8 | ZDARZENIE_LPCD | Ten bit jest ustawiany w momencie wygenerowania zdarzenia LPCD. | Tabela 15 |

| 7 | 7 | AUTOCOLL_EVENT | Ten bit jest ustawiany po zakończeniu operacji AUTOCOLL. | Tabela 52 |

| 6 | 6 | ZDARZENIE_TIMER0 | Ten bit jest ustawiany, gdy wystąpi zdarzenie TIMER0. | Brak danych o wydarzeniu |

| 5 | 5 | BŁĄD_PRZECIĄŻENIA_TX_ WYDARZENIE |

Ten bit jest ustawiony, gdy prąd w sterowniku TX jest wyższy niż zdefiniowany próg w pamięci EEPROM. W takim przypadku pole jest automatycznie wyłączane przed powiadomieniem hosta. Zapoznaj się z sekcją 4.4.2.2. | Brak danych o wydarzeniu |

| 4 | 4 | ZDARZENIE_RFON_DET | Ten bit zostaje ustawiony, gdy zostanie wykryte zewnętrzne pole RF. | Brak danych o wydarzeniu |

| 3 | 3 | ZDARZENIE_RFOFF_DET | Ten bit jest ustawiony, gdy istniejące zewnętrzne pole RF zniknie. | Brak danych o wydarzeniu |

| 2 | 2 | STANDBY_PREV_EVENT | Ten bit jest ustawiony, gdy stan gotowości jest zapobiegawczy ze względu na istniejące warunki zapobiegawcze. | Tabela 13 |

| 1 | 1 | OGÓLNE_ZDARZENIE_BŁĘDU | Ten bit jest ustawiony, gdy występują jakiekolwiek ogólne warunki błędu | Tabela 14 |

| 0 | 0 | ZDARZENIE_BOOT | Ten bit jest ustawiony, gdy PN5190 jest uruchamiany z POR/Standby | Tabela 12 |

4.4.1.2.2 Definicje bitów dla BOOT_STATUS_DATA

Tabela 12. Definicje bitów BOOT_STATUS_DATA

| trochę do | Kawałek z | Stan rozruchu | Powód rozruchu z powodu |

| 31 | 27 | RFU | Skryty |

| 26 | 26 | ULP_STANDBY | Przyczyną rozruchu jest wyjście z ULP_STANDBY. |

| 25 | 23 | RFU | Skryty |

| 22 | 22 | BOOT_ RX_ ULPDET | RX ULPDET spowodował rozruch w trybie gotowości ULP |

| 21 | 21 | RFU | Skryty |

| 20 | 20 | BOOT_SPI | Przyczyną rozruchu jest obniżenie sygnału SPI_NTS |

| 19 | 17 | RFU | Skryty |

| 16 | 16 | Rozruch_GPIO3 | Przyczyną rozruchu jest zmiana stanu GPIO3 z niskiego na wysoki. |

| 15 | 15 | Rozruch_GPIO2 | Przyczyną rozruchu jest zmiana stanu GPIO2 z niskiego na wysoki. |

| 14 | 14 | Rozruch_GPIO1 | Przyczyną rozruchu jest zmiana stanu GPIO1 z niskiego na wysoki. |

| 13 | 13 | Rozruch_GPIO0 | Przyczyną rozruchu jest zmiana stanu GPIO0 z niskiego na wysoki. |

| 12 | 12 | BOOT_LPDET | Przyczyna rozruchu: obecność zewnętrznego pola RF podczas STANDBY/SUSPEND |

| 11 | 11 | RFU | Skryty |

| 10 | 8 | RFU | Skryty |

| 7 | 7 | BOOT_SOFT_RESET | Przyczyna rozruchu: miękki reset układu scalonego |

| 6 | 6 | UTRATA_BOOT_VDDIO | Przyczyna rozruchu z powodu utraty VDDIO. Zobacz sekcję 4.4.2.3 |

| 5 | 5 | BOOT_VDDIO_START | Powód rozruchu, jeśli wprowadzono STANDBY z VDDIO LOSS. Patrz rozdział 4.4.2.3 |

| 4 | 4 | BOOT_WUC | Powód uruchomienia z powodu upływu czasu licznika wybudzeń podczas operacji STANDBY. |

| 3 | 3 | TEMP_ROBOTU | Przyczyna rozruchu z powodu temperatury IC jest wyższa niż skonfigurowany limit progowy. Zapoznaj się z sekcją 4.4.2.1 |

| 2 | 2 | BOOT_WDG | Powód rozruchu z powodu resetu watchdoga |

| 1 | 1 | RFU | Skryty |

| 0 | 0 | Porcja rozruchu | Powód rozruchu: ponowne uruchomienie |

4.4.1.2.3 Definicje bitów dla STANDBY_PREV_STATUS_DATA

Tabela 13. Definicje bitów STANDBY_PREV_STATUS_DATA

| trochę do | Kawałek z | Zapobieganie gotowości | Tryb gotowości zablokowany z powodu |

| 31 | 26 | RFU | SKRYTY |

| 25 | 25 | RFU | SKRYTY |

| 24 | 24 | POPRZEDNIA TEMP. | Temperatura pracy układów scalonych jest poza progiem |

| 23 | 23 | RFU | SKRYTY |

| 22 | 22 | POPRZEDNI_HOSTCOMM | Komunikacja interfejsu hosta |

| 21 | 21 | POPRZEDNI_SPI | Sygnał SPI_NTS jest ściągany w dół |

| 20 | 18 | RFU | SKRYTY |

| 17 | 17 | POPRZEDNI_GPIO3 | Przejście sygnału GPIO3 z niskiego na wysoki |

| 16 | 16 | POPRZEDNI_GPIO2 | Przejście sygnału GPIO2 z niskiego na wysoki |

| 15 | 15 | POPRZEDNI_GPIO1 | Przejście sygnału GPIO1 z niskiego na wysoki |

| 14 | 14 | POPRZEDNI_GPIO0 | Przejście sygnału GPIO0 z niskiego na wysoki |

| 13 | 13 | POPRZEDNI_WUC | Upłynął czas wybudzenia |

| 12 | 12 | POPRZEDNI_LPDET | Wykrywanie niskiego poboru mocy. Występuje, gdy zewnętrzny sygnał RF zostanie wykryty w trakcie przechodzenia w tryb czuwania. |

| 11 | 11 | POPRZEDNIE_RX_ULPDET | Wykrywanie ultraniskiej mocy RX. Występuje, gdy sygnał RF zostanie wykryty w procesie przechodzenia do ULP_STANDBY. |

| 10 | 10 | RFU | SKRYTY |

| 9 | 5 | RFU | SKRYTY |

| 4 | 4 | RFU | SKRYTY |

| 3 | 3 | RFU | SKRYTY |

| 2 | 2 | RFU | SKRYTY |

| 1 | 1 | RFU | SKRYTY |

| 0 | 0 | RFU | SKRYTY |

4.4.1.2.4 Definicje bitów dla GENERAL_ERROR_STATUS_DATA

Tabela 14. Definicje bitów GENERAL_ERROR_STATUS_DATA

| trochę do | Kawałek z | Stan błędu | Opis |

| 31 | 6 | RFU | Skryty |

| 5 | 5 | Błąd startu XTAL | Nieudany start XTAL podczas rozruchu |

| 4 | 4 | BŁĄD_ODZYSKIWANIA_SYS_TRIM | Wystąpił wewnętrzny błąd pamięci trim systemu, ale odzyskiwanie nie powiodło się. System działa w trybie downgrade. |

| 3 | 3 | SYS_TRIM_RECOVERY_POWODZENIE | Wystąpił wewnętrzny błąd pamięci trim systemu, a odzyskiwanie powiodło się. Host musi wykonać restart PN5190, aby odzyskiwanie zostało zastosowane. |

| 2 | 2 | Błąd TXLDO | Błąd TXLDO |

| 1 | 1 | BŁĄD_ZEGARA | Błąd zegara |

| 0 | 0 | Błąd GPADC | Błąd ADC |

4.4.1.2.5 Definicje bitów dla LPCD_STATUS_DATA

Tabela 15. Definicje bajtów LPCD_STATUS_DATA

| trochę do | Kawałek z | Stosowalność bitów stanu zgodnie z podstawową operacją LPCD lub ULPCD | Opis odpowiadającego bitu jest ustawiony w bajcie stanu. | ||

| LCD | ULPCD | ||||

| 31 | 7 | RFU | Skryty | ||

| 6 | 6 | Przerwij_HIF | Y | N | Przerwane z powodu aktywności HIF |

| 5 | 5 | Błąd CLKDET | N | Y | Przerwano z powodu wystąpienia błędu CLKDET |

| 4 | 4 | Przekroczenie limitu czasu XTAL | N | Y | Przerwano z powodu przekroczenia limitu czasu XTAL |

| 3 | 3 | Nadprądowy VDDPA LDO | N | Y | Przerwano z powodu przetężenia VDDPA LDO |

| 2 | 2 | Zewnętrzne pole RF | Y | Y | Przerwane z powodu zewnętrznego pola RF |

| 1 | 1 | Przerwij GPIO3 | N | Y | Przerwane z powodu zmiany poziomu GPIO3 |

| 0 | 0 | Wykryto kartę | Y | Y | Karta została wykryta |

4.4.1.2.6 Definicje bitów dla danych statusu LPCD_CALIBRATION_DONE

Tabela 16. Definicje bajtów danych stanu LPCD_CALIBRATION_DONE dla ULPCD

| trochę do | Kawałek z | Status LPCD_CALIBRATION DONE wydarzenie | Opis odpowiadającego bitu jest ustawiony w bajcie stanu. |

| 31 | 11 | Skryty | |

| 10 | 0 | Wartość odniesienia z kalibracji ULPCD | Zmierzona wartość RSSI podczas kalibracji ULPCD, która jest używana jako punkt odniesienia podczas ULPCD |

Tabela 17. Definicje bajtów danych stanu LPCD_CALIBRATION_DONE dla LPCD

| trochę do | Kawałek z | Stosowalność bitów stanu zgodnie z podstawową operacją LPCD lub ULPCD | Opis odpowiadającego bitu jest ustawiony w bajcie stanu. | ||

| 2 | 2 | Zewnętrzne pole RF | Y | Y | Przerwane z powodu zewnętrznego pola RF |

| 1 | 1 | Przerwij GPIO3 | N | Y | Przerwane z powodu zmiany poziomu GPIO3 |

| 0 | 0 | Wykryto kartę | Y | Y | Karta została wykryta |

4.4.2 Obsługa różnych scenariuszy rozruchowych

Układ scalony PN5190 obsługuje różne warunki błędów związane z parametrami układu scalonego, jak pokazano poniżej.

4.4.2.1 Obsługa scenariusza przekroczenia temperatury podczas pracy PN5190

Za każdym razem, gdy wewnętrzna temperatura układu PN5190 IC osiągnie wartość progową skonfigurowaną w polu EEPROM TEMP_WARNING [2], układ IC przechodzi w tryb gotowości. W konsekwencji, jeśli pole EEPROM ENABLE_GPIO0_ON_OVERTEMP [2] jest skonfigurowane tak, aby wysyłać powiadomienie do hosta, GPIO0 zostanie podciągnięte do góry, aby powiadomić układ IC o przekroczeniu temperatury.

Gdy temperatura układu scalonego spadnie poniżej wartości progowej skonfigurowanej w polu pamięci EEPROM TEMP_WARNING [2], układ scalony uruchomi się z komunikatem BOOT_EVENT, jak w tabeli 11, a bit stanu rozruchu BOOT_TEMP zostanie ustawiony zgodnie z tabelą 12, a GPIO0 zostanie ściągnięte do stanu niskiego.

4.4.2.2 Postępowanie w przypadku przetężenia

Jeżeli układ scalony PN5190 wykryje stan nadmiernego prądu, wyłącza zasilanie RF i wysyła sygnał TX_OVERCURRENT_ERROR_EVENT, jak pokazano w tabeli 11.

Czas trwania stanu przetężenia można kontrolować poprzez modyfikację pola pamięci EEPROM TXLDO_CONFIG [2].

Informacje na temat progu przekroczenia prądu w układzie scalonym można znaleźć w dokumencie [2].

Notatka:

Jeśli istnieją inne oczekujące zdarzenia lub odpowiedzi, zostaną one wysłane do hosta.

4.4.2.3 Utrata VDDIO podczas pracy

Jeżeli układ scalony PN5190 stwierdzi brak sygnału VDDIO (utrata sygnału VDDIO), przechodzi w tryb czuwania.

Układ scalony IC uruchamia się tylko wtedy, gdy dostępny jest interfejs VDDIO, przy BOOT_EVENT, jak w tabeli 11, oraz ustawionym bitzie stanu rozruchu BOOT_VDDIO_START, jak w tabeli 12.

Informacje na temat statycznych charakterystyk układu scalonego PN5190 można znaleźć w dokumencie [2].

4.4.3 Obsługa scenariuszy przerwania

Układ scalony PN5190 obsługuje przerywanie aktualnie wykonywanych poleceń. Zachowanie układu scalonego PN5190 po wysłaniu do układu scalonego PN4.5.4.5.2 polecenia przerwania, takiego jak opisane w sekcji 5190, przedstawiono w tabeli 18.

Notatka:

Gdy układ scalony PN5190 znajduje się w trybie ULPCD i ULP-Standby, nie można go przerwać ani przez wysłanie sekcji 4.5.4.5.2, ani przez rozpoczęcie transakcji SPI (poprzez podanie stanu niskiego na sygnał SPI_NTS).

Tabela 18. Oczekiwana odpowiedź zdarzenia po zakończeniu różnych poleceń zgodnie z sekcją 4.5.4.5.2

| Polecenia | Zachowanie po wysłaniu polecenia Przełącz tryb normalny |

| Wszystkie polecenia, w których nie wprowadzono niskiego poboru mocy | EVENT_STAUS jest ustawiony na „IDLE_EVENT” |

| Tryb przełączania LPCD | EVENT_STATUS jest ustawiony na „LPCD_EVENT”, a „LPCD_ STATUS_DATA” wskazuje bity stanu jako „Abort_HIF” |

| Przełącz tryb gotowości | EVENT_STAUS jest ustawiony na „BOOT_EVENT” z „BOOT_ STATUS_DATA” wskazującym bity „BOOT_SPI” |

| Tryb przełączania Autocoll (brak trybu autonomicznego, tryb autonomiczny z trybem gotowości i tryb autonomiczny bez trybu gotowości) | Parametr EVENT_STAUS jest ustawiony na „AUTOCOLL_EVENT”, a bity STATUS_DATA wskazują, że polecenie zostało anulowane przez użytkownika. |

4.5 Szczegóły instrukcji obsługi trybu normalnego

4.5.1 Manipulacja rejestrami

Instrukcje w tej sekcji służą do dostępu do rejestrów logicznych PN5190.

4.5.1.1 Zapis rejestru

Ta instrukcja służy do zapisu wartości 32-bitowej (little-endian) do rejestru logicznego.

4.5.1.1.1 warunków

Adres rejestru musi istnieć i rejestr musi mieć atrybut READ-WRITE lub WRITE-ONLY.

4.5.1.1.2 Polecenie

Tabela 19. Wartość polecenia WRITE_REGISTER Zapisuje wartość 32-bitową do rejestru.

| Pole ładunku | Długość | Wartość/opis |

| Adres rejestrowy | 1 bajtów | Adres rejestru. |

Tabela 19. Wartość polecenia WRITE_REGISTER…cd.

Zapisz wartość 32-bitową w rejestrze.

| Pole ładunku | Długość | Wartość/opis |

| Wartość | 4 bajty | Wartość rejestru 32-bitowego, która musi zostać zapisana. (Little-endian) |

4.5.1.1.3 Odpowiedź

Tabela 20. Wartość odpowiedzi WRITE_REGISTER

| Pole ładunku | Długość | Wartość/opis |

| Status | 1 bajtów | Status operacji [Tabela 9]. Oczekiwane wartości są następujące: |

| PN5190_STATUS_POWODZENIE | ||

| PN5190_BŁĄD_INSTR_STATUS |

4.5.1.1.4 wydarzenie

Brak zdarzeń dla tego polecenia.

4.5.1.2 Zapis_rejestru_lub_maski

Ta instrukcja służy do modyfikowania zawartości rejestru za pomocą operacji logicznej OR. Zawartość rejestru jest odczytywana i wykonywana jest operacja logiczna OR z podaną maską. Zmodyfikowana zawartość jest zapisywana z powrotem do rejestru.

4.5.1.2.1 warunków

Adres rejestru musi istnieć i rejestr musi mieć atrybut READ-WRITE.

4.5.1.2.2 Polecenie

Tabela 21. Wartość polecenia WRITE_REGISTER_OR_MASK Wykonuje operację logiczną LUB na rejestrze przy użyciu podanej maski.

| Pole ładunku | Długość | Wartość/opis |

| Adres rejestrowy | 1 bajtów | Adres rejestru. |

| Maska | 4 bajty | Maska bitowa używana jako operand dla operacji logicznej OR. (Little-endian) |

4.5.1.2.3 Odpowiedź

Tabela 22. Wartość odpowiedzi WRITE_REGISTER_OR_MASK

| Pole ładunku | Długość | Wartość/opis |

| Status | 1 bajtów | Status operacji [Tabela 9]. Oczekiwane wartości są następujące: |

| PN5190_STATUS_POWODZENIE | ||

| PN5190_BŁĄD_INSTR_STATUS |

4.5.1.2.4 wydarzenie

Brak zdarzeń dla tego polecenia.

4.5.1.3 Zapis_rejestru_i_maski

Ta instrukcja służy do modyfikowania zawartości rejestru za pomocą operacji logicznej AND. Zawartość rejestru jest odczytywana i wykonywana jest operacja logiczna AND z podaną maską. Zmodyfikowana zawartość jest zapisywana z powrotem do rejestru.

4.5.1.3.1 warunków

Adres rejestru musi istnieć i rejestr musi mieć atrybut READ-WRITE.

4.5.1.3.2 Polecenie

Tabela 23. Wartość polecenia WRITE_REGISTER_AND_MASK Wykonuje operację logiczną AND na rejestrze przy użyciu podanej maski.

| Pole ładunku | Długość | Wartość/opis |

| Adres rejestrowy | 1 bajtów | Adres rejestru. |

| Maska | 4 bajty | Maska bitowa używana jako operand dla operacji logicznej AND. (Little-endian) |

4.5.1.3.3 Odpowiedź

Tabela 24. Wartość odpowiedzi WRITE_REGISTER_AND_MASK

| Pole ładunku | Długość | Wartość/opis |

| Status | 1 bajtów | Status operacji [Tabela 9]. Oczekiwane wartości są następujące: |

| PN5190_STATUS_POWODZENIE | ||

| PN5190_BŁĄD_INSTR_STATUS |

4.5.1.3.4 wydarzenie

Brak zdarzeń dla tego polecenia.

4.5.1.4 Zapis rejestru wielokrotnego

Ta funkcjonalność instrukcji jest podobna do sekcji 4.5.1.1, sekcji 4.5.1.2, sekcji 4.5.1.3, z możliwością ich łączenia. W rzeczywistości pobiera tablicę zestawów register-type-value i wykonuje odpowiednią akcję. Typ odzwierciedla akcję, która jest albo zapisem rejestru, logiczną operacją OR na rejestrze albo logiczną operacją AND na rejestrze.

4.5.1.4.1 warunków

W zestawie musi istnieć odpowiedni adres logiczny rejestru.

Atrybut dostępu do rejestru musi zezwalać na wykonanie wymaganej akcji (typ):

- Akcja zapisu (0x01): atrybut READ-WRITE lub WRITE-ONLY

- Akcja maski OR (0x02): atrybut READ-WRITE

- Działanie maski AND (0x03): atrybut READ-WRITE

Rozmiar tablicy „Zestaw” musi mieścić się w zakresie od 1 do 43 włącznie.

Pole „Typ” musi mieścić się w zakresie od 1 do 3 włącznie

4.5.1.4.2 Polecenie

Tabela 25. Wartość polecenia WRITE_REGISTER_MULTIPLE Wykonuje operację zapisu rejestru przy użyciu zestawu par rejestr-wartość.

| Pole ładunku | Długość | Wartość/opis | |||

| Ustaw [1…n] | 6 bajty | Adres rejestrowy | 1 bajtów | Adres logiczny rejestru. | |

| Typ | 1 bajtów | 0x1 | Zapisz się do rejestru | ||

| 0x2 | Napisz Rejestr LUB Maska | ||||

| 0x3 | Napisz Rejestr I Maska | ||||

| Wartość | 4 bajty | 32 Wartość rejestru bitowego, która musi zostać zapisana, lub maska bitowa używana do operacji logicznej. (Little-endian) | |||

Uwaga: W przypadku wyjątku operacja nie jest wycofywana, tj. rejestry, które zostały zmodyfikowane do momentu wystąpienia wyjątku, pozostają w zmodyfikowanym stanie. Host musi podjąć odpowiednie działania, aby powrócić do zdefiniowanego stanu.

4.5.1.4.3 Odpowiedź

Tabela 26. Wartość odpowiedzi WRITE_REGISTER_MULTIPLE

| Pole ładunku | Długość | Wartość/opis |

| Status | 1 bajtów | Status operacji [Tabela 9]. Oczekiwane wartości są następujące: |

| PN5190_STATUS_POWODZENIE | ||

| PN5190_BŁĄD_INSTR_STATUS |

4.5.1.4.4 wydarzenie

Brak zdarzeń dla tego polecenia.

4.5.1.5 REJESTRACJA_ODCZYTU

Ta instrukcja służy do odczytu zawartości rejestru logicznego. Zawartość jest obecna w odpowiedzi jako wartość 4-bajtowa w formacie little-endian.

4.5.1.5.1 warunków

Adres rejestru logicznego musi istnieć. Atrybut dostępu rejestru musi być READ-WRITE lub READ-ONLY.

4.5.1.5.2 Polecenie

Tabela 27. Wartość polecenia READ_REGISTER

Odczytaj zawartość rejestru.

| Pole ładunku | Długość | Wartość/opis |

| Adres rejestrowy | 1 bajtów | Adres rejestru logicznego |

4.5.1.5.3 Odpowiedź

Tabela 28. Wartość odpowiedzi READ_REGISTER

| Pole ładunku | Długość | Wartość/opis |

| Status | 1 bajtów | Status operacji [Tabela 9]. Oczekiwane wartości są następujące: |

| PN5190_STATUS_SUCCESS PN5190_STATUS_INSTR_ERROR (Brak dalszych danych) | ||

| Zarejestruj wartość | 4 bajty | Wartość rejestru 32-bitowego, która została odczytana. (Little-endian) |

4.5.1.5.4 wydarzenie

Brak zdarzeń dla tego polecenia.

4.5.1.6 REJESTRACJA_WIELOKROTNA_REJESTRACJA

Ta instrukcja służy do odczytu wielu rejestrów logicznych na raz. Wynik (zawartość każdego rejestru) jest dostarczany w odpowiedzi na instrukcję. Sam adres rejestru nie jest zawarty w odpowiedzi. Kolejność zawartości rejestru w odpowiedzi odpowiada kolejności adresów rejestrów w instrukcji.

4.5.1.6.1 warunków

Wszystkie adresy rejestrów w instrukcji muszą istnieć. Atrybut dostępu dla każdego rejestru musi być albo READ-WRITE albo READ-ONLY. Rozmiar tablicy 'Register Address' musi mieścić się w zakresie od 1 do 18 włącznie.

4.5.1.6.2 Polecenie

Tabela 29. Wartość polecenia READ_REGISTER_MULTIPLE Wykonuje operację odczytu rejestru na zestawie rejestrów.

| Pole ładunku | Długość | Wartość/opis |

| Adres rejestru[1…n] | 1 bajtów | Adres rejestrowy |

4.5.1.6.3 Odpowiedź

Tabela 30. Wartość odpowiedzi READ_REGISTER_MULTIPLE

| Pole ładunku | Długość | Wartość/opis | ||

| Status | 1 bajtów | Status operacji [Tabela 9]. Oczekiwane wartości są następujące: | ||

| PN5190_STATUS_SUCCESS PN5190_STATUS_INSTR_ERROR (Brak dalszych danych) | ||||

| Wartość rejestru [1…n] | 4 bajty | Wartość | 4 bajty | Wartość rejestru 32-bitowego, która została odczytana (little-endian). |

4.5.1.6.4 wydarzenie

Brak zdarzeń dla tego polecenia.

4.5.2 Manipulacja pamięcią E2PROM

Dostępny obszar w pamięci E2PROM jest zgodny z mapą pamięci EEPROM i rozmiarem adresowalnym.

Notatka:

1. W każdej podanej poniżej instrukcji wzmianka o „Adresie E2PROM” odnosi się do rozmiaru adresowalnego obszaru pamięci EEPROM.

4.5.2.1 ZAPIS_E2PROM

Ta instrukcja służy do zapisu jednej lub więcej wartości do pamięci E2PROM. Pole „Values” zawiera dane, które mają zostać zapisane do pamięci E2PROM, zaczynając od adresu podanego w polu „E2PROM Address”. Dane są zapisywane w kolejności sekwencyjnej.

Notatka:

Należy pamiętać, że jest to polecenie blokujące, co oznacza, że NFC FE jest blokowany podczas operacji zapisu. Może to potrwać kilka milisekund.

4.5.2.1.1 warunków

Pole „Adres E2PROM” musi mieścić się w zakresie zgodnie z [2]. Liczba bajtów w polu „Wartości” musi mieścić się w zakresie od 1 do 1024 (0x0400) włącznie. Operacja zapisu nie może wykraczać poza adres EEPROM, jak wspomniano w [2]. Odpowiedź błędu musi zostać wysłana do hosta, jeśli adres przekracza przestrzeń adresową EEPROM, jak w [2].

4.5.2.1.2 Polecenie

Tabela 31. Wartość polecenia WRITE_E2PROM Zapisuje podane wartości sekwencyjnie do pamięci E2PROM.

| Pole ładunku | Długość | Wartość/opis |

| Adres E2PROM | 2 bajtów | Adres w pamięci EEPROM, od którego ma rozpocząć się operacja zapisu. (Little-endian) |

| Wartości | 1 – 1024 bajtów | Wartości, które muszą zostać zapisane w pamięci E2PROM w kolejności sekwencyjnej. |

4.5.2.1.3 Odpowiedź

Tabela 32. Wartość odpowiedzi WRITE_EEPROM

| Pole ładunku | Długość | Wartość/opis |

| Status | 1 bajtów | Status operacji [Tabela 9]. Oczekiwane wartości są następujące: |

| PN5190_STATUS_SUCCESS PN5190_STATUS_INSTR_ERROR PN5190_STATUS_MEMORY_ERROR |

4.5.2.1.4 wydarzenie

Brak zdarzeń dla tego polecenia.

4.5.2.2 ODCZYT_E2PROM

Ta instrukcja służy do odczytu danych z obszaru pamięci E2PROM. Pole „Adres E2PROM” wskazuje adres początkowy operacji odczytu. Odpowiedź zawiera dane odczytane z E2PROM.

4.5.2.2.1 warunków

Pole „Adres E2PROM” musi mieścić się w prawidłowym zakresie.

Pole „Liczba bajtów” musi mieścić się w zakresie od 1 do 256 włącznie.

Operacja odczytu nie może wykraczać poza ostatni dostępny adres EEPROM.

Odpowiedź o błędzie zostanie wysłana do hosta, jeśli adres przekroczy przestrzeń adresową pamięci EEPROM.

4.5.2.2.2 Polecenie

Tabela 33. Wartość polecenia READ_E2PROM Odczyt wartości z pamięci E2PROM sekwencyjnie.

| Pole ładunku | Długość | Wartość/opis |

| Adres E2PROM | 2 bajtów | Adres w pamięci E2PROM, od którego ma rozpocząć się operacja odczytu. (Little-endian) |

| Liczba bajtów | 2 bajtów | Liczba bajtów do odczytania. (Little-endian) |

4.5.2.2.3 Odpowiedź

Tabela 34. Wartość odpowiedzi READ_E2PROM

| Pole ładunku | Długość | Wartość/opis |

| Status | 1 bajtów | Status operacji [Tabela 9]. Oczekiwane wartości są następujące: |

| PN5190_STATUS_POWODZENIE | ||

| PN5190_STATUS_INSTR_ERROR (Brak dalszych danych) | ||

| Wartości | 1 – 1024 bajtów | Wartości odczytane w kolejności sekwencyjnej. |

4.5.2.2.4 wydarzenie

Brak zdarzeń dla tego polecenia.

4.5.2.3 POBIERZ_OBSZAR_UŻYTKOWNIKA_CRC

Ta instrukcja służy do obliczenia sumy kontrolnej CRC dla całego obszaru konfiguracji użytkownika, łącznie z obszarem protokołu układu scalonego PN5190.

4.5.2.3.1 Polecenie

Tabela 35. Wartość polecenia GET_CRC_USER_AREA

Odczytaj sumę kontrolną CRC obszaru konfiguracji użytkownika, łącznie z obszarem protokołu.

| Pole ładunku | Długość | Wartość/opis |

| – | – | Brak danych w ładunku |

4.5.2.3.2 Odpowiedź

Tabela 36. Wartość odpowiedzi GET_CRC_USER_AREA

| Pole ładunku | Długość | Wartość/opis |

| Status | 1 bajtów | Status operacji [Tabela 9]. Oczekiwane wartości są następujące: |

| PN5190_STATUS_POWODZENIE | ||

| PN5190_STATUS_INSTR_ERROR (Brak dalszych danych) | ||

| Wartości | 4 bajty | 4 bajty danych CRC w formacie little-endian. |

4.5.2.3.3 wydarzenie

Brak zdarzeń dla tego polecenia.

4.5.3 Manipulacja danymi CLIF

Instrukcje zawarte w tej sekcji opisują polecenia dotyczące nadawania i odbioru sygnału RF.

4.5.3.1 WYMIANA_DANYCH_RF

Funkcja wymiany RF polega na transmisji danych TX i oczekiwaniu na odbiór danych RX.

Funkcja zwraca w przypadku odbioru (błędnego lub poprawnego) lub przekroczenia limitu czasu. Timer jest uruchamiany z END TRANSMISSION i zatrzymywany z START RECEPTION. Wartość limitu czasu wstępnie skonfigurowana w pamięci EEPROM zostanie użyta w przypadku, gdy limit czasu nie zostanie skonfigurowany przed wykonaniem polecenia Exchange.

Jeśli transceiver_state jest

- w trybie IDLE włączony jest tryb TRANSCEIVE.

- W trybie WAIT_RECEIVE stan transceivera jest resetowany do TRYBU TRANSCEIVE w przypadku ustawienia bitu inicjatora

- W trybie WAIT_TRANSMIT stan transceivera jest resetowany do TRYBU TRANSCEIVE, jeśli bit inicjatora NIE jest ustawiony

Pole „Liczba prawidłowych bitów w ostatnim bajcie” wskazuje dokładną długość danych, które mają zostać przesłane.

4.5.3.1.1 warunków

Rozmiar pola „Dane TX” musi mieścić się w zakresie od 0 do 1024 włącznie.

Pole „Liczba prawidłowych bitów w ostatnim bajcie” musi mieścić się w zakresie od 0 do 7.

Polecenie nie może zostać wywołane podczas trwającej transmisji RF. Polecenie musi zapewnić właściwy stan transceivera do transmisji danych.

Notatka:

Ta komenda jest ważna tylko w trybie czytnika i trybie inicjatora „P2P” pasywnym/aktywnym.

4.5.3.1.2 Polecenie

Tabela 37. Wartość polecenia EXCHANGE_RF_DATA

Zapisz dane TX do wewnętrznego bufora transmisji RF i rozpocznij transmisję za pomocą polecenia transceive, a następnie czekaj na odbiór lub przekroczenie limitu czasu, aby przygotować odpowiedź dla hosta.

| Pole ładunku | Długość | Wartość/opis | |

| Liczba prawidłowych bitów w ostatnim bajcie | 1 bajtów | 0 | Wszystkie bity ostatniego bajtu są przesyłane |

| 1 – 7 | Liczba bitów w ostatnim bajcie, które mają zostać przesłane. | ||

| Konfiguracja RFExchange | 1 bajtów | Konfiguracja funkcji RFExchange. Szczegóły poniżej | |

Tabela 37. Wartość polecenia EXCHANGE_RF_DATA…cd.

Zapisz dane TX do wewnętrznego bufora transmisji RF i rozpocznij transmisję za pomocą polecenia transceive, a następnie czekaj na odbiór lub przekroczenie limitu czasu, aby przygotować odpowiedź dla hosta.

| Pole ładunku | Długość | Wartość/opis |

| Dane Teksasu | n bajtów | Dane TX, które muszą zostać wysłane przez CLIF przy użyciu polecenia transceive. n = 0 – 1024 bajtów |

Tabela 38. Maska bitowa RFexchangeConfig

| b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 | Opis |

| Bity 4–7 to RFU | ||||||||

| X | Dołącz dane RX do odpowiedzi na podstawie RX_STATUS, jeśli bit jest ustawiony na 1b. | |||||||

| X | Dołącz rejestr EVENT_STATUS w odpowiedzi, jeśli bit jest ustawiony na 1b. | |||||||

| X | Dołącz rejestr RX_STATUS_ERROR w odpowiedzi, jeśli bit jest ustawiony na 1b. | |||||||

| X | Dołącz rejestr RX_STATUS w odpowiedzi, jeśli bit jest ustawiony na 1b. |

4.5.3.1.3 Odpowiedź

Tabela 39. Wartość odpowiedzi EXCHANGE_RF_DATA

| Pole ładunku | Długość | Wartość/opis |

| Status | 1 bajtów | Status operacji [Tabela 9]. Oczekiwane wartości są następujące: |

| PN5190_STATUS_INSTR_POWODZENIE PN5190_STATUS_INSTR_ERROR (Brak dalszych danych) PN5190_STATUS_TIMEOUT PN5190_STATUS_RX_TIMEOUT PN5190_STATUS_NO_RF_FIELD PN5190_STATUS_TIMEOUT_WITH_EMD_ERROR |

||

| RX_STATUS | 4 bajty | Jeśli zażądano RX_STATUS (little-endian) |

| BŁĄD_STATUSU_RX | 4 bajty | Jeśli zażądano RX_STATUS_ERROR (little-endian) |

| STAN_ZDARZENIA | 4 bajty | Jeśli zażądano EVENT_STATUS (little-endian) |

| Dane RX | 1 – 1024 bajtów | Jeśli zażądano danych RX. Dane RX otrzymane podczas fazy odbioru sygnału RF wymiany RF. |

4.5.3.1.4 wydarzenie

Brak zdarzeń dla tego polecenia.

4.5.3.2 TRANSMISJA_DANYCH_RF

Ta instrukcja służy do zapisu danych do wewnętrznego bufora transmisji CLIF i rozpoczęcia transmisji za pomocą polecenia transceive wewnętrznie. Rozmiar tego bufora jest ograniczony do 1024 bajtów. Po wykonaniu tej instrukcji odbiór RF jest uruchamiany automatycznie.

Polecenie powraca natychmiast po zakończeniu transmisji, nie czekając na zakończenie odbioru.

4.5.3.2.1 warunków

Liczba bajtów w polu „Dane TX” musi mieścić się w zakresie od 1 do 1024 włącznie.

Polecenie nie może zostać wywołane w trakcie trwającej transmisji RF.

4.5.3.2.2 Polecenie

Tabela 40. Wartość polecenia TRANSMIT_RF_DATA Zapisuje dane TX do wewnętrznego bufora transmisji CLIF.

| Pole ładunku | Długość | Wartość/opis |

| Liczba prawidłowych bitów w ostatnim bajcie | 1 bajtów | 0 Wszystkie bity ostatniego bajtu są przesyłane. 1 – 7 Liczba bitów w ostatnim bajcie, które mają zostać przesłane. |

| RFU | 1 bajtów | Skryty |

| Dane Teksasu | 1 – 1024 bajtów | Dane TX, które będą wykorzystane podczas następnej transmisji RF. |

4.5.3.2.3 Odpowiedź

Tabela 41. Wartość odpowiedzi TRANSMIT_RF_DATA

| Pole ładunku | Długość | Wartość/opis |

| Status | 1 bajtów | Status operacji [Tabela 9]. Oczekiwane wartości są następujące: |

| PN5190_STATUS_INSTR_SUCCESS PN5190_STATUS_INSTR_ERROR PN5190_STATUS_NO_RF_FIELD PN5190_STATUS_NO_EXTERNAL_RF_FIELD |

4.5.3.2.4 wydarzenie

Brak zdarzeń dla tego polecenia.

4.5.3.3 POBIERZ_DANE_RF

Ta instrukcja służy do odczytu danych z wewnętrznego bufora CLIF RX, który zawiera dane odpowiedzi RF (jeśli takie istnieją) przesłane do niego od czasu poprzedniego wykonania sekcji 4.5.3.1 z opcją nieuwzględniania odebranych danych w odpowiedzi lub poleceniu sekcji 4.5.3.2.

4.5.3.3.1 Polecenie

Tabela 42. Wartość polecenia RETRIEVE_RF_DATA Odczyt danych RX z wewnętrznego bufora odbioru sygnału RF.

| Pole ładunku | Długość | Wartość/opis |

| Pusty | Pusty | Pusty |

4.5.3.3.2 Odpowiedź

Tabela 43. Wartość odpowiedzi RETRIEVE_RF_DATA

| Pole ładunku | Długość | Wartość/opis |

| Status | 1 bajtów | Status operacji [Tabela 9]. Oczekiwane wartości są następujące: |

| Pole ładunku | Długość | Wartość/opis |

| PN5190_STATUS_INSTR_POWODZENIE PN5190_STATUS_INSTR_ERROR (Brak dalszych danych) |

||

| Dane RX | 1 – 1024 bajtów | Dane RX odebrane podczas ostatniego udanego odbioru sygnału RF. |

4.5.3.3.3 wydarzenie

Brak zdarzeń dla tego polecenia.

4.5.3.4 ODBIERZ_DANE_RF

Ta instrukcja oczekuje na dane otrzymane poprzez interfejs RF czytnika.

W trybie czytnika ta instrukcja zwraca albo odbiór (błędny lub poprawny), albo przekroczenie limitu czasu FWT. Timer jest uruchamiany z END TRANSMISSION i zatrzymywany z START RECEPTION. Domyślna wartość limitu czasu wstępnie skonfigurowana w pamięci EEPROM powinna być używana w przypadku, gdy limit czasu nie został skonfigurowany przed wykonaniem polecenia Exchange.

W trybie docelowym instrukcja ta powraca w przypadku odbioru (błędnego lub poprawnego) lub zewnętrznego błędu RF.

Notatka:

Ta instrukcja powinna być używana z poleceniem TRANSMIT_RF_DATA w celu wykonania operacji TX i RX…

4.5.3.4.1 Polecenie

Tabela 44. Wartość polecenia RECEIVE_RF_DATA

| Pole ładunku | Długość | Wartość/opis |

| Odbierz konfigurację RF | 1 bajtów | Konfiguracja funkcji ReceiveRFConfig. Zobacz Tabela 45 |

Tabela 45. Maska bitowa ReceiveRFConfig

| b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 | Opis |

| Bity 4–7 to RFU | ||||||||

| X | Dołącz dane RX do odpowiedzi na podstawie RX_STATUS, jeśli bit jest ustawiony na 1b. | |||||||

| X | Dołącz rejestr EVENT_STATUS w odpowiedzi, jeśli bit jest ustawiony na 1b. | |||||||

| X | Dołącz rejestr RX_STATUS_ERROR w odpowiedzi, jeśli bit jest ustawiony na 1b. | |||||||

| X | Dołącz rejestr RX_STATUS w odpowiedzi, jeśli bit jest ustawiony na 1b. |

4.5.3.4.2 Odpowiedź

Tabela 46. Wartość odpowiedzi RECEIVE_RF_DATA

| Pole ładunku | Długość | Wartość/opis |

| Status | 1 bajtów | Status operacji [Tabela 9]. Oczekiwane wartości są następujące: |

| PN5190_STATUS_INSTR_POWODZENIE PN5190_STATUS_INSTR_ERROR (Brak dalszych danych) PN5190_STATUS_TIMEOUT |

| Pole ładunku | Długość | Wartość/opis |

| PN5190_STATUS_NO_RF_FIELD PN5190_STATUS_NO_EXTERNAL_RF_FIELD |

||

| RX_STATUS | 4 bajty | Jeśli zażądano RX_STATUS (little-endian) |

| BŁĄD_STATUSU_RX | 4 bajty | Jeśli zażądano RX_STATUS_ERROR (little-endian) |

| STAN_ZDARZENIA | 4 bajty | Jeśli zażądano EVENT_STATUS (little-endian) |

| Dane RX | 1 – 1024 bajtów | Jeśli zażądano danych RX. Dane RX otrzymano przez RF. |

4.5.3.4.3 wydarzenie

Brak zdarzeń dla tego polecenia.

4.5.3.5 RETRIEVE_RF_FELICA_EMD_DATA (Konfiguracja FeliCa EMD)

Ta instrukcja służy do odczytu danych z wewnętrznego bufora CLIF RX, który zawiera dane odpowiedzi FeliCa EMD (jeśli takie istnieją), przesłane do niego z poprzedniego wykonania polecenia EXCHANGE_RF_DATA ze statusem „PN5190_STATUS_TIMEOUT_WITH_EMD_ERROR”.

Notatka: Polecenie to jest dostępne od wersji PN5190 FW v02.03.

4.5.3.5.1 Polecenie

Odczyt danych RX z wewnętrznego bufora odbioru sygnału RF.

Tabela 47. Wartość polecenia RETRIEVE_RF_FELICA_EMD_DATA

| Pole ładunku | Długość | Wartość/opis | |

| FeliCaRFPobierz konfigurację | 1 bajtów | 00 – FF | Konfiguracja funkcji RETRIEVE_RF_FELICA_EMD_DATA |

| opis konfiguracji (maski bitowej) | bit 7..2: RFU bit 1: Dołącz rejestr RX_STATUS_ ERROR w odpowiedzi, jeśli bit jest ustawiony na 1b. bit 0: Dołącz rejestr RX_STATUS w odpowiedzi, jeśli bit jest ustawiony na 1b. |

||

4.5.3.5.2 Odpowiedź

Tabela 48. Wartość odpowiedzi RETRIEVE_RF_FELICA_EMD_DATA

| Pole ładunku | Długość | Wartość/opis | |||

| Status | 1 bajtów | Status operacji. Oczekiwane wartości są następujące: PN5190_STATUS_INSTR_SUCCESS PN5190_STATUS_INSTR_ERROR (Brak dalszych danych) | |||

| RX_STATUS | 4 bajtów | Jeśli zażądano RX_STATUS (little-endian) | |||

| BŁĄD RX_STATUS_ | 4 bajtów | Jeśli zażądano RX_STATUS_ERROR (little-endian) | |||

| Pole ładunku | Długość | Wartość/opis | |||

| Dane RX | 1…1024 bajtów | Dane FeliCa EMD RX odebrane podczas ostatniego nieudanego odbioru sygnału RF za pomocą polecenia Exchange. | |||

4.5.3.5.3 wydarzenie

Brak zdarzeń dla tego polecenia.

4.5.4 Przełączanie trybu pracy

PN5190 obsługuje 4 różne tryby pracy:

4.5.4.1 Normal

Jest to tryb domyślny, w którym dozwolone są wszystkie instrukcje.

4.5.4.2 Gotowość

PN5190 jest w stanie gotowości/uśpienia, aby oszczędzać energię. Warunki wybudzania muszą być ustawione, aby określić, kiedy ponownie wyjść z trybu gotowości.

4.5.4.3 LPCD

Układ PN5190 znajduje się w trybie wykrywania karty o niskim poborze mocy, w którym próbuje wykryć kartę wchodzącą do woluminu roboczego przy możliwie najniższym poborze mocy.

4.5.4.4 Autokolekcja

PN5190 działa jako odbiornik RF, wykonując autonomiczną aktywację trybu docelowego (aby zagwarantować ograniczenia w czasie rzeczywistym)

4.5.4.5 TRYB PRZEŁĄCZANIA_NORMALNY

Polecenie Switch Mode Normal ma trzy przypadki użycia.

4.5.4.5.1 Przypadek użycia 1: Wejdź w normalny tryb działania po włączeniu zasilania (POR)

Użyj tego przycisku, aby zresetować do stanu bezczynności w celu odebrania/przetworzenia następnego polecenia poprzez przejście do normalnego trybu pracy.

4.5.4.5.2 Przypadek użycia 2: Zakończenie już uruchomionego polecenia w celu przejścia do normalnego trybu działania (przerwanie polecenia)

Użyj tej opcji, aby zresetować do stanu bezczynności w celu odebrania/przetworzenia następnego polecenia poprzez zakończenie już uruchomionych poleceń.

Polecenia takie jak standby, LPCD, Exchange, PRBS i Autocoll można będzie zakończyć za pomocą tego polecenia.

To jest jedyne specjalne polecenie, które nie ma odpowiedzi. Zamiast tego ma powiadomienie EVENT.

Więcej informacji na temat typów zdarzeń występujących podczas wykonywania różnych poleceń podstawowych można znaleźć w rozdziale 4.4.3.

4.5.4.5.2.1 Przypadek użycia 2.1:

To polecenie zresetuje wszystkie rejestry CLIF TX, RX i Field Control do stanu Boot. Wydanie tego polecenia wyłączy wszelkie istniejące pola RF.

4.5.4.5.2.2 Przypadek użycia 2.2:

Dostępne od wersji PN5190 FW v02.03:

Polecenie to nie modyfikuje rejestrów CLIF TX, RX ani Field Control, lecz jedynie przełącza transceiver w stan IDLE.

4.5.4.5.3 Przypadek użycia 3: Normalny tryb pracy po miękkim resecie/wyjściu ze stanu gotowości, LPCD W tym przypadku PN5190 przechodzi bezpośrednio do normalnego trybu pracy, wysyłając IDLE_EVENT do hosta (rysunek 12 lub rysunek 13), a bit „IDLE_EVENT” jest ustawiany w tabeli 11.

Nie ma wymogu wysyłania polecenia SWITCH_MODE_NORMAL.

Notatka:

Po przełączeniu układu scalonego IC do trybu normalnego wszystkie ustawienia RF są modyfikowane do stanu domyślnego. Konieczne jest załadowanie odpowiedniej konfiguracji RF i innych powiązanych rejestrów odpowiednimi wartościami przed wykonaniem operacji RF ON lub RF Exchange.

4.5.4.5.4 Ramka poleceń do wysłania w różnych przypadkach użycia

4.5.4.5.4.1 Przypadek użycia 1: Polecenie przechodzi w normalny tryb działania po włączeniu zasilania (POR) 0x20 0x01 0x00

4.5.4.5.4.2 UseCase2: Polecenie kończące już uruchomione polecenia w celu przejścia do normalnego trybu działania

Przypadek użycia 2.1:

0x20 0x00 0x00

Przypadek użycia 2.2: (Od wersji FW v02.02):

0x20 0x02 0x00

4.5.4.5.4.3 Przypadek użycia 3: Polecenie trybu normalnej pracy po miękkim resecie/wyjściu ze stanu gotowości, LPCD, ULPCD

Brak. PN5190 przechodzi bezpośrednio do trybu normalnej pracy.

4.5.4.5.5 Odpowiedź

Nic

4.5.4.5.6 wydarzenie

BOOT_EVENT (w rejestrze EVENT_STATUS) jest ustawiany, wskazując, że tryb normalny jest włączony i jest wysyłany do hosta. Zobacz Rysunek 12 i Rysunek 13, aby uzyskać dane zdarzenia.

Ustawiane jest zdarzenie IDLE_EVENT (w rejestrze EVENT_STATUS), wskazujące na przejście do trybu normalnego i wysyłane do hosta. Dane zdarzenia znajdują się na rysunku 12 i rysunku 13.

BOOT_EVENT (w rejestrze EVENT_STATUS) jest ustawiany, wskazując, że wprowadzono tryb normalny i jest wysyłany do hosta. Zobacz Rysunek 12 i Rysunek 13, aby uzyskać dane zdarzenia.

4.5.4.6 AUTOMATYCZNE_KOMUNIKOWANIE_TRYBU_PRZEŁĄCZANIA

Funkcja Switch Mode Autocoll automatycznie przeprowadza procedurę aktywacji karty w trybie docelowym.

Pole „Tryb autokoll” musi mieścić się w zakresie od 0 do 2 włącznie.

W przypadku gdy pole „Tryb Autocoll” jest ustawione na 2 (Autocoll): Pole „Technologie RF” (Tabela 50) musi zawierać maskę bitową wskazującą technologie RF, które mają być obsługiwane podczas Autocoll.

Będąc w tym trybie nie wolno wysyłać żadnych instrukcji.

Zakończenie sygnalizowane jest za pomocą przerwania.

4.5.4.6.1 Polecenie

Tabela 49. Wartość polecenia SWITCH_MODE_AUTOCOLL

| Parametr | Długość | Wartość/opis | |

| Technologie RF | 1 bajtów | Maska bitowa wskazująca technologię RF, na którą należy zwracać uwagę podczas automatycznego zestawiania sygnałów. | |

| Tryb autocoll | 1 bajtów | 0 | Brak trybu autonomicznego, tj. Autocoll kończy działanie, gdy nie ma zewnętrznego pola RF. |

| Wypowiedzenie w przypadku | |||

| • BRAK POLA RF lub POLE RF zniknęło | |||

| • PN5190 jest AKTYWOWANY w trybie DOCELOWYM | |||

| 1 | Tryb autonomiczny z funkcją czuwania. Gdy nie ma pola RF, Autocoll automatycznie przechodzi w tryb gotowości. Po wykryciu zewnętrznego pola RF PN5190 ponownie przechodzi w tryb Autocoll. | ||

| Wypowiedzenie w przypadku | |||

| • PN5190 jest AKTYWOWANY w trybie DOCELOWYM | |||

| Z PN5190 FW wersja 02.03 dalej: Jeśli pole EEPROM „bCard ModeUltraLowPowerEnabled” pod adresem „0xCDF” jest ustawione na „1”, układ PN5190 przechodzi w tryb czuwania o bardzo niskim poborze mocy. | |||

| 2 | Tryb autonomiczny bez trybu czuwania. Gdy nie ma pola RF, PN5190 czeka, aż pole RF będzie obecne, zanim rozpocznie algorytm Autocoll. W tym przypadku tryb gotowości nie jest używany. | ||

| Wypowiedzenie w przypadku • PN5190 jest AKTYWOWANY w trybie DOCELOWYM |

|||

Tabela 50. Maska bitowa technologii RF

| b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 | Opis |

| 0 | 0 | 0 | 0 | RFU | ||||

| X | Jeżeli ustawiono na 1b, nasłuchiwanie NFC-F Active jest włączone. (Niedostępne). | |||||||

| X | Jeżeli ustawiono na 1b, nasłuchiwanie NFC-A Active jest włączone. (Niedostępne). | |||||||

| X | Jeżeli ustawione na 1b, nasłuchiwanie NFC-F jest włączone. | |||||||

| X | Jeżeli ustawione na 1b, nasłuchiwanie NFC-A jest włączone. |

4.5.4.6.2 Odpowiedź

Odpowiedź sygnalizuje jedynie, że polecenie zostało przetworzone.

Tabela 51. Wartość odpowiedzi SWITCH_MODE_AUTOCOLL

| Pole ładunku | Długość | Wartość/opis |

| Status | 1 bajtów | Status operacji [Tabela 9]. Oczekiwane wartości są następujące: |

| PN5190_STATUS_INSTR_POWODZENIE PN5190_STATUS_INSTR_ERROR (Nie wprowadzono trybu przełączania z powodu błędnych ustawień) |

4.5.4.6.3 wydarzenie

Powiadomienie o zdarzeniu jest wysyłane po zakończeniu polecenia i przejściu do trybu normalnego. Host musi odczytać bajty odpowiedzi na podstawie wartości zdarzenia.

Notatka:

Gdy status jest inny niż „PN5190_STATUS_INSTR_SUCCESS”, wówczas dalsze bajty danych „Protocol” i „Card_Activated” nie są obecne.

Informacje technologiczne pobierane są z rejestrów przy użyciu poleceń podanych w rozdziale 4.5.1.5, rozdziale 4.5.1.6.

Poniższa tabela przedstawia dane zdarzenia, które są wysyłane jako część komunikatu zdarzenia (rysunek 12 i rysunek 13).

Tabela 52. EVENT_SWITCH_MODE_AUTOCOLL – dane AUTOCOLL_EVENT Tryb działania przełącznika Zdarzenie Autocoll

| Pole ładunku | Długość | Wartość/opis | |

| Status | 1 bajt | Status operacji | |

| PN5190_STATUS_INSTR_POWODZENIE | PN5190 jest AKTYWOWANY w trybie DOCELOWYM. Dalsze dane dotyczące tego zdarzenia są aktualne. |

||

| PN5190_STATUS_PREVENT_STANDBY | Oznacza, że PN5190 nie może przejść w tryb gotowości. Ten status jest ważny tylko wtedy, gdy tryb Autocoll jest wybrany jako „Tryb autonomiczny z gotowością”. | ||

| PN5190_STATUS_NO_EXTERNAL_RF_ FIELD | Oznacza, że podczas wykonywania funkcji Autocoll w trybie nieautonomicznym nie występuje żadne zewnętrzne pole RF | ||

| PN5190_STATUS_UŻYTKOWNIK_ANULOWANY | Oznacza, że bieżące polecenie w toku zostało przerwane przez polecenie przełączania trybu normalnego | ||

| Protokół | 1 bajt | 0x10 | Aktywowany jako pasywny typ A |

| 0x11 | Aktywowany jako pasywny TypeF 212 | ||

| 0x12 | Aktywowany jako pasywny TypeF 424 | ||

| 0x20 | Aktywowany jako aktywny typ A | ||

| 0x21 | Aktywowany jako Aktywny Typ F 212 | ||

| 0x22 | Aktywowany jako Aktywny Typ F 424 | ||

| Inne wartości | Nieważny | ||

| Karta_Aktywowana | 1 bajt | 0x00 | Brak procesu aktywacji karty zgodnie z normą ISO 14443-3 |

| 0x01 | Oznacza, że urządzenie jest aktywowane w trybie pasywnym. |

Notatka:

Po odczytaniu danych zdarzenia należy odczytać dane otrzymane z karty/urządzenia, które zostało aktywowane (takie jak „n” bajtów ATR_REQ/RATS zgodnie z normą ISO18092/ISO1443-4), korzystając z polecenia z sekcji 4.5.3.3.

4.5.4.6.4 Komunikacja npample

4.5.4.7 TRYB PRZEŁĄCZANIA_CZUWANIA

Tryb gotowości Switch Mode automatycznie ustawia układ scalony IC w tryb gotowości. Układ scalony IC wybudzi się po tym, jak skonfigurowane źródła wybudzania spełnią warunki wybudzania.

Notatka:

Liczniki wygasania dla trybu gotowości ULP i przerwania HIF dla trybu gotowości są dostępne domyślnie, umożliwiając wyjście z trybu gotowości.

4.5.4.7.1 Polecenie

Tabela 53. Wartość polecenia SWITCH_MODE_STANDBY

| Parametr | Długość | Wartość/opis |

| Konfiguracja | 1 bajtów | Maska bitowa kontrolująca źródło budzenia, które ma być użyte i tryb gotowości, do którego ma wejść. Zobacz Tabela 54 |

| Wartość licznika | 2 bajty | Wartość używana dla licznika wybudzania w milisekundach. Maksymalna obsługiwana wartość to 2690 dla trybu gotowości. Maksymalna obsługiwana wartość to 4095 dla trybu gotowości ULP. Wartość, która ma zostać podana, jest w formacie little-endian. Zawartość tego parametru jest ważna tylko wtedy, gdy opcja „Config Bitmask” jest włączona w celu wybudzenia po wygaśnięciu licznika. |

Tabela 54. Konfiguracja maski bitowej