UM11942

UM11942

Capa de instrucción PN5190

Controlador de interfaz NFC

Manual de usuario

Controlador frontal NFC PN5190

Información del documento

| Información | Contenido |

| Palabras clave | PN5190, NFC, interfaz NFC, controlador, capa de instrucciones |

| Abstracto | Este documento describe los comandos y respuestas de la capa de instrucción para trabajar desde un controlador host, para evaluar el funcionamiento del controlador frontend NFC NXP PN5190. PN5190 es un controlador frontal NFC de próxima generación. El alcance de este documento es describir los comandos de interfaz para trabajar con el controlador frontend NFC PN5190. Para obtener más información sobre el funcionamiento del controlador frontend NFC PN5190, consulte la hoja de datos y su información complementaria. |

Historial de revisiones

| Rdo | Fecha | Descripción |

| 3.7 | 20230525 | • El tipo de documento y el título cambiaron del anexo de la hoja de datos del producto al manual del usuario. • Limpieza editorial • Términos editoriales actualizados para señales SPI • Se agregó el comando GET_CRC_USER_AREA en la Tabla 8 en la Sección 4.5.2.3 • Se actualizaron varios detalles diferenciados para PN5190B1 y PN5190B2 en la Sección 3.4.1. • Respuesta actualizada de la Sección 3.4.7 |

| 3.6 | 20230111 | Descripción mejorada de la respuesta de Verificación de integridad en la Sección 3.4.7 |

| 3.5 | 20221104 | Sección 4.5.4.6.3 “Evento”: añadido |

| 3.4 | 20220701 | • Se agregó el comando CONFIGURE_MULTIPLE_TESTBUS_DIGITAL en la Tabla 8 en la Sección 4.5.9.3 • Sección actualizada 4.5.9.2.2 |

| 3.3 | 20220329 | Descripción del hardware mejorada en la Sección 4.5.12.2.1 "Comando" y la Sección 4.5.12.2.2 "Respuesta" |

| 3.2 | 20210910 | Números de versión de firmware actualizados de 2.1 a 2.01 y 2.3 a 2.03 |

| 3.1 | 20210527 | Se agregó la descripción del comando RETRIEVE_RF_FELICA_EMD_DATA |

| 3 | 20210118 | Primera versión oficial lanzada |

Introducción

1.1 Introducción

Este documento describe la interfaz de host PN5190 y las API. La interfaz de host físico utilizada en la documentación es SPI. La característica física del SPI no se considera en el documento.

La separación de cuadros y el control de flujo son parte de este documento.

1.1.1 Ámbito de aplicación

El documento describe la capa lógica, el código de instrucción y las API que son relevantes para el cliente.

Comunicación con el anfitrión terminadaview

PN5190 tiene dos modos principales de operación para comunicarse con el controlador de host.

- La comunicación basada en HDLL se utiliza cuando se activa el dispositivo para ingresar:

a. Modo de descarga segura cifrada para actualizar su firmware - Comunicación basada en comando-respuesta TLV (dada como example).

2.1 Modo HDLL

El modo HDLL se utiliza para que el formato de intercambio de paquetes funcione con los siguientes modos operativos de IC:

- Modo de descarga segura de firmware (SFWU), consulte la Sección 3

2.1.1 Descripción de HDLL

HDLL es la capa de enlace desarrollada por NXP para garantizar una descarga de FW confiable.

Un mensaje HDLL está formado por un encabezado de 2 bytes, seguido de una trama, que comprende el código de operación y la carga útil del comando. Cada mensaje termina con un CRC de 16 bits, como se describe en la siguiente imagen: El encabezado HDLL contiene:

El encabezado HDLL contiene:

- Un poco. Lo que indica si este mensaje es el único o el último fragmento de un mensaje (fragmento = 0). O si, al menos, le sigue otro fragmento (fragmento = 1).

- La longitud de la carga útil codificada en 10 bits. Por lo tanto, la carga útil del marco HDLL puede llegar hasta 1023 bytes.

El orden de los bytes se ha definido como big-endian, es decir, Ms Byte primero.

El CRC16 cumple con el estándar X.25 (CRC-CCITT, ISO/IEC13239) con polinomio x^16 + x^12 + x^5 +1 y valor de precarga 0xFFFF.

Se calcula sobre todo el marco HDLL, es decir, Cabecera + Marco.

Sampimplementación del código C:

estático uint16_t phHal_Host_CalcCrc16(uint8_t* p, uint32_t dwLength)

{

uint32_ti;

uint16_t crc_nuevo;

uint16_t crc = 0xffffU;

para (I = 0; i < dwLength; i++)

{

crc_nuevo = (uint8_t)(crc >> 8) | (crc << 8 );

crc_new ^= p[i];

crc_new ^= (uint8_t)(crc_new & 0xff) >> 4;

crc_nuevo ^= crc_nuevo << 12;

crc_nuevo ^= (crc_nuevo & 0xff) << 5;

crc = crc_nuevo;

}

volver crc;

}

2.1.2 Mapeo de transporte sobre el SPI

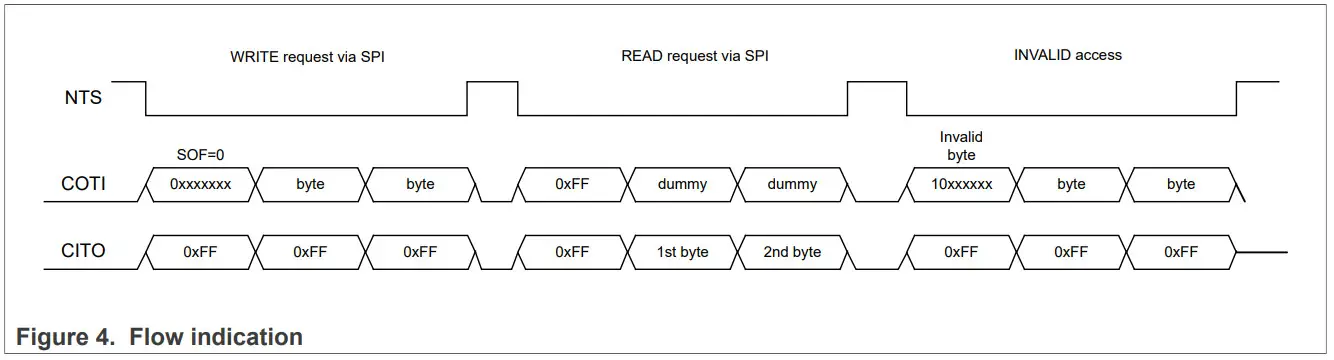

Para cada aserción NTS, el primer byte es siempre un ENCABEZADO (byte de indicación de flujo), puede ser 0x7F/0xFF con respecto a la operación de escritura/lectura.

2.1.2.1 Secuencia de escritura desde el host (dirección DH => PN5190) 2.1.2.2 Secuencia de lectura desde el host (Dirección PN5190 => DH)

2.1.2.2 Secuencia de lectura desde el host (Dirección PN5190 => DH) 2.1.3 Protocolo HDLL

2.1.3 Protocolo HDLL

HDLL es un protocolo de comando-respuesta. Todas las operaciones mencionadas anteriormente se activan mediante un comando específico y se validan en función de la respuesta.

Los comandos y las respuestas siguen la sintaxis de mensajes HDLL: el comando lo envía el host del dispositivo y la respuesta el PN5190. El código de operación indica el comando y el tipo de respuesta.

Comunicaciones basadas en HDLL, solo se utilizan cuando se activa el PN5190 para ingresar al modo "Descarga segura de firmware".

2.2 Modo TLV

TLV significa Tag Valor de longitud.

2.2.1 Definición de trama

Un marco SPI comienza con el flanco descendente de NTS y termina con el flanco ascendente de NTS. SPI es dúplex completo por definición física, pero PN5190 usa SPI en un modo semidúplex. El modo SPI está limitado a CPOL 0 y CPHA 0 con una velocidad de reloj máxima como se especifica en [2]. Cada marco SPI se compone de un encabezado de 1 byte y n bytes de cuerpo.

2.2.2 Indicación de caudal El HOST siempre envía como primer byte el byte de indicación de flujo, ya sea que quiera escribir o leer datos del PN5190.

El HOST siempre envía como primer byte el byte de indicación de flujo, ya sea que quiera escribir o leer datos del PN5190.

Si hay una solicitud de lectura y no hay datos disponibles, la respuesta contiene 0xFF.

Los datos después del byte de indicación de flujo son uno o varios mensajes.

Para cada aserción NTS, el primer byte es siempre un ENCABEZADO (byte de indicación de flujo), puede ser 0x7F/0xFF con respecto a la operación de escritura/lectura.

2.2.3 Tipo de mensaje

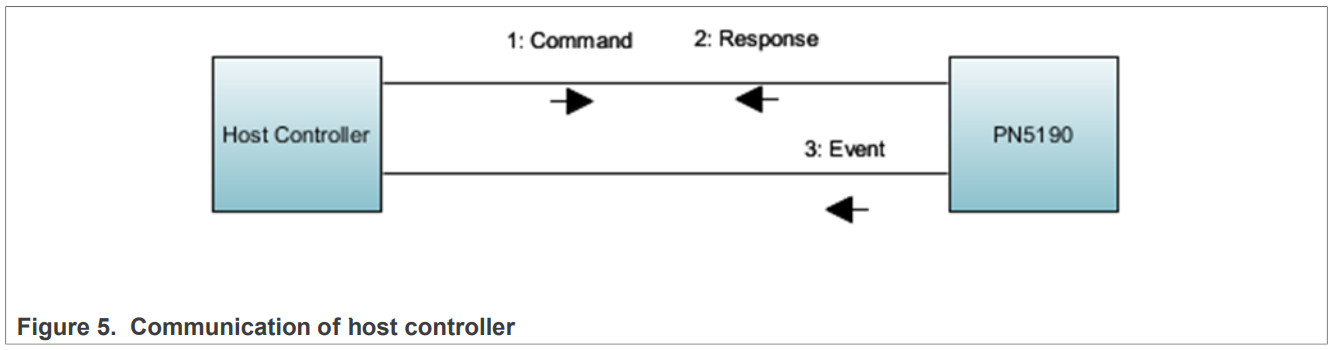

Un controlador de host se comunicará con PN5190 utilizando mensajes que se transportan dentro de tramas SPI.

Hay tres tipos de mensajes diferentes:

- Dominio

- Respuesta

- Evento

El diagrama de comunicación anterior muestra las direcciones permitidas para los diferentes tipos de mensajes de la siguiente manera:

El diagrama de comunicación anterior muestra las direcciones permitidas para los diferentes tipos de mensajes de la siguiente manera:

- Mando y respuesta.

- Los comandos sólo se envían desde el controlador host a PN5190.

- Las respuestas y los eventos solo se envían desde PN5190 al controlador del host.

- Las respuestas a los comandos se sincronizan mediante el pin IRQ.

- El host puede enviar los comandos solo cuando la IRQ es baja.

- El anfitrión puede leer la respuesta/evento solo cuando la IRQ es alta.

2.2.3.1 Secuencias y reglas permitidas Secuencias permitidas de comando, respuesta y eventos

Secuencias permitidas de comando, respuesta y eventos

- Un comando siempre se reconoce mediante una respuesta, un evento o ambos.

- El controlador de host no puede enviar otro comando antes de no haber recibido una respuesta al comando anterior.

- Los eventos pueden enviarse de forma asincrónica en cualquier momento (NO entrelazados dentro de un par comando/respuesta).

- Los mensajes de EVENTO nunca se combinan con los mensajes de RESPUESTA dentro de un cuadro.

Nota: La disponibilidad de un mensaje (ya sea RESPUESTA o EVENTO) se señala con la IRQ subiendo desde baja. La IRQ permanece alta hasta que se lee toda la respuesta o marco de evento. Sólo después de que la señal IRQ sea baja, el host puede enviar el siguiente comando.

2.2.4 Formato del mensaje

Cada mensaje está codificado en una estructura TLV con carga útil de n bytes para cada mensaje excepto para el comando SWITCH_MODE_NORMAL. Cada TLV se compone de:

Cada TLV se compone de: Tipo (T) => 1 byte

Tipo (T) => 1 byte

Bit[7] Tipo de mensaje

0: Mensaje de COMANDO o RESPUESTA

1: mensaje de EVENTO

Bit[6:0]: código de instrucción

Longitud (L) => 2 bytes (debe estar en formato big-endian)

Valor (V) => N bytes de valor/datos del TLV (Parámetros de comando/datos de respuesta) basados en el campo Longitud (formato big-endian)

2.2.4.1 Marco dividido

El mensaje COMMAND debe enviarse en una trama SPI.

Los mensajes de RESPUESTA y EVENTO se pueden leer en múltiples tramas SPI, por ejemplo para leer el byte de longitud. Los mensajes de RESPUESTA o EVENTO se pueden leer en un solo marco SPI pero retrasados por NO-CLOCK en el medio, por ejemplo, para leer el byte de longitud.

Los mensajes de RESPUESTA o EVENTO se pueden leer en un solo marco SPI pero retrasados por NO-CLOCK en el medio, por ejemplo, para leer el byte de longitud.

Modo de arranque operativo IC: modo de descarga segura de FW

3.1 Introducción

Parte del código de firmware PN5190 se almacena permanentemente en la ROM, mientras que el resto del código y los datos se almacenan en la memoria flash integrada. Los datos del usuario se almacenan en flash y están protegidos por mecanismos antidesgarro que aseguran la integridad y disponibilidad de los datos. Para proporcionar a los clientes de NXP funciones que cumplan con los estándares más recientes (EMVCo, NFC Forum, etc.), tanto el código como los datos de usuario en FLASH se pueden actualizar.

La autenticidad y la integridad del firmware encriptado están protegidas por una firma de clave asimétrica/simétrica y un mecanismo hash encadenado inverso. El primer comando DL_SEC_WRITE contiene el hash del segundo comando y está protegido por una firma RSA en la carga útil del primer marco. El firmware PN5190 usa la clave pública RSA para autenticar el primer comando. El hash encadenado en cada comando se utiliza para autenticar el comando posterior, para garantizar que terceros no accedan al código de firmware y a los datos.

Las cargas útiles de los comandos DL_SEC_WRITE se cifran con una clave AES-128. Después de la autenticación de cada comando, el contenido de la carga útil se descifra y se escribe en la memoria flash mediante el firmware PN5190.

Para el firmware de NXP, NXP es responsable de entregar nuevas actualizaciones de firmware seguras, junto con nuevos datos de usuario.

El procedimiento de actualización está equipado con un mecanismo para proteger la autenticidad, integridad y confidencialidad del código y los datos de NXP.

El esquema de paquetes de tramas basado en HDLL se utiliza para todos los comandos y respuestas del modo de actualización de firmware seguro.

La Sección 2.1 proporciona másview del esquema de paquetes de tramas HDLL utilizado.

Los circuitos integrados PN5190 admiten tanto la descarga de FW segura cifrada heredada como el protocolo de descarga de FW seguro cifrado asistido por hardware, según la variante utilizada.

Los dos tipos son:

- Protocolo de descarga de FW seguro heredado que funciona solo con la versión IC PN5190 B0/B1.

- Protocolo de descarga de firmware seguro asistido por criptografía de hardware que funciona solo con la versión IC PN5190B2 y que utiliza bloques criptográficos de hardware en el chip.

Las siguientes secciones explican los comandos y las respuestas del modo de descarga segura de firmware.

3.2 Cómo activar el modo "Descarga segura de firmware"

El siguiente diagrama y los pasos posteriores muestran cómo activar el modo de descarga de firmware seguro. Condición previa: PN5190 está en estado de funcionamiento.

Condición previa: PN5190 está en estado de funcionamiento.

Escenario principal:

- Condición de entrada donde se utiliza el pin DWL_REQ para ingresar al modo "Descarga segura de firmware".

a. El host del dispositivo coloca el pin DWL_REQ en alto (válido solo si la actualización del firmware es segura a través del pin DWL_REQ) O

b. El host del dispositivo realiza un reinicio completo para iniciar el PN5190 - Condición de entrada donde el pin DWL_REQ no se utiliza para ingresar al modo "Descarga de firmware segura" (descarga sin PIN).

a. El host del dispositivo realiza un reinicio completo para iniciar el PN5190

b. El host del dispositivo envía SWITCH_MODE_NORMAL (Sección 4.5.4.5) para ingresar al modo de aplicación normal.

C. Ahora, cuando IC está en modo normal de aplicación, el host del dispositivo envía SWITCH_MODE_DOWNLOAD (Sección 4.5.4.9) para ingresar al modo de descarga segura. - El host del dispositivo envía el comando DL_GET_VERSION (Sección 3.4.4), o DL_GET_DIE_ID (Sección 3.4.6), o DL_GET_SESSION_STATE (Sección 3.4.5).

- El host del dispositivo lee la versión actual de hardware y firmware, la sesión y el Die-id del dispositivo.

a. El host del dispositivo verifica el estado de la sesión si se completó la última descarga

b. El host del dispositivo aplica las reglas de verificación de versión para decidir si iniciar o salir de la descarga. - El host del dispositivo se carga desde un file el código binario del firmware que se descargará

- El host del dispositivo proporciona un primer comando DL_SEC_WRITE (Sección 3.4.8) que contiene:

a. La versión del nuevo firmware,

b. Un nonce de 16 bytes de valores arbitrarios utilizados para la ofuscación de la clave de cifrado

C. Un valor de resumen del siguiente fotograma,

d. La firma digital del propio marco. - El host del dispositivo carga la secuencia del protocolo de descarga segura en el PN5190 con los comandos DL_SEC_WRITE (Sección 3.4.8)

- Cuando se ha enviado el último comando DL_SEC_WRITE (Sección 3.4.8), el host del dispositivo ejecuta el comando DL_CHECK_INTEGRITY (Sección 3.4.7) para comprobar si las memorias se han escrito correctamente.

- El host del dispositivo lee la nueva versión del firmware y verifica el estado de la sesión si está cerrada para informar a la capa superior

- El host del dispositivo baja el pin DWL_REQ (si el pin DWL_REQ se usa para ingresar al modo de descarga)

- El host del dispositivo realiza un restablecimiento completo (alternando el pin VEN) en el dispositivo para reiniciar el PN5190

Condición posterior: el firmware está actualizado; se informa el nuevo número de versión del firmware.

3.3 Firma de firmware y control de versiones

En el modo de descarga de firmware PN5190, un mecanismo garantiza que solo se aceptará un firmware firmado y entregado por NXP para el firmware de NXP.

Lo siguiente es aplicable solo para el firmware NXP seguro cifrado.

Durante una sesión de descarga, se envía una nueva versión de firmware de 16 bits. Se compone de un número mayor y un número menor:

- Número mayor: 8 bits (MSB)

- Número menor: 8 bits (LSB)

El PN5190 comprueba si el nuevo número de versión principal es mayor o igual al actual. De lo contrario, se rechaza la descarga segura del firmware y la sesión se mantiene cerrada.

3.4 Comandos HDLL para descargas cifradas heredadas y asistidas por hardware criptográfico descarga cifrada

Esta sección proporciona información sobre los comandos y las respuestas que se usaron para ambos tipos de descargas para la descarga de firmware de NXP.

3.4.1 Códigos OP de comando HDLL

Nota: Los marcos de comando HDLL están alineados con 4 bytes. Los bytes de carga útil no utilizados se dejan en cero.

Tabla 1. Lista de códigos OP de comando HDLL

| PN5190 B0/B1 (Descarga heredada) |

PN5190 B2 (Descarga asistida por criptografía) |

Alias de comando | Descripción |

| 0xF0 | 0xE5 | DL_RESET | Realiza un reinicio por software |

| 0xF1 | 0xE1 | DL_GET_VERSION | Devuelve los números de versión. |

| 0xF2 | 0xDB | DL_GET_SESSION_STATE | Devuelve el estado de la sesión actual. |

| 0xF4 | 0xDF | DL_GET_DIE_ID | Devuelve el ID del troquel |

| 0xE0 | 0xE7 | DL_CHECK_INTEGRIDAD | Comprueba y devuelve los CRC en las diferentes áreas, así como los indicadores de estado de aprobación/rechazo para cada una. |

| 0xC0 | 0x8C | DL_SEC_ESCRIBIR | Escribe x bytes en la memoria comenzando en la dirección absoluta y |

3.4.2 Códigos de operación de respuesta HDLL

Nota: Las tramas de respuesta HDLL están alineadas en 4 bytes. Los bytes de carga útil no utilizados se dejan en cero. Solo las respuestas DL_OK pueden contener valores de carga útil.

Tabla 2. Lista de códigos OP de respuesta HDLL

| código de operación | Alias de respuesta | Descripción |

| 0x00 | DL_OK | comando pasado |

| 0x01 | DL_INVALID_ADDR | Dirección no permitida |

| 0x0B | DL_UNKNOW_CMD | Comando desconocido |

| 0x0C | DL_ABORTED_CMD | La secuencia de fragmentos es demasiado grande |

| 0x1E | DL_ADDR_RANGE_OFL_ERROR | Dirección fuera de rango |

| 0x1F | DL_BUFFER_OFL_ERROR | El búfer es demasiado pequeño |

| 0x20 | DL_MEM_BSY | Memoria ocupada |

| 0x21 | DL_SIGNATURE_ERROR | La firma no coincide |

| 0x24 | DL_FIRMWARE_VERSION_ERROR | Versión actual igual o superior |

| 0x28 | DL_PROTOCOL_ERROR | Error de protocolo |

| 0x2A | DL_SFWU_DEGRADADO | Corrupción de datos flash |

| 0x2D | PH_STATUS_DL_FIRST_CHUNK | Primer trozo recibido |

| 0x2E | PH_STATUS_DL_NEXT_CHUNK | Espera el siguiente fragmento |

| 0xC5 | PH_STATUS_INTERNAL_ERROR_5 | Longitud no coincidente |

3.4.3 Comando DL_RESET

Intercambio de cuadros:

PN5190 B0/B1: [HDLL] -> [0x00 0x04 0xF0 0x00 0x00 0x00 0x18 0x5B]

PN5190 B2: [HDLL] -> [0x00 0x04 0xE5 0x00 0x00 0x00 0xBF 0xB9] [HDLL] <- [0x00 0x04 STAT 0x00 CRC16] El reinicio evita que el PN5190 envíe la respuesta DL_STATUS_OK. Por lo tanto, sólo se pueden recibir estados erróneos.

STAT es el estado de devolución.

3.4.4 Comando DL_GET_VERSION

Intercambio de cuadros:

PN5190 B0/B1: [HDLL] -> [0x00 0x04 0xF1 0x00 0x00 0x00 0x6E 0xEF]

PN5190 B2: [HDLL] -> [0x00 0x04 0xE1 0x00 0x00 0x00 0x75 0x48] [HDLL] <- [0x00 0x08 STAT HW_V RO_V MODEL_ID FM1V FM2V RFU1 RFU2 CRC16] La trama de carga útil de la respuesta GetVersion es:

Tabla 3. Respuesta al comando GetVersion

| Campo | Byte | Descripción |

| ESTADÍSTICA | 1 | Estado |

| HW_V | 2 | Versión de hardware |

| RO_V | 3 | codigo rom |

| MODELO_ID | 4 | Modelo ID |

| FM x V | 5-6 | Versión de firmware (utilizada para la descarga) |

| RFU1-RFU2 | 7-8 | – |

Los valores esperados de diferentes campos de respuesta y su mapeo son los siguientes:

Tabla 4. Valores esperados de la respuesta del comando GetVersion

| Tipo de IC | Versión HW (hexadecimal) | Versión ROM (hexadecimal) | ID del modelo (hexadecimal) | Versión FW (hexadecimal) |

| PN5190 B0 | 0x51 | 0x02 | 0x00 | xx.yy |

| PN5190 B1 | 0x52 | 0x02 | 0x00 | xx.yy |

| PN5190 B2 | 0x53 | 0x03 | 0x00 | xx.yy |

3.4.5 Comando DL_GET_SESSION_STATE

Intercambio de cuadros:

PN5190 B0/B1: [HDLL] -> [0x00 0x04 0xF2 0x00 0x00 0x00 0xF5 0x33]

PN5190 B2: [HDLL] -> [0x00 0x04 0xDB 0x00 0x00 0x00 0x31 0x0A] [HDLL] <- [0x00 0x04 STAT SSTA RFU CRC16] El marco de carga útil de la respuesta GetSession es:

Tabla 5. Respuesta al comando GetSession

| Campo | Byte | Descripción |

| ESTADÍSTICA | 1 | Estado |

| SSTA | 2 | Estado de la sesión • 0x00: cerrado • 0x01: abierto • 0x02: bloqueado (ya no se permite la descarga) |

| RFU | 3-4 |

3.4.6 Comando DL_GET_DIE_ID

Intercambio de cuadros:

PN5190 B0/B1: [HDLL] -> [0x00 0x04 0xF4 0x00 0x00 0x00 0xD2 0xAA]

PN5190 B2: [HDLL] -> [0x00 0x04 0xDF 0x00 0x00 0x00 0xFB 0xFB] [HDLL] <- [0x00 0x14 STAT 0x00 0x00 0x00 ID0 ID1 ID2 ID3 ID4 ID5 ID6 ID7 ID8 ID9

ID10 ID11 ID12 ID13 ID14 ID15 CRC16] El marco de carga útil de la respuesta GetDieId es:

Tabla 6. Respuesta al comando GetDieId

| Campo | Byte | Descripción |

| ESTADÍSTICA | 1 | Estado |

| RFU | 2-4 | |

| MUERTO | 5-20 | ID del dado (16 bytes) |

3.4.7 Comando DL_CHECK_INTEGRITY

Intercambio de cuadros:

PN5190 B0/B1: [HDLL] -> [0x00 0x04 0xE0 0x00 0x00 0x00 CRC16]

PN5190 B2: [HDLL] -> [0x00 0x04 0xE7 0x00 0x00 0x00 0x52 0xD1] [HDLL] <- [0x00 0x20 STAT LEN_DATA LEN_CODE 0x00 [CRC_INFO] [CRC32] CRC16] El marco de carga útil de la respuesta CheckIntegrity es:

Tabla 7. Respuesta al comando CheckIntegrity

| Campo | Byte | Valor / Descripción | |

| ESTADÍSTICA | 1 | Estado | |

| DATOS DE LEN | 2 | Número total de secciones de datos | |

| CÓDIGO LEN | 3 | Número total de secciones de código | |

| RFU | 4 | Reservado | |

| [CRC_INFO] | 58 | 32 bits (little-endian). Si se establece un bit, el CRC de la sección correspondiente está bien; de lo contrario, no está bien. | |

| Poco | Estado de integridad del área | ||

| [31:28] | Reservado [3] | ||

| [27:23] | Reservado [1] | ||

| [22] | Reservado [3] | ||

| [21:20] | Reservado [1] | ||

| [19] | Área de configuración de RF (PN5190 B0/B1) [2] Reservado (PN5190 B2) [3] | ||

| [18] | Área de configuración de protocolo (PN5190 B0/B1) [2] Área de configuración de RF (PN5190 B2) [2] | ||

| [17] | Reservado (PN5190 B0/B1) [3] Área de configuración de usuario (PN5190 B2) [2] | ||

| [16:6] | Reservado [3] | ||

| [5:4] | Reservado para PN5190 B0/B1 [3] Reservado para PN5190 B2 [1] | ||

| [3:0] | Reservado [1] | ||

| [CRC32] | 9-136 | CRC32 de las 32 secciones. Cada CRC es de 4 bytes almacenados en formato little-endian. Los primeros 4 bytes de CRC son del bit CRC_INFO[31], los siguientes 4 bytes de CRC son del bit CRC_INFO[30] y así sucesivamente. |

|

- [1] Este bit debe ser 1 para que el PN5190 funcione correctamente (con funciones o descarga de firmware cifrado).

- [2] Este bit está establecido en 1 de forma predeterminada, pero la configuración modificada por el usuario invalida el CRC. Ningún efecto sobre la funcionalidad PN5190.

- [3] Este valor de bit, incluso si es 0, no es relevante. Este valor de bit se puede ignorar.

3.4.8 Comando DL_SEC_WRITE

El comando DL_SEC_WRITE se debe considerar en el contexto de una secuencia de comandos de escritura segura: la "descarga segura de firmware" encriptada (a menudo denominada eSFWu).

El comando de escritura segura primero abre la sesión de descarga y pasa la autenticación RSA. Los siguientes pasan direcciones y bytes encriptados para escribir en el Flash PN5190. Todos, excepto el último, contienen el hash de los siguientes, por lo tanto, informan que no son los últimos y unen criptográficamente los cuadros de secuencia.

Se pueden insertar otros comandos (excepto DL_RESET y DL_CHECK_INTEGRITY) entre los comandos de escritura seguros de una secuencia sin romperla.

3.4.8.1 Primer comando DL_SEC_WRITE

Un comando de escritura seguro es el primero si y solo si:

- La longitud del marco es de 312 bytes.

- No se ha recibido ningún comando de escritura segura desde el último reinicio.

- La firma incorporada es verificada exitosamente por el PN5190.

La respuesta al comando del primer cuadro sería la siguiente: [HDLL] <- [0x00 0x04 STAT 0x00 0x00 0x00 CRC16] STAT es el estado de retorno.

Nota: Se debe escribir al menos un fragmento de datos durante un eSFWu, aunque los datos escritos solo tengan una longitud de un byte. Por tanto, el primer comando siempre contendrá el hash del siguiente comando, ya que habrá al menos dos comandos.

3.4.8.2 Comandos DL_SEC_WRITE intermedios

Un comando de escritura segura es "intermedio" si y sólo si:

- El código de operación es el descrito en la Sección 3.4.1 para el comando DL_SEC_WRITE.

- Ya se recibió y se verificó con éxito un primer comando de escritura segura antes

- No se ha producido ningún reinicio desde que se recibió el primer comando de escritura segura

- La longitud del marco es igual al tamaño de los datos + tamaño del encabezado + tamaño del hash: FLEN = TAMAÑO + 6 + 32

- El resumen de todo el cuadro es igual al valor hash recibido en el cuadro anterior

La respuesta al comando del primer cuadro sería la siguiente: [HDLL] <- [0x00 0x04 STAT 0x00 0x00 0x00 CRC16] STAT es el estado de retorno.

3.4.8.3 Último comando DL_SEC_WRITE

Un comando de escritura segura es el último si y sólo si:

- El código de operación es el descrito en la Sección 3.4.1 para el comando DL_SEC_WRITE.

- Ya se recibió y se verificó con éxito un primer comando de escritura segura antes

- No se ha producido ningún reinicio desde que se recibió el primer comando de escritura segura

- La longitud del marco es igual al tamaño de los datos + tamaño del encabezado: FLEN = TAMAÑO + 6

- El resumen de todo el cuadro es igual al valor hash recibido en el cuadro anterior

La respuesta al comando del primer cuadro sería la siguiente: [HDLL] <- [0x00 0x04 STAT 0x00 0x00 0x00 CRC16] STAT es el estado de retorno.

Modo de arranque operativo IC: modo de funcionamiento normal

4.1 Introducción

Generalmente, el PN5190 IC debe estar en modo de funcionamiento normal para obtener la funcionalidad NFC.

Cuando se inicia el PN5190 IC, siempre está esperando que se reciban comandos de un host para realizar la operación, a menos que los eventos generados dentro del PN5190 IC provoquen el inicio del PN5190 IC.

4.2 Lista de comandosview

Tabla 8. Lista de comandos PN5190

| código de comando | Nombre del comando |

| 0x00 | ESCRIBIR_REGISTRAR |

| 0x01 | ESCRIBIR_REGISTER_OR_MASK |

| 0x02 | ESCRIBIR_REGISTRO_Y_MASCARILLA |

| 0x03 | ESCRIBIR_REGISTER_MULTIPLE |

| 0x04 | LEER_REGISTRAR |

| 0x05 | LEER_REGISTER_MULTIPLE |

| 0x06 | ESCRIBIR_E2PROM |

| 0x07 | LEER_E2PROM |

| 0x08 | TRANSMITIR_RF_DATOS |

| 0x09 | RECUPERAR_RF_DATOS |

| 0x0A | EXCHANGE_RF_DATA |

| 0x0B | MFC_AUTENTIFICAR |

| 0x0C | EPC_GEN2_INVENTARIO |

| 0x0D | CARGAR_RF_CONFIGURACIÓN |

| 0x0E | ACTUALIZAR_RF_CONFIGURACIÓN |

| 0x0F | GET_RF_CONFIGURACIÓN |

| 0x10 | RF_ON |

| 0x11 | RF_DESACTIVADO |

| 0x12 | CONFIGURAR TESTBUS_DIGITAL |

| 0x13 | CONFIGURE_TESTBUS_ANALOG |

| 0x14 | CTS_ENABLE |

| 0x15 | CTS_CONFIGURAR |

| 0x16 | CTS_RETRIEVE_LOG |

| 0x17-0x18 | RFU |

| 0x19 | hasta FW v2.01: RFU |

| desde FW v2.03 en adelante: RETRIEVE_RF_FELICA_EMD_DATA | |

| 0x1A | RECIBIR_RF_DATOS |

| 0x1B-0x1F | RFU |

| 0x20 | INTERRUPTOR_MODO_NORMAL |

| 0x21 | SWITCH_MODE_AUTOCOLL |

| 0x22 | INTERRUPTOR_MODO_ESPERA |

| 0x23 | INTERRUPTOR_MODO_LPCD |

| 0x24 | RFU |

| 0x25 | CAMBIAR_MODO_DESCARGAR |

| 0x26 | GET_DIEID |

| 0x27 | GET_VERSION |

| 0x28 | RFU |

| 0x29 | hasta FW v2.05: RFU |

| desde FW v2.06 en adelante: GET_CRC_USER_AREA | |

| 0x2A | hasta FW v2.03: RFU |

| desde FW v2.05 en adelante: CONFIGURE_MULTIPLE_TESTBUS_DIGITAL | |

| 0x2B-0x3F | RFU |

| 0x40 | ANTENNA_SELF_TEST (No compatible) |

| 0x41 | PRBS_TEST |

| 0x42-0x4F | RFU |

4.3 Valores de estado de respuesta

Los siguientes son los valores de estado de respuesta, que se devuelven como parte de la respuesta de PN5190 después de que se pone en funcionamiento el comando.

Tabla 9. Valores de estado de respuesta de PN5190

| Estado de respuesta | Valor de estado de respuesta | Descripción |

| PN5190_ESTADO_ÉXITO | 0x00 | Indica que la operación se completó con éxito |

| PN5190_STATUS_TIMEOUT | 0x01 | Indica que la operación del comando resultó en tiempo de espera |

| PN5190_STATUS_INTEGRITY_ERROR | 0x02 | Indica que la operación del comando resultó en un error de integridad de datos de RF |

| PN5190_STATUS_RF_COLLISION_ERROR | 0x03 | Indica que la operación del comando resultó en un error de colisión de RF |

| PN5190_STATUS_RFU1 | 0x04 | Reservado |

| PN5190_STATUS_INVALID_COMMAND | 0x05 | Indica que el comando dado no es válido/no está implementado |

| PN5190_STATUS_RFU2 | 0x06 | Reservado |

| PN5190_STATUS_AUTH_ERROR | 0x07 | Indica que la autenticación MFC falló (permiso denegado) |

| PN5190_STATUS_MEMORY_ERROR | 0x08 | Indica que la operación del comando resultó en un error de programación o error de memoria interna |

| PN5190_STATUS_RFU4 | 0x09 | Reservado |

| PN5190_STATUS_NO_RF_FIELD | 0x0A | Indica que no hay presencia de campo de RF interno o hay un error (aplicable solo si está en modo iniciador/lector) |

| PN5190_STATUS_RFU5 | 0x0B | Reservado |

| PN5190_STATUS_SYNTAX_ERROR | 0x0C | Indica que se recibe una longitud de trama de comando no válida |

| PN5190_STATUS_RESOURCE_ERROR | 0x0D | Indica que ocurrió un error de recurso interno |

| PN5190_STATUS_RFU6 | 0x0E | Reservado |

| PN5190_STATUS_RFU7 | 0x0F | Reservado |

| PN5190_STATUS_NO_EXTERNAL_RF_FIELD | 0x10 | Indica que no hay ningún campo RF externo presente durante la ejecución del comando (Aplicable solo en modo tarjeta/objetivo) |

| PN5190_STATUS_RX_TIMEOUT | 0x11 | Indica que los datos no se reciben después de que se inicia RFExchange y se agota el tiempo de RX. |

| PN5190_STATUS_USER_CANCELLED | 0x12 | Indica que se abortó el comando actual en curso |

| PN5190_STATUS_PREVENT_STANDBY | 0x13 | Indica que se impide que PN5190 entre en modo de espera |

| PN5190_STATUS_RFU9 | 0x14 | Reservado |

| PN5190_STATUS_CLOCK_ERROR | 0x15 | Indica que reloj al CLIF no arrancó |

| PN5190_STATUS_RFU10 | 0x16 | Reservado |

| PN5190_STATUS_PRBS_ERROR | 0x17 | Indica que el comando PRBS devolvió un error |

| PN5190_STATUS_INSTR_ERROR | 0x18 | Indica que la operación del comando falló (puede incluir un error en los parámetros de la instrucción, un error de sintaxis, un error en la operación en sí, no se cumplen los requisitos previos para la instrucción, etc.) |

| PN5190_STATUS_ACCESS_DENIED | 0x19 | Indica que el acceso a la memoria interna está denegado |

| PN5190_STATUS_TX_FAILURE | 0x1A | Indica que TX sobre RF ha fallado |

| PN5190_STATUS_NO_ANTENA | 0x1B | Indica que no hay antena conectada/presente |

| PN5190_STATUS_TXLDO_ERROR | 0x1C | Indica que hay un error en TXLDO cuando el VUP no está disponible y RF está encendido. |

| PN5190_ESTADO_RFCFG_NO_APLICADO | 0x1D | Indica que la configuración de RF no se carga cuando se enciende RF |

| PN5190_STATUS_TIMEOUT_WITH_EMD_ERROR | 0x1E | hasta FW 2.01: no esperado |

| desde FW 2.03 en adelante: Indica que durante el intercambio con LOG ENABLE BIT configurado en el registro FeliCa EMD, se observó un error FeliCa EMD |

||

| PN5190_STATUS_INTERNAL_ERROR | 0x7F | Indica que la operación de NVM falló |

| PN5190_STATUS_SUCCSES_CHAINING | 0xAF | Indica que, además, hay datos pendientes de leer |

4.4 Eventos finalizadosview

Hay dos formas en que los eventos se notifican al host.

4.4.1 Eventos normales sobre pin IRQ

Estos eventos son categorías de la siguiente manera:

- Siempre habilitado: el host siempre recibe una notificación

- Controlado por el host: se notifica al host si el bit de habilitación de evento respectivo está establecido en el registro (EVENT_ENABLE (01h)).

Las interrupciones de bajo nivel de las IP periféricas, incluida la CLIF, se manejarán por completo dentro del firmware y el host solo será notificado de los eventos enumerados en la sección de eventos.

El firmware implementa dos registros de eventos como registros RAM que se pueden escribir/leer usando los comandos de la Sección 4.5.1.1/Sección 4.5.1.5.

El registro EVENT_ENABLE (0x01) => Habilitar notificaciones específicas/de todos los eventos.

El registro EVENT_STATUS (0x02) => Parte de la carga útil del mensaje de evento.

Los eventos serán borrados por el host una vez que el host lea el mensaje del evento.

Los eventos son de naturaleza asíncrona y se notifican al host, si están habilitados dentro del registro EVENT_ENABLE.

A continuación se muestra la lista de eventos que estarán disponibles para el host como parte del mensaje de evento.

Tabla 10. Eventos PN5190 (contenido de EVENT_STATUS)

| Bit – Rango | Campo [1] | Siempre Habilitado (S/N) | |

| 31 | 12 | RFU | NA |

| 11 | 11 | CTS_EVENTO [2] | N |

| 10 | 10 | IDLE_EVENT | Y |

| 9 | 9 | LPCD_CALIBRATION_DONE_EVENT | Y |

| 8 | 8 | LPCD_EVENT | Y |

| 7 | 7 | AUTOCOLL_EVENT | Y |

| 6 | 6 | TIMER0_EVENT | N |

| 5 | 5 | TX_OVERCURRENT_EVENT | N |

| 4 | 4 | RFON_DET_EVENT [2] | N |

| 3 | 3 | RFOFF_DET_EVENT [2] | N |

| 2 | 2 | STANDBY_PREV_EVENT | Y |

| 1 | 1 | GENERAL_ERROR_EVENT | Y |

| 0 | 0 | BOOT_EVENT | Y |

- Tenga en cuenta que no se superan dos eventos excepto en caso de errores. En caso de errores durante la operación, se establecerán eventos funcionales (por ejemplo, BOOT_EVENT, AUTOCALL_EVENT, etc.) y GENERAL_ERROR_EVENT.

- Este evento se desactivará automáticamente después de que se publique en el anfitrión. El anfitrión debe habilitar nuevamente estos eventos si desea que se le notifiquen.

4.4.1.1 Formatos de mensajes de eventos

El formato del mensaje de evento difiere según las ocurrencias de un evento y el estado diferente del PN5190.

El anfitrión debe leer tag (T) y la longitud del mensaje (L) y luego leer el número correspondiente de bytes como valor (V) de los eventos.

En general, el mensaje de evento (consulte la Figura 12) contiene EVENT_STATUS como se define en la Tabla 11 y los datos del evento corresponden al bit de evento respectivo establecido en EVENT_STATUS.

Nota:

Para algunos eventos, la carga útil no existe. Por ejemplo, si se activa TIMER0_EVENT, solo se proporciona EVENT_STATUS como parte del mensaje de evento.

La Tabla 11 también detalla si los datos del evento están presentes para el evento correspondiente en el mensaje de evento. GENERAL_ERROR_EVENT también puede ocurrir con otros eventos.

GENERAL_ERROR_EVENT también puede ocurrir con otros eventos.

En este escenario, el mensaje de evento (consulte la Figura 13) contiene EVENT_STATUS como se define en la Tabla 11 y GENERAL_ERROR_STATUS_DATA como se define en la Tabla 14 y luego los datos del evento corresponden al bit de evento respectivo establecido en EVENT_STATUS como se define en la Tabla 11. Nota:

Nota:

Solo después de BOOT_EVENT o después de POR, STANDBY, ULPCD, el host podrá trabajar en el modo de operación normal emitiendo los comandos enumerados anteriormente.

En caso de cancelar un comando en ejecución existente, solo después de IDLE_EVENT, el host podrá trabajar en el modo de operación normal emitiendo los comandos enumerados anteriormente.

4.4.1.2 Diferentes definiciones de estado de EVENTO

4.4.1.2.1 Definiciones de bits para EVENT_STATUS

Tabla 11. Definiciones para bits EVENT_STATUS

| Bit (A – Desde) | Evento | Descripción | Datos del evento del evento correspondiente. (si hay alguna) |

|

| 31 | 12 | RFU | Reservado | |

| 11 | 11 | CTS_EVENTO | Este bit se establece cuando se genera un evento CTS. | Tabla 86 |

| 10 | 10 | IDLE_EVENT | Este bit se establece cuando el comando en curso se cancela debido a la emisión del comando SWITCH_MODE_NORMAL. | Sin datos de eventos |

| 9 | 9 | LPCD_CALIBRATION_DONE_ EVENTO |

Este bit se establece cuando se genera el evento de calibración LPCD. | Tabla 16 |

| 8 | 8 | LPCD_EVENT | Este bit se establece cuando se genera el evento LPCD. | Tabla 15 |

| 7 | 7 | AUTOCOLL_EVENT | Este bit se establece cuando se completa la operación AUTOCOLL. | Tabla 52 |

| 6 | 6 | TIMER0_EVENT | Este bit se establece cuando ocurre el evento TIMER0. | Sin datos de eventos |

| 5 | 5 | TX_OVERCURRENT_ERROR_ EVENTO |

Este bit se establece cuando la corriente en el controlador TX es mayor que el umbral definido en la EEPROM. En esta condición, el campo se apaga automáticamente antes de la notificación al host. Consulte la Sección 4.4.2.2. | Sin datos de eventos |

| 4 | 4 | RFON_DET_EVENT | Este bit se establece cuando se detecta el campo de RF externo. | Sin datos de eventos |

| 3 | 3 | RFOFF_DET_EVENT | Este bit se establece cuando desaparece el campo RF externo ya existente. | Sin datos de eventos |

| 2 | 2 | STANDBY_PREV_EVENT | Este bit se establece cuando se impide el modo de espera debido a que existen condiciones de prevención. | Tabla 13 |

| 1 | 1 | GENERAL_ERROR_EVENT | Este bit se establece cuando existen condiciones generales de error. | Tabla 14 |

| 0 | 0 | BOOT_EVENT | Este bit se establece cuando PN5190 se inicia con POR/Standby | Tabla 12 |

4.4.1.2.2 Definiciones de bits para BOOT_STATUS_DATA

Tabla 12. Definiciones para bits BOOT_STATUS_DATA

| poco a | Bit de | Estado de arranque | Razón de arranque debido a |

| 31 | 27 | RFU | Reservado |

| 26 | 26 | ULP_ESPERA | Motivo de inicio debido a la salida de ULP_STANDBY. |

| 25 | 23 | RFU | Reservado |

| 22 | 22 | BOOT_RX_ULPDET | RX ULPDET provocó el arranque en modo ULP-Standby |

| 21 | 21 | RFU | Reservado |

| 20 | 20 | BOOT_SPI | Motivo de arranque debido a que la señal SPI_NTS está baja |

| 19 | 17 | RFU | Reservado |

| 16 | 16 | BOOT_GPIO3 | Motivo de arranque debido a la transición de GPIO3 de bajo a alto. |

| 15 | 15 | BOOT_GPIO2 | Motivo de arranque debido a la transición de GPIO2 de bajo a alto. |

| 14 | 14 | BOOT_GPIO1 | Motivo de arranque debido a la transición de GPIO1 de bajo a alto. |

| 13 | 13 | BOOT_GPIO0 | Motivo de arranque debido a la transición de GPIO0 de bajo a alto. |

| 12 | 12 | BOOT_LPDET | Motivo de arranque debido a la presencia de un campo RF externo durante STANDBY/SUSPEND |

| 11 | 11 | RFU | Reservado |

| 10 | 8 | RFU | Reservado |

| 7 | 7 | BOOT_SOFT_RESET | Motivo de arranque debido a un restablecimiento parcial de IC |

| 6 | 6 | BOOT_VDDIO_LOSS | Motivo de arranque debido a la pérdida de VDDIO. Consulte la Sección 4.4.2.3 |

| 5 | 5 | BOOT_VDDIO_START | Motivo de inicio si se ingresó STANDBY con VDDIO LOSS. Consulte la Sección 4.4.2.3 |

| 4 | 4 | BOOT_WUC | Motivo de arranque debido a que transcurrió el contador de activación durante cualquiera de las operaciones de ESPERA. |

| 3 | 3 | BOOT_TEMP | El motivo de arranque debido a que la temperatura del IC supera el límite de umbral configurado. Consulte la Sección 4.4.2.1 |

| 2 | 2 | BOOT_WDG | Razón de arranque debido al restablecimiento del perro guardián |

| 1 | 1 | RFU | Reservado |

| 0 | 0 | BOOT_POR | Razón de arranque debido al reinicio de encendido |

4.4.1.2.3 Definiciones de bits para STANDBY_PREV_STATUS_DATA

Tabla 13. Definiciones para bits STANDBY_PREV_STATUS_DATA

| poco a | Bit de | Prevención en espera | Standby impedido debido a |

| 31 | 26 | RFU | RESERVADO |

| 25 | 25 | RFU | RESERVADO |

| 24 | 24 | ANTERIOR_TEMP | La temperatura de funcionamiento de los circuitos integrados está fuera del umbral |

| 23 | 23 | RFU | RESERVADO |

| 22 | 22 | ANTERIOR_HOSTCOMM | Comunicación de interfaz de host |

| 21 | 21 | ANTERIOR_SPI | Señal SPI_NTS baja |

| 20 | 18 | RFU | RESERVADO |

| 17 | 17 | ANTERIOR_GPIO3 | Señal GPIO3 en transición de baja a alta |

| 16 | 16 | ANTERIOR_GPIO2 | Señal GPIO2 en transición de baja a alta |

| 15 | 15 | ANTERIOR_GPIO1 | Señal GPIO1 en transición de baja a alta |

| 14 | 14 | ANTERIOR_GPIO0 | Señal GPIO0 en transición de baja a alta |

| 13 | 13 | ANTERIOR_WUC | Contador de despertador transcurrido |

| 12 | 12 | ANTERIOR_LPDET | Detección de baja potencia. Ocurre cuando se detecta una señal de RF externa en el proceso de pasar al modo de espera. |

| 11 | 11 | PREV_RX_ULPDET | Detección de potencia ultrabaja RX. Ocurre cuando se detecta una señal de RF en el proceso de ir a ULP_STANDBY. |

| 10 | 10 | RFU | RESERVADO |

| 9 | 5 | RFU | RESERVADO |

| 4 | 4 | RFU | RESERVADO |

| 3 | 3 | RFU | RESERVADO |

| 2 | 2 | RFU | RESERVADO |

| 1 | 1 | RFU | RESERVADO |

| 0 | 0 | RFU | RESERVADO |

4.4.1.2.4 Definiciones de bits para GENERAL_ERROR_STATUS_DATA

Tabla 14. Definiciones para bits GENERAL_ERROR_STATUS_DATA

| poco a | Un poco de | Estado de error | Descripción |

| 31 | 6 | RFU | Reservado |

| 5 | 5 | XTAL_START_ERROR | El inicio de XTAL falló durante el arranque |

| 4 | 4 | SYS_TRIM_RECOVERY_ERROR | Ocurrió un error de memoria de recorte del sistema interno, pero la recuperación falló. El sistema funciona en modo degradado. |

| 3 | 3 | SYS_TRIM_RECOVERY_SUCCESS | Se produjo un error de memoria de recorte del sistema interno y la recuperación se realizó correctamente. El host debe reiniciar el PN5190 para que la recuperación surta efecto. |

| 2 | 2 | TXLDO_ERROR | Error TXLDO |

| 1 | 1 | ERROR_RELOJ | Error de reloj |

| 0 | 0 | GPADC_ERROR | error ADC |

4.4.1.2.5 Definiciones de bits para LPCD_STATUS_DATA

Tabla 15. Definiciones para bytes LPCD_STATUS_DATA

| poco a | Bit de | Aplicabilidad de los bits de estado según la operación subyacente de LPCD o ULPCD | La descripción del bit correspondiente se establece en el byte de estado. | ||

| CDLP | ULPCD | ||||

| 31 | 7 | RFU | Reservado | ||

| 6 | 6 | Abortar_HIF | Y | N | Abortado debido a la actividad HIF |

| 5 | 5 | Error CLKDET | N | Y | Anulado debido a que ocurrió un error CLKDET |

| 4 | 4 | Tiempo de espera XTAL | N | Y | Anulado debido a que se produjo un tiempo de espera XTAL |

| 3 | 3 | VDDPA LDO Sobrecorriente | N | Y | Abortado debido a que se produjo una sobrecorriente de LDO de VDDPA |

| 2 | 2 | Campo de RF externo | Y | Y | Cancelado debido a un campo de RF externo |

| 1 | 1 | Abortar GPIO3 | N | Y | Anulado debido al cambio de nivel de GPIO3 |

| 0 | 0 | Tarjeta detectada | Y | Y | Se detecta la tarjeta |

4.4.1.2.6 Definiciones de bits para LPCD_CALIBRATION_DONE Datos de estado

Tabla 16. Definiciones de bytes de datos de estado LPCD_CALIBRATION_DONE para ULPCD

| poco a | Bit de | Estado de LPCD_CALIBRATION DONE evento | La descripción del bit correspondiente se establece en el byte de estado. |

| 31 | 11 | Reservado | |

| 10 | 0 | Valor de referencia de la calibración ULPCD | El valor RSSI medido durante la calibración ULPCD que se utiliza como referencia durante ULPCD |

Tabla 17. Definiciones de bytes de datos de estado LPCD_CALIBRATION_DONE para LPCD

| poco a | Bit de | Aplicabilidad de los bits de estado según la operación subyacente de LPCD o ULPCD | La descripción del bit correspondiente se establece en el byte de estado. | ||

| 2 | 2 | Campo de RF externo | Y | Y | Cancelado debido a un campo de RF externo |

| 1 | 1 | Abortar GPIO3 | N | Y | Anulado debido al cambio de nivel de GPIO3 |

| 0 | 0 | Tarjeta detectada | Y | Y | Se detecta la tarjeta |

4.4.2 Manejo de diferentes escenarios de arranque

El IC PN5190 maneja diferentes condiciones de error relacionadas con los parámetros del IC como se muestra a continuación.

4.4.2.1 Manejo del escenario de sobretemperatura cuando el PN5190 está en funcionamiento

Cada vez que la temperatura interna del PN5190 IC alcanza el valor umbral configurado en el campo EEPROM TEMP_WARNING [2], el IC entra en modo de espera. Y, en consecuencia, si el campo de EEPROM ENABLE_GPIO0_ON_OVERTEMP [2] está configurado para generar una notificación al host, entonces GPIO0 se elevará para notificar el sobrecalentamiento del IC.

A medida que la temperatura del IC cae por debajo del valor umbral configurado en el campo EEPROM TEMP_WARNING [2], el IC se iniciará con BOOT_EVENT como en la Tabla 11 y el bit de estado de inicio BOOT_TEMP se establecerá como en la Tabla 12 y GPIO0 se reducirá.

4.4.2.2 Manejo de sobrecorriente

Si el IC PN5190 detecta la condición de sobrecorriente, el IC desconecta la alimentación de RF y envía TX_OVERCURRENT_ERROR_EVENT como en la Tabla 11.

La duración de la condición de sobrecorriente se puede controlar modificando el campo EEPROM TXLDO_CONFIG [2].

Para obtener información sobre IC por encima del umbral de corriente, consulte el documento [2].

Nota:

Si hay otros eventos o respuestas pendientes, se enviarán al host.

4.4.2.3 Pérdida de VDDIO durante el funcionamiento

Si el IC PN5190 detecta que no hay VDDIO (pérdida de VDDIO), el IC entra en modo de espera.

El IC arranca solo cuando VDDIO está disponible, con BOOT_EVENT como en la Tabla 11 y el bit de estado de inicio BOOT_VDDIO_START está configurado como en la Tabla 12.

Para obtener información sobre las características estáticas del IC PN5190, consulte el documento [2].

4.4.3 Manejo de escenarios de aborto

El PN5190 IC admite la cancelación de los comandos de ejecución actuales y el comportamiento del PN5190 IC, cuando dicho comando de cancelación, como la Sección 4.5.4.5.2, se envía al PN5190 IC es como se muestra en la Tabla 18.

Nota:

Cuando PN5190 IC está en modo ULPCD y ULP-Standby, no se puede cancelar enviando una Sección 4.5.4.5.2 O iniciando una transacción SPI (al bajar la señal SPI_NTS).

Tabla 18. Respuesta de evento esperada cuando diferentes comandos terminaron con la Sección 4.5.4.5.2

| Comandos | Comportamiento cuando se envía el comando Switch Mode Normal |

| Todos los comandos donde no se ingresa baja potencia | EVENT_STAUS está establecido en "IDLE_EVENT" |

| Cambiar modo LPCD | EVENT_STATUS se establece en "LPCD_EVENT" con "LPCD_ STATUS_DATA" que indica los bits de estado como "Abort_HIF" |

| Cambiar modo de espera | EVENT_STAUS se establece en "BOOT_EVENT" con "BOOT_ STATUS_DATA" que indica los bits "BOOT_SPI" |

| Switch Mode Autocoll (sin modo autónomo, modo autónomo con modo de espera y modo autónomo sin modo de espera) | EVENT_STAUS está configurado en "AUTOCOLL_EVENT" con bits STATUS_DATA que indican que el comando fue cancelado por el usuario. |

4.5 Detalles de las instrucciones de funcionamiento en modo normal

4.5.1 Manipulación de registros

Las instrucciones de esta sección se utilizan para acceder a los registros lógicos de PN5190.

4.5.1.1 ESCRIBIR_REGISTRAR

Esta instrucción se utiliza para escribir un valor de 32 bits (little-endian) en un registro lógico.

4.5.1.1.1 condiciones

La dirección del registro debe existir y el registro debe tener el atributo READ-WRITE o WRITE-ONLY.

4.5.1.1.2 Comando

Tabla 19. Valor del comando WRITE_REGISTER Escribe un valor de 32 bits en un registro.

| Campo de carga útil | Longitud | Valor / Descripción |

| Dirección de registro | 1 bytes | Dirección del registro. |

Tabla 19. Valor del comando WRITE_REGISTER...continuación

Escriba un valor de 32 bits en un registro.

| Campo de carga útil | Longitud | Valor / Descripción |

| Valor | 4 bytes | Valor de registro de 32 bits que se debe escribir. (Little-endian) |

4.5.1.1.3 Respuesta

Tabla 20. Valor de respuesta WRITE_REGISTER

| Campo de carga útil | Longitud | Valor / Descripción |

| Estado | 1 bytes | Estado de la operación [Tabla 9]. Los valores esperados son los siguientes: |

| PN5190_ESTADO_ÉXITO | ||

| PN5190_STATUS_INSTR_ERROR |

4.5.1.1.4 Evento

No hay eventos para este comando.

4.5.1.2 ESCRIBIR_REGISTRO_O_MASCARILLA

Esta instrucción se utiliza para modificar el contenido del registro mediante una operación lógica OR. Se lee el contenido del registro y se realiza una operación lógica OR con la máscara proporcionada. El contenido modificado se vuelve a escribir en el registro.

4.5.1.2.1 condiciones

La dirección del registro debe existir y el registro debe tener el atributo LEER-ESCRIBIR.

4.5.1.2.2 Comando

Tabla 21. Valor del comando WRITE_REGISTER_OR_MASK Realice una operación lógica OR en un registro utilizando la máscara proporcionada.

| Campo de carga útil | Longitud | Valor/descripción |

| Dirección de registro | 1 bytes | Dirección del registro. |

| Mascarilla | 4 bytes | Máscara de bits utilizada como operando para la operación lógica OR. (Little-endian) |

4.5.1.2.3 Respuesta

Tabla 22. Valor de respuesta WRITE_REGISTER_OR_MASK

| Campo de carga útil | Longitud | Valor / Descripción |

| Estado | 1 bytes | Estado de la operación [Tabla 9]. Los valores esperados son los siguientes: |

| PN5190_ESTADO_ÉXITO | ||

| PN5190_STATUS_INSTR_ERROR |

4.5.1.2.4 Evento

No hay eventos para este comando.

4.5.1.3 ESCRIBIR_REGISTRO_Y_MÁSCARA

Esta instrucción se utiliza para modificar el contenido del registro mediante una operación lógica AND. Se lee el contenido del registro y se realiza una operación AND lógica con la máscara proporcionada. El contenido modificado se vuelve a escribir en el registro.

4.5.1.3.1 condiciones

La dirección del registro debe existir y el registro debe tener el atributo LEER-ESCRIBIR.

4.5.1.3.2 Comando

Tabla 23. Valor del comando WRITE_REGISTER_AND_MASK Realice una operación AND lógica en un registro utilizando la máscara proporcionada.

| Campo de carga útil | Longitud | Valor/descripción |

| Dirección de registro | 1 bytes | Dirección del registro. |

| Mascarilla | 4 bytes | Máscara de bits utilizada como operando para la operación lógica AND. (Little-endian) |

4.5.1.3.3 Respuesta

Tabla 24. Valor de respuesta WRITE_REGISTER_AND_MASK

| Campo de carga útil | Longitud | Valor / Descripción |

| Estado | 1 bytes | Estado de la operación [Tabla 9]. Los valores esperados son los siguientes: |

| PN5190_ESTADO_ÉXITO | ||

| PN5190_STATUS_INSTR_ERROR |

4.5.1.3.4 Evento

No hay eventos para este comando.

4.5.1.4 ESCRIBIR_REGISTRO_MÚLTIPLES

La funcionalidad de esta instrucción es similar a la Sección 4.5.1.1, Sección 4.5.1.2, Sección 4.5.1.3, con la posibilidad de combinarlas. De hecho, toma una matriz de conjuntos de valores de tipo de registro y realiza la acción apropiada. El tipo refleja la acción que es escribir registro, operación lógica OR en un registro u operación lógica AND en un registro.

4.5.1.4.1 condiciones

Debe existir la dirección lógica respectiva del registro dentro de un conjunto.

El atributo de acceso al registro debe permitir la ejecución de la acción requerida (tipo):

- Acción de escritura (0x01): atributo LECTURA-ESCRITURA o SÓLO ESCRITURA

- O acción de máscara (0x02): atributo LEER-ESCRIBIR

- Acción de máscara AND (0x03): atributo LEER-ESCRIBIR

El tamaño de la matriz 'Set' debe estar en el rango de 1 a 43, inclusive.

El campo 'Tipo' debe estar en el rango de 1 a 3, inclusive

4.5.1.4.2 Comando

Tabla 25. Valor del comando WRITE_REGISTER_MULTIPLE Realice una operación de escritura de registro utilizando un conjunto de pares Registro-Valor.

| Campo de carga útil | Longitud | Valor/descripción | |||

| Establecer [1…n] | 6 bytes | Dirección de registro | 1 bytes | Dirección lógica del registro. | |

| Tipo | 1 bytes | 0x1 | Escribir registro | ||

| 0x2 | Escribir Registro O Máscara | ||||

| 0x3 | Escribir Registro Y Máscara | ||||

| Valor | 4 bytes | 32 Valor de registro de bits que debe escribirse o máscara de bits utilizada para la operación lógica. (Little-endian) | |||

Nota: En caso de una excepción, la operación no se revierte, es decir, los registros que se han modificado hasta que se produce la excepción permanecen en estado modificado. El host debe tomar las medidas adecuadas para recuperar un estado definido.

4.5.1.4.3 Respuesta

Tabla 26. Valor de respuesta WRITE_REGISTER_MULTIPLE

| Campo de carga útil | Longitud | Valor / Descripción |

| Estado | 1 bytes | Estado de la operación [Tabla 9]. Los valores esperados son los siguientes: |

| PN5190_ESTADO_ÉXITO | ||

| PN5190_STATUS_INSTR_ERROR |

4.5.1.4.4 Evento

No hay eventos para este comando.

4.5.1.5 LEER_REGISTRO

Esta instrucción se utiliza para leer el contenido de un registro lógico. El contenido está presente en la respuesta, como valor de 4 bytes en formato little-endian.

4.5.1.5.1 condiciones

La dirección del registro lógico debe existir. El atributo de acceso del registro debe ser LECTURA-ESCRITURA o SOLO LECTURA.

4.5.1.5.2 Comando

Tabla 27. Valor del comando READ_REGISTER

Leer el contenido de un registro.

| Campo de carga útil | Longitud | Valor / Descripción |

| Dirección de registro | 1 bytes | Dirección del registro lógico |

4.5.1.5.3 Respuesta

Tabla 28. Valor de respuesta READ_REGISTER

| Campo de carga útil | Longitud | Valor / Descripción |

| Estado | 1 bytes | Estado de la operación [Tabla 9]. Los valores esperados son los siguientes: |

| PN5190_STATUS_SUCCESS PN5190_STATUS_INSTR_ERROR (No hay más datos presentes) | ||

| Valor de registro | 4 bytes | Valor de registro de 32 bits que se ha leído. (Little-endian) |

4.5.1.5.4 Evento

No hay eventos para este comando.

4.5.1.6 LEER_REGISTRO_MULTIPLE

Esta instrucción se utiliza para leer varios registros lógicos a la vez. El resultado (contenido de cada registro) se proporciona en la respuesta a la instrucción. La dirección del registro en sí no está incluida en la respuesta. El orden de los contenidos de registro dentro de la respuesta corresponde al orden de las direcciones de registro dentro de la instrucción.

4.5.1.6.1 condiciones

Todas las direcciones de registro dentro de la instrucción deben existir. El atributo de acceso para cada registro debe ser LECTURA-ESCRITURA o SÓLO LECTURA. El tamaño de la matriz 'Dirección de registro' debe estar en el rango de 1 a 18, inclusive.

4.5.1.6.2 Comando

Tabla 29. Valor del comando READ_REGISTER_MULTIPLE Realizar una operación de lectura de registro en un conjunto de registros.

| Campo de carga útil | Longitud | Valor / Descripción |

| Dirección de registro[1…n] | 1 bytes | Dirección de registro |

4.5.1.6.3 Respuesta

Tabla 30. Valor de respuesta READ_REGISTER_MULTIPLE

| Campo de carga útil | Longitud | Valor/descripción | ||

| Estado | 1 bytes | Estado de la operación [Tabla 9]. Los valores esperados son los siguientes: | ||

| PN5190_STATUS_SUCCESS PN5190_STATUS_INSTR_ERROR (No hay más datos presentes) | ||||

| Valor de registro [1…n] | 4 bytes | Valor | 4 bytes | Valor de registro de 32 bits que se ha leído (little-endian). |

4.5.1.6.4 Evento

No hay eventos para este comando.

4.5.2 Manipulación de E2PROM

El área accesible en E2PROM es según el mapa de EEPROM y el tamaño direccionable.

Nota:

1. Siempre que se mencione la 'Dirección E2PROM' en las siguientes instrucciones, se hará referencia al tamaño del área EEPROM direccionable.

4.5.2.1 ESCRIBIR_E2PROM

Esta instrucción se utiliza para escribir uno o más valores en E2PROM. El campo 'Valores' contiene los datos que se escribirán en E2PROM comenzando en la dirección proporcionada por el campo 'Dirección E2PROM'. Los datos se escriben en orden secuencial.

Nota:

Tenga en cuenta que este es un comando de bloqueo, lo que significa que NFC FE está bloqueado durante la operación de escritura. Esto puede tardar varios milisegundos.

4.5.2.1.1 condiciones

El campo 'Dirección E2PROM' debe estar en el rango según [2]. La cantidad de bytes dentro del campo 'Valores' debe estar en el rango de 1 a 1024 (0x0400), inclusive. La operación de escritura no debe ir más allá de la dirección EEPROM como se menciona en [2]. Se enviará una respuesta de error al host si la dirección excede el espacio de direcciones EEPROM como en [2].

4.5.2.1.2 Comando

Tabla 31. Valor del comando WRITE_E2PROM Escribe los valores dados secuencialmente en E2PROM.

| Campo de carga útil | Longitud | Valor/descripción |

| Dirección E2PROM | 2 bytes | Dirección en EEPROM desde la cual se iniciará la operación de escritura. (Little-endian) |

| Valores | 1 – 1024 bytes | Valores que deben escribirse en E2PROM en orden secuencial. |

4.5.2.1.3 Respuesta

Tabla 32. Valor de respuesta WRITE_EEPROM

| Campo de carga útil | Longitud | Valor / Descripción |

| Estado | 1 bytes | Estado de la operación [Tabla 9]. Los valores esperados son los siguientes: |

| PN5190_STATUS_SUCCESS PN5190_STATUS_INSTR_ERROR PN5190_STATUS_MEMORY_ERROR |

4.5.2.1.4 Evento

No hay eventos para este comando.

4.5.2.2 LEER_E2PROM

Esta instrucción se utiliza para leer datos del área de memoria E2PROM. El campo 'Dirección E2PROM' indica la dirección de inicio de la operación de lectura. La respuesta contiene los datos leídos de E2PROM.

4.5.2.2.1 condiciones

El campo 'Dirección E2PROM' debe estar en un rango válido.

El campo 'Número de bytes' debe estar en el rango de 1 a 256, inclusive.

La operación de lectura no debe ir más allá de la última dirección EEPROM accesible.

Se enviará una respuesta de error al host si la dirección excede el espacio de direcciones EEPROM.

4.5.2.2.2 Comando

Tabla 33. Valor del comando READ_E2PROM Lee los valores de E2PROM secuencialmente.

| Campo de carga útil | Longitud | Valor/descripción |

| Dirección E2PROM | 2 bytes | Dirección en E2PROM desde la cual se iniciará la operación de lectura. (Little-endian) |

| Número de bytes | 2 bytes | Número de bytes a leer. (Little-endian) |

4.5.2.2.3 Respuesta

Tabla 34. Valor de respuesta READ_E2PROM

| Campo de carga útil | Longitud | Valor / Descripción |

| Estado | 1 bytes | Estado de la operación [Tabla 9]. Los valores esperados son los siguientes: |

| PN5190_ESTADO_ÉXITO | ||

| PN5190_STATUS_INSTR_ERROR (No hay más datos presentes) | ||

| Valores | 1 – 1024 bytes | Valores que se han leído en orden secuencial. |

4.5.2.2.4 Evento

No hay eventos para este comando.

4.5.2.3 GET_CRC_USER_AREA

Esta instrucción se usa para calcular el CRC para el área de configuración de usuario completa, incluida el área de protocolo de PN5190 IC.

4.5.2.3.1 Comando

Tabla 35. Valor del comando GET_CRC_USER_AREA

Lea el CRC del área de configuración del usuario, incluido el área de protocolo.

| Campo de carga útil | Longitud | Valor / Descripción |

| – | – | No hay datos en la carga útil |

4.5.2.3.2 Respuesta

Tabla 36. Valor de respuesta GET_CRC_USER_AREA

| Campo de carga útil | Longitud | Valor/descripción |

| Estado | 1 bytes | Estado de la operación [Tabla 9]. Los valores esperados son los siguientes: |

| PN5190_ESTADO_ÉXITO | ||

| PN5190_STATUS_INSTR_ERROR (No hay más datos presentes) | ||

| Valores | 4 bytes | 4 bytes de datos CRC en formato little-endian. |

4.5.2.3.3 Evento

No hay eventos para este comando.

4.5.3 Manipulación de datos CLIF

Las instrucciones descritas en esta sección describen los comandos para la transmisión y recepción de RF.

4.5.3.1 INTERCAMBIO_RF_DATOS

La función de intercambio de RF realiza una transmisión de los datos TX y espera la recepción de cualquier dato RX.

La función regresa en caso de que se produzca una recepción (errónea o correcta) o se agote el tiempo de espera. El cronómetro se pone en marcha con el FINAL de TRANSMISIÓN y se detiene con el INICIO de RECEPCIÓN. El valor de tiempo de espera preconfigurado en EEPROM se utilizará en caso de que el tiempo de espera no esté configurado antes de la ejecución del comando Exchange.

Si transceiver_state es

- en IDLE se ingresa al modo TRANSCEPCIÓN.

- En WAIT_RECEIVE, el estado del transceptor se restablece al MODO TRANSCEPCIÓN en caso de que se establezca el bit iniciador.

- En WAIT_TRANSMIT, el estado del transceptor se restablece al MODO TRANSCEPCIÓN en caso de que el bit iniciador NO esté configurado

El campo 'Número de bits válidos en el último byte' indica la longitud exacta de los datos que se transmitirán.

4.5.3.1.1 condiciones

El tamaño del campo 'Datos TX' debe estar en el rango de 0 a 1024, inclusive.

El campo 'Número de bits válidos en el último byte' debe estar en el rango de 0 a 7.

El comando no debe llamarse durante una transmisión de RF en curso. El comando garantizará el estado correcto del transceptor para transmitir los datos.

Nota:

Este comando es válido sólo para el modo Lector y el modo iniciador P2P” Pasivo/Activo.

4.5.3.1.2 Comando

Tabla 37. Valor del comando EXCHANGE_RF_DATA

Escriba datos de TX en el búfer de transmisión de RF interno e inicie la transmisión usando el comando transceptor y espere hasta la recepción o el tiempo de espera para preparar una respuesta al host.

| Campo de carga útil | Longitud | Valor / Descripción | |

| Número de bits válidos en el último byte | 1 bytes | 0 | Todos los bits del último byte se transmiten |

| 1 – 7 | Número de bits del último byte que se transmitirán. | ||

| RFExchangeConfig | 1 bytes | Configuración de la función RFExchange. Detalles ver abajo | |

Tabla 37. Valor del comando EXCHANGE_RF_DATA...continuación

Escriba datos de TX en el búfer de transmisión de RF interno e inicie la transmisión usando el comando transceptor y espere hasta la recepción o el tiempo de espera para preparar una respuesta al host.

| Campo de carga útil | Longitud | Valor / Descripción |

| Datos de transmisión | n bytes | Datos TX que deben enviarse a través de CLIF mediante el comando transceive. norte = 0 – 1024 bytes |

Tabla 38. Máscara de bits RFexchangeConfig

| b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 | Descripción |

| Los bits 4 – 7 son RFU | ||||||||

| X | Incluya datos RX en respuesta según RX_STATUS, si el bit está establecido en 1b. | |||||||

| X | Incluya el registro EVENT_STATUS en respuesta, si el bit está establecido en 1b. | |||||||

| X | Incluya el registro RX_STATUS_ERROR en respuesta, si el bit está establecido en 1b. | |||||||

| X | Incluya el registro RX_STATUS en respuesta, si el bit está establecido en 1b. |

4.5.3.1.3 Respuesta

Tabla 39. Valor de respuesta EXCHANGE_RF_DATA

| Campo de carga útil | Longitud | Valor / Descripción |

| Estado | 1 bytes | Estado de la operación [Tabla 9]. Los valores esperados son los siguientes: |

| PN5190_STATUS_INSTR_SUCCESS PN5190_STATUS_INSTR_ERROR (No hay más datos presentes) PN5190_STATUS_TIMEOUT PN5190_STATUS_RX_TIMEOUT PN5190_STATUS_NO_RF_FIELD PN5190_STATUS_TIMEOUT_WITH_EMD_ERROR |

||

| RX_ESTADO | 4 bytes | Si se solicita RX_STATUS (little-endian) |

| RX_STATUS_ERROR | 4 bytes | Si se solicita RX_STATUS_ERROR (little-endian) |

| EVENTO_ESTADO | 4 bytes | Si se solicita EVENT_STATUS (little-endian) |

| Datos RX | 1 – 1024 bytes | Si se solicitan datos RX. Datos RX recibidos durante la fase de recepción de RF del intercambio de RF. |

4.5.3.1.4 Evento

No hay eventos para este comando.

4.5.3.2 TRANSMITIR_RF_DATOS

Esta instrucción se utiliza para escribir datos en el búfer de transmisión CLIF interno e iniciar la transmisión utilizando el comando transceive internamente. El tamaño de este búfer está limitado a 1024 bytes. Después de ejecutar esta instrucción, se inicia automáticamente una recepción de RF.

El comando regresa inmediatamente después de que se completa la transmisión, sin esperar a que se complete la recepción.

4.5.3.2.1 condiciones

La cantidad de bytes dentro del campo 'Datos TX' debe estar en el rango de 1 a 1024, inclusive.

El comando no debe llamarse durante una transmisión de RF en curso.

4.5.3.2.2 Comando

Tabla 40. Valor del comando TRANSMIT_RF_DATA Escribe datos de TX en el búfer de transmisión CLIF interno.

| Campo de carga útil | Longitud | Valor / Descripción |

| Número de bits válidos en el último byte | 1 bytes | 0 Se transmiten todos los bits del último byte. 1 – 7 Número de bits del último byte que se transmitirán. |

| RFU | 1 bytes | Reservado |

| Datos de transmisión | 1 – 1024 bytes | Datos de TX que se utilizarán durante la próxima transmisión de RF. |

4.5.3.2.3 Respuesta

Tabla 41. Valor de respuesta TRANSMIT_RF_DATA

| Campo de carga útil | Longitud | Valor / Descripción |

| Estado | 1 bytes | Estado de la operación [Tabla 9]. Los valores esperados son los siguientes: |

| PN5190_STATUS_INSTR_SUCCESS PN5190_STATUS_INSTR_ERROR PN5190_STATUS_NO_RF_FIELD PN5190_STATUS_NO_EXTERNAL_RF_FIELD |

4.5.3.2.4 Evento

No hay eventos para este comando.

4.5.3.3 RECUPERAR_DATOS_RF

Esta instrucción se usa para leer datos del búfer CLIF RX interno, que contiene los datos de respuesta de RF (si los hay) enviados desde la ejecución anterior de la Sección 4.5.3.1 con la opción de no incluir los datos recibidos en la respuesta o la Sección 4.5.3.2 .XNUMX mando.

4.5.3.3.1 Comando

Tabla 42. Valor del comando RETRIEVE_RF_DATA Leer datos RX del búfer de recepción de RF interno.

| Campo de carga útil | Longitud | Valor / Descripción |

| Vacío | Vacío | Vacío |

4.5.3.3.2 Respuesta

Tabla 43. Valor de respuesta RETRIEVE_RF_DATA

| Campo de carga útil | Longitud | Valor / Descripción |

| Estado | 1 bytes | Estado de la operación [Tabla 9]. Los valores esperados son los siguientes: |

| Campo de carga útil | Longitud | Valor / Descripción |

| PN5190_STATUS_INSTR_SUCCESS PN5190_STATUS_INSTR_ERROR (No hay más datos presentes) |

||

| Datos RX | 1 – 1024 bytes | Datos de RX que se han recibido durante la última recepción de RF satisfactoria. |

4.5.3.3.3 Evento

No hay eventos para este comando.

4.5.3.4 RECIBIR_DATOS_RF

Esta instrucción espera los datos recibidos a través de la interfaz RF del lector.

En el modo lector, esta instrucción regresa si hay una recepción (ya sea incorrecta o correcta) o si se agotó el tiempo de espera del FWT. El temporizador se inicia con el FIN de TRANSMISIÓN y se detiene con el INICIO de RECEPCIÓN. El valor de tiempo de espera predeterminado preconfigurado en EEPROM se utilizará en caso de que el tiempo de espera no esté configurado antes de la ejecución del comando Exchange.

En el modo objetivo, esta instrucción regresa en caso de recepción (errónea o correcta) o error de RF externo.

Nota:

Esta instrucción se utilizará con el comando TRANSMIT_RF_DATA para realizar operaciones TX y RX...

4.5.3.4.1 Comando

Tabla 44. Valor del comando RECEIVE_RF_DATA

| Campo de carga útil | Longitud | Valor / Descripción |

| Recibir RFConfig | 1 bytes | Configuración de la función ReceiverRFConfig. Ver Tabla 45 |

Tabla 45. Máscara de bits de ReceiverRFConfig

| b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 | Descripción |

| Los bits 4 – 7 son RFU | ||||||||

| X | Incluya datos RX en respuesta según RX_STATUS, si el bit está establecido en 1b. | |||||||

| X | Incluya el registro EVENT_STATUS en respuesta, si el bit está establecido en 1b. | |||||||

| X | Incluya el registro RX_STATUS_ERROR en respuesta, si el bit está establecido en 1b. | |||||||

| X | Incluya el registro RX_STATUS en respuesta, si el bit está establecido en 1b. |

4.5.3.4.2 Respuesta

Tabla 46. Valor de respuesta RECEIVE_RF_DATA

| Campo de carga útil | Longitud | Valor/descripción |

| Estado | 1 bytes | Estado de la operación [Tabla 9]. Los valores esperados son los siguientes: |

| PN5190_STATUS_INSTR_SUCCESS PN5190_STATUS_INSTR_ERROR (No hay más datos presentes) PN5190_STATUS_TIMEOUT |

| Campo de carga útil | Longitud | Valor/descripción |

| PN5190_STATUS_NO_RF_FIELD PN5190_STATUS_NO_EXTERNAL_RF_FIELD |

||

| RX_ESTADO | 4 bytes | Si se solicita RX_STATUS (little-endian) |

| RX_STATUS_ERROR | 4 bytes | Si se solicita RX_STATUS_ERROR (little-endian) |

| EVENTO_ESTADO | 4 bytes | Si se solicita EVENT_STATUS (little-endian) |

| Datos RX | 1 – 1024 bytes | Si se solicitan datos RX. Datos RX recibidos por RF. |

4.5.3.4.3 Evento

No hay eventos para este comando.

4.5.3.5 RETRIEVE_RF_FELICA_EMD_DATA (Configuración FeliCa EMD)

Esta instrucción se utiliza para leer datos del búfer CLIF RX interno, que contiene datos de respuesta de FeliCa EMD (si los hay) publicados desde la ejecución anterior del comando EXCHANGE_RF_DATA que regresa con el estado 'PN5190_STATUS_TIMEOUT_WITH_EMD_ERROR'.

Nota: Este comando está disponible desde PN5190 FW v02.03 en adelante.

4.5.3.5.1 Comando

Leer datos RX del búfer de recepción de RF interno.

Tabla 47. Valor del comando RETRIEVE_RF_FELICA_EMD_DATA

| Campo de carga útil | Longitud | Valor / Descripción | |

| FeliCaRFRetrieveConfig | 1 bytes | 00 – FF | Configuración de la función RETRIEVE_RF_FELICA_EMD_DATA |

| descripción de la configuración (máscara de bits) | bits 7..2: RFU bit 1: incluye el registro RX_STATUS_ ERROR en respuesta, si el bit se establece en 1b. bit 0: incluye el registro RX_STATUS en respuesta, si el bit se establece en 1b. |

||

4.5.3.5.2 Respuesta

Tabla 48. Valor de respuesta RETRIEVE_RF_FELICA_EMD_DATA

| Campo de carga útil | Longitud | Valor/descripción | |||

| Estado | 1 bytes | Estado de la operación. Los valores esperados son los siguientes: PN5190_STATUS_INSTR_SUCCESS PN5190_STATUS_INSTR_ERROR (No hay más datos presentes) | |||

| RX_ESTADO | 4 bytes | Si se solicita RX_STATUS (little-endian) | |||

| RX_STATUS_ERROR | 4 bytes | Si se solicita RX_STATUS_ERROR (little-endian) | |||

| Campo de carga útil | Longitud | Valor/descripción | |||

| Datos RX | 1…1024 bytes | Datos de FeliCa EMD RX que se recibieron durante la última recepción de RF fallida usando Exchange Command. | |||

4.5.3.5.3 Evento

No hay eventos para este comando.

4.5.4 Cambio del modo de operación

PN5190 admite 4 modos de operación diferentes:

4.5.4.1 Normal

Este es el modo predeterminado, donde se permiten todas las instrucciones.

4.5.4.2 En espera

PN5190 está en estado de espera/suspensión para ahorrar energía. Se deben configurar las condiciones de activación para definir cuándo salir nuevamente del modo de espera.

4.5.4.3 LPCD

PN5190 está en modo de detección de tarjeta de bajo consumo, donde intenta detectar una tarjeta que está ingresando al volumen operativo, con el menor consumo de energía posible.

4.5.4.4 Recopilación automática

PN5190 actúa como escucha de RF y realiza la activación del modo objetivo de forma autónoma (para garantizar restricciones en tiempo real)

4.5.4.5 CAMBIAR_MODO_NORMAL

El comando Cambiar modo normal tiene tres casos de uso.

4.5.4.5.1 Caso de uso 1: Ingrese al modo de operación normal al encender (POR)

Úselo para restablecer al estado inactivo para recibir/procesar el siguiente comando ingresando al modo de operación normal.

4.5.4.5.2 Caso de uso 2: Terminar el comando que ya se está ejecutando para cambiar al modo de operación normal (comando de cancelación)

Úselo para restablecer el estado inactivo para recibir/procesar el siguiente comando finalizando los comandos que ya se están ejecutando.

Comandos como standby, LPCD, Exchange, PRBS y Autocoll podrán finalizarse utilizando este comando.

Este es el único comando especial que no tiene respuesta. En cambio, tiene una notificación de EVENTO.

Consulte la Sección 4.4.3 para obtener más información sobre el tipo de eventos que ocurren durante la ejecución de diferentes comandos subyacentes.

4.5.4.5.2.1 Caso de uso 2.1:

Este comando restablecerá todos los registros CLIF TX, RX y de control de campo al estado de inicio. Al emitir este comando, se apagará cualquier campo de RF existente.

4.5.4.5.2.2 Caso de uso 2.2:

Disponible desde PN5190 FW v02.03 en adelante:

Este comando no modificará CLIF TX, RX y los registros de control de campo, sino que solo moverá el transceptor al estado IDLE.

4.5.4.5.3 Caso de uso 3: Modo de operación normal al realizar un reinicio por software/salir del modo de espera, LPCD En este caso, el PN5190 ingresa directamente al modo de operación normal, enviando IDLE_EVENT al host (Figura 12 o Figura 13) y “ El bit IDLE_EVENT” se establece en la Tabla 11.

No es necesario enviar el comando SWITCH_MODE_NORMAL.

Nota:

Después de que el IC cambia al modo normal, todas las configuraciones de RF se modifican al estado predeterminado. Es imperativo que la configuración de RF respectiva y otros registros relacionados se carguen con los valores apropiados antes de realizar una operación de encendido de RF o intercambio de RF.

4.5.4.5.4 Trama de comando para enviar para diferentes casos de uso

4.5.4.5.4.1 UseCase1: el comando ingresa al modo de operación normal al encender (POR) 0x20 0x01 0x00

4.5.4.5.4.2 Caso de uso 2: Comando para finalizar comandos que ya se están ejecutando para cambiar al modo de operación normal

Caso de uso 2.1:

0x20 0x00 0x00

Caso de uso 2.2: (Desde FW v02.02 en adelante):

0x20 0x02 0x00

4.5.4.5.4.3 Caso de uso 3: Comando para el modo de funcionamiento normal al realizar un reinicio por software/salir del modo de espera, LPCD, ULPCD

Ninguno. PN5190 ingresa directamente al modo de operación normal.

4.5.4.5.5 Respuesta

Ninguno

4.5.4.5.6 Evento

Se establece un BOOT_EVENT (en el registro EVENT_STATUS) que indica que se ingresa al modo normal y se envía al host. Consulte la Figura 12 y la Figura 13 para ver los datos del evento.

Se establece un IDLE_EVENT (en el registro EVENT_STATUS) que indica que se ingresa al modo normal y se envía al host. Consulte la Figura 12 y la Figura 13 para ver los datos del evento.

Se establece un BOOT_EVENT (en el registro EVENT_STATUS) que indica que se ingresa al modo normal y se envía al host. Consulte la Figura 12 y la Figura 13 para ver los datos del evento.

4.5.4.6 SWITCH_MODE_AUTOCOLL

El Switch Mode Autocoll realiza automáticamente el procedimiento de activación de la tarjeta en modo objetivo.

El campo 'Modo de recopilación automática' debe estar en el rango de 0 a 2, inclusive.

En caso de que el campo 'Modo Autocoll' esté configurado en 2 (Autocoll): el campo 'Tecnologías RF' (Tabla 50) debe contener una máscara de bits que indique las tecnologías RF que se admitirán durante Autocoll.

No se deben enviar instrucciones mientras se esté en este modo.

La terminación se indica mediante una interrupción.

4.5.4.6.1 Comando

Tabla 49. Valor del comando SWITCH_MODE_AUTOCOLL

| Parámetro | Longitud | Valor / Descripción | |

| Tecnologías de RF | 1 bytes | Máscara de bits que indica la tecnología de RF para escuchar durante Autocoll. | |

| Modo de búsqueda automática | 1 bytes | 0 | Sin modo autónomo, es decir, Autocoll finaliza cuando el campo de RF externo no está presente. |

| Terminación en caso de | |||

| • NO HAY CAMPO DE RF o CAMPO DE RF ha desaparecido | |||

| • PN5190 está ACTIVADO en modo OBJETIVO | |||

| 1 | Modo autónomo con standby. Cuando no hay ningún campo RF presente, Autocoll ingresa automáticamente al modo de espera. Una vez que se detecta el campo RF externo, PN5190 ingresa nuevamente al modo Autocoll. | ||

| Terminación en caso de | |||

| • PN5190 está ACTIVADO en modo OBJETIVO | |||

| Desde PN5190 FW v02.03 en adelante: Si el campo EEPROM “bCard ModeUltraLowPowerEnabled” en la dirección '0xCDF' está configurado en '1', entonces PN5190 ingresa al modo de espera de energía ultrabaja. | |||

| 2 | Modo autónomo sin espera. Cuando no hay ningún campo de RF presente, PN5190 espera hasta que esté presente el campo de RF antes de iniciar el algoritmo Autocoll. En este caso no se utiliza el modo de espera. | ||

| Terminación en caso de • PN5190 está ACTIVADO en modo OBJETIVO |

|||

Tabla 50. Máscara de bits de tecnologías RF

| b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 | Descripción |

| 0 | 0 | 0 | 0 | RFU | ||||

| X | Si se establece en 1b, se habilita la escucha de NFC-F Active. (No disponible). | |||||||

| X | Si se configura en 1b, se habilita la escucha de NFC-A Active. (No disponible). | |||||||

| X | Si se establece en 1b, se habilita la escucha de NFC-F. | |||||||

| X | Si se establece en 1b, se habilita la escucha de NFC-A. |

4.5.4.6.2 Respuesta

La respuesta solo indica que el comando ha sido procesado.

Tabla 51. Valor de respuesta SWITCH_MODE_AUTOCOLL

| Campo de carga útil | Longitud | Valor / Descripción |

| Estado | 1 bytes | Estado de la operación [Tabla 9]. Los valores esperados son los siguientes: |

| PN5190_STATUS_INSTR_SUCCESS PN5190_STATUS_INSTR_ERROR (no se ingresó al modo de cambio debido a una configuración incorrecta) |

4.5.4.6.3 Evento

La notificación del evento se envía cuando finaliza el comando y se ingresa al modo normal. El host leerá los bytes de respuesta en función del valor del evento.

Nota:

Cuando el estado no es "PN5190_STATUS_INSTR_SUCCESS", no están presentes más bytes de datos de "Protocolo" y "Card_Activated".

La información tecnológica se recupera de los registros utilizando los comandos de la Sección 4.5.1.5, Sección 4.5.1.6.

La siguiente tabla muestra los datos del evento que se envían como parte del mensaje de evento Figura 12 y Figura 13.

Tabla 52. EVENT_SWITCH_MODE_AUTOCOLL – Datos de AUTOCOLL_EVENT Modo de operación del interruptor Evento de Autocoll

| Campo de carga útil | Longitud | Valor / Descripción | |

| Estado | 1 byte | Estado de la operación | |

| PN5190_STATUS_INSTR_SUCCESS | PN5190 está ACTIVADO en modo OBJETIVO. Otros datos en este caso son válidos. |

||