UM11942

UM11942

Capa d'instruccions PN5190

Controlador frontal NFC

Manual d'usuari

Controlador frontal NFC PN5190

Informació del document

| Informació | Contingut |

| Paraules clau | PN5190, NFC, frontend NFC, controlador, capa d'instruccions |

| Resum | Aquest document descriu les ordres i les respostes de la capa d'instruccions per treballar des d'un controlador amfitrió, per avaluar el funcionament del controlador frontal NFC NXP PN5190. PN5190 és un controlador frontal NFC de nova generació. L'abast d'aquest document és descriure les ordres d'interfície per treballar amb el controlador de frontend NFC PN5190. Per obtenir més informació sobre el funcionament del controlador frontal NFC PN5190, consulteu la fitxa tècnica i la seva informació complementària. |

Historial de revisions

| Rev | Data | Descripció |

| 3.7 | 20230525 | • El tipus de document i el títol s'han canviat de l'annex a la fitxa del producte al manual d'usuari • Neteja editorial • Termes editorials actualitzats per a senyals SPI • S'ha afegit l'ordre GET_CRC_USER_AREA a la Taula 8 de la Secció 4.5.2.3 • S'han actualitzat diversos detalls diferenciats per a PN5190B1 i PN5190B2 a la secció 3.4.1 • Resposta actualitzada de l'apartat 3.4.7 |

| 3.6 | 20230111 | Descripció de la resposta de verificació d'integritat millorada a la secció 3.4.7 |

| 3.5 | 20221104 | Secció 4.5.4.6.3 “Esdeveniment”: afegit |

| 3.4 | 20220701 | • S'ha afegit l'ordre CONFIGURE_MULTIPLE_TESTBUS_DIGITAL a la Taula 8 de la Secció 4.5.9.3 • Secció actualitzada 4.5.9.2.2 |

| 3.3 | 20220329 | La descripció del maquinari s'ha millorat a la secció 4.5.12.2.1 "Ordre" i a la secció 4.5.12.2.2 "Resposta" |

| 3.2 | 20210910 | Números de versió del firmware actualitzats de la 2.1 a la 2.01 i de la 2.3 a la 2.03 |

| 3.1 | 20210527 | S'ha afegit la descripció de l'ordre RETRIEVE_RF_FELICA_EMD_DATA |

| 3 | 20210118 | Primera versió oficial publicada |

Introducció

1.1 Introducció

Aquest document descriu la interfície d'amfitrió PN5190 i les API. La interfície d'amfitrió física utilitzada a la documentació és SPI. La característica física de l'SPI no es considera al document.

La separació de trames i el control de flux formen part d'aquest document.

1.1.1 Àmbit

El document descriu la capa lògica, el codi d'instruccions i les API que són rellevants per al client.

S'ha acabat la comunicació amb l'amfitrióview

El PN5190 té dos modes principals de funcionament per comunicar-se amb el controlador amfitrió.

- La comunicació basada en HDLL s'utilitza quan el dispositiu s'activa per introduir:

a. Mode de descàrrega segura xifrada per actualitzar el seu microprogramari - Comunicació basada en la resposta d'ordres TLV (donada com a example).

Mode HDLL 2.1

El mode HDLL s'utilitza perquè el format d'intercanvi de paquets funcioni amb els modes de funcionament d'IC següents:

- Mode de descàrrega de microprogramari segur (SFWU), vegeu la secció 3

2.1.1 Descripció de HDLL

HDLL és la capa d'enllaç desenvolupada per NXP per garantir una descàrrega de FW fiable.

Un missatge HDLL està format per una capçalera de 2 bytes, seguida d'una trama, que inclou el codi operatiu i la càrrega útil de l'ordre. Cada missatge acaba amb un CRC de 16 bits, tal com es descriu a la imatge següent: La capçalera HDLL conté:

La capçalera HDLL conté:

- Un trosset. Que indica si aquest missatge és l'únic o l'últim fragment d'un missatge (frag = 0). O si, almenys, segueix un altre tros (tros = 1).

- La longitud de la càrrega útil codificada en 10 bits. Per tant, la càrrega útil del marc HDLL pot arribar a 1023 bytes.

L'ordre dels bytes s'ha definit com a big-endian, és a dir, Ms Byte primer.

El CRC16 compleix l'estàndard X.25 (CRC-CCITT, ISO/IEC13239) amb el polinomi x^16 + x^12 + x^5 +1 i el valor de precàrrega 0xFFFF.

Es calcula sobre tot el marc HDLL, és a dir, Capçalera + Marc.

Sampimplementació del codi C:

static uint16_t phHal_Host_CalcCrc16(uint8_t* p, uint32_t dwLength)

{

uint32_t i ;

uint16_t crc_new ;

uint16_t crc = 0xffffU;

per (I = 0; i <dwLength; i++)

{

crc_new = (uint8_t)(crc >> 8) | (crc << 8);

crc_new ^= p[i];

crc_new ^= (uint8_t)(crc_new & 0xff) >> 4;

crc_new ^= crc_new << 12;

crc_new ^= (crc_new & 0xff) << 5;

crc = crc_new;

}

retornar crc;

}

2.1.2 Cartografia de transport sobre l'SPI

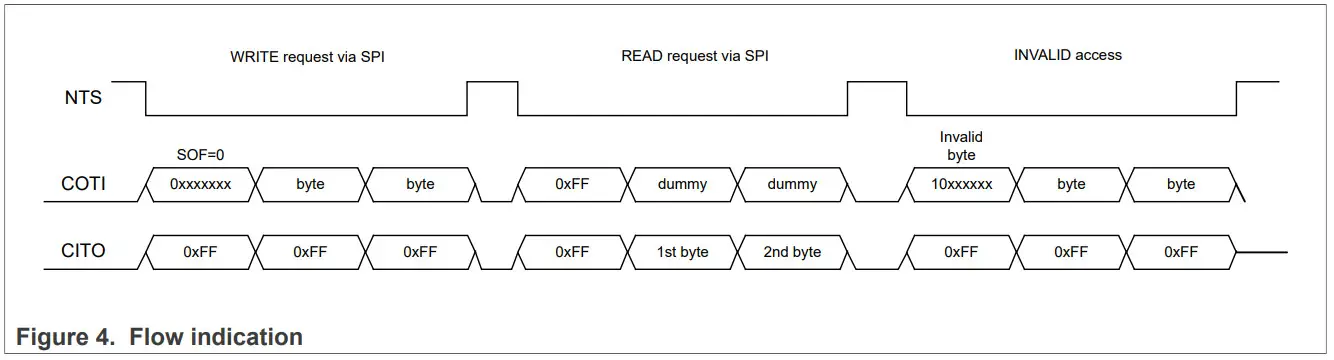

Per a cada afirmació NTS, el primer byte és sempre un HEADER (byte d'indicació de flux), pot ser 0x7F/0xFF pel que fa a l'operació d'escriptura/lectura.

2.1.2.1 Seqüència d'escriptura des de l'amfitrió (direcció DH => PN5190) 2.1.2.2 Seqüència de lectura des de l'amfitrió (Direcció PN5190 => DH)

2.1.2.2 Seqüència de lectura des de l'amfitrió (Direcció PN5190 => DH) 2.1.3 Protocol HDLL

2.1.3 Protocol HDLL

HDLL és un protocol de resposta d'ordres. Totes les operacions esmentades anteriorment es desencadenen mitjançant una comanda específica i es validen en funció de la resposta.

Les ordres i les respostes segueixen la sintaxi dels missatges HDLL, l'ordre l'envia l'amfitrió del dispositiu i la resposta el PN5190. El codi operatiu indica l'ordre i el tipus de resposta.

Comunicacions basades en HDLL, només s'utilitzen quan el PN5190 s'activa per entrar en el mode de "Descàrrega segura del firmware".

2.2 Mode TLV

TLV significa Tag Valor de longitud.

2.2.1 Definició del marc

Un marc SPI comença amb la vora descendent de NTS i acaba amb la vora ascendent de NTS. SPI és dúplex complet per definició física, però PN5190 utilitza SPI en mode semidúplex. El mode SPI està limitat a CPOL 0 i CPHA 0 amb una velocitat de rellotge màxima tal com s'especifica a [2]. Cada trama SPI es compon d'una capçalera d'1 byte i n-bytes de cos.

2.2.2 Indicació de cabal L'HOST sempre envia com a primer byte el byte d'indicació de flux, tant si vol escriure com llegir dades del PN5190.

L'HOST sempre envia com a primer byte el byte d'indicació de flux, tant si vol escriure com llegir dades del PN5190.

Si hi ha una sol·licitud de lectura i no hi ha dades disponibles, la resposta conté 0xFF.

Les dades després del byte d'indicació de flux són un o diversos missatges.

Per a cada afirmació NTS, el primer byte és sempre un HEADER (byte d'indicació de flux), pot ser 0x7F/0xFF pel que fa a l'operació d'escriptura/lectura.

2.2.3 Tipus de missatge

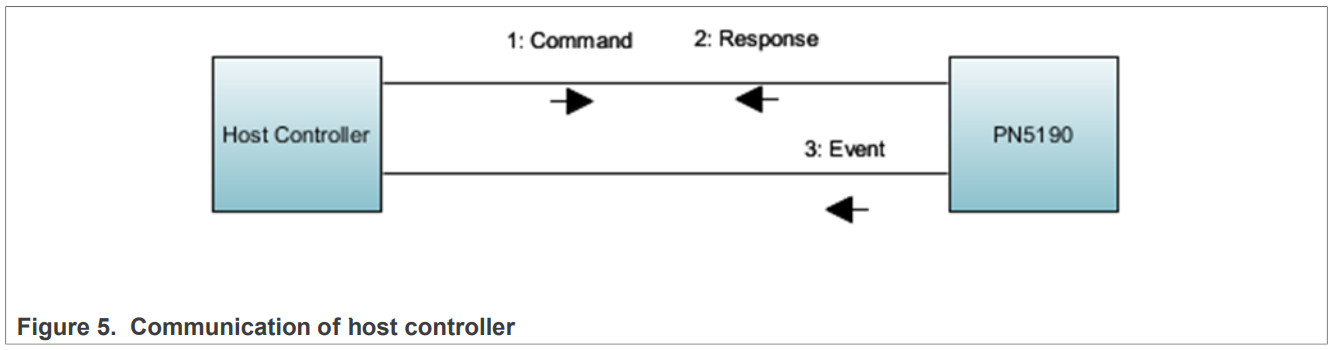

Un controlador amfitrió s'ha de comunicar amb PN5190 mitjançant missatges que es transporten dins de trames SPI.

Hi ha tres tipus de missatges diferents:

- Comandament

- Resposta

- Esdeveniment

El diagrama de comunicació anterior mostra les indicacions permeses per als diferents tipus de missatges de la següent manera:

El diagrama de comunicació anterior mostra les indicacions permeses per als diferents tipus de missatges de la següent manera:

- Comandament i resposta.

- Les ordres només s'envien des del controlador amfitrió a PN5190.

- Les respostes i els esdeveniments només s'envien des del PN5190 al controlador amfitrió.

- Les respostes d'ordres es sincronitzen mitjançant el pin IRQ.

- L'amfitrió només pot enviar les ordres quan l'IRQ és baix.

- L'amfitrió només pot llegir la resposta/esdeveniment quan l'IRQ és alt.

2.2.3.1 Seqüències i regles permeses Seqüències permeses d'ordres, resposta i esdeveniments

Seqüències permeses d'ordres, resposta i esdeveniments

- Una ordre sempre es reconeix mitjançant una resposta, un esdeveniment o ambdós.

- El controlador de l'amfitrió no té permís per enviar una altra ordre abans de no haver rebut una resposta a l'ordre anterior.

- Els esdeveniments es poden enviar de manera asíncrona en qualsevol moment (NO entrellaçats dins d'un parell d'ordres/resposta).

- Els missatges EVENT mai es combinen amb els missatges RESPOSTA dins d'un marc.

Nota: La disponibilitat d'un missatge (ja sigui RESPOSTA o ESDEVENIMENT) es senyalitza amb l'IRQ en alt, des de baix. L'IRQ es manté alt fins que es llegeix tota la resposta o el marc d'esdeveniment. Només després que el senyal IRQ sigui baix, l'amfitrió pot enviar la següent ordre.

2.2.4 Format del missatge

Cada missatge està codificat en una estructura TLV amb n bytes de càrrega útil per a cada missatge, excepte per a l'ordre SWITCH_MODE_NORMAL. Cada TLV està format per:

Cada TLV està format per: Tipus (T) => 1 byte

Tipus (T) => 1 byte

Bit[7] Tipus de missatge

0: Missatge d'ORDA o RESPOSTA

1: Missatge d'ESDEVENIMENT

Bit[6:0]: codi d'instrucció

Longitud (L) => 2 bytes (hauria d'estar en format big-endian)

Valor (V) => N bytes de valor/dades del TLV (paràmetres de comandament/dades de resposta) basat en el camp Longitud (format big-endian)

2.2.4.1 Dividir el marc

El missatge COMMAND s'ha d'enviar en un marc SPI.

Els missatges RESPOSTA i ESDEVENIMENT es poden llegir en múltiples trames SPI, per exemple, per llegir el byte de longitud. Els missatges de RESPOSTA o d'ESDEVENIMENT es poden llegir en una sola trama SPI, però es poden retardar per NO-CLOCK entremig, per exemple, per llegir el byte de longitud.

Els missatges de RESPOSTA o d'ESDEVENIMENT es poden llegir en una sola trama SPI, però es poden retardar per NO-CLOCK entremig, per exemple, per llegir el byte de longitud.

Mode d'arrencada operatiu IC: mode de descàrrega de FW assegurat

3.1 Introducció

Una part del codi del microprogramari PN5190 s'emmagatzema permanentment a la ROM, mentre que la resta del codi i les dades s'emmagatzemen al flash incrustat. Les dades de l'usuari s'emmagatzemen en flash i estan protegides per mecanismes anti-esquinçament que garanteixen la integritat i la disponibilitat de les dades. Per tal de proporcionar als clients de NXP funcions que compleixin els estàndards més recents (EMVCo, NFC Forum, etc.), es poden actualitzar tant el codi com les dades d'usuari a FLASH.

L'autenticitat i la integritat del microprogramari xifrat estan protegides per la signatura de clau asimètrica/simètrica i el mecanisme hash encadenat invers. La primera ordre DL_SEC_WRITE conté el hash de la segona ordre i està protegida per una signatura RSA a la càrrega útil de la primera trama. El microprogramari PN5190 utilitza la clau pública RSA per autenticar la primera ordre. El hash encadenat de cada comanda s'utilitza per autenticar l'ordre posterior, per assegurar-se que tercers no accedeixen al codi del microprogramari i a les dades.

Les càrregues útils de les ordres DL_SEC_WRITE es xifren amb una clau AES-128. Després de l'autenticació de cada comanda, el contingut de la càrrega útil es desxifra i s'escriu al flash pel microprogramari PN5190.

Per al microprogramari NXP, NXP s'encarrega de lliurar noves actualitzacions de microprogramari segures, juntament amb noves dades d'usuari.

El procediment d'actualització està equipat amb un mecanisme per protegir l'autenticitat, la integritat i la confidencialitat del codi i les dades NXP.

L'esquema de paquets de trama basat en HDLL s'utilitza per a totes les ordres i respostes per al mode d'actualització de microprogramari segur.

La secció 2.1 proporciona el finalview de l'esquema de paquets de trama HDLL utilitzat.

Els circuits integrats PN5190 admeten tant el protocol de descàrrega segura de FW xifrat heretat com el protocol de descàrrega segura de FW xifrat assistit per maquinari en funció de la variant utilitzada.

Els dos tipus són:

- Protocol de descàrrega de FW segur heretat que només funciona amb la versió PN5190 B0/B1 IC.

- Protocol de descàrrega segura de FW amb criptografia de maquinari que només funciona amb la versió PN5190B2 IC, que utilitza els blocs de criptografia de maquinari integrats en el xip

Les seccions següents expliquen les ordres i les respostes del mode de descàrrega de microprogramari segur.

3.2 Com activar el mode "Descàrrega segura del firmware".

El diagrama següent i els passos posteriors mostren com activar el mode de descàrrega de microprogramari segur. Condició prèvia: PN5190 està en estat de funcionament.

Condició prèvia: PN5190 està en estat de funcionament.

Escenari principal:

- Condició d'entrada on s'utilitza el pin DWL_REQ per entrar en el mode "Descàrrega de microprogramari segura".

a. L'amfitrió del dispositiu treu el pin DWL_REQ alt (vàlid només si l'actualització del microprogramari és segura mitjançant el pin DWL_REQ) O

b. L'amfitrió del dispositiu realitza un restabliment dur per arrencar el PN5190 - Condició d'entrada en què el pin DWL_REQ no s'utilitza per entrar al mode "Descàrrega segura del firmware" (descàrrega sense pin).

a. L'amfitrió del dispositiu realitza un restabliment dur per arrencar el PN5190

b. L'amfitrió del dispositiu envia SWITCH_MODE_NORMAL (Secció 4.5.4.5) per entrar al mode d'aplicació normal.

c. Ara, quan l'IC està en mode d'aplicació normal, l'amfitrió del dispositiu envia SWITCH_MODE_DOWNLOAD (Secció 4.5.4.9) per entrar al mode de descàrrega segur. - L'amfitrió del dispositiu envia l'ordre DL_GET_VERSION (Secció 3.4.4) o DL_GET_DIE_ID (Secció 3.4.6) o DL_GET_SESSION_STATE (Secció 3.4.5).

- L'amfitrió del dispositiu llegeix la versió actual de maquinari i microprogramari, sessió, Die-id del dispositiu.

a. L'amfitrió del dispositiu comprova l'estat de la sessió si es va completar l'última descàrrega

b. L'amfitrió del dispositiu aplica les regles de comprovació de la versió per decidir si s'inicia la descàrrega o si surt de la descàrrega. - L'amfitrió del dispositiu es carrega des de a file el codi binari del firmware que s'ha de descarregar

- L'amfitrió del dispositiu proporciona una primera ordre DL_SEC_WRITE (Secció 3.4.8) que conté:

a. La versió del nou firmware,

b. Un noce de 16 bytes de valors arbitraris utilitzats per a l'ofuscament de claus de xifratge

c. Un valor de resum del fotograma següent,

d. La signatura digital del propi marc - L'amfitrió del dispositiu carrega la seqüència de protocol de descàrrega segura al PN5190 amb ordres DL_SEC_WRITE (Secció 3.4.8)

- Quan s'ha enviat l'última ordre DL_SEC_WRITE (Secció 3.4.8), l'amfitrió del dispositiu executa l'ordre DL_CHECK_INTEGRITY (Secció 3.4.7) per comprovar si les memòries s'han escrit correctament.

- L'amfitrió del dispositiu llegeix la nova versió del microprogramari i comprova l'estat de la sessió si està tancat per informar-ne a la capa superior

- L'amfitrió del dispositiu fa baixar el pin DWL_REQ (si s'utilitza el pin DWL_REQ per entrar al mode de descàrrega)

- L'amfitrió del dispositiu realitza un restabliment dur (canviant el pin VEN) al dispositiu per reiniciar el PN5190

Condició posterior: el firmware està actualitzat; s'informa del nou número de versió del firmware.

3.3 Signatura de firmware i control de versions

En el mode de descàrrega del microprogramari PN5190, un mecanisme garanteix que només s'acceptarà un microprogramari signat i lliurat per NXP per al microprogramari NXP.

El següent només s'aplica al microprogramari NXP segur xifrat.

Durant una sessió de descàrrega, s'envia una nova versió de microprogramari de 16 bits. Està compost per un nombre major i un nombre menor:

- Número principal: 8 bits (MSB)

- Número menor: 8 bits (LSB)

El PN5190 comprova si el número de versió principal nou és més gran o igual a l'actual. Si no, la descàrrega segura del microprogramari es rebutja i la sessió es manté tancada.

3.4 Ordres HDLL per a la descàrrega xifrada heretada i la criptografia de maquinari assistida descàrrega xifrada

Aquesta secció proporciona la informació sobre les ordres i les respostes que es van utilitzar per als dos tipus de descàrregues per a la descàrrega del microprogramari NXP.

3.4.1 Codis OP d'ordres HDLL

Nota: Els marcs d'ordres HDLL estan alineats de 4 bytes. Els bytes de càrrega útil no utilitzats queden nuls.

Taula 1. Llista de codis OP d'ordres HDLL

| PN5190 B0/ B1 (Descàrrega heretada) |

PN5190 B2 (Descàrrega assistida per criptografia) |

Àlies de comandament | Descripció |

| 0xF0 | 0xE5 | DL_RESET | Realitza un reinici suau |

| 0xF1 | 0xE1 | DL_GET_VERSION | Retorna els números de versió |

| 0xF2 | 0xDB | DL_GET_SESSION_STATE | Retorna l'estat de la sessió actual |

| 0xF4 | 0xDF | DL_GET_DIE_ID | Retorna l'identificador de la matriu |

| 0xE0 | 0xE7 | DL_CHECK_INTEGRITY | Comprova i retorna els CRC a les diferents àrees, així com les banderes d'estat d'aprovació/falla per a cadascuna |

| 0xC0 | 0x8C | DL_SEC_WRITE | Escriu x bytes a la memòria començant per l'adreça absoluta y |

3.4.2 Codis operatius de resposta HDLL

Nota: Els marcs de resposta HDLL estan alineats de 4 bytes. Els bytes de càrrega útil no utilitzats queden nuls. Només les respostes DL_OK poden contenir valors de càrrega útil.

Taula 2. Llista de codis OP de resposta HDLL

| Opcode | Àlies de resposta | Descripció |

| 0 x 00 | DL_OK | S'ha passat l'ordre |

| 0 x 01 | DL_INVALID_ADDR | Adreça no permesa |

| 0x0B | DL_UNKNOW_CMD | Ordre desconeguda |

| 0x0C | DL_ABORTED_CMD | La seqüència de fragments és massa gran |

| 0x1E | DL_ADDR_RANGE_OFL_ERROR | Adreça fora de rang |

| 0x1F | DL_BUFFER_OFL_ERROR | El buffer és massa petit |

| 0 x 20 | DL_MEM_BSY | Memòria ocupada |

| 0 x 21 | DL_SIGNATURE_ERROR | Desajust de signatura |

| 0 x 24 | DL_FIRMWARE_VERSION_ERROR | Versió actual igual o superior |

| 0 x 28 | DL_PROTOCOL_ERROR | Error de protocol |

| 0x2A | DL_SFWU_DEGRADED | Corrupció de dades flash |

| 0x2D | PH_STATUS_DL_FIRST_CHUNK | Primer tros rebut |

| 0x2E | PH_STATUS_DL_NEXT_CHUNK | Espereu el següent tros |

| 0xC5 | PH_STATUS_INTERNAL_ERROR_5 | Desajust de longitud |

3.4.3 Ordre DL_RESET

Canvi de fotogrames:

PN5190 B0/B1: [HDLL] -> [0x00 0x04 0xF0 0x00 0x00 0x00 0x18 0x5B]

PN5190 B2: [HDLL] -> [0x00 0x04 0xE5 0x00 0x00 0x00 0xBF 0xB9] [HDLL] <- [0x00 0x04 STAT 0x00 CRC16] El restabliment impedeix que el PN5190 enviï la resposta DL_STATUS_OK. Per tant, només es pot rebre un estat erroni.

STAT és l'estat de retorn.

3.4.4 Ordre DL_GET_VERSION

Canvi de fotogrames:

PN5190 B0/B1: [HDLL] -> [0x00 0x04 0xF1 0x00 0x00 0x00 0x6E 0xEF]

PN5190 B2: [HDLL] -> [0x00 0x04 0xE1 0x00 0x00 0x00 0x75 0x48] [HDLL] <- [0x00 0x08 STAT HW_V RO_V MODEL_ID FM1V FM2V RFU1 RFU2 CRC16 del marc de càrrega útil Get TheVersion és:]

Taula 3. Resposta a l'ordre GetVersion

| Camp | Byte | Descripció |

| ESTADÍSTICA | 1 | Estat |

| HW_V | 2 | Versió de maquinari |

| RO_V | 3 | codi ROM |

| MODEL_ID | 4 | Identificador del model |

| FMxV | 5-6 | Versió del firmware (utilitzada per a la descàrrega) |

| RFU1-RFU2 | 7-8 | – |

Els valors esperats de diferents camps de resposta i la seva assignació són els següents:

Taula 4. Valors esperats de la resposta de l'ordre GetVersion

| Tipus IC | Versió HW (hexadecimal) | Versió ROM (hexadecimal) | Identificador del model (hexadecimal) | Versió FW (hexadecimal) |

| PN5190 B0 | 0 x 51 | 0 x 02 | 0 x 00 | xx.aa |

| PN5190 B1 | 0 x 52 | 0 x 02 | 0 x 00 | xx.aa |

| PN5190 B2 | 0 x 53 | 0 x 03 | 0 x 00 | xx.aa |

3.4.5 Ordre DL_GET_SESSION_STATE

Canvi de fotogrames:

PN5190 B0/B1: [HDLL] -> [0x00 0x04 0xF2 0x00 0x00 0x00 0xF5 0x33]

PN5190 B2: [HDLL] -> [0x00 0x04 0xDB 0x00 0x00 0x00 0x31 0x0A] [HDLL] <- [0x00 0x04 STAT SSTA RFU CRC16] El marc de càrrega útil de la resposta GetSession és:

Taula 5. Resposta a l'ordre GetSession

| Camp | Byte | Descripció |

| ESTADÍSTICA | 1 | Estat |

| SSTA | 2 | Estat de la sessió • 0x00: tancat • 0x01: obert • 0x02: bloquejat (no es permet la baixada més) |

| RFU | 3-4 |

3.4.6 Ordre DL_GET_DIE_ID

Canvi de fotogrames:

PN5190 B0/B1: [HDLL] -> [0x00 0x04 0xF4 0x00 0x00 0x00 0xD2 0xAA]

PN5190 B2: [HDLL] -> [0x00 0x04 0xDF 0x00 0x00 0x00 0xFB 0xFB] [HDLL] <- [0x00 0x14 STAT 0x00 0x00 0x00 ID0 ID1 ID2 ID3 ID4 ID5 ID6 ID7 ID8 ID9

ID10 ID11 ID12 ID13 ID14 ID15 CRC16] El marc de càrrega útil de la resposta GetDieId és:

Taula 6. Resposta a l'ordre GetDieId

| Camp | Byte | Descripció |

| ESTADÍSTICA | 1 | Estat |

| RFU | 2-4 | |

| DIEID | 5-20 | ID de la matriu (16 bytes) |

3.4.7 Ordre DL_CHECK_INTEGRITY

Canvi de fotogrames:

PN5190 B0/B1: [HDLL] -> [0x00 0x04 0xE0 0x00 0x00 0x00 CRC16]

PN5190 B2: [HDLL] -> [0x00 0x04 0xE7 0x00 0x00 0x00 0x52 0xD1] [HDLL] <- [0x00 0x20 STAT LEN_DATA LEN_CODE 0x00 [CRC_INFO] [CRC32] El marc de càrrega útil de la resposta és el CRC16 CheckIn:

Taula 7. Resposta a l'ordre CheckIntegrity

| Camp | Byte | Valor/Descripció | |

| ESTADÍSTICA | 1 | Estat | |

| DADES LEN | 2 | Nombre total de seccions de dades | |

| CODI LEN | 3 | Nombre total de seccions de codi | |

| RFU | 4 | Reservat | |

| [CRC_INFO] | 58 | 32 bits (little-endian). Si s'estableix un bit, el CRC de la secció corresponent està bé, en cas contrari, no és correcte. | |

| Bit | Estat d'integritat de l'àrea | ||

| [31:28] | Reservat [3] | ||

| [27:23] | Reservat [1] | ||

| [22] | Reservat [3] | ||

| [21:20] | Reservat [1] | ||

| [19] | Àrea de configuració de RF (PN5190 B0/B1) [2] Reservat (PN5190 B2) [3] | ||

| [18] | Àrea de configuració del protocol (PN5190 B0/B1) [2] Àrea de configuració de RF (PN5190 B2) [2] | ||

| [17] | Reservat (PN5190 B0/B1) [3] Àrea de configuració d'usuari (PN5190 B2) [2] | ||

| [16:6] | Reservat [3] | ||

| [5:4] | Reservat per a PN5190 B0/B1 [3] Reservat per a PN5190 B2 [1] | ||

| [3:0] | Reservat [1] | ||

| [CRC32] | 9-136 | CRC32 de les 32 seccions. Cada CRC és de 4 bytes emmagatzemats en format little-endian. Els primers 4 bytes de CRC són del bit CRC_INFO[31], els següents 4 bytes de CRC són del bit CRC_INFO[30] i així successivament. |

|

- [1] Aquest bit ha de ser 1 perquè el PN5190 funcioni correctament (amb funcions i/o descàrrega de FW xifrada).

- [2] Aquest bit està establert a 1 per defecte, però la configuració modificada per l'usuari invalida el CRC. No hi ha cap efecte sobre la funcionalitat PN5190.

- [3] Aquest valor de bit, encara que sigui 0, no és rellevant. Aquest valor de bit es pot ignorar.

3.4.8 Ordre DL_SEC_WRITE

L'ordre DL_SEC_WRITE s'ha de considerar en el context d'una seqüència d'ordres d'escriptura segura: la "descàrrega de microprogramari segura" xifrada (sovint anomenada eSFWu).

L'ordre d'escriptura segura obre primer la sessió de descàrrega i passa l'autenticació RSA. Els següents passen adreces i bytes xifrats per escriure al Flash PN5190. Tots menys l'últim conté els hash següents, per tant, informant que no són els últims i unint criptogràficament els fotogrames de la seqüència.

Altres ordres (excepte DL_RESET i DL_CHECK_INTEGRITY) es poden inserir entre les ordres d'escriptura segures d'una seqüència sense trencar-la.

3.4.8.1 Primera ordre DL_SEC_WRITE

Una ordre d'escriptura segura és la primera si i només si:

- La longitud del fotograma és de 312 bytes

- No s'ha rebut cap ordre d'escriptura segura des de l'últim restabliment.

- El PN5190 verifica correctament la signatura incrustada.

La resposta a la primera ordre de trama seria la següent: [HDLL] <- [0x00 0x04 STAT 0x00 0x00 0x00 CRC16] STAT és l'estat de retorn.

Nota: S'ha d'escriure almenys un tros de dades durant un eSFWu tot i que les dades escrites només poden tenir una longitud d'un byte. Per tant, la primera ordre sempre contindrà el hash de l'ordre següent, ja que almenys hi haurà dues ordres.

3.4.8.2 Ordres DL_SEC_WRITE mitjanes

Una ordre d'escriptura segura és una "mitjana" si i només si:

- El codi operatiu és el que es descriu a la Secció 3.4.1 per a l'ordre DL_SEC_WRITE.

- Ja s'ha rebut una primera ordre d'escriptura segura i s'ha verificat correctament abans

- No s'ha produït cap restabliment des que es va rebre la primera ordre d'escriptura segura

- La longitud del fotograma és igual a la mida de les dades + mida de la capçalera + mida hash: FLEN = SIZE + 6 + 32

- El resum de tot el fotograma és igual al valor hash rebut al fotograma anterior

La resposta a la primera ordre de trama seria la següent: [HDLL] <- [0x00 0x04 STAT 0x00 0x00 0x00 CRC16] STAT és l'estat de retorn.

3.4.8.3 Última ordre DL_SEC_WRITE

Una ordre d'escriptura segura és l'última si i només si:

- El codi operatiu és el que es descriu a la Secció 3.4.1 per a l'ordre DL_SEC_WRITE.

- Ja s'ha rebut una primera ordre d'escriptura segura i s'ha verificat correctament abans

- No s'ha produït cap restabliment des que es va rebre la primera ordre d'escriptura segura

- La longitud del fotograma és igual a la mida de les dades + mida de la capçalera: FLEN = SIZE + 6

- El resum de tot el fotograma és igual al valor hash rebut al fotograma anterior

La resposta a la primera ordre de trama seria la següent: [HDLL] <- [0x00 0x04 STAT 0x00 0x00 0x00 CRC16] STAT és l'estat de retorn.

Mode d'arrencada operativa de l'IC - Mode de funcionament normal

4.1 Introducció

En general, PN5190 IC ha d'estar en mode de funcionament normal per obtenir-ne la funcionalitat NFC.

Quan s'engega el PN5190 IC, sempre està esperant que es rebin ordres d'un amfitrió per dur a terme l'operació, tret que els esdeveniments generats dins del PN5190 IC hagin donat lloc a l'arrencada del PN5190 IC.

4.2 S'ha acabat la llista d'ordresview

Taula 8. Llista d'ordres PN5190

| Codi de comandament | Nom de l'ordre |

| 0 x 00 | WRITE_REGISTER |

| 0 x 01 | WRITE_REGISTER_OR_MASK |

| 0 x 02 | WRITE_REGISTER_AND_MASK |

| 0 x 03 | WRITE_REGISTER_MULTIPLE |

| 0 x 04 | READ_REGISTER |

| 0 x 05 | READ_REGISTER_MULTIPLE |

| 0 x 06 | WRITE_E2PROM |

| 0 x 07 | READ_E2PROM |

| 0 x 08 | TRANSMIT_RF_DATA |

| 0 x 09 | RETRIEVE_RF_DATA |

| 0x0A | EXCHANGE_RF_DATA |

| 0x0B | MFC_AUTHENTICATE |

| 0x0C | EPC_GEN2_INVENTORY |

| 0x0D | LOAD_RF_CONFIGURATION |

| 0x0E | UPDATE_RF_CONFIGURATION |

| 0x0F | GET_ RF_CONFIGURATION |

| 0 x 10 | RF_ON |

| 0 x 11 | RF_OFF |

| 0 x 12 | CONFIGURA TESTBUS_DIGITAL |

| 0 x 13 | CONFIGURE_TESTBUS_ANALOG |

| 0 x 14 | CTS_ENABLE |

| 0 x 15 | CTS_CONFIGURE |

| 0 x 16 | CTS_RETRIEVE_LOG |

| 0x17-0x18 | RFU |

| 0 x 19 | fins a FW v2.01: RFU |

| des del FW v2.03 en endavant: RETRIEVE_RF_FELICA_EMD_DATA | |

| 0x1A | RECEIVE_RF_DATA |

| 0x1B-0x1F | RFU |

| 0 x 20 | SWITCH_MODE_NORMAL |

| 0 x 21 | SWITCH_MODE_AUTOCOLL |

| 0 x 22 | SWITCH_MODE_STANDBY |

| 0 x 23 | SWITCH_MODE_LPCD |

| 0 x 24 | RFU |

| 0 x 25 | SWITCH_MODE_DOWNLOAD |

| 0 x 26 | GET_DIEID |

| 0 x 27 | GET_VERSION |

| 0 x 28 | RFU |

| 0 x 29 | fins a FW v2.05: RFU |

| a partir de la versió 2.06 de FW: GET_CRC_USER_AREA | |

| 0x2A | fins a FW v2.03: RFU |

| a partir del FW v2.05: CONFIGURE_MULTIPLE_TESTBUS_DIGITAL | |

| 0x2B-0x3F | RFU |

| 0 x 40 | ANTENNA_SELF_TEST (no compatible) |

| 0 x 41 | PRBS_TEST |

| 0x42-0x4F | RFU |

4.3 Valors d'estat de resposta

A continuació es mostren els valors d'estat de resposta, que es retornen com a part de la resposta des de PN5190 després que l'ordre estigui operativa.

Taula 9. Valors d'estat de resposta PN5190

| Estat de resposta | Valor d'estat de resposta | Descripció |

| PN5190_STATUS_SUCCESS | 0 x 00 | Indica que l'operació s'ha completat correctament |

| PN5190_STATUS_TIMEOUT | 0 x 01 | Indica que l'operació de l'ordre ha provocat un temps d'espera |

| PN5190_STATUS_INTEGRITY_ERROR | 0 x 02 | Indica que l'operació de l'ordre ha provocat un error en la integritat de les dades de RF |

| PN5190_STATUS_RF_COLLISION_ERROR | 0 x 03 | Indica que l'operació de l'ordre va provocar un error de col·lisió de RF |

| PN5190_STATUS_RFU1 | 0 x 04 | Reservat |

| PN5190_STATUS_INVALID_COMMAND | 0 x 05 | Indica que l'ordre donada no és vàlida/no s'ha implementat |

| PN5190_STATUS_RFU2 | 0 x 06 | Reservat |

| PN5190_STATUS_AUTH_ERROR | 0 x 07 | Indica que l'autenticació MFC ha fallat (permís denegat) |

| PN5190_STATUS_MEMORY_ERROR | 0 x 08 | Indica que l'operació de l'ordre ha provocat un error de programació o un error de memòria interna |

| PN5190_STATUS_RFU4 | 0 x 09 | Reservat |

| PN5190_STATUS_NO_RF_FIELD | 0x0A | Indica que no hi ha cap error o hi ha un error en la presència interna del camp de RF (aplicable només si el mode iniciador/lector) |

| PN5190_STATUS_RFU5 | 0x0B | Reservat |

| PN5190_STATUS_SYNTAX_ERROR | 0x0C | Indica que s'ha rebut una longitud de trama d'ordres no vàlida |

| PN5190_STATUS_RESOURCE_ERROR | 0x0D | Indica que s'ha produït un error de recurs intern |

| PN5190_STATUS_RFU6 | 0x0E | Reservat |

| PN5190_STATUS_RFU7 | 0x0F | Reservat |

| PN5190_STATUS_NO_EXTERNAL_RF_FIELD | 0 x 10 | Indica que no hi ha cap camp de RF extern durant l'execució de l'ordre (aplicable només en mode targeta/objectiu) |

| PN5190_STATUS_RX_TIMEOUT | 0 x 11 | Indica que no es reben dades després d'iniciar RFExchange i esgotar el temps d'espera de RX. |

| PN5190_STATUS_USER_CANCELLED | 0 x 12 | Indica que l'ordre actual en curs s'ha avortat |

| PN5190_STATUS_PREVENT_STANDBY | 0 x 13 | Indica que PN5190 no pot entrar en mode d'espera |

| PN5190_STATUS_RFU9 | 0 x 14 | Reservat |

| PN5190_STATUS_CLOCK_ERROR | 0 x 15 | Indica que el rellotge del CLIF no s'ha iniciat |

| PN5190_STATUS_RFU10 | 0 x 16 | Reservat |

| PN5190_STATUS_PRBS_ERROR | 0 x 17 | Indica que l'ordre PRBS ha retornat un error |

| PN5190_STATUS_INSTR_ERROR | 0 x 18 | Indica que l'operació de l'ordre ha fallat (pot incloure, l'error en els paràmetres de la instrucció, l'error de sintaxi, l'error en el propi funcionament, no es compleixen els requisits previs per a la instrucció, etc.) |

| PN5190_STATUS_ACCESS_DENIED | 0 x 19 | Indica que l'accés a la memòria interna està denegat |

| PN5190_STATUS_TX_FAILURE | 0x1A | Indica que la TX per RF ha fallat |

| PN5190_STATUS_NO_ANTENNA | 0x1B | Indica que no hi ha cap antena connectada/present |

| PN5190_STATUS_TXLDO_ERROR | 0x1C | Indica que hi ha un error a TXLDO quan el VUP no està disponible i RF està activat. |

| PN5190_STATUS_RFCFG_NOT_APPLIED | 0x1D | Indica que la configuració de RF no es carrega quan RF està activat |

| PN5190_STATUS_TIMEOUT_WITH_EMD_ERROR | 0x1E | fins a FW 2.01: no s'esperava |

| a partir del FW 2.03: Indica que durant l'intercanvi amb LOG ENABLE BIT està establert al registre FeliCa EMD, s'ha observat un error FeliCa EMD |

||

| PN5190_STATUS_INTERNAL_ERROR | 0x7F | Indica que l'operació NVM ha fallat |

| PN5190_STATUS_SUCCSES_CHAINING | 0xAF | Indica que, a més, les dades estan pendents de llegir |

4.4 Esdeveniments acabatsview

Hi ha dues maneres de notificar els esdeveniments a l'amfitrió.

4.4.1 Esdeveniments normals sobre el pin IRQ

Aquests esdeveniments són les categories següents:

- Sempre activat: l'amfitrió sempre s'avisa

- Controlat per l'amfitrió: l'amfitrió es notifica si el bit d'habilitació d'esdeveniments corresponent està establert al registre (EVENT_ENABLE (01h)).

Les interrupcions de baix nivell de les IP perifèriques, inclòs el CLIF, s'han de gestionar completament dins del microprogramari i l'amfitrió només es notificarà dels esdeveniments enumerats a la secció d'esdeveniments.

El microprogramari implementa dos registres d'esdeveniments com a registres RAM que es poden escriure/llegir mitjançant les ordres de la Secció 4.5.1.1/Secció 4.5.1.5.

El registre EVENT_ENABLE (0x01) => Activa les notificacions específiques/de tots els esdeveniments.

El registre EVENT_STATUS (0x02) => Part de la càrrega útil del missatge d'esdeveniment.

L'amfitrió esborrarà els esdeveniments un cop l'amfitrió hagi llegit el missatge de l'esdeveniment.

Els esdeveniments són de naturalesa asíncrona i es notifiquen a l'amfitrió, si estan habilitats dins del registre EVENT_ENABLE.

A continuació es mostra la llista d'esdeveniments que estaran disponibles per a l'amfitrió com a part del missatge de l'esdeveniment.

Taula 10. Esdeveniments PN5190 (contingut de EVENT_STATUS)

| Bit - Interval | Camp [1] | Sempre Activat (S/N) | |

| 31 | 12 | RFU | NA |

| 11 | 11 | CTS_EVENT [2] | N |

| 10 | 10 | IDLE_EVENT | Y |

| 9 | 9 | LPCD_CALIBRATION_DONE_EVENT | Y |

| 8 | 8 | LPCD_EVENT | Y |

| 7 | 7 | AUTOCOLL_EVENT | Y |

| 6 | 6 | TIMER0_EVENT | N |

| 5 | 5 | TX_OVERCURRENT_EVENT | N |

| 4 | 4 | RFON_DET_EVENT [2] | N |

| 3 | 3 | RFOFF_DET_EVENT [2] | N |

| 2 | 2 | STANDBY_PREV_EVENT | Y |

| 1 | 1 | GENERAL_ERROR_EVENT | Y |

| 0 | 0 | BOOT_EVENT | Y |

- Tingueu en compte que no hi ha dos esdeveniments marcats excepte en cas d'error. En cas d'error durant l'operació, s'establiran l'esdeveniment funcional (per exemple, BOOT_EVENT, AUTOCALL_EVENT, etc.) i GENERAL_ERROR_EVENT.

- Aquest esdeveniment es desactivarà automàticament després de publicar-lo a l'amfitrió. L'amfitrió hauria de tornar a habilitar aquests esdeveniments si vol que se li notifiquen aquests esdeveniments.

4.4.1.1 Formats de missatges d'esdeveniment

El format del missatge d'esdeveniment varia en funció de les ocurrències d'un esdeveniment i de l'estat diferent del PN5190.

L'amfitrió ha de llegir tag (T) i la longitud del missatge (L) i després llegiu el nombre de bytes corresponent com a valor (V) dels esdeveniments.

En general, el missatge d'esdeveniment (vegeu la figura 12) conté l'EVENT_STATUS tal com es defineix a la Taula 11 i les dades d'esdeveniment corresponen al bit d'esdeveniment respectiu establert a EVENT_STATUS.

Nota:

Per a alguns esdeveniments, la càrrega útil no existeix. Per exemple, si s'activa TIMER0_EVENT, només es proporciona EVENT_STATUS com a part del missatge d'esdeveniment.

La Taula 11 també detalla si les dades d'esdeveniment estan presents per a l'esdeveniment corresponent al missatge d'esdeveniment. GENERAL_ERROR_EVENT també es pot produir amb altres esdeveniments.

GENERAL_ERROR_EVENT també es pot produir amb altres esdeveniments.

En aquest escenari, el missatge d'esdeveniment (vegeu la figura 13) conté EVENT_STATUS tal com es defineix a la taula 11 i GENERAL_ERROR_STATUS_DATA tal com es defineix a la taula 14 i, a continuació, les dades de l'esdeveniment corresponen al bit d'esdeveniment respectiu establert a EVENT_STATUS tal com es defineix a la taula 11. Nota:

Nota:

Només després de BOOT_EVENT o després de POR, STANDBY, ULPCD, l'amfitrió podrà funcionar en el mode de funcionament normal emetent les ordres esmentades anteriorment.

En cas d'avortar una ordre en execució existent, només després d'IDLE_EVENT, l'amfitrió podrà funcionar en el mode de funcionament normal emetent les ordres enumerades anteriorment.

4.4.1.2 Diferents definicions d'estat d'ESDEVENIMENT

4.4.1.2.1 Definicions de bits per a EVENT_STATUS

Taula 11. Definicions dels bits EVENT_STATUS

| Bit (A - De) | Esdeveniment | Descripció | Dades de l'esdeveniment corresponent (si n'hi ha) |

|

| 31 | 12 | RFU | Reservat | |

| 11 | 11 | CTS_EVENT | Aquest bit s'estableix quan es genera l'esdeveniment CTS. | Taula 86 |

| 10 | 10 | IDLE_EVENT | Aquest bit s'estableix quan l'ordre en curs es cancel·la a causa de l'emissió de l'ordre SWITCH_MODE_NORMAL. | No hi ha dades d'esdeveniment |

| 9 | 9 | LPCD_CALIBRATION_DONE_ ESDEVENIMENT |

Aquest bit s'estableix quan es genera l'esdeveniment de calibratge LPCD fet. | Taula 16 |

| 8 | 8 | LPCD_EVENT | Aquest bit s'estableix quan es genera l'esdeveniment LPCD. | Taula 15 |

| 7 | 7 | AUTOCOLL_EVENT | Aquest bit s'activa quan s'ha completat l'operació AUTOCOLL. | Taula 52 |

| 6 | 6 | TIMER0_EVENT | Aquest bit s'estableix quan es produeix l'esdeveniment TIMER0. | No hi ha dades d'esdeveniment |

| 5 | 5 | TX_OVERCURRENT_ERROR_ ESDEVENIMENT |

Aquest bit s'estableix quan el corrent del controlador TX és superior al llindar definit a l'EEPROM. En aquesta condició, el camp s'apaga automàticament abans de la notificació a l'amfitrió. Consulteu la secció 4.4.2.2. | No hi ha dades d'esdeveniment |

| 4 | 4 | RFON_DET_EVENT | Aquest bit s'estableix quan es detecta el camp de RF extern. | No hi ha dades d'esdeveniment |

| 3 | 3 | RFOFF_DET_EVENT | Aquest bit s'estableix quan el camp de RF extern ja existent desapareix. | No hi ha dades d'esdeveniment |

| 2 | 2 | STANDBY_PREV_EVENT | Aquest bit s'activa quan s'impedeix l'espera a causa de les condicions de prevenció | Taula 13 |

| 1 | 1 | GENERAL_ERROR_EVENT | Aquest bit s'estableix quan existeixen condicions d'error generals | Taula 14 |

| 0 | 0 | BOOT_EVENT | Aquest bit s'estableix quan s'inicia el PN5190 amb POR/Standby | Taula 12 |

4.4.1.2.2 Definicions de bits per a BOOT_STATUS_DATA

Taula 12. Definicions dels bits BOOT_STATUS_DATA

| Poc a | Bit De | Estat d'arrencada | Motiu d'arrencada a causa de |

| 31 | 27 | RFU | Reservat |

| 26 | 26 | ULP_STANDBY | Motiu d'arrencada a causa de la sortida de ULP_STANDBY. |

| 25 | 23 | RFU | Reservat |

| 22 | 22 | BOOT_ RX_ULPDET | RX ULPDET va donar lloc a l'arrencada en mode d'espera ULP |

| 21 | 21 | RFU | Reservat |

| 20 | 20 | BOOT_SPI | Motiu d'arrencada a causa de la baixada del senyal SPI_NTS |

| 19 | 17 | RFU | Reservat |

| 16 | 16 | BOOT_GPIO3 | Motiu d'arrencada a causa de la transició de GPIO3 de baix a alt. |

| 15 | 15 | BOOT_GPIO2 | Motiu d'arrencada a causa de la transició de GPIO2 de baix a alt. |

| 14 | 14 | BOOT_GPIO1 | Motiu d'arrencada a causa de la transició de GPIO1 de baix a alt. |

| 13 | 13 | BOOT_GPIO0 | Motiu d'arrencada a causa de la transició de GPIO0 de baix a alt. |

| 12 | 12 | BOOT_LPDET | Motiu d'arrencada a causa de la presència de camp RF extern durant STANDBY/SUSPEND |

| 11 | 11 | RFU | Reservat |

| 10 | 8 | RFU | Reservat |

| 7 | 7 | BOOT_SOFT_RESET | Motiu d'arrencada a causa del restabliment suau de l'IC |

| 6 | 6 | BOOT_VDDIO_LOSS | Motiu d'arrencada a causa de la pèrdua de VDDIO. Consulteu la secció 4.4.2.3 |

| 5 | 5 | BOOT_VDDIO_START | Motiu d'arrencada si s'ha introduït STANDBY amb VDDIO LOSS. Consulteu la secció 4.4.2.3 |

| 4 | 4 | BOOT_WUC | Motiu d'arrencada a causa del comptador de despertador transcorregut durant qualsevol de les operacions STANDBY. |

| 3 | 3 | BOOT_TEMP | El motiu d'arrencada a causa de la temperatura de l'IC és superior al límit de llindar configurat. Consulteu la secció 4.4.2.1 |

| 2 | 2 | BOOT_WDG | Motiu d'arrencada a causa del restabliment del gos vigilant |

| 1 | 1 | RFU | Reservat |

| 0 | 0 | BOOT_POR | Motiu d'arrencada per restabliment de l'engegada |

4.4.1.2.3 Definicions de bits per a STANDBY_PREV_STATUS_DATA

Taula 13. Definicions dels bits STANDBY_PREV_STATUS_DATA

| Poc a | Bit De | Prevenció en espera | S'ha impedit l'espera a causa de |

| 31 | 26 | RFU | RESERVAT |

| 25 | 25 | RFU | RESERVAT |

| 24 | 24 | PREV_TEMP | La temperatura de funcionament dels circuits integrats està fora del llindar |

| 23 | 23 | RFU | RESERVAT |

| 22 | 22 | PREV_HOSTCOMM | Interfície de comunicació de l'amfitrió |

| 21 | 21 | PREV_SPI | El senyal SPI_NTS s'està baixant |

| 20 | 18 | RFU | RESERVAT |

| 17 | 17 | PREV_GPIO3 | Transició del senyal GPIO3 de baix a alt |

| 16 | 16 | PREV_GPIO2 | Transició del senyal GPIO2 de baix a alt |

| 15 | 15 | PREV_GPIO1 | Transició del senyal GPIO1 de baix a alt |

| 14 | 14 | PREV_GPIO0 | Transició del senyal GPIO0 de baix a alt |

| 13 | 13 | PREV_WUC | El comptador de despertador ha transcorregut |

| 12 | 12 | PREV_LPDET | Detecció de baixa potència. Es produeix quan es detecta un senyal de RF extern en el procés de posar-se en espera. |

| 11 | 11 | PREV_RX_ULPDET | Detecció de potència ultra baixa RX. Es produeix quan es detecta un senyal de RF en el procés d'anar a ULP_STANDBY. |

| 10 | 10 | RFU | RESERVAT |

| 9 | 5 | RFU | RESERVAT |

| 4 | 4 | RFU | RESERVAT |

| 3 | 3 | RFU | RESERVAT |

| 2 | 2 | RFU | RESERVAT |

| 1 | 1 | RFU | RESERVAT |

| 0 | 0 | RFU | RESERVAT |

4.4.1.2.4 Definicions de bits per a GENERAL_ERROR_STATUS_DATA

Taula 14. Definicions dels bits GENERAL_ERROR_STATUS_DATA

| Poc a | Una mica de | Estat d'error | Descripció |

| 31 | 6 | RFU | Reservat |

| 5 | 5 | XTAL_START_ERROR | L'inici de XTAL ha fallat durant l'arrencada |

| 4 | 4 | SYS_TRIM_RECOVERY_ERROR | S'ha produït un error de memòria de retall del sistema intern, però la recuperació ha fallat. El sistema funciona en mode rebaixat. |

| 3 | 3 | SYS_TRIM_RECOVERY_SUCCESS | S'ha produït un error de memòria de retall del sistema intern i la recuperació ha estat correcta. L'amfitrió ha de reiniciar el PN5190 perquè la recuperació tingui efecte. |

| 2 | 2 | TXLDO_ERROR | Error TXLDO |

| 1 | 1 | CLOCK_ERROR | Error de rellotge |

| 0 | 0 | GPADC_ERROR | Error ADC |

4.4.1.2.5 Definicions de bits per a LPCD_STATUS_DATA

Taula 15. Definicions dels bytes LPCD_STATUS_DATA

| Poc a | Bit De | Aplicabilitat dels bits d'estat segons l'operació subjacent de LPCD o ULPCD | La descripció del bit corresponent s'estableix en byte d'estat. | ||

| LPCD | ULPCD | ||||

| 31 | 7 | RFU | Reservat | ||

| 6 | 6 | Avorta_HIF | Y | N | Avortat a causa de l'activitat HIF |

| 5 | 5 | Error CLKDET | N | Y | Avortat a causa d'un error CLKDET |

| 4 | 4 | Temps d'espera XTAL | N | Y | Avortat perquè s'ha produït el temps d'espera XTAL |

| 3 | 3 | VDDPA LDO Sobreintensitat | N | Y | Avortat a causa d'una sobreintensitat de VDDPA LDO |

| 2 | 2 | Camp de RF extern | Y | Y | Avortat a causa d'un camp de RF extern |

| 1 | 1 | GPIO3 Avorta | N | Y | Avortat a causa del canvi de nivell de GPIO3 |

| 0 | 0 | S'ha detectat la targeta | Y | Y | S'ha detectat la targeta |

4.4.1.2.6 Definicions de bits per a dades d'estat LPCD_CALIBRATION_DONE

Taula 16. Definicions dels bytes de dades d'estat LPCD_CALIBRATION_DONE per a ULPCD

| Poc a | Bit De | Estat de LPCD_CALIBRATION DONE esdeveniment | La descripció del bit corresponent s'estableix en byte d'estat. |

| 31 | 11 | Reservat | |

| 10 | 0 | Valor de referència de la calibració ULPCD | El valor RSSI mesurat durant la calibració ULPCD que s'utilitza com a referència durant ULPCD |

Taula 17. Definicions dels bytes de dades d'estat LPCD_CALIBRATION_DONE per a LPCD

| Poc a | Bit De | Aplicabilitat dels bits d'estat segons l'operació subjacent de LPCD o ULPCD | La descripció del bit corresponent s'estableix en byte d'estat. | ||

| 2 | 2 | Camp de RF extern | Y | Y | Avortat a causa d'un camp de RF extern |

| 1 | 1 | GPIO3 Avorta | N | Y | Avortat a causa del canvi de nivell de GPIO3 |

| 0 | 0 | S'ha detectat la targeta | Y | Y | S'ha detectat la targeta |

4.4.2 Maneig de diferents escenaris d'arrencada

L'IC PN5190 gestiona diferents condicions d'error relacionades amb els paràmetres de l'IC com a continuació.

4.4.2.1 Gestió de l'escenari de sobretemperatura quan PN5190 està en funcionament

Sempre que la temperatura interna del PN5190 IC arriba al valor llindar configurat al camp EEPROM TEMP_WARNING [2], l'IC entra en espera. I, en conseqüència, si el camp EEPROM ENABLE_GPIO0_ON_OVERTEMP [2] està configurat per enviar una notificació a l'amfitrió, aleshores GPIO0 s'elevarà per notificar la sobretemperatura de l'IC.

Quan la temperatura de l'IC cau per sota del valor llindar configurat al camp EEPROM TEMP_WARNING [2], l'IC s'iniciarà amb BOOT_EVENT com a la Taula 11 i el bit d'estat d'arrencada BOOT_TEMP s'estableix com a la Taula 12 i GPIO0 es baixarà.

4.4.2.2 Tractament de sobreintensitat

Si PN5190 IC detecta la condició de sobreintensitat, l'IC desactiva l'alimentació de RF i envia el TX_OVERCURRENT_ERROR_EVENT com a la Taula 11.

La durada de la condició de sobreintensitat es pot controlar modificant el camp EEPROM TXLDO_CONFIG [2].

Per obtenir informació sobre l'IC sobre el llindar actual, consulteu el document [2].

Nota:

Si hi ha altres esdeveniments o resposta pendents, s'enviaran a l'amfitrió.

4.4.2.3 Pèrdua de VDDIO durant el funcionament

Si PN5190 IC troba que no hi ha VDDIO (pèrdua de VDDIO), l'IC entra en espera.

L'IC arrenca només quan el VDDIO està disponible, amb BOOT_EVENT com a la Taula 11 i el bit d'estat d'arrencada BOOT_VDDIO_START s'estableix com a la Taula 12.

Per obtenir informació sobre les característiques estàtiques de PN5190 IC, consulteu el document [2].

4.4.3 Gestió d'escenaris d'avortament

L'IC PN5190 té un suport per avortar les ordres d'execució actuals i el comportament de l'IC PN5190, quan aquesta ordre d'avortament, com ara la secció 4.5.4.5.2, s'envia a l'IC PN5190, com es mostra a la Taula 18.

Nota:

Quan PN5190 IC es troba en mode ULPCD i ULP-Standby, no es pot cancel·lar ni enviant una secció 4.5.4.5.2 O iniciant una transacció SPI (en baixar el senyal SPI_NTS).

Taula 18. Resposta a l'esdeveniment esperada quan diferents ordres finalitzaven amb la secció 4.5.4.5.2

| Ordres | Comportament quan s'envia l'ordre de canvi de mode normal |

| Totes les ordres on no s'introdueixi poca potència | EVENT_STAUS s'ha establert en “IDLE_EVENT” |

| Canvi de mode LPCD | EVENT_STATUS s'estableix a "LPCD_EVENT" amb "LPCD_ STATUS_DATA" que indica els bits d'estat com "Abort_HIF" |

| Canvia el mode d'espera | EVENT_STAUS s'estableix a "BOOT_EVENT" amb "BOOT_ STATUS_DATA" que indica els bits "BOOT_SPI" |

| Mode de commutació automàtica (sense mode autònom, mode autònom amb espera i mode autònom sense espera) | EVENT_STAUS s'estableix en "AUTOCOLL_EVENT" amb els bits STATUS_DATA que indiquen que l'ordre s'ha cancel·lat per l'usuari. |

4.5 Detalls de les instruccions d'operació en mode normal

4.5.1 Manipulació del registre

Les instruccions d'aquesta secció s'utilitzen per accedir als registres lògics de PN5190.

4.5.1.1 WRITE_REGISTER

Aquesta instrucció s'utilitza per escriure un valor de 32 bits (little-endian) en un registre lògic.

4.5.1.1.1 Condicions

L'adreça del registre ha d'existir i el registre ha de tenir l'atribut READ-WRITE o WRITE-ONLY.

4.5.1.1.2 Comandament

Taula 19. Valor de l'ordre WRITE_REGISTER Escriu un valor de 32 bits en un registre.

| Camp de càrrega útil | Longitud | Valor/Descripció |

| Adreça de registre | 1 byte | Adreça del registre. |

Taula 19. Valor de l'ordre WRITE_REGISTER…continuació

Escriu un valor de 32 bits en un registre.

| Camp de càrrega útil | Longitud | Valor/Descripció |

| Valor | 4 bytes | Valor de registre de 32 bits que cal escriure. (Little-endian) |

4.5.1.1.3 Resposta

Taula 20. Valor de resposta WRITE_REGISTER

| Camp de càrrega útil | Longitud | Valor/Descripció |

| Estat | 1 byte | Estat de l'operació [Taula 9]. Els valors esperats són els següents: |

| PN5190_STATUS_SUCCESS | ||

| PN5190_STATUS_INSTR_ERROR |

4.5.1.1.4 esdeveniment

No hi ha esdeveniments per a aquesta comanda.

4.5.1.2 WRITE_REGISTER_OR_MASK

Aquesta instrucció s'utilitza per modificar el contingut del registre mitjançant una operació OR lògica. Es llegeix el contingut del registre i es realitza una operació OR lògica amb la màscara proporcionada. El contingut modificat es torna a escriure al registre.

4.5.1.2.1 Condicions

L'adreça del registre ha d'existir i el registre ha de tenir l'atribut READ-WRITE.

4.5.1.2.2 Comandament

Taula 21. Valor de l'ordre WRITE_REGISTER_OR_MASK Realitzeu una operació OR lògica en un registre mitjançant la màscara proporcionada.

| Camp de càrrega útil | Longitud | Valor/descripció |

| Adreça de registre | 1 byte | Adreça del registre. |

| Màscara | 4 bytes | Màscara de bits utilitzada com a operand per a l'operació OR lògica. (Little-endian) |

4.5.1.2.3 Resposta

Taula 22. Valor de resposta WRITE_REGISTER_OR_MASK

| Camp de càrrega útil | Longitud | Valor/Descripció |

| Estat | 1 byte | Estat de l'operació [Taula 9]. Els valors esperats són els següents: |

| PN5190_STATUS_SUCCESS | ||

| PN5190_STATUS_INSTR_ERROR |

4.5.1.2.4 esdeveniment

No hi ha esdeveniments per a aquesta comanda.

4.5.1.3 ESCRIU_REGISTER_I_MÁSCARA

Aquesta instrucció s'utilitza per modificar el contingut del registre mitjançant una operació AND lògica. Es llegeix el contingut del registre i es realitza una operació AND lògica amb la màscara proporcionada. El contingut modificat es torna a escriure al registre.

4.5.1.3.1 Condicions

L'adreça del registre ha d'existir i el registre ha de tenir l'atribut READ-WRITE.

4.5.1.3.2 Comandament

Taula 23. Valor de l'ordre WRITE_REGISTER_AND_MASK Realitzeu una operació AND lògica en un registre mitjançant la màscara proporcionada.

| Camp de càrrega útil | Longitud | Valor/descripció |

| Adreça de registre | 1 byte | Adreça del registre. |

| Màscara | 4 bytes | Màscara de bits utilitzada com a operand per a l'operació AND lògica. (Little-endian) |

4.5.1.3.3 Resposta

Taula 24. Valor de resposta WRITE_REGISTER_AND_MASK

| Camp de càrrega útil | Longitud | Valor/Descripció |

| Estat | 1 byte | Estat de l'operació [Taula 9]. Els valors esperats són els següents: |

| PN5190_STATUS_SUCCESS | ||

| PN5190_STATUS_INSTR_ERROR |

4.5.1.3.4 esdeveniment

No hi ha esdeveniments per a aquesta comanda.

4.5.1.4 WRITE_REGISTER_MULTIPLE

Aquesta funcionalitat d'instruccions és similar a la Secció 4.5.1.1, Secció 4.5.1.2, Secció 4.5.1.3, amb la possibilitat de combinar-les. De fet, pren una matriu de conjunt de valors de tipus de registre i realitza l'acció adequada. El tipus reflecteix l'acció que és registre d'escriptura, operació OR lògica en un registre o operació AND lògica en un registre.

4.5.1.4.1 Condicions

L'adreça lògica corresponent del registre dins d'un conjunt ha d'existir.

L'atribut d'accés al registre ha de permetre l'execució de l'acció requerida (tipus):

- Acció d'escriptura (0x01): atribut READ-WRITE o WRITE-ONLY

- OR acció de màscara (0x02): atribut READ-WRITE

- Acció de màscara AND (0x03): atribut READ-WRITE

La mida de la matriu "Estableix" ha d'estar entre 1 i 43, inclosos.

El camp "Tipus" ha d'estar entre 1 i 3, inclosos

4.5.1.4.2 Comandament

Taula 25. Valor de l'ordre WRITE_REGISTER_MULTIPLE Realitzeu una operació de registre d'escriptura mitjançant un conjunt de parells Registre-Valor.

| Camp de càrrega útil | Longitud | Valor/descripció | |||

| Estableix [1…n] | 6 bytes | Adreça de registre | 1 byte | Adreça lògica del registre. | |

| Tipus | 1 byte | 0 x 1 | Escriure Registre | ||

| 0 x 2 | Escriviu Registre O Mascareta | ||||

| 0 x 3 | Escriviu Registre I Mascareta | ||||

| Valor | 4 bytes | 32 Valor del registre de mossegada que s'ha d'escriure, o màscara de bits utilitzada per a l'operació lògica. (Little-endian) | |||

Nota: En cas d'excepció, l'operació no es reverteix, és a dir, els registres que s'han modificat fins que es produeixi una excepció romanen en estat modificat. L'amfitrió ha de prendre les accions adequades per recuperar-se a un estat definit.

4.5.1.4.3 Resposta

Taula 26. Valor de resposta WRITE_REGISTER_MULTIPLE

| Camp de càrrega útil | Longitud | Valor/Descripció |

| Estat | 1 byte | Estat de l'operació [Taula 9]. Els valors esperats són els següents: |

| PN5190_STATUS_SUCCESS | ||

| PN5190_STATUS_INSTR_ERROR |

4.5.1.4.4 esdeveniment

No hi ha esdeveniments per a aquesta comanda.

4.5.1.5 READ_REGISTER

Aquesta instrucció s'utilitza per llegir el contingut d'un registre lògic. El contingut està present a la resposta, com a valor de 4 bytes en format little-endian.

4.5.1.5.1 Condicions

L'adreça del registre lògic ha d'existir. L'atribut d'accés del registre ha de ser READ-WRITE o READ-ONLY.

4.5.1.5.2 Comandament

Taula 27. Valor de l'ordre READ_REGISTER

Tornar a llegir el contingut d'un registre.

| Camp de càrrega útil | Longitud | Valor/Descripció |

| Adreça de registre | 1 byte | Adreça del registre lògic |

4.5.1.5.3 Resposta

Taula 28. Valor de resposta READ_REGISTER

| Camp de càrrega útil | Longitud | Valor/Descripció |

| Estat | 1 byte | Estat de l'operació [Taula 9]. Els valors esperats són els següents: |

| PN5190_STATUS_SUCCESS PN5190_STATUS_INSTR_ERROR (No hi ha més dades) | ||

| Valor de registre | 4 bytes | Valor de registre de 32 bits que s'ha llegit. (Little-endian) |

4.5.1.5.4 esdeveniment

No hi ha esdeveniments per a aquesta comanda.

4.5.1.6 READ_REGISTER_MULTIPLE

Aquesta instrucció s'utilitza per llegir diversos registres lògics alhora. El resultat (contingut de cada registre) es proporciona a la resposta a la instrucció. La pròpia adreça de registre no s'inclou a la resposta. L'ordre dels continguts del registre dins de la resposta correspon a l'ordre de les adreces del registre dins de la instrucció.

4.5.1.6.1 Condicions

Totes les adreces de registre de la instrucció han d'existir. L'atribut d'accés per a cada registre ha de ser READ-WRITE o READ-ONLY. La mida de la matriu "Adreça de registre" ha d'estar entre 1 i 18, inclosos.

4.5.1.6.2 Comandament

Taula 29. Valor de l'ordre READ_REGISTER_MULTIPLE Realitzeu una operació de lectura de registre en un conjunt de registres.

| Camp de càrrega útil | Longitud | Valor/Descripció |

| Adreça de registre[1…n] | 1 byte | Adreça de registre |

4.5.1.6.3 Resposta

Taula 30. Valor de resposta READ_REGISTER_MULTIPLE

| Camp de càrrega útil | Longitud | Valor/descripció | ||

| Estat | 1 byte | Estat de l'operació [Taula 9]. Els valors esperats són els següents: | ||

| PN5190_STATUS_SUCCESS PN5190_STATUS_INSTR_ERROR (No hi ha més dades) | ||||

| Valor de registre [1…n] | 4 bytes | Valor | 4 bytes | Valor del registre de 32 bits que s'ha llegit (little-endian). |

4.5.1.6.4 esdeveniment

No hi ha esdeveniments per a aquesta comanda.

4.5.2 Manipulació d'E2PROM

L'àrea accessible a E2PROM és segons el mapa EEPROM i la mida adreçable.

Nota:

1. Sempre que s'esmenti l'"E2PROM Address" a les instruccions següents, es refereix a la mida de l'àrea EEPROM adreçable.

4.5.2.1 WRITE_E2PROM

Aquesta instrucció s'utilitza per escriure un o més valors a E2PROM. El camp "Valors" conté les dades que s'han d'escriure a l'E2PROM a partir de l'adreça donada pel camp "E2PROM Address". Les dades s'escriuen en ordre seqüencial.

Nota:

Tingueu en compte que aquesta és una ordre de bloqueig, això significa que l'NFC FE està bloquejat durant l'operació d'escriptura. Això pot trigar uns quants mil·lisegons.

4.5.2.1.1 Condicions

El camp "E2PROM Address" ha d'estar dins l'interval segons [2]. El nombre de bytes dins del camp "Valors" ha d'estar entre 1 i 1024 (0x0400), inclosos. L'operació d'escriptura no ha d'anar més enllà de l'adreça EEPROM tal com s'esmenta a [2]. La resposta d'error s'enviarà a l'amfitrió si l'adreça supera l'espai d'adreces EEPROM com a [2].

4.5.2.1.2 Comandament

Taula 31. Valor de l'ordre WRITE_E2PROM Escriu els valors donats seqüencialment a E2PROM.

| Camp de càrrega útil | Longitud | Valor/descripció |

| Adreça E2PROM | 2 byte | Adreça a l'EEPROM des de la qual començarà l'operació d'escriptura. (Little-endià) |

| Valors | 1 – 1024 bytes | Valors que s'han d'escriure a E2PROM en ordre seqüencial. |

4.5.2.1.3 Resposta

Taula 32. Valor de resposta WRITE_EEPROM

| Camp de càrrega útil | Longitud | Valor/Descripció |

| Estat | 1 byte | Estat de l'operació [Taula 9]. Els valors esperats són els següents: |

| PN5190_STATUS_SUCCESS PN5190_STATUS_INSTR_ERROR PN5190_STATUS_MEMORY_ERROR |

4.5.2.1.4 esdeveniment

No hi ha esdeveniments per a aquesta comanda.

4.5.2.2 READ_E2PROM

Aquesta instrucció s'utilitza per llegir dades de l'àrea de memòria E2PROM. El camp 'E2PROM Address' indica l'adreça inicial de l'operació de lectura. La resposta conté les dades llegides des de l'E2PROM.

4.5.2.2.1 Condicions

El camp "E2PROM Address" ha d'estar en un interval vàlid.

El camp "Nombre de bytes" ha d'estar entre 1 i 256, inclosos.

L'operació de lectura no ha d'anar més enllà de l'última adreça EEPROM accessible.

La resposta d'error s'enviarà a l'amfitrió si l'adreça supera l'espai d'adreces EEPROM.

4.5.2.2.2 Comandament

Taula 33. Valor de l'ordre READ_E2PROM Llegeix els valors de l'E2PROM de manera seqüencial.

| Camp de càrrega útil | Longitud | Valor/descripció |

| Adreça E2PROM | 2 byte | Adreça a E2PROM des de la qual s'iniciarà l'operació de lectura. (Little-endià) |

| Nombre de bytes | 2 byte | Nombre de bytes a llegir. (Little-endian) |

4.5.2.2.3 Resposta

Taula 34. Valor de resposta READ_E2PROM

| Camp de càrrega útil | Longitud | Valor/Descripció |

| Estat | 1 byte | Estat de l'operació [Taula 9]. Els valors esperats són els següents: |

| PN5190_STATUS_SUCCESS | ||

| PN5190_STATUS_INSTR_ERROR (No hi ha més dades) | ||

| Valors | 1 – 1024 bytes | Valors que s'han llegit en ordre seqüencial. |

4.5.2.2.4 esdeveniment

No hi ha esdeveniments per a aquesta comanda.

4.5.2.3 GET_CRC_USER_AREA

Aquesta instrucció s'utilitza per calcular el CRC per a l'àrea completa de configuració de l'usuari inclosa l'àrea de protocol de PN5190 IC.

4.5.2.3.1 Comandament

Taula 35. Valor de l'ordre GET_CRC_USER_AREA

Llegiu el CRC de l'àrea de configuració de l'usuari inclosa l'àrea de protocol.

| Camp de càrrega útil | Longitud | Valor/Descripció |

| – | – | No hi ha dades a la càrrega útil |

4.5.2.3.2 Resposta

Taula 36. Valor de resposta GET_CRC_USER_AREA

| Camp de càrrega útil | Longitud | Valor/descripció |

| Estat | 1 byte | Estat de l'operació [Taula 9]. Els valors esperats són els següents: |

| PN5190_STATUS_SUCCESS | ||

| PN5190_STATUS_INSTR_ERROR (No hi ha més dades) | ||

| Valors | 4 bytes | 4 bytes de dades CRC en format little-endian. |

4.5.2.3.3 esdeveniment

No hi ha esdeveniments per a aquesta comanda.

4.5.3 Manipulació de dades CLIF

Les instruccions descrites en aquesta secció descriuen les ordres per a la transmissió i recepció de RF.

4.5.3.1 INTERCANVI_DADES_RF

La funció d'intercanvi de RF realitza una transmissió de les dades de TX i està esperant la recepció de qualsevol dada de RX.

La funció torna en cas d'una recepció (ja sigui errònia o correcta) o en cas d'esperar. El temporitzador s'inicia amb el FINAL DE LA TRANSMISSIÓ i s'atura amb l'INICIACIÓ de la RECEPCIÓ. El valor del temps d'espera preconfigurat a l'EEPROM s'utilitzarà en cas que el temps d'espera no s'hagi configurat abans de l'execució de l'ordre Exchange.

Si transceiver_state és

- en IDLE s'entra en el mode TRANSCEPTOR.

- A WAIT_RECEIVE, l'estat del transceptor es restableix al MODE TRANSCEPCIÓ en cas que s'estableixi el bit d'iniciador

- A WAIT_TRANSMIT, l'estat del transceptor es restableix a MODE TRANSCEPCIÓ en cas que el bit iniciador NO s'estableixi

El camp 'Nombre de bits vàlids en l'últim byte' indica la longitud exacta de les dades que s'han de transmetre.

4.5.3.1.1 Condicions

La mida del camp "TX Data" ha d'estar entre 0 i 1024, inclosos.

El camp "Nombre de bits vàlids a l'últim byte" ha d'estar entre 0 i 7.

L'ordre no s'ha de cridar durant una transmissió de RF en curs. El comandament ha de garantir l'estat correcte del transceptor per transmetre les dades.

Nota:

Aquesta ordre només és vàlida per al mode Lector i el mode d'iniciador passiu/actiu P2P.

4.5.3.1.2 Comandament

Taula 37. Valor de l'ordre EXCHANGE_RF_DATA

Escriu les dades de TX a la memòria intermèdia de transmissió de RF i comença la transmissió mitjançant l'ordre de transmissió i espera fins a la recepció o el temps d'espera per preparar una resposta a l'amfitrió.

| Camp de càrrega útil | Longitud | Valor/Descripció | |

| Nombre de bits vàlids a l'últim byte | 1 byte | 0 | Es transmeten tots els bits de l'últim byte |

| 1 – 7 | Nombre de bits dins de l'últim byte a transmetre. | ||

| RFExchangeConfig | 1 byte | Configuració de la funció RFExchange. Els detalls vegeu a continuació | |

Taula 37. Valor de l'ordre EXCHANGE_RF_DATA...continuació

Escriu les dades de TX a la memòria intermèdia de transmissió de RF i comença la transmissió mitjançant l'ordre de transmissió i espera fins a la recepció o el temps d'espera per preparar una resposta a l'amfitrió.

| Camp de càrrega útil | Longitud | Valor/Descripció |

| Dades TX | n bytes | Dades TX que s'han d'enviar mitjançant CLIF mitjançant l'ordre de transmissió. n = 0 – 1024 bytes |

Taula 38. Màscara de bits RFexchangeConfig

| b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 | Descripció |

| Els bits 4-7 són RFU | ||||||||

| X | Incloeu les dades RX com a resposta basada en RX_STATUS, si el bit s'estableix a 1b. | |||||||

| X | Inclou el registre EVENT_STATUS com a resposta, si el bit s'estableix a 1b. | |||||||

| X | Incloeu el registre RX_STATUS_ERROR en resposta, si el bit està establert a 1b. | |||||||

| X | Inclou el registre RX_STATUS com a resposta, si el bit està establert a 1b. |

4.5.3.1.3 Resposta

Taula 39. Valor de resposta EXCHANGE_RF_DATA

| Camp de càrrega útil | Longitud | Valor/Descripció |

| Estat | 1 byte | Estat de l'operació [Taula 9]. Els valors esperats són els següents: |

| PN5190_STATUS_INSTR_SUCCESS PN5190_STATUS_INSTR_ERROR (No hi ha més dades) PN5190_STATUS_TIMEOUT PN5190_STATUS_RX_TIMEOUT PN5190_STATUS_NO_RF_FIELD PN5190_STATUS_TIMEOUT_WITH_EMD_ERROR |

||

| RX_STATUS | 4 bytes | Si es demana RX_STATUS (little-endian) |

| RX_STATUS_ERROR | 4 bytes | Si es demana RX_STATUS_ERROR (little-endian) |

| EVENT_STATUS | 4 bytes | Si es demana EVENT_STATUS (little-endian) |

| Dades RX | 1 – 1024 bytes | Si es demanen dades de RX. Dades RX rebudes durant la fase de recepció de RF de l'intercanvi de RF. |

4.5.3.1.4 esdeveniment

No hi ha esdeveniments per a aquesta comanda.

4.5.3.2 TRANSMIT_DADES_RF

Aquesta instrucció s'utilitza per escriure dades al buffer de transmissió CLIF intern i iniciar la transmissió mitjançant l'ordre transceive internament. La mida d'aquest buffer està limitada a 1024 bytes. Després d'executar aquesta instrucció, s'inicia automàticament una recepció de RF.

L'ordre torna immediatament després que la transmissió s'hagi completat sense esperar que finalitzi la recepció.

4.5.3.2.1 Condicions

El nombre de bytes dins del camp "TX Data" ha d'estar entre 1 i 1024, inclosos.

L'ordre no s'ha de cridar durant una transmissió de RF en curs.

4.5.3.2.2 Comandament

Taula 40. Valor de l'ordre TRANSMIT_RF_DATA Escriu dades TX a la memòria intermèdia de transmissió CLIF interna.

| Camp de càrrega útil | Longitud | Valor/Descripció |

| Nombre de bits vàlids a l'últim byte | 1 byte | 0 Es transmeten tots els bits de l'últim byte 1 – 7 Nombre de bits de l'últim byte a transmetre. |

| RFU | 1 byte | Reservat |

| Dades TX | 1 – 1024 bytes | Dades TX que s'utilitzaran durant la propera transmissió de RF. |

4.5.3.2.3 Resposta

Taula 41. Valor de resposta TRANSMIT_RF_DATA

| Camp de càrrega útil | Longitud | Valor/Descripció |

| Estat | 1 byte | Estat de l'operació [Taula 9]. Els valors esperats són els següents: |

| PN5190_STATUS_INSTR_SUCCESS PN5190_STATUS_INSTR_ERROR PN5190_STATUS_NO_RF_FIELD PN5190_STATUS_NO_EXTERNAL_RF_FIELD |

4.5.3.2.4 esdeveniment

No hi ha esdeveniments per a aquesta comanda.

4.5.3.3 RECUPERAR_DADES_RF

Aquesta instrucció s'utilitza per llegir dades de la memòria intermèdia CLIF RX interna, que conté les dades de resposta de RF (si n'hi ha) que s'hi han publicat des de l'execució anterior de la secció 4.5.3.1 amb l'opció de no incloure les dades rebudes a la resposta o a la secció 4.5.3.2. .XNUMX comandament.

4.5.3.3.1 Comandament

Taula 42. Valor de l'ordre RETRIEVE_RF_DATA Llegiu les dades de RX del buffer de recepció de RF intern.

| Camp de càrrega útil | Longitud | Valor/Descripció |

| Buit | Buit | Buit |

4.5.3.3.2 Resposta

Taula 43. Valor de resposta RETRIEVE_RF_DATA

| Camp de càrrega útil | Longitud | Valor/Descripció |

| Estat | 1 byte | Estat de l'operació [Taula 9]. Els valors esperats són els següents: |

| Camp de càrrega útil | Longitud | Valor/Descripció |

| PN5190_STATUS_INSTR_SUCCESS PN5190_STATUS_INSTR_ERROR (No hi ha més dades) |

||

| Dades RX | 1 – 1024 bytes | Dades de RX que s'han rebut durant la darrera recepció de RF amb èxit. |

4.5.3.3.3 esdeveniment

No hi ha esdeveniments per a aquesta comanda.

4.5.3.4 RECEIVE_RF_DATA

Aquesta instrucció espera les dades rebudes a través de la interfície RF del lector.

En el mode de lector, aquesta instrucció torna si hi ha una recepció (ja sigui errònia o correcta) o si s'ha produït un temps d'espera FWT. El temporitzador s'inicia amb el FINAL DE LA TRANSMISSIÓ i s'atura amb l'INICIACIÓ de la RECEPCIÓ. El valor de temps d'espera per defecte preconfigurat a l'EEPROM s'utilitzarà en cas que el temps d'espera no estigui configurat abans de l'execució de l'ordre d'Exchange.

En el mode objectiu, aquesta instrucció retorna en cas de recepció (ja sigui errònia o correcta) o en cas d'error de RF extern.

Nota:

Aquesta instrucció s'utilitzarà amb l'ordre TRANSMIT_RF_DATA per realitzar operacions TX i RX...

4.5.3.4.1 Comandament

Taula 44. Valor de l'ordre RECEIVE_RF_DATA

| Camp de càrrega útil | Longitud | Valor/Descripció |

| ReceiveRFConfig | 1 byte | Configuració de la funció ReceiveRFConfig. Mireu Taula 45 |

Taula 45. Màscara de bits ReceiveRFConfig

| b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 | Descripció |

| Els bits 4-7 són RFU | ||||||||

| X | Incloeu les dades RX com a resposta basada en RX_STATUS, si el bit s'estableix a 1b. | |||||||

| X | Inclou el registre EVENT_STATUS com a resposta, si el bit s'estableix a 1b. | |||||||

| X | Incloeu el registre RX_STATUS_ERROR en resposta, si el bit està establert a 1b. | |||||||

| X | Inclou el registre RX_STATUS com a resposta, si el bit està establert a 1b. |

4.5.3.4.2 Resposta

Taula 46. Valor de resposta RECEIVE_RF_DATA

| Camp de càrrega útil | Longitud | Valor/descripció |

| Estat | 1 byte | Estat de l'operació [Taula 9]. Els valors esperats són els següents: |

| PN5190_STATUS_INSTR_SUCCESS PN5190_STATUS_INSTR_ERROR (No hi ha més dades) PN5190_STATUS_TIMEOUT |

| Camp de càrrega útil | Longitud | Valor/descripció |

| PN5190_STATUS_NO_RF_FIELD PN5190_STATUS_NO_EXTERNAL_RF_FIELD |

||

| RX_STATUS | 4 bytes | Si es demana RX_STATUS (little-endian) |

| RX_STATUS_ERROR | 4 bytes | Si es demana RX_STATUS_ERROR (little-endian) |

| EVENT_STATUS | 4 bytes | Si es demana EVENT_STATUS (little-endian) |

| Dades RX | 1 – 1024 bytes | Si es demanen dades de RX. Dades RX rebudes per RF. |

4.5.3.4.3 esdeveniment

No hi ha esdeveniments per a aquesta comanda.

4.5.3.5 RETRIEVE_RF_FELICA_EMD_DATA (Configuració de FeliCa EMD)

Aquesta instrucció s'utilitza per llegir dades de la memòria intermèdia CLIF RX interna, que conté les dades de resposta de FeliCa EMD (si n'hi ha) enviades des de l'execució anterior de l'ordre EXCHANGE_RF_DATA que torna amb l'estat 'PN5190_STATUS_TIMEOUT_WITH_EMD_ERROR'.

Nota: Aquesta ordre està disponible a partir de PN5190 FW v02.03.

4.5.3.5.1 Comandament

Llegiu les dades de RX del buffer intern de recepció de RF.

Taula 47. Valor de l'ordre RETRIEVE_RF_FELICA_EMD_DATA

| Camp de càrrega útil | Longitud | Valor/Descripció | |

| FeliCaRFRetrieveConfig | 1 byte | 00 – FF | Configuració de la funció RETRIEVE_RF_FELICA_EMD_DATA |

| descripció de la configuració (màscara de bits). | bit 7..2: RFU bit 1: inclou el registre RX_STATUS_ ERROR en resposta, si el bit està establert a 1b. bit 0: inclou el registre RX_STATUS en resposta, si el bit està establert a 1b. |

||

4.5.3.5.2 Resposta

Taula 48. Valor de resposta RETRIEVE_RF_FELICA_EMD_DATA

| Camp de càrrega útil | Longitud | Valor/descripció | |||

| Estat | 1 byte | Estat de l'operació. Els valors esperats són els següents: PN5190_STATUS_INSTR_SUCCESS PN5190_STATUS_INSTR_ERROR (No hi ha més dades) | |||

| RX_STATUS | 4 byte | Si es demana RX_STATUS (little-endian) | |||

| RX_STATUS_ ERROR | 4 byte | Si es demana RX_STATUS_ERROR (little-endian) | |||

| Camp de càrrega útil | Longitud | Valor/descripció | |||

| Dades RX | 1…1024 bytes | Dades de FeliCa EMD RX que s'han rebut durant la darrera recepció de RF sense èxit mitjançant Exchange Command. | |||

4.5.3.5.3 esdeveniment

No hi ha esdeveniments per a aquesta comanda.

4.5.4 Canvi de mode d'operació

El PN5190 admet 4 modes de funcionament diferents:

4.5.4.1 Normal

Aquest és el mode predeterminat, on es permeten totes les instruccions.

4.5.4.2 En espera

El PN5190 està en estat d'espera/repòs per estalviar energia. Les condicions d'activació s'han d'establir per definir quan tornar a sortir del mode d'espera.

4.5.4.3 LPCD

El PN5190 es troba en mode de detecció de targetes de baix consum, on intenta detectar una targeta que està entrant al volum d'operació, amb el menor consum d'energia possible.

4.5.4.4 Autocoll

PN5190 actua com a oient de RF, realitzant l'activació del mode objectiu de manera autònoma (per garantir les limitacions en temps real)

4.5.4.5 SWITCH_MODE_NORMAL

L'ordre Switch Mode Normal té tres casos d'ús.

4.5.4.5.1 UseCase1: introduïu el mode de funcionament normal quan s'engega (POR)

Utilitzeu-lo per restablir a l'estat inactiu per rebre/processar la següent ordre entrant al mode de funcionament normal.

4.5.4.5.2 UseCase2: s'està acabant l'ordre que ja s'està executant per canviar al mode de funcionament normal (ordre avortada)

Utilitzeu-lo per restablir a l'estat inactiu per rebre/processar la següent ordre acabant amb les ordres que ja s'executen.

Les ordres com ara standby, LPCD, Exchange, PRBS i Autocoll es podran finalitzar mitjançant aquesta ordre.

Aquesta és l'única comanda especial, que no té resposta. En comptes d'això, té una notificació d'ESDEVENIMENT.

Consulteu la secció 4.4.3 per obtenir més informació sobre el tipus d'esdeveniments que es produeixen durant l'execució d'ordres subjacents diferents.

4.5.4.5.2.1 Cas d'ús 2.1:

Aquesta ordre restablirà tots els registres CLIF TX, RX i de control de camp a l'estat d'arrencada. L'emissió d'aquesta ordre desactivarà qualsevol camp de RF existent.

4.5.4.5.2.2 Cas d'ús 2.2:

Disponible a partir de PN5190 FW v02.03:

Aquesta ordre no modificarà els registres CLIF TX, RX i control de camp, sinó que només mourà el transceptor a l'estat IDLE.

4.5.4.5.3 UseCase3: Mode d'operació normal en reiniciar/sortir del mode d'espera, LPCD En aquest cas, el PN5190 entra directament en el mode de funcionament normal, enviant IDLE_EVENT a l'amfitrió (Figura 12 o Figura 13) i “ El bit IDLE_EVENT s'estableix a la taula 11.

No hi ha cap requisit per enviar l'ordre SWITCH_MODE_NORMAL.

Nota:

Després de canviar l'IC al mode normal, tots els paràmetres de RF es modifiquen a l'estat predeterminat. És imprescindible que la configuració de RF respectiva i altres registres relacionats s'hagin de carregar amb els valors adequats abans de realitzar una operació RF ON o RF Exchange.

4.5.4.5.4 Marc d'ordres per enviar per a diferents casos d'ús

4.5.4.5.4.1 UseCase1: l'ordre entra al mode de funcionament normal quan s'engega (POR) 0x20 0x01 0x00

4.5.4.5.4.2 UseCase2: ordre per finalitzar les ordres que ja s'executen per canviar al mode de funcionament normal

Cas d'ús 2.1:

0x20 0x00 0x00

Cas d'ús 2.2: (a partir de FW v02.02):

0x20 0x02 0x00

4.5.4.5.4.3 UseCase3: ordre per al mode de funcionament normal quan es reinicia/sorteix del mode d'espera, LPCD, ULPCD

Cap. PN5190 entra directament al mode de funcionament normal.

4.5.4.5.5 Resposta

Cap

4.5.4.5.6 esdeveniment

S'estableix un BOOT_EVENT (al registre EVENT_STATUS) que indica que s'ha introduït el mode normal i s'envia a l'amfitrió. Consulteu la figura 12 i la figura 13 per obtenir les dades de l'esdeveniment.

S'estableix un IDLE_EVENT (al registre EVENT_STATUS) que indica que s'ha introduït el mode normal i s'envia a l'amfitrió. Consulteu la figura 12 i la figura 13 per obtenir les dades de l'esdeveniment.

S'estableix un BOOT_EVENT (al registre EVENT_STATUS) que indica que s'ha introduït el mode normal i s'envia a l'amfitrió. Consulteu la figura 12 i la figura 13 per obtenir les dades de l'esdeveniment.

4.5.4.6 SWITCH_MODE_AUTOCOLL

El mode de commutació automàtica realitza automàticament el procediment d'activació de la targeta en mode objectiu.

El camp "Mode de col·lecció automàtica" ha d'estar en el rang de 0 a 2, inclosos.

En cas que el camp "Mode Autocoll" estigui definit en 2 (Autocoll): el camp "RF Technologies" (Taula 50) ha de contenir una màscara de bits que indiqui les tecnologies de RF que s'admeten durant l'Autocoll.

No s'han d'enviar instruccions mentre estigui en aquest mode.

La terminació s'indica mitjançant una interrupció.

4.5.4.6.1 Comandament

Taula 49. Valor de l'ordre SWITCH_MODE_AUTOCOLL

| Paràmetre | Longitud | Valor/Descripció | |

| Tecnologies de RF | 1 byte | Màscara de bits que indica la tecnologia de RF que cal escoltar durant Autocoll. | |

| Mode Autocoll | 1 byte | 0 | Sense mode autònom, és a dir, Autocoll finalitza quan no hi ha camp de RF extern. |

| Terminació en cas de | |||

| • NO RF FIELD o RF FIELD ha desaparegut | |||

| • PN5190 està ACTIVAT en mode TARGET | |||

| 1 | Mode autònom amb espera. Quan no hi ha cap camp de RF, Autocoll entra automàticament en mode d'espera. Un cop detectat el camp RF extern de RF, el PN5190 torna a entrar en mode Autocoll. | ||

| Terminació en cas de | |||

| • PN5190 està ACTIVAT en mode TARGET | |||

| Des de PN5190 FW v02.03 en endavant: si el camp EEPROM "bCard ModeUltraLowPowerEnabled" a l'adreça "0xCDF" està establert a "1", aleshores el PN5190 entra en espera d'ultra baixa potència. | |||

| 2 | Mode autònom sense espera. Quan no hi ha cap camp de RF, el PN5190 espera fins que hi hagi un camp de RF abans d'iniciar l'algorisme Autocoll. En aquest cas, no s'utilitza el mode d'espera. | ||

| Terminació en cas de • PN5190 està ACTIVAT en mode TARGET |

|||

Taula 50. Màscara de bits de tecnologies RF

| b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 | Descripció |

| 0 | 0 | 0 | 0 | RFU | ||||

| X | Si s'estableix a 1b, s'habilita l'escolta de NFC-F Active. (No disponible). | |||||||

| X | Si s'estableix a 1b, s'habilita l'escolta de NFC-A Active. (No disponible). | |||||||

| X | Si s'estableix a 1b, s'habilita l'escolta de NFC-F. | |||||||

| X | Si s'estableix a 1b, s'habilita l'escolta de NFC-A. |

4.5.4.6.2 Resposta

La resposta només indica que l'ordre s'ha processat.

Taula 51. Valor de resposta SWITCH_MODE_AUTOCOLL

| Camp de càrrega útil | Longitud | Valor/Descripció |

| Estat | 1 byte | Estat de l'operació [Taula 9]. Els valors esperats són els següents: |

| PN5190_STATUS_INSTR_SUCCESS PN5190_STATUS_INSTR_ERROR (No s'ha introduït el mode de canvi a causa d'una configuració incorrecta) |

4.5.4.6.3 esdeveniment

La notificació d'esdeveniment s'envia quan s'ha acabat l'ordre i s'introdueix el mode normal. L'amfitrió ha de llegir els bytes de resposta en funció del valor de l'esdeveniment.

Nota:

Quan l'estat no és "PN5190_STATUS_INSTR_SUCCESS", no hi ha més bytes de dades "Protocol" i "Card_Activated".

La informació tecnològica es recupera dels registres mitjançant les ordres de la Secció 4.5.1.5, Secció 4.5.1.6.

La taula següent mostra les dades d'esdeveniment que s'envien com a part del missatge d'esdeveniment Figura 12 i Figura 13.

Taula 52. EVENT_SWITCH_MODE_AUTOCOLL – Dades AUTOCOLL_EVENT Canvia el mode d'operació Esdeveniment Autocoll

| Camp de càrrega útil | Longitud | Valor/Descripció | |

| Estat | 1 byte | Estat de l'operació | |

| PN5190_STATUS_INSTR_SUCCESS | PN5190 està ACTIVAT en mode TARGET. Més dades d'aquest esdeveniment són vàlides. |

||

| PN5190_STATUS_PREVENT_STANDBY | Indica que PN5190 no pot entrar en mode d'espera. Aquest estat només és vàlid quan el mode Autocoll està seleccionat com a "Mode autònom amb espera". | ||

| PN5190_STATUS_NO_EXTERNAL_RF_ CAMP | Indica que no hi ha cap camp de RF extern durant l'execució d'Autocoll en mode no autònom | ||

| PN5190_STATUS_USER_CANCELLED | Indica que l'ordre actual en curs s'avorta per l'ordre normal de canvi de mode | ||

| Protocol | 1 byte | 0 x 10 | Activat com a tipus passiu A |

| 0 x 11 | Activat com a tipus passiu F 212 | ||

| 0 x 12 | Activat com a tipus passiu F 424 | ||

| 0 x 20 | Activat com a tipus actiu A | ||

| 0 x 21 | Activat com a Active TypeF 212 | ||

| 0 x 22 | Activat com a Active TypeF 424 | ||

| Altres valors | No vàlid | ||

| Targeta_Activada | 1 byte | 0 x 00 | No hi ha cap procés d'activació de la targeta segons ISO 14443-3 |

| 0 x 01 | Indica que el dispositiu està activat en mode passiu |

Nota: