UM11942

UM11942

Couche d'instructions PN5190

Contrôleur frontal NFC

Manuel d'utilisation

Contrôleur frontal NFC PN5190

Informations sur le document

| Information | Contenu |

| Mots clés | PN5190, NFC, interface NFC, contrôleur, couche d'instructions |

| Abstrait | Ce document décrit les commandes et les réponses de la couche d'instructions à exécuter à partir d'un contrôleur hôte, pour évaluer le fonctionnement du contrôleur frontal NFC NXP PN5190. PN5190 est un contrôleur frontal NFC de nouvelle génération. L'objectif de ce document est de décrire les commandes d'interface permettant de fonctionner avec le contrôleur frontal NFC PN5190. Pour plus d'informations sur le fonctionnement du contrôleur frontal NFC PN5190, reportez-vous à la fiche technique et à ses informations complémentaires. |

Historique des révisions

| Tour | Date | Description |

| 3.7 | 20230525 | • Le type et le titre du document ont été modifiés de l'addendum à la fiche technique du produit au manuel d'utilisation. • Nettoyage éditorial • Conditions éditoriales mises à jour pour les signaux SPI • Ajout de la commande GET_CRC_USER_AREA dans le tableau 8 de la section 4.5.2.3. • Mise à jour de divers détails différenciés pour PN5190B1 et PN5190B2 dans la section 3.4.1. • Réponse mise à jour de la section 3.4.7 |

| 3.6 | 20230111 | Description de la réponse de vérification améliorée de l'intégrité à la section 3.4.7 |

| 3.5 | 20221104 | Section 4.5.4.6.3 « Événement » : ajouté |

| 3.4 | 20220701 | • Ajout de la commande CONFIGURE_MULTIPLE_TESTBUS_DIGITAL dans le tableau 8 de la section 4.5.9.3. • Section 4.5.9.2.2 mise à jour |

| 3.3 | 20220329 | Description du matériel améliorée dans la section 4.5.12.2.1 « Commande » et la section 4.5.12.2.2 « Réponse » |

| 3.2 | 20210910 | Numéros de version du micrologiciel mis à jour de 2.1 à 2.01 et de 2.3 à 2.03 |

| 3.1 | 20210527 | Description de la commande RETRIEVE_RF_FELICA_EMD_DATA ajoutée |

| 3 | 20210118 | Première version officielle publiée |

Introduction

1.1 Introduction

Ce document décrit l'interface hôte PN5190 et les API. L'interface hôte physique utilisée dans la documentation est SPI. La caractéristique physique du SPI n’est pas prise en compte dans le document.

La séparation des trames et le contrôle de flux font partie de ce document.

1.1.1 Portée

Le document décrit la couche logique, le code d'instruction et les API pertinents pour le client.

Communication hôte terminéeview

Le PN5190 dispose de deux modes de fonctionnement principaux pour communiquer avec le contrôleur hôte.

- La communication basée sur HDLL est utilisée lorsque l'appareil est déclenché pour entrer :

un. Mode de téléchargement sécurisé crypté pour mettre à jour son firmware - Communication basée sur la commande-réponse TLV (donnée en example).

2.1 Mode HDLL

Le mode HDLL est utilisé pour le format d'échange de paquets afin de fonctionner avec les modes de fonctionnement IC ci-dessous :

- Mode de téléchargement sécurisé du micrologiciel (SFWU), voir section 3

2.1.1 Description des HDLL

HDLL est la couche de liaison développée par NXP pour garantir un téléchargement fiable du micrologiciel.

Un message HDLL est constitué d'un en-tête de 2 octets, suivi d'une trame, comprenant l'opcode et le Payload de la commande. Chaque message se termine par un CRC de 16 bits, comme décrit sur l'image ci-dessous : L'en-tête HDLL contient :

L'en-tête HDLL contient :

- Un peu un peu. Ce qui indique si ce message est le seul ou le dernier morceau d'un message (morceau = 0). Ou si, au moins, un autre morceau suit (morceau = 1).

- La longueur du Payload codé sur 10 bits. Ainsi, la charge utile de la trame HDLL peut aller jusqu'à 1023 XNUMX octets.

L'ordre des octets a été défini comme big-endian, ce qui signifie Ms Byte en premier.

Le CRC16 est conforme à la norme X.25 (CRC-CCITT, ISO/IEC13239) avec le polynôme x^16 + x^12 + x^5 +1 et la valeur de précharge 0xFFFF.

Il est calculé sur toute la trame HDLL, c'est-à-dire En-tête + Trame.

Sampl'implémentation du code C :

statique uint16_t phHal_Host_CalcCrc16(uint8_t* p, uint32_t dwLength)

{

uint32_t je ;

uint16_t crc_new ;

uint16_t crc = 0xffffU;

pour (I = 0; i < dwLength; i++)

{

crc_new = (uint8_t)(crc >> 8) | (crc << 8 );

crc_new ^= p[je];

crc_new ^= (uint8_t)(crc_new & 0xff) >> 4;

crc_nouveau ^= crc_nouveau << 12;

crc_new ^= (crc_new & 0xff) << 5;

crc = crc_nouveau;

}

retour crc ;

}

2.1.2 Mappage de transport sur le SPI

Pour chaque assertion NTS, le premier octet est toujours un HEADER (octet d'indication de flux), il peut être soit 0x7F/0xFF en ce qui concerne l'opération d'écriture/lecture.

2.1.2.1 Séquence d'écriture depuis l'hôte (sens DH => PN5190) 2.1.2.2 Séquence de lecture depuis l'hôte (Direction PN5190 => DH)

2.1.2.2 Séquence de lecture depuis l'hôte (Direction PN5190 => DH) 2.1.3 Protocole HDLL

2.1.3 Protocole HDLL

HDLL est un protocole commande-réponse. Toutes les opérations mentionnées ci-dessus sont déclenchées via une commande spécifique et validées en fonction de la réponse.

Les commandes et les réponses suivent la syntaxe des messages HDLL, la commande étant envoyée par l'hôte de l'appareil, la réponse par le PN5190. L'opcode indique la commande et le type de réponse.

Communications basées sur HDLL, utilisées uniquement lorsque le PN5190 est déclenché pour entrer en mode « Téléchargement sécurisé du firmware ».

2.2 Mode TLV

TLV signifie Tag Valeur de longueur.

2.2.1 Définition de la trame

Une trame SPI commence par le front descendant de NTS et se termine par le front montant de NTS. SPI est par définition physique full duplex mais le PN5190 utilise SPI en mode semi-duplex. Le mode SPI est limité à CPOL 0 et CPHA 0 avec une vitesse d'horloge maximale spécifiée dans [2]. Chaque trame SPI est composée d'un en-tête de 1 octet et de n octets de corps.

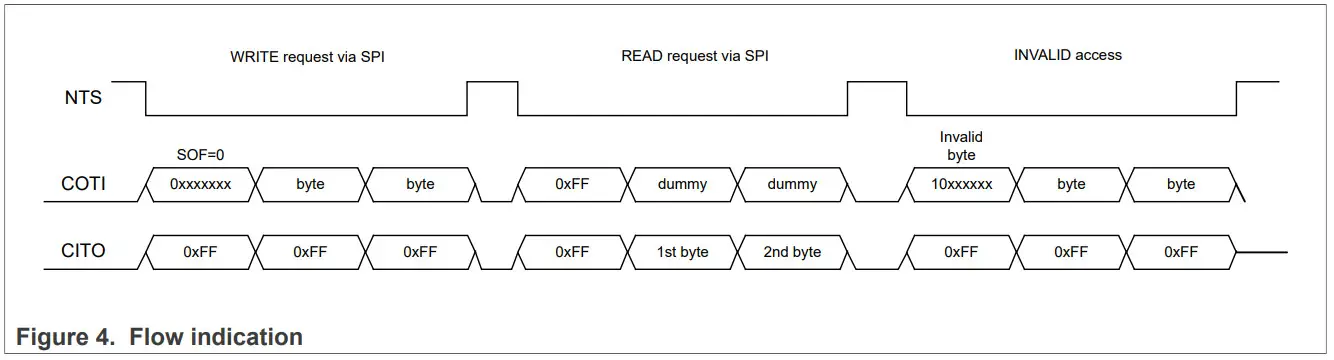

2.2.2 Indication du débit L'HOST envoie toujours comme premier octet l'octet d'indication de flux, s'il souhaite écrire ou lire des données depuis le PN5190.

L'HOST envoie toujours comme premier octet l'octet d'indication de flux, s'il souhaite écrire ou lire des données depuis le PN5190.

S'il y a une demande de lecture et qu'aucune donnée n'est disponible, la réponse contient 0xFF.

Les données après l'octet d'indication de flux sont un ou plusieurs messages.

Pour chaque assertion NTS, le premier octet est toujours un HEADER (octet d'indication de flux), il peut être soit 0x7F/0xFF en ce qui concerne l'opération d'écriture/lecture.

2.2.3 Type de message

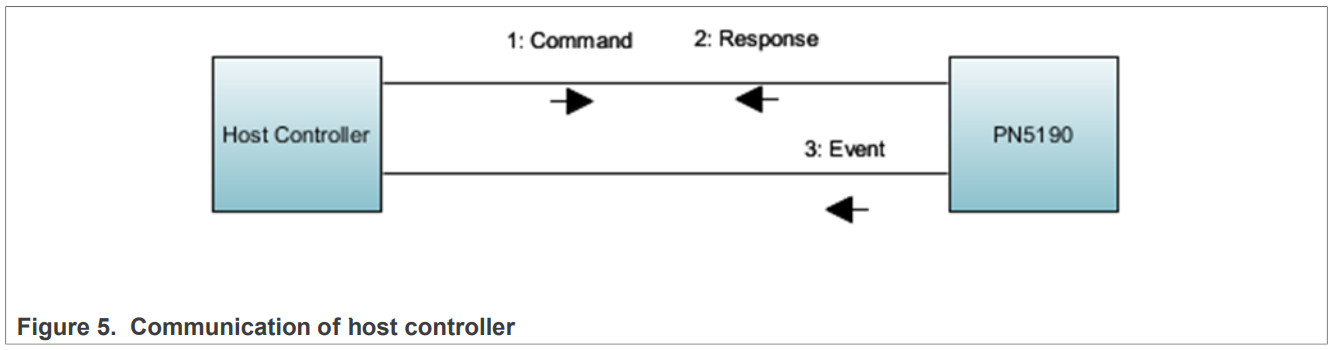

Un contrôleur hôte doit communiquer avec le PN5190 à l'aide de messages transportés dans les trames SPI.

Il existe trois types de messages différents :

- Commande

- Réponse

- Événement

Le diagramme de communication ci-dessus montre les directions autorisées pour les différents types de messages comme ci-dessous :

Le diagramme de communication ci-dessus montre les directions autorisées pour les différents types de messages comme ci-dessous :

- Commandement et réponse.

- Les commandes sont uniquement envoyées du contrôleur hôte au PN5190.

- Les réponses et les événements sont uniquement envoyés du PN5190 au contrôleur hôte.

- Les réponses aux commandes sont synchronisées à l'aide de la broche IRQ.

- L'hôte ne peut envoyer les commandes que lorsque l'IRQ est faible.

- L'hôte peut lire la réponse/l'événement uniquement lorsque l'IRQ est élevée.

2.2.3.1 Séquences et règles autorisées Séquences autorisées de commande, de réponse et d'événements

Séquences autorisées de commande, de réponse et d'événements

- Une commande est toujours reconnue par une réponse, ou un événement, ou les deux.

- Le contrôleur hôte n'est pas autorisé à envoyer une autre commande avant d'avoir reçu une réponse à la commande précédente.

- Les événements peuvent être envoyés de manière asynchrone à tout moment (PAS entrelacés dans une paire commande/réponse).

- Les messages EVENT ne sont jamais combinés avec les messages RESPONSE dans une même trame.

Note: La disponibilité d'un message (soit RESPONSE, soit EVENT) est signalée par l'IRQ allant de haut en bas. L'IRQ reste élevé jusqu'à ce que toute la réponse ou la trame d'événement soit lue. Ce n'est qu'une fois le signal IRQ faible que l'hôte peut envoyer la commande suivante.

2.2.4 Format des messages

Chaque message est codé dans une structure TLV avec une charge utile de n octets pour chaque message, à l'exception de la commande SWITCH_MODE_NORMAL. Chaque TLV est composé de :

Chaque TLV est composé de : Type (T) => 1 octet

Type (T) => 1 octet

Bit[7] Type de message

0: Message de COMMANDE ou de RÉPONSE

1: Message d'ÉVÉNEMENT

Bit[6:0] : code instruction

Longueur (L) => 2 octets (doit être au format big-endian)

Valeur (V) => N octets de valeur/données du TLV (Paramètres de commande / Données de réponse) basés sur le champ Longueur (format big-endian)

2.2.4.1 Trame divisée

Le message COMMAND doit être envoyé dans une seule trame SPI.

Les messages RESPONSE et EVENT peuvent être lus dans plusieurs trames SPI, par exemple pour lire la longueur en octets. Les messages RESPONSE ou EVENT peuvent être lus dans une seule trame SPI mais retardés par NO-CLOCK entre les deux, par exemple pour lire la longueur de l'octet.

Les messages RESPONSE ou EVENT peuvent être lus dans une seule trame SPI mais retardés par NO-CLOCK entre les deux, par exemple pour lire la longueur de l'octet.

Mode de démarrage opérationnel IC – mode de téléchargement sécurisé du micrologiciel

3.1 Introduction

Une partie du code du firmware PN5190 est stockée en permanence dans la ROM, tandis que le reste du code et les données sont stockés dans la mémoire flash intégrée. Les données utilisateur sont stockées en flash et sont protégées par des mécanismes anti-déchirure qui garantissent l'intégrité et la disponibilité des données. Afin de fournir aux clients de NXP des fonctionnalités conformes aux dernières normes (EMVCo, NFC Forum, etc.), le code et les données utilisateur en FLASH peuvent être mis à jour.

L'authenticité et l'intégrité du micrologiciel crypté sont protégées par une signature de clé asymétrique/symétrique et un mécanisme de hachage à chaîne inversée. La première commande DL_SEC_WRITE contient le hachage de la deuxième commande et est protégée par une signature RSA sur la charge utile de la première trame. Le micrologiciel PN5190 utilise la clé publique RSA pour authentifier la première commande. Le hachage chaîné de chaque commande est utilisé pour authentifier la commande suivante, afin de garantir que le code et les données du micrologiciel ne soient pas accessibles à des tiers.

Les charges utiles des commandes DL_SEC_WRITE sont chiffrées avec une clé AES-128. Après l'authentification de chaque commande, le contenu de la charge utile est déchiffré et écrit sur flash par le micrologiciel PN5190.

Pour le micrologiciel NXP, NXP est chargé de fournir de nouvelles mises à jour sécurisées du micrologiciel, ainsi que les nouvelles données utilisateur.

La procédure de mise à jour est équipée d'un mécanisme pour protéger l'authenticité, l'intégrité et la confidentialité du code et des données NXP.

Le schéma de paquets de trames basé sur HDLL est utilisé pour toutes les commandes et réponses pour le mode de mise à niveau sécurisée du micrologiciel.

La section 2.1 fournit plus deview du schéma de paquets de trames HDLL utilisé.

Les circuits intégrés PN5190 prennent en charge à la fois le téléchargement de micrologiciel sécurisé chiffré existant et le protocole de téléchargement de micrologiciel sécurisé chiffré assisté par chiffrement matériel, en fonction de la variante utilisée.

Les deux types sont :

- Protocole de téléchargement de micrologiciel sécurisé hérité qui fonctionne uniquement avec la version IC PN5190 B0/B1.

- Protocole de téléchargement de micrologiciel sécurisé assisté par chiffrement matériel qui fonctionne uniquement avec la version IC PN5190B2, qui utilise les blocs de chiffrement matériels sur puce

Les sections suivantes expliquent les commandes et les réponses du mode de téléchargement sécurisé du micrologiciel.

3.2 Comment déclencher le mode « Téléchargement sécurisé du firmware »

Le diagramme ci-dessous et les étapes suivantes montrent comment déclencher le mode de téléchargement sécurisé du micrologiciel. Condition préalable : PN5190 est en état de fonctionnement.

Condition préalable : PN5190 est en état de fonctionnement.

Scénario principal :

- Condition d'entrée où la broche DWL_REQ est utilisée pour accéder au mode « Téléchargement sécurisé du micrologiciel ».

un. L'hôte de l'appareil tire la broche DWL_REQ vers le haut (valable uniquement si la mise à jour sécurisée du micrologiciel via la broche DWL_REQ) OU

b. L'hôte de l'appareil effectue une réinitialisation matérielle pour démarrer le PN5190 - Condition d'entrée où la broche DWL_REQ n'est pas utilisée pour accéder au mode « Téléchargement sécurisé du micrologiciel » (téléchargement sans broche).

un. L'hôte de l'appareil effectue une réinitialisation matérielle pour démarrer le PN5190

b. L'hôte de l'appareil envoie SWITCH_MODE_NORMAL (Section 4.5.4.5) pour entrer en mode d'application normal.

c. Désormais, lorsque IC est en mode d'application normal, l'hôte de l'appareil envoie SWITCH_MODE_DOWNLOAD (Section 4.5.4.9) pour entrer en mode de téléchargement sécurisé. - L'hôte de l'appareil envoie la commande DL_GET_VERSION (Section 3.4.4), ou DL_GET_DIE_ID (Section 3.4.6), ou DL_GET_SESSION_STATE (Section 3.4.5).

- L'hôte de l'appareil lit la version actuelle du matériel et du micrologiciel, la session et l'ID de matrice de l'appareil.

un. L'hôte de l'appareil vérifie l'état de la session si le dernier téléchargement est terminé

b. L'hôte de l'appareil applique les règles de vérification de version pour décider de démarrer ou de quitter le téléchargement. - L'hôte de périphérique se charge à partir d'un file le code binaire du firmware à télécharger

- L'hôte du périphérique fournit une première commande DL_SEC_WRITE (Section 3.4.8) qui contient :

un. La version du nouveau firmware,

b. Un nom occasionnel de 16 octets de valeurs arbitraires utilisé pour l'obscurcissement de la clé de chiffrement

c. Une valeur de résumé de la trame suivante,

d. La signature numérique du cadre lui-même - L'hôte de l'appareil charge la séquence de protocole de téléchargement sécurisé sur le PN5190 avec les commandes DL_SEC_WRITE (Section 3.4.8).

- Lorsque la dernière commande DL_SEC_WRITE (Section 3.4.8) a été envoyée, l'hôte du périphérique exécute la commande DL_CHECK_INTEGRITY (Section 3.4.7) pour vérifier si les mémoires ont été écrites avec succès.

- L'hôte de l'appareil lit la nouvelle version du micrologiciel et vérifie l'état de la session si elle est fermée pour le signaler à la couche supérieure

- L'hôte de l'appareil tire la broche DWL_REQ au niveau bas (si la broche DWL_REQ est utilisée pour passer en mode de téléchargement)

- L'hôte de l'appareil effectue une réinitialisation matérielle (basculement de la broche VEN) sur l'appareil pour redémarrer le PN5190

Post-condition : le micrologiciel est mis à jour ; le nouveau numéro de version du micrologiciel est signalé.

3.3 Signature du micrologiciel et contrôle de version

En mode de téléchargement du micrologiciel PN5190, un mécanisme garantit que seul un micrologiciel signé et fourni par NXP sera accepté pour le micrologiciel NXP.

Ce qui suit s’applique uniquement au micrologiciel NXP sécurisé et chiffré.

Lors d'une session de téléchargement, une nouvelle version du firmware 16 bits est envoyée. Il est composé d'un nombre majeur et d'un nombre mineur :

- Nombre majeur : 8 bits (MSB)

- Numéro mineur : 8 bits (LSB)

Le PN5190 vérifie si le nouveau numéro de version majeure est supérieur ou égal à celui actuel. Dans le cas contraire, le téléchargement sécurisé du micrologiciel est rejeté et la session reste fermée.

3.4 Commandes HDLL pour le téléchargement chiffré existant et le chiffrement matériel assisté téléchargement crypté

Cette section fournit des informations sur les commandes et les réponses utilisées pour les deux types de téléchargements du micrologiciel NXP.

3.4.1 Codes OP de commande HDLL

Note: Les trames de commande HDLL sont alignées sur 4 octets. Les octets de charge utile inutilisés restent nuls.

Tableau 1. Liste des codes OP des commandes HDLL

| PN5190B0/B1 (Téléchargement hérité) | PN5190 B2 (Téléchargement assisté par Crypto) | Alias de commande | Description |

| 0xF0 | 0xE5 | DL_RESET | Effectue une réinitialisation logicielle |

| 0xF1 | 0xE1 | DL_GET_VERSION | Renvoie les numéros de version |

| 0xF2 | 0xDB | DL_GET_SESSION_STATE | Renvoie l'état de la session actuelle |

| 0xF4 | 0xDF | DL_GET_DIE_ID | Renvoie l'ID du dé |

| 0xE0 | 0xE7 | DL_CHECK_INTEGRITY | Vérifie et renvoie les CRC sur les différentes zones ainsi que les indicateurs de statut réussite/échec pour chacune |

| 0xC0 | 0x8C | DL_SEC_WRITE | Écrit x octets dans la mémoire en commençant à l'adresse absolue y |

3.4.2 Opcodes de réponse HDLL

Note: Les trames de réponse HDLL sont alignées sur 4 octets. Les octets de charge utile inutilisés restent nuls. Seules les réponses DL_OK peuvent contenir des valeurs de charge utile.

Tableau 2. Liste des codes OP de réponse HDLL

| Opcode | Alias de réponse | Description |

| 0x00 | DL_OK | Commande passée |

| 0x01 | DL_INVALID_ADDR | Adresse non autorisée |

| 0x0B | DL_UNKNOW_CMD | Commande inconnue |

| 0x0C | DL_ABORTED_CMD | La séquence de fragments est trop grande |

| 0x1E | DL_ADDR_RANGE_OFL_ERROR | Adresse hors plage |

| 0x1F | DL_BUFFER_OFL_ERROR | Le tampon est trop petit |

| 0x20 | DL_MEM_BSY | Mémoire occupée |

| 0x21 | DL_SIGNATURE_ERROR | Incompatibilité de signature |

| 0x24 | DL_FIRMWARE_VERSION_ERROR | Version actuelle égale ou supérieure |

| 0x28 | DL_PROTOCOL_ERROR | Erreur de protocole |

| 0x2A | DL_SFWU_DEGRADED | Corruption des données Flash |

| 0x2D | PH_STATUS_DL_FIRST_CHUNK | Premier morceau reçu |

| 0x2E | PH_STATUS_DL_NEXT_CHUNK | Attendez le prochain morceau |

| 0xC5 | PH_STATUS_INTERNAL_ERROR_5 | Inadéquation de longueur |

3.4.3 Commande DL_RESET

Échange de trames :

PN5190B0/B1 : [HDLL] -> [0x00 0x04 0xF0 0x00 0x00 0x00 0x18 0x5B]

PN5190 B2 : [HDLL] -> [0x00 0x04 0xE5 0x00 0x00 0x00 0xBF 0xB9] [HDLL] <- [0x00 0x04 STAT 0x00 CRC16] La réinitialisation empêche le PN5190 d'envoyer la réponse DL_STATUS_OK. Par conséquent, seul un statut erroné peut être reçu.

STAT est le statut de retour.

3.4.4 Commande DL_GET_VERSION

Échange de trames :

PN5190B0/B1 : [HDLL] -> [0x00 0x04 0xF1 0x00 0x00 0x00 0x6E 0xEF]

PN5190 B2 : [HDLL] -> [0x00 0x04 0xE1 0x00 0x00 0x00 0x75 0x48] [HDLL] <- [0x00 0x08 STAT HW_V RO_V MODEL_ID FM1V FM2V RFU1 RFU2 CRC16] La trame de charge utile de la réponse GetVersion est :

Tableau 3. Réponse à la commande GetVersion

| Champ | Octet | Description |

| STAT | 1 | Statut |

| HW_V | 2 | Version du matériel |

| RO_V | 3 | Code ROM |

| ID_MODÈLE | 4 | ID du modèle |

| FMxV | 5-6 | Version du micrologiciel (utilisée pour le téléchargement) |

| RFU1-RFU2 | 7-8 | – |

Les valeurs attendues des différents champs de réponse et leur mappage sont les suivants :

Tableau 4. Valeurs attendues de la réponse de la commande GetVersion

| Type de CI | Version matérielle (hexadécimale) | Version ROM (hexadécimale) | ID du modèle (hexadécimal) | Version du micrologiciel (hexadécimal) |

| PN5190 B0 | 0x51 | 0x02 | 0x00 | xx.aa |

| PN5190 B1 | 0x52 | 0x02 | 0x00 | xx.aa |

| PN5190 B2 | 0x53 | 0x03 | 0x00 | xx.aa |

3.4.5 Commande DL_GET_SESSION_STATE

Échange de trames :

PN5190B0/B1 : [HDLL] -> [0x00 0x04 0xF2 0x00 0x00 0x00 0xF5 0x33]

PN5190 B2 : [HDLL] -> [0x00 0x04 0xDB 0x00 0x00 0x00 0x31 0x0A] [HDLL] <- [0x00 0x04 STAT SSTA RFU CRC16] La trame de charge utile de la réponse GetSession est :

Tableau 5. Réponse à la commande GetSession

| Champ | Octet | Description |

| STAT | 1 | Statut |

| SSTA | 2 | État de la session • 0x00 : fermé • 0x01 : ouvert • 0x02 : verrouillé (le téléchargement n'est plus autorisé) |

| RFU | 3-4 |

3.4.6 Commande DL_GET_DIE_ID

Échange de trames :

PN5190B0/B1 : [HDLL] -> [0x00 0x04 0xF4 0x00 0x00 0x00 0xD2 0xAA]

PN5190 B2 : [HDLL] -> [0x00 0x04 0xDF 0x00 0x00 0x00 0xFB 0xFB] [HDLL] <- [0x00 0x14 STAT 0x00 0x00 0x00 ID0 ID1 ID2 ID3 ID4 ID5 ID6 ID7 ID8 ID9

ID10 ID11 ID12 ID13 ID14 ID15 CRC16] La trame de charge utile de la réponse GetDieId est :

Tableau 6. Réponse à la commande GetDieId

| Champ | Octet | Description |

| STAT | 1 | Statut |

| RFU | 2-4 | |

| DIÉID | 5-20 | ID du dé (16 octets) |

3.4.7 Commande DL_CHECK_INTEGRITY

Échange de trames :

PN5190B0/B1 : [HDLL] -> [0x00 0x04 0xE0 0x00 0x00 0x00 CRC16]

PN5190 B2 : [HDLL] -> [0x00 0x04 0xE7 0x00 0x00 0x00 0x52 0xD1] [HDLL] <- [0x00 0x20 STAT LEN_DATA LEN_CODE 0x00 [CRC_INFO] [CRC32] CRC16] La trame de charge utile de la réponse CheckIntegrity est :

Tableau 7. Réponse à la commande CheckIntegrity

| Champ | Octet | Valeur/Description | |

| STAT | 1 | Statut | |

| DONNÉES LEN | 2 | Nombre total de sections de données | |

| CODE LEN | 3 | Nombre total de sections de code | |

| RFU | 4 | Réservé | |

| [CRC_INFO] | 58 | 32 bits (petit-boutiste). Si un bit est activé, le CRC de la section correspondante est OK, sinon Not OK. | |

| Peu | Statut d'intégrité de la zone | ||

| [31:28] | Réservé [3] | ||

| [27:23] | Réservé [1] | ||

| [22] | Réservé [3] | ||

| [21:20] | Réservé [1] | ||

| [19] | Zone de configuration RF (PN5190 B0/B1) [2] Réservé (PN5190 B2) [3] | ||

| [18] | Zone de configuration du protocole (PN5190 B0/B1) [2] Zone de configuration RF (PN5190 B2) [2] | ||

| [17] | Réservé (PN5190 B0/B1) [3] Zone de configuration utilisateur (PN5190 B2) [2] | ||

| [16:6] | Réservé [3] | ||

| [5:4] | Réservé au PN5190 B0/B1 [3] Réservé au PN5190 B2 [1] | ||

| [3:0] | Réservé [1] | ||

| [CRC32] | 9-136 | CRC32 des 32 sections. Chaque CRC est de 4 octets stockés au format petit-boutiste. Les 4 premiers octets du CRC sont du bit CRC_INFO[31], les 4 octets suivants du CRC sont du bit CRC_INFO[30] et ainsi de suite. | |

- [1] Ce bit doit être 1 pour que le PN5190 fonctionne correctement (avec fonctionnalités et/ou téléchargement de firmware crypté).

- [2] Ce bit est défini sur 1 par défaut, mais les paramètres modifiés par l'utilisateur invalident le CRC. Aucun effet sur la fonctionnalité du PN5190.

- [3] Cette valeur de bit, même si elle est 0, n'est pas pertinente. Cette valeur de bit peut être ignorée.

3.4.8 Commande DL_SEC_WRITE

La commande DL_SEC_WRITE est à considérer dans le cadre d'une séquence de commandes d'écriture sécurisée : le « téléchargement sécurisé du firmware » crypté (souvent appelé eSFWu).

La commande d'écriture sécurisée ouvre d'abord la session de téléchargement et transmet l'authentification RSA. Les suivants transmettent des adresses et des octets cryptés à écrire dans le Flash PN5190. Tous, sauf le dernier, contiennent le hachage des suivants, informant donc qu'ils ne sont pas les derniers et liant cryptographiquement les images de séquence entre elles.

D'autres commandes (sauf DL_RESET et DL_CHECK_INTEGRITY) peuvent être insérées entre les commandes d'écriture sécurisée d'une séquence sans la rompre.

3.4.8.1 Première commande DL_SEC_WRITE

Une commande d'écriture sécurisée est la première si et seulement si :

- La longueur de la trame est de 312 octets

- Aucune commande d'écriture sécurisée n'a été reçue depuis la dernière réinitialisation.

- La signature intégrée est vérifiée avec succès par le PN5190.

La réponse à la première commande de trame serait la suivante : [HDLL] <- [0x00 0x04 STAT 0x00 0x00 0x00 CRC16] STAT est l'état de retour.

Note: Au moins un bloc de données doit être écrit lors d'un eSFWu, même si les données écrites ne peuvent contenir qu'un octet. Par conséquent, la première commande contiendra toujours le hachage de la commande suivante, puisqu’il y aura au moins deux commandes.

3.4.8.2 Commandes DL_SEC_WRITE du milieu

Une commande d'écriture sécurisée est une commande « intermédiaire » si et seulement si :

- L'opcode est tel que décrit dans la section 3.4.1 pour la commande DL_SEC_WRITE.

- Une première commande d'écriture sécurisée a déjà été reçue et vérifiée avec succès avant

- Aucune réinitialisation n'a eu lieu depuis la réception de la première commande d'écriture sécurisée

- La longueur de la trame est égale à la taille des données + taille de l'en-tête + taille du hachage : FLEN = SIZE + 6 + 32

- Le résumé de la trame entière est égal à la valeur de hachage reçue dans la trame précédente

La réponse à la première commande de trame serait la suivante : [HDLL] <- [0x00 0x04 STAT 0x00 0x00 0x00 CRC16] STAT est l'état de retour.

3.4.8.3 Dernière commande DL_SEC_WRITE

Une commande d'écriture sécurisée est la dernière si et seulement si :

- L'opcode est tel que décrit dans la section 3.4.1 pour la commande DL_SEC_WRITE.

- Une première commande d'écriture sécurisée a déjà été reçue et vérifiée avec succès avant

- Aucune réinitialisation n'a eu lieu depuis la réception de la première commande d'écriture sécurisée

- La longueur de la trame est égale à la taille des données + taille de l'en-tête : FLEN = SIZE + 6

- Le résumé de la trame entière est égal à la valeur de hachage reçue dans la trame précédente

La réponse à la première commande de trame serait la suivante : [HDLL] <- [0x00 0x04 STAT 0x00 0x00 0x00 CRC16] STAT est l'état de retour.

Mode de démarrage de fonctionnement IC – Mode de fonctionnement normal

4.1 Introduction

Généralement, le CI PN5190 doit être en mode de fonctionnement normal pour en tirer la fonctionnalité NFC.

Lorsque le circuit intégré PN5190 démarre, il attend toujours que les commandes soient reçues d'un hôte pour effectuer l'opération, à moins que les événements générés dans le circuit intégré PN5190 n'entraînent le démarrage du circuit intégré PN5190.

4.2 Liste des commandes terminéeview

Tableau 8. Liste des commandes PN5190

| Code de commande | Nom de la commande |

| 0x00 | ÉCRIRE_REGISTER |

| 0x01 | WRITE_REGISTER_OR_MASK |

| 0x02 | WRITE_REGISTER_AND_MASK |

| 0x03 | WRITE_REGISTER_MULTIPLE |

| 0x04 | READ_REGISTER |

| 0x05 | READ_REGISTER_MULTIPLE |

| 0x06 | ÉCRIRE_E2PROM |

| 0x07 | READ_E2PROM |

| 0x08 | TRANSMIT_RF_DATA |

| 0x09 | RETRIEVE_RF_DATA |

| 0x0A | EXCHANGE_RF_DATA |

| 0x0B | MFC_AUTHENTICATE |

| 0x0C | EPC_GEN2_INVENTORY |

| 0x0D | LOAD_RF_CONFIGURATION |

| 0x0E | UPDATE_RF_CONFIGURATION |

| 0x0F | GET_RF_CONFIGURATION |

| 0x10 | RF_ON |

| 0x11 | RF_OFF |

| 0x12 | CONFIGURER TESTBUS_DIGITAL |

| 0x13 | CONFIGURE_TESTBUS_ANALOG |

| 0x14 | CTS_ENABLE |

| 0x15 | CTS_CONFIGURE |

| 0x16 | CTS_RETRIEVE_LOG |

| 0x17-0x18 | RFU |

| 0x19 | jusqu'au FW v2.01 : RFU |

| à partir du FW v2.03 : RETRIEVE_RF_FELICA_EMD_DATA | |

| 0x1A | RECEIVE_RF_DATA |

| 0x1B-0x1F | RFU |

| 0x20 | SWITCH_MODE_NORMAL |

| 0x21 | SWITCH_MODE_AUTOCOLL |

| 0x22 | SWITCH_MODE_STANDBY |

| 0x23 | SWITCH_MODE_LPCD |

| 0x24 | RFU |

| 0x25 | SWITCH_MODE_DOWNLOAD |

| 0x26 | GET_DIEID |

| 0x27 | GET_VERSION |

| 0x28 | RFU |

| 0x29 | jusqu'au FW v2.05 : RFU |

| à partir du FW v2.06 : GET_CRC_USER_AREA | |

| 0x2A | jusqu'au FW v2.03 : RFU |

| à partir du FW v2.05 : CONFIGURE_MULTIPLE_TESTBUS_DIGITAL | |

| 0x2B-0x3F | RFU |

| 0x40 | ANTENNA_SELF_TEST (non pris en charge) |

| 0x41 | PRBS_TEST |

| 0x42-0x4F | RFU |

4.3 Valeurs d'état de réponse

Voici les valeurs d'état de réponse, qui sont renvoyées dans le cadre de la réponse du PN5190 une fois la commande opérationnalisée.

Tableau 9. Valeurs d'état de réponse PN5190

| Statut de réponse | Valeur de l'état de la réponse | Description |

| PN5190_STATUS_SUCCESS | 0x00 | Indique que l'opération s'est terminée avec succès |

| PN5190_STATUS_TIMEOUT | 0x01 | Indique que l'exécution de la commande a entraîné un délai d'attente |

| PN5190_STATUS_INTEGRITY_ERROR | 0x02 | Indique que l'exécution de la commande a entraîné une erreur d'intégrité des données RF. |

| PN5190_STATUS_RF_COLLISION_ERROR | 0x03 | Indique que l'exécution de la commande a entraîné une erreur de collision RF |

| PN5190_STATUS_RFU1 | 0x04 | Réservé |

| PN5190_STATUS_INVALID_COMMAND | 0x05 | Indique que la commande donnée n'est pas valide/non implémentée |

| PN5190_STATUS_RFU2 | 0x06 | Réservé |

| PN5190_STATUS_AUTH_ERROR | 0x07 | Indique que l'authentification MFC a échoué (autorisation refusée) |

| PN5190_STATUS_MEMORY_ERROR | 0x08 | Indique que l'exécution de la commande a entraîné une erreur de programmation ou une erreur de mémoire interne |

| PN5190_STATUS_RFU4 | 0x09 | Réservé |

| PN5190_STATUS_NO_RF_FIELD | 0x0A | Indique qu'il n'y a pas ou erreur de présence du champ RF interne (applicable uniquement si mode initiateur/lecteur) |

| PN5190_STATUS_RFU5 | 0x0B | Réservé |

| PN5190_STATUS_SYNTAX_ERROR | 0x0C | Indique qu'une longueur de trame de commande non valide est reçue |

| PN5190_STATUS_RESOURCE_ERROR | 0x0D | Indique qu'une erreur de ressource interne s'est produite |

| PN5190_STATUS_RFU6 | 0x0E | Réservé |

| PN5190_STATUS_RFU7 | 0x0F | Réservé |

| PN5190_STATUS_NO_EXTERNAL_RF_FIELD | 0x10 | Indique qu'aucun champ RF externe n'est présent lors de l'exécution de la commande (Applicable uniquement en mode carte/cible) |

| PN5190_STATUS_RX_TIMEOUT | 0x11 | Indique que les données ne sont pas reçues après le lancement de RFExchange et que le délai RX a expiré. |

| PN5190_STATUS_USER_CANCELLED | 0x12 | Indique que la commande en cours en cours est abandonnée |

| PN5190_STATUS_PREVENT_STANDBY | 0x13 | Indique que le PN5190 ne peut pas passer en mode veille |

| PN5190_STATUS_RFU9 | 0x14 | Réservé |

| PN5190_STATUS_CLOCK_ERROR | 0x15 | Indique que l'horloge du CLIF n'a pas démarré |

| PN5190_STATUS_RFU10 | 0x16 | Réservé |

| PN5190_STATUS_PRBS_ERROR | 0x17 | Indique que la commande PRBS a renvoyé une erreur |

| PN5190_STATUS_INSTR_ERROR | 0x18 | Indique que l'exécution de la commande a échoué (cela peut inclure une erreur dans les paramètres de l'instruction, une erreur de syntaxe, une erreur dans l'opération elle-même, les conditions préalables pour l'instruction ne sont pas remplies, etc.) |

| PN5190_STATUS_ACCESS_DENIED | 0x19 | Indique que l'accès à la mémoire interne est refusé |

| PN5190_STATUS_TX_FAILURE | 0x1A | Indique que l'émission sur RF a échoué |

| PN5190_STATUS_NO_ANTENNA | 0x1B | Indique qu'aucune antenne n'est connectée/présente |

| PN5190_STATUS_TXLDO_ERROR | 0x1C | Indique qu'il y a une erreur dans TXLDO lorsque le VUP n'est pas disponible et que RF est activé. |

| PN5190_STATUS_RFCFG_NOT_APPLIED | 0x1D | Indique que la configuration RF n'est pas chargée lorsque RF est allumé |

| PN5190_STATUS_TIMEOUT_WITH_EMD_ERROR | 0x1E | jusqu'à FW 2.01 : non prévu |

| à partir du FW 2.03 : Indique que lors de l'échange avec LOG ENABLE BIT est défini dans le registre FeliCa EMD, une erreur FeliCa EMD a été observée | ||

| PN5190_STATUS_INTERNAL_ERROR | 0x7F | Indique que l'opération NVM a échoué |

| PN5190_STATUS_SUCCSES_CHAINING | 0xAF | Indique que, de plus, les données sont en attente de lecture |

4.4 Événements terminésview

Il existe deux manières de notifier les événements à l'hôte.

4.4.1 Événements normaux sur la broche IRQ

Ces événements sont les catégories ci-dessous :

- Toujours activé – L'hôte est toujours averti

- Contrôlé par l'hôte – L'hôte est averti si le bit d'activation d'événement correspondant est défini dans le registre (EVENT_ENABLE (01h)).

Les interruptions de bas niveau provenant des adresses IP périphériques, y compris le CLIF, doivent être entièrement gérées dans le micrologiciel et l'hôte doit être informé uniquement des événements répertoriés dans la section Événements.

Le micrologiciel implémente deux registres d'événements en tant que registres RAM qui peuvent être écrits/lus à l'aide des commandes Section 4.5.1.1/Section 4.5.1.5.

Le registre EVENT_ENABLE (0x01) => Activer les notifications d'événements spécifiques/toutes.

Le registre EVENT_STATUS (0x02) => Partie de la charge utile du message d'événement.

Les événements doivent être effacés par l'hôte une fois que le message d'événement est lu par l'hôte.

Les événements sont de nature asynchrone et sont notifiés à l'hôte, s'ils sont activés dans le registre EVENT_ENABLE.

Voici la liste des événements qui doivent être disponibles pour l'hôte dans le cadre du message d'événement.

Tableau 10. Événements PN5190 (contenu de EVENT_STATUS)

| Bit – Plage | Champ [1] | Toujours Activé (O/N) | |

| 31 | 12 | RFU | NA |

| 11 | 11 | CTS_ÉVÉNEMENT [2] | N |

| 10 | 10 | IDLE_EVENT | Y |

| 9 | 9 | LPCD_CALIBRATION_DONE_EVENT | Y |

| 8 | 8 | LPCD_ÉVÉNEMENT | Y |

| 7 | 7 | AUTOCOLL_EVENT | Y |

| 6 | 6 | TIMER0_EVENT | N |

| 5 | 5 | TX_OVERCURRENT_EVENT | N |

| 4 | 4 | RFON_DET_EVENT [2] | N |

| 3 | 3 | RFOFF_DET_EVENT [2] | N |

| 2 | 2 | STANDBY_PREV_EVENT | Y |

| 1 | 1 | GENERAL_ERROR_EVENT | Y |

| 0 | 0 | BOOT_EVENT | Y |

- A noter qu'aucun événement n'est matraqué sauf en cas d'erreur. En cas d'erreurs pendant l'opération, l'événement fonctionnel (par exemple BOOT_EVENT, AUTOCALL_EVENT etc.) et GENERAL_ERROR_EVENT seront définis.

- Cet événement sera automatiquement désactivé après sa publication sur l'hôte. L'hébergeur doit réactiver ces événements s'il souhaite que ces événements lui soient notifiés.

4.4.1.1 Formats des messages d'événement

Le format du message d'événement diffère en fonction des occurrences d'un événement et des différents états du PN5190.

L'hôte doit lire tag (T) et la longueur du message (L), puis lire le nombre d'octets correspondant comme valeur (V) des événements.

En général, le message d'événement (voir la figure 12) contient le EVENT_STATUS tel que défini dans le Tableau 11 et les données d'événement correspondent au bit d'événement respectif défini dans EVENT_STATUS.

Note:

Pour certains événements, la charge utile n'existe pas. Par exemple, si TIMER0_EVENT est déclenché, seul EVENT_STATUS est fourni dans le cadre du message d'événement.

Le tableau 11 détaille également si les données d'événement sont présentes pour l'événement correspondant dans le message d'événement. GENERAL_ERROR_EVENT peut également se produire avec d'autres événements.

GENERAL_ERROR_EVENT peut également se produire avec d'autres événements.

Dans ce scénario, le message d'événement (voir Figure 13) contient EVENT_STATUS tel que défini dans le Tableau 11 et GENERAL_ERROR_STATUS_DATA tel que défini dans le Tableau 14, puis les données d'événement correspondent au bit d'événement respectif défini dans EVENT_STATUS tel que défini dans le Tableau 11. Note:

Note:

Ce n'est qu'après le BOOT_EVENT ou après POR, STANDBY, ULCCD que l'hôte pourra fonctionner en mode de fonctionnement normal en exécutant les commandes répertoriées ci-dessus.

En cas d'abandon d'une commande en cours d'exécution existante, seulement après IDLE_EVENT, l'hôte pourra fonctionner en mode de fonctionnement normal en émettant les commandes répertoriées ci-dessus.

4.4.1.2 Différentes définitions d'état d'ÉVÉNEMENT

4.4.1.2.1 Définitions de bits pour EVENT_STATUS

Tableau 11. Définitions des bits EVENT_STATUS

| Bit (vers – depuis) | Événement | Description | Données d'événement de l'événement correspondant (le cas échéant) | |

| 31 | 12 | RFU | Réservé | |

| 11 | 11 | CTS_ÉVÉNEMENT | Ce bit est défini lorsque l'événement CTS est généré. | Tableau 86 |

| 10 | 10 | IDLE_EVENT | Ce bit est activé lorsque la commande en cours est annulée en raison de l'émission de la commande SWITCH_MODE_NORMAL. | Aucune donnée d'événement |

| 9 | 9 | LPCD_CALIBRATION_DONE_ ÉVÉNEMENT | Ce bit est défini lorsque l’événement LPCD calibrationdone est généré. | Tableau 16 |

| 8 | 8 | LPCD_ÉVÉNEMENT | Ce bit est activé lorsque l'événement LPCD est généré. | Tableau 15 |

| 7 | 7 | AUTOCOLL_EVENT | Ce bit est activé lorsque l'opération AUTOCOLL est terminée. | Tableau 52 |

| 6 | 6 | TIMER0_EVENT | Ce bit est activé lorsque l'événement TIMER0 se produit. | Aucune donnée d'événement |

| 5 | 5 | TX_OVERCURRENT_ERROR_ ÉVÉNEMENT | Ce bit est activé lorsque le courant sur le pilote TX est supérieur au seuil défini dans l'EEPROM. Dans cette condition, le champ est automatiquement désactivé avant la notification à l'hôte. Veuillez vous référer à la section 4.4.2.2. | Aucune donnée d'événement |

| 4 | 4 | RFON_DET_EVENT | Ce bit est activé lorsque le champ RF externe est détecté. | Aucune donnée d'événement |

| 3 | 3 | RFOFF_DET_EVENT | Ce bit est activé lorsque le champ RF externe déjà existant disparaît. | Aucune donnée d'événement |

| 2 | 2 | STANDBY_PREV_EVENT | Ce bit est activé lorsque la veille est empêchée en raison de conditions de prévention existantes. | Tableau 13 |

| 1 | 1 | GENERAL_ERROR_EVENT | Ce bit est activé lorsque des conditions d'erreur générales existent | Tableau 14 |

| 0 | 0 | BOOT_EVENT | Ce bit est défini lorsque le PN5190 est démarré avec POR/Standby | Tableau 12 |

4.4.1.2.2 Définitions de bits pour BOOT_STATUS_DATA

Tableau 12. Définitions des bits BOOT_STATUS_DATA

| Un peu à | Bit de | Statut de démarrage | Raison de démarrage due à |

| 31 | 27 | RFU | Réservé |

| 26 | 26 | ULP_STANDBY | Raison du démarrage due à la sortie de ULP_STANDBY. |

| 25 | 23 | RFU | Réservé |

| 22 | 22 | BOOT_RX_ULPDET | RX ULPDET a entraîné un démarrage en mode ULP-Standby |

| 21 | 21 | RFU | Réservé |

| 20 | 20 | BOOT_SPI | Raison du démarrage due au signal SPI_NTS abaissé |

| 19 | 17 | RFU | Réservé |

| 16 | 16 | BOOT_GPIO3 | Raison du démarrage due à la transition de GPIO3 de bas en haut. |

| 15 | 15 | BOOT_GPIO2 | Raison du démarrage due à la transition de GPIO2 de bas en haut. |

| 14 | 14 | BOOT_GPIO1 | Raison du démarrage due à la transition de GPIO1 de bas en haut. |

| 13 | 13 | BOOT_GPIO0 | Raison du démarrage due à la transition de GPIO0 de bas en haut. |

| 12 | 12 | BOOT_LPDET | Raison du démarrage due à la présence d'un champ RF externe pendant STANDBY/SUSPEND |

| 11 | 11 | RFU | Réservé |

| 10 | 8 | RFU | Réservé |

| 7 | 7 | BOOT_SOFT_RESET | Raison du démarrage en raison d'une réinitialisation logicielle du circuit intégré |

| 6 | 6 | BOOT_VDDIO_LOSS | Raison du démarrage en raison de la perte de VDDIO. Se référer à la section 4.4.2.3 |

| 5 | 5 | BOOT_VDDIO_START | Raison du démarrage si STANDBY est entré avec VDDIO LOSS. Reportez-vous à la section 4.4.2.3 |

| 4 | 4 | BOOT_WUC | Raison du démarrage due au compteur de réveil écoulé pendant l’une ou l’autre des opérations STANDBY. |

| 3 | 3 | BOOT_TEMP | La raison du démarrage due à la température du circuit intégré est supérieure à la limite de seuil configurée. Veuillez vous référer à la section 4.4.2.1. |

| 2 | 2 | BOOT_WDG | Raison du démarrage due à la réinitialisation du chien de garde |

| 1 | 1 | RFU | Réservé |

| 0 | 0 | BOOT_POR | Raison du démarrage due à une réinitialisation à la mise sous tension |

4.4.1.2.3 Définitions de bits pour STANDBY_PREV_STATUS_DATA

Tableau 13. Définitions des bits STANDBY_PREV_STATUS_DATA

| Un peu à | Bit de | Prévention en veille | Veille empêchée en raison de |

| 31 | 26 | RFU | RÉSERVÉ |

| 25 | 25 | RFU | RÉSERVÉ |

| 24 | 24 | PREV_TEMP | La température de fonctionnement des circuits intégrés est hors seuil |

| 23 | 23 | RFU | RÉSERVÉ |

| 22 | 22 | PREV_HOSTCOMM | Communication de l'interface hôte |

| 21 | 21 | PREV_SPI | Le signal SPI_NTS est abaissé |

| 20 | 18 | RFU | RÉSERVÉ |

| 17 | 17 | PREV_GPIO3 | Signal GPIO3 passant de bas à haut |

| 16 | 16 | PREV_GPIO2 | Signal GPIO2 passant de bas à haut |

| 15 | 15 | PREV_GPIO1 | Signal GPIO1 passant de bas à haut |

| 14 | 14 | PREV_GPIO0 | Signal GPIO0 passant de bas à haut |

| 13 | 13 | PREV_WUC | Compteur de réveil écoulé |

| 12 | 12 | PREV_LPDET | Détection de faible puissance. Se produit lorsqu'un signal RF externe est détecté lors du processus de mise en veille. |

| 11 | 11 | PREV_RX_ULPDET | Détection de puissance ultra faible RX. Se produit lorsqu'un signal RF est détecté lors du processus d'accès à ULP_STANDBY. |

| 10 | 10 | RFU | RÉSERVÉ |

| 9 | 5 | RFU | RÉSERVÉ |

| 4 | 4 | RFU | RÉSERVÉ |

| 3 | 3 | RFU | RÉSERVÉ |

| 2 | 2 | RFU | RÉSERVÉ |

| 1 | 1 | RFU | RÉSERVÉ |

| 0 | 0 | RFU | RÉSERVÉ |

4.4.1.2.4 Définitions de bits pour GENERAL_ERROR_STATUS_DATA

Tableau 14. Définitions des bits GENERAL_ERROR_STATUS_DATA

| Un peu à | Un peu de | Statut d'erreur | Description |

| 31 | 6 | RFU | Réservé |

| 5 | 5 | XTAL_START_ERROR | Le démarrage de XTAL a échoué lors du démarrage |

| 4 | 4 | SYS_TRIM_RECOVERY_ERROR | Une erreur de mémoire de suppression du système interne s'est produite, mais la récupération a échoué. Le système fonctionne en mode dégradé. |

| 3 | 3 | SYS_TRIM_RECOVERY_SUCCESS | Une erreur de mémoire de suppression du système interne s'est produite et la récupération a réussi. L'hôte doit effectuer un redémarrage du PN5190 pour que la récupération prenne effet. |

| 2 | 2 | TXLDO_ERROR | Erreur TXLDO |

| 1 | 1 | CLOCK_ERROR | Erreur d'horloge |

| 0 | 0 | GPADC_ERREUR | Erreur ADC |

4.4.1.2.5 Définitions de bits pour LPCD_STATUS_DATA

Tableau 15. Définitions des octets LPCD_STATUS_DATA

| Un peu à | Bit de | Applicabilité des bits d’état selon le fonctionnement sous-jacent du LPCD ou de l’ULPCD | La description du bit correspondant est définie dans l'octet d'état. | ||

| LPCD | ULPCD | ||||

| 31 | 7 | RFU | Réservé | ||

| 6 | 6 | Abandon_HIF | Y | N | Avorté en raison de l'activité HIF |

| 5 | 5 | Erreur CLKDET | N | Y | Abandonné en raison d'une erreur CLKDET |

| 4 | 4 | Expiration du délai XTAL | N | Y | Abandonné en raison d'un délai d'attente XTAL. |

| 3 | 3 | Surintensité VDDPA LDO | N | Y | Abandon en raison d'une surintensité VDDPA LDO survenue |

| 2 | 2 | Champ RF externe | Y | Y | Avorté en raison d'un champ RF externe |

| 1 | 1 | Abandon GPIO3 | N | Y | Avorté en raison d'un changement de niveau GPIO3 |

| 0 | 0 | Carte détectée | Y | Y | La carte est détectée |

4.4.1.2.6 Définitions de bits pour LPCD_CALIBRATION_DONE Données d'état

Tableau 16. Définitions des octets de données d'état LPCD_CALIBRATION_DONE pour UPCD

| Un peu à | Bit de | Statut de LPCD_CALIBRATION DONE événement | La description du bit correspondant est définie dans l'octet d'état. |

| 31 | 11 | Réservé | |

| 10 | 0 | Valeur de référence issue de l'étalonnage UPCD | La valeur RSSI mesurée lors de l'étalonnage UPCD qui est utilisée comme référence pendant l'ULPCD |

Tableau 17. Définitions des octets de données d'état LPCD_CALIBRATION_DONE pour LPCD

| Un peu à | Bit de | Applicabilité des bits d’état selon le fonctionnement sous-jacent du LPCD ou de l’ULPCD | La description du bit correspondant est définie dans l'octet d'état. | ||

| 2 | 2 | Champ RF externe | Y | Y | Avorté en raison d'un champ RF externe |

| 1 | 1 | Abandon GPIO3 | N | Y | Avorté en raison d'un changement de niveau GPIO3 |

| 0 | 0 | Carte détectée | Y | Y | La carte est détectée |

4.4.2 Gestion des différents scénarios de démarrage

Le CI PN5190 gère différentes conditions d'erreur liées aux paramètres du CI comme ci-dessous.

4.4.2.1 Gestion du scénario de surchauffe lorsque le PN5190 est en fonctionnement

Chaque fois que la température interne du CI PN5190 atteint la valeur seuil configurée dans le champ EEPROM TEMP_WARNING [2], le CI entre en veille. Et par conséquent, si le champ EEPROM ENABLE_GPIO0_ON_OVERTEMP [2] est configuré pour envoyer une notification à l'hôte, alors GPIO0 sera tiré vers le haut pour avertir le circuit intégré d'une surchauffe.

Au fur et à mesure que la température du CI tombe en dessous de la valeur seuil configurée dans le champ EEPROM TEMP_WARNING [2], le CI démarrera avec BOOT_EVENT comme dans le tableau 11 et le bit d'état de démarrage BOOT_TEMP est défini comme dans le tableau 12 et GPIO0 sera abaissé.

4.4.2.2 Gestion des surintensités

Si le CI PN5190 détecte la condition de surintensité, le CI coupe l'alimentation RF et envoie le TX_OVERCURRENT_ERROR_EVENT comme dans le tableau 11.

La durée de la condition de surintensité peut être contrôlée en modifiant le champ EEPROM TXLDO_CONFIG [2].

Pour plus d'informations sur le seuil de dépassement de courant IC, reportez-vous au document [2].

Note:

S'il y a d'autres événements ou réponses en attente, ils seront envoyés à l'hôte.

4.4.2.3 Perte de VDDIO pendant le fonctionnement

Si le CI PN5190 constate qu'il n'y a pas de VDDIO (perte de VDDIO), le CI entre en veille.

IC démarre uniquement lorsque le VDDIO est disponible, avec BOOT_EVENT comme dans le tableau 11 et le bit d'état de démarrage BOOT_VDDIO_START est défini comme dans le tableau 12.

Pour plus d'informations sur les caractéristiques statiques du CI PN5190, reportez-vous au document [2].

4.4.3 Gestion des scénarios d'abandon

Le CI PN5190 prend en charge l'abandon des commandes en cours d'exécution et le comportement du CI PN5190, lorsqu'une telle commande d'abandon telle que la section 4.5.4.5.2 est envoyée au CI PN5190, est comme indiqué dans le tableau 18.

Note:

Lorsque le circuit intégré PN5190 est en mode ULPCD et ULP-Standby, il ne peut pas être interrompu soit en envoyant une section 4.5.4.5.2 OU en démarrant une transaction SPI (en tirant vers le bas sur le signal SPI_NTS).

Tableau 18. Réponse d'événement attendue lorsque différentes commandes se terminent avec la section 4.5.4.5.2

| Commandes | Comportement lorsque la commande Switch Mode Normal est envoyée |

| Toutes les commandes pour lesquelles une faible puissance n'est pas saisie | EVENT_STAUS est défini sur « IDLE_EVENT » |

| Mode de commutation LPCD | EVENT_STATUS est défini sur « LPCD_EVENT » avec « LPCD_ STATUS_DATA » indiquant les bits d'état comme « Abort_HIF » |

| Mode de commutation en veille | EVENT_STAUS est défini sur « BOOT_EVENT » avec « BOOT_ STATUS_DATA » indiquant les bits « BOOT_SPI » |

| Mode de commutation Autocoll (pas de mode autonome, mode autonome avec veille et mode autonome sans veille) | EVENT_STAUS est défini sur « AUTOCOLL_EVENT » avec des bits STATUS_DATA indiquant que la commande a été annulée par l'utilisateur. |

4.5 Détails des instructions de fonctionnement en mode normal

4.5.1 Manipulation des registres

Les instructions de cette section sont utilisées pour accéder aux registres logiques du PN5190.

4.5.1.1 ÉCRIRE_REGISTER

Cette instruction est utilisée pour écrire une valeur de 32 bits (petit-boutiste) dans un registre logique.

4.5.1.1.1 conditions

L'adresse du registre doit exister et le registre doit avoir l'attribut READ-WRITE ou WRITE-ONLY.

4.5.1.1.2 Commande

Tableau 19. Valeur de la commande WRITE_REGISTER Écrit une valeur 32 bits dans un registre.

| Champ de charge utile | Longueur | Valeur/Description |

| Adresse d'inscription | 1 octets | Adresse du registre. |

Tableau 19. Valeur de la commande WRITE_REGISTER…suite

Écrivez une valeur 32 bits dans un registre.

| Champ de charge utile | Longueur | Valeur/Description |

| Valeur | 4 octets | Valeur de registre 32 bits qui doit être écrite. (Petit endian) |

4.5.1.1.3 Réponse

Tableau 20. Valeur de réponse WRITE_REGISTER

| Champ de charge utile | Longueur | Valeur/Description |

| Statut | 1 octets | Statut de l'opération [Tableau 9]. Les valeurs attendues sont les suivantes : |

| PN5190_STATUS_SUCCESS | ||

| PN5190_STATUS_INSTR_ERROR |

4.5.1.1.4 événement

Il n'y a aucun événement pour cette commande.

4.5.1.2 WRITE_REGISTER_OR_MASK

Cette instruction permet de modifier le contenu du registre à l'aide d'une opération OU logique. Le contenu du registre est lu et une opération OU logique est effectuée avec le masque fourni. Le contenu modifié est réécrit dans le registre.

4.5.1.2.1 conditions

L'adresse du registre doit exister et le registre doit avoir l'attribut READ-WRITE.

4.5.1.2.2 Commande

Tableau 21. Valeur de la commande WRITE_REGISTER_OR_MASK Effectue une opération OU logique sur un registre à l'aide du masque fourni.

| Champ de charge utile | Longueur | Valeur/description |

| Adresse d'inscription | 1 octets | Adresse du registre. |

| Masque | 4 octets | Masque de bits utilisé comme opérande pour l’opération OU logique. (Petit endian) |

4.5.1.2.3 Réponse

Tableau 22. Valeur de réponse WRITE_REGISTER_OR_MASK

| Champ de charge utile | Longueur | Valeur/Description |

| Statut | 1 octets | Statut de l'opération [Tableau 9]. Les valeurs attendues sont les suivantes : |

| PN5190_STATUS_SUCCESS | ||

| PN5190_STATUS_INSTR_ERROR |

4.5.1.2.4 événement

Il n'y a aucun événement pour cette commande.

4.5.1.3 WRITE_REGISTER_AND_MASK

Cette instruction permet de modifier le contenu du registre à l'aide d'une opération logique ET. Le contenu du registre est lu et une opération ET logique est effectuée avec le masque fourni. Le contenu modifié est réécrit dans le registre.

4.5.1.3.1 conditions

L'adresse du registre doit exister et le registre doit avoir l'attribut READ-WRITE.

4.5.1.3.2 Commande

Tableau 23. Valeur de la commande WRITE_REGISTER_AND_MASK Effectue une opération ET logique sur un registre à l'aide du masque fourni.

| Champ de charge utile | Longueur | Valeur/description |

| Adresse d'inscription | 1 octets | Adresse du registre. |

| Masque | 4 octets | Masque de bits utilisé comme opérande pour l’opération ET logique. (Petit endian ) |

4.5.1.3.3 Réponse

Tableau 24. Valeur de réponse WRITE_REGISTER_AND_MASK

| Champ de charge utile | Longueur | Valeur/Description |

| Statut | 1 octets | Statut de l'opération [Tableau 9]. Les valeurs attendues sont les suivantes : |

| PN5190_STATUS_SUCCESS | ||

| PN5190_STATUS_INSTR_ERROR |

4.5.1.3.4 événement

Il n'y a aucun événement pour cette commande.

4.5.1.4 WRITE_REGISTER_MULTIPLE

Cette fonctionnalité d'instruction est similaire à la Section 4.5.1.1, Section 4.5.1.2, Section 4.5.1.3, avec la possibilité de les combiner. En fait, il prend un tableau d'ensembles de valeurs de type de registre et exécute l'action appropriée. Le type reflète l'action qui est soit une écriture dans un registre, soit une opération OU logique sur un registre, soit une opération ET logique sur un registre.

4.5.1.4.1 conditions

L'adresse logique respective du registre dans un ensemble doit exister.

L'attribut d'accès au registre doit permettre l'exécution de l'action requise (type) :

- Action d'écriture (0x01) : attribut READ-WRITE ou WRITE-ONLY

- Action de masque OU (0x02) : attribut READ-WRITE

- ET action de masque (0x03) : attribut READ-WRITE

La taille du tableau « Set » doit être comprise entre 1 et 43 inclus.

Le champ « Type » doit être compris entre 1 et 3 inclus.

4.5.1.4.2 Commande

Tableau 25. Valeur de la commande WRITE_REGISTER_MULTIPLE Effectue une opération d'écriture de registre à l'aide d'un ensemble de paires Registre-Valeur.

| Champ de charge utile | Longueur | Valeur/description | |||

| Définir [1…n] | 6 octets | Adresse d'inscription | 1 octets | Adresse logique du registre. | |

| Taper | 1 octets | 0x1 | Registre d'écriture | ||

| 0x2 | Écrire le registre OU le masque | ||||

| 0x3 | Écrire le registre ET le masque | ||||

| Valeur | 4 octets | 32 Valeur du registre de bits qui doit être écrite, ou masque de bits utilisé pour l'opération logique. (Petit endian) | |||

Remarque : En cas d'exception, l'opération n'est pas annulée, c'est-à-dire que les registres qui ont été modifiés jusqu'à ce qu'une exception se produise restent dans un état modifié. L'hôte doit prendre les mesures appropriées pour revenir à un état défini.

4.5.1.4.3 Réponse

Tableau 26. Valeur de réponse WRITE_REGISTER_MULTIPLE

| Champ de charge utile | Longueur | Valeur/Description |

| Statut | 1 octets | Statut de l'opération [Tableau 9]. Les valeurs attendues sont les suivantes : |

| PN5190_STATUS_SUCCESS | ||

| PN5190_STATUS_INSTR_ERROR |

4.5.1.4.4 événement

Il n'y a aucun événement pour cette commande.

4.5.1.5 READ_REGISTER

Cette instruction permet de relire le contenu d'un registre logique. Le contenu est présent dans la réponse, sous forme de valeur de 4 octets au format petit-boutiste.

4.5.1.5.1 conditions

L'adresse du registre logique doit exister. L'attribut d'accès du registre doit être soit READ-WRITE, soit READ-ONLY.

4.5.1.5.2 Commande

Tableau 27. Valeur de la commande READ_REGISTER

Relisez le contenu d'un registre.

| Champ de charge utile | Longueur | Valeur/Description |

| Adresse d'inscription | 1 octets | Adresse du registre logique |

4.5.1.5.3 Réponse

Tableau 28. Valeur de réponse READ_REGISTER

| Champ de charge utile | Longueur | Valeur/Description |

| Statut | 1 octets | Statut de l'opération [Tableau 9]. Les valeurs attendues sont les suivantes : |

| PN5190_STATUS_SUCCESS PN5190_STATUS_INSTR_ERROR (Aucune autre donnée n'est présente) | ||

| Enregistrer la valeur | 4 octets | Valeur du registre 32 bits qui a été lue. (Petit endian) |

4.5.1.5.4 événement

Il n'y a aucun événement pour cette commande.

4.5.1.6 READ_REGISTER_MULTIPLE

Cette instruction est utilisée pour lire plusieurs registres logiques à la fois. Le résultat (contenu de chaque registre) est fourni dans la réponse à l'instruction. L'adresse du registre elle-même n'est pas incluse dans la réponse. L'ordre du contenu du registre dans la réponse correspond à l'ordre des adresses du registre dans l'instruction.

4.5.1.6.1 conditions

Toutes les adresses de registre dans l'instruction doivent exister. L'attribut d'accès pour chaque registre doit être soit READ-WRITE, soit READ-ONLY. La taille du tableau « Register Address » doit être comprise entre 1 et 18 inclus.

4.5.1.6.2 Commande

Tableau 29. Valeur de la commande READ_REGISTER_MULTIPLE Effectue une opération de lecture de registre sur un ensemble de registres.

| Champ de charge utile | Longueur | Valeur/Description |

| Adresse d'enregistrement[1…n] | 1 octets | Adresse d'inscription |

4.5.1.6.3 Réponse

Tableau 30. Valeur de réponse READ_REGISTER_MULTIPLE

| Champ de charge utile | Longueur | Valeur/description | ||

| Statut | 1 octets | Statut de l'opération [Tableau 9]. Les valeurs attendues sont les suivantes : | ||

| PN5190_STATUS_SUCCESS PN5190_STATUS_INSTR_ERROR (Aucune autre donnée n'est présente) | ||||

| Valeur du registre [1…n] | 4 octets | Valeur | 4 octets | Valeur de registre 32 bits qui a été lue (little-endian). |

4.5.1.6.4 événement

Il n'y a aucun événement pour cette commande.

4.5.2 Manipulation de l'E2PROM

La zone accessible dans E2PROM est conforme à la carte EEPROM et à la taille adressable.

Note:

1. Chaque fois que « l'adresse E2PROM » est mentionnée dans les instructions ci-dessous, elle fait référence à la taille de la zone EEPROM adressable.

4.5.2.1 ÉCRITURE_E2PROM

Cette instruction est utilisée pour écrire une ou plusieurs valeurs dans E2PROM. Le champ « Valeurs » contient les données à écrire dans E2PROM à partir de l'adresse indiquée dans le champ « Adresse E2PROM ». Les données sont écrites dans un ordre séquentiel.

Note:

Notez qu'il s'agit d'une commande de blocage, cela signifie que le NFC FE est bloqué pendant l'opération d'écriture. Cela peut prendre plusieurs millisecondes.

4.5.2.1.1 conditions

Le champ « Adresse E2PROM » doit être compris dans la plage indiquée dans [2]. Le nombre d'octets dans le champ « Valeurs » doit être compris entre 1 et 1024 0 (0400x2), inclus. L'opération d'écriture ne doit pas aller au-delà de l'adresse EEPROM comme mentionné dans [2]. La réponse d'erreur doit être envoyée à l'hôte si l'adresse dépasse l'espace d'adressage EEPROM comme dans [XNUMX].

4.5.2.1.2 Commande

Tableau 31. Valeur de la commande WRITE_E2PROM Écrit les valeurs données de manière séquentielle dans E2PROM.

| Champ de charge utile | Longueur | Valeur/description |

| Adresse E2PROM | 2 octets | Adresse dans l'EEPROM à partir de laquelle l'opération d'écriture doit commencer. (Petit endian ) |

| Valeurs | 1 – 1024 octets | Valeurs qui doivent être écrites dans E2PROM dans un ordre séquentiel. |

4.5.2.1.3 Réponse

Tableau 32. Valeur de réponse WRITE_EEPROM

| Champ de charge utile | Longueur | Valeur/Description |

| Statut | 1 octets | Statut de l'opération [Tableau 9]. Les valeurs attendues sont les suivantes : |

| PN5190_STATUS_SUCCESS PN5190_STATUS_INSTR_ERROR PN5190_STATUS_MEMORY_ERROR |

4.5.2.1.4 événement

Il n'y a aucun événement pour cette commande.

4.5.2.2 READ_E2PROM

Cette instruction est utilisée pour relire les données de la zone mémoire E2PROM. Le champ 'E2PROM Address' indique l'adresse de début de l'opération de lecture. La réponse contient les données lues depuis E2PROM.

4.5.2.2.1 conditions

Le champ « Adresse E2PROM » doit être dans une plage valide.

Le champ « Nombre d'octets » doit être compris entre 1 et 256 inclus.

L’opération de lecture ne doit pas dépasser la dernière adresse EEPROM accessible.

La réponse à l'erreur doit être envoyée à l'hôte si l'adresse dépasse l'espace d'adressage EEPROM.

4.5.2.2.2 Commande

Tableau 33. Valeur de la commande READ_E2PROM Lit les valeurs de E2PROM de manière séquentielle.

| Champ de charge utile | Longueur | Valeur/description |

| Adresse E2PROM | 2 octets | Adresse dans E2PROM à partir de laquelle l'opération de lecture doit commencer. (Petit endian ) |

| Nombre d'octets | 2 octets | Nombre d'octets à lire. (Petit endian) |

4.5.2.2.3 Réponse

Tableau 34. Valeur de réponse READ_E2PROM

| Champ de charge utile | Longueur | Valeur/Description |

| Statut | 1 octets | Statut de l'opération [Tableau 9]. Les valeurs attendues sont les suivantes : |

| PN5190_STATUS_SUCCESS | ||

| PN5190_STATUS_INSTR_ERROR (Aucune autre donnée n'est présente) | ||

| Valeurs | 1 – 1024 octets | Valeurs lues dans un ordre séquentiel. |

4.5.2.2.4 événement

Il n'y a aucun événement pour cette commande.

4.5.2.3 GET_CRC_USER_AREA

Cette instruction est utilisée pour calculer le CRC pour la zone de configuration utilisateur complète, y compris la zone de protocole du CI PN5190.

4.5.2.3.1 Commande

Tableau 35. Valeur de la commande GET_CRC_USER_AREA

Lire le CRC de la zone de configuration utilisateur, y compris la zone de protocole.

| Champ de charge utile | Longueur | Valeur/Description |

| – | – | Aucune donnée dans la charge utile |

4.5.2.3.2 Réponse

Tableau 36. Valeur de réponse GET_CRC_USER_AREA

| Champ de charge utile | Longueur | Valeur/description |

| Statut | 1 octets | Statut de l'opération [Tableau 9]. Les valeurs attendues sont les suivantes : |

| PN5190_STATUS_SUCCESS | ||

| PN5190_STATUS_INSTR_ERROR (Aucune autre donnée n'est présente) | ||

| Valeurs | 4 octets | 4 octets de données CRC au format petit-boutiste. |

4.5.2.3.3 événement

Il n'y a aucun événement pour cette commande.

4.5.3 Manipulation des données CLIF

Les instructions décrites dans cette section décrivent les commandes d'émission et de réception RF.

4.5.3.1 EXCHANGE_RF_DATA

La fonction d'échange RF effectue une transmission des données TX et attend la réception d'éventuelles données RX.

La fonction revient en cas de réception (erreur ou correcte) ou d'un timeout. Le temporisateur est démarré avec la FIN de TRANSMISSION et arrêté avec le DÉBUT de RÉCEPTION. La valeur de délai d'attente préconfigurée dans l'EEPROM doit être utilisée dans le cas où le délai d'attente n'est pas configuré avant l'exécution de la commande Exchange.

Si transceiver_state est

- en IDLE, le mode TRANSCEIVE est entré.

- Dans WAIT_RECEIVE, l'état de l'émetteur-récepteur est réinitialisé sur TRANSCEIVE MODE si le bit initiateur est défini.

- Dans WAIT_TRANSMIT, l'état de l'émetteur-récepteur est réinitialisé sur TRANSCEIVE MODE au cas où le bit initiateur n'est PAS défini.

Le champ 'Nombre de bits valides dans le dernier octet' indique la longueur exacte des données à transmettre.

4.5.3.1.1 conditions

La taille du champ « Données TX » doit être comprise entre 0 et 1024 XNUMX inclus.

Le champ « Nombre de bits valides dans le dernier octet » doit être compris entre 0 et 7.

La commande ne doit pas être appelée pendant une transmission RF en cours. La commande doit garantir le bon état de l’émetteur-récepteur pour transmettre les données.

Note:

Cette commande est valable uniquement pour le mode Lecteur et le mode initiateur Passif/Actif P2P.

4.5.3.1.2 Commande

Tableau 37. Valeur de la commande EXCHANGE_RF_DATA

Écrivez les données TX dans le tampon de transmission RF interne et démarrez la transmission à l'aide de la commande d'émission-réception et attendez la réception ou le délai d'attente pour préparer une réponse à l'hôte.

| Champ de charge utile | Longueur | Valeur/Description | |

| Nombre de bits valides dans le dernier octet | 1 octets | 0 | Tous les bits du dernier octet sont transmis |

| 1 – 7 | Nombre de bits dans le dernier octet à transmettre. | ||

| RFExchangeConfig | 1 octets | Configuration de la fonction RFExchange. Détails voir ci-dessous | |

Tableau 37. Valeur de la commande EXCHANGE_RF_DATA…suite

Écrivez les données TX dans le tampon de transmission RF interne et démarrez la transmission à l'aide de la commande d'émission-réception et attendez la réception ou le délai d'attente pour préparer une réponse à l'hôte.

| Champ de charge utile | Longueur | Valeur/Description |

| Données d'émission | n octets | Données TX qui doivent être envoyées via CLIF à l'aide de la commande transceive. n = 0 – 1024 octets |

Tableau 38. Masque de bits RFexchangeConfig

| b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 | Description |

| Les bits 4 à 7 sont des RFU | ||||||||

| X | Inclut les données RX dans la réponse basée sur RX_STATUS, si le bit est défini sur 1b. | |||||||

| X | Incluez le registre EVENT_STATUS en réponse, si le bit est défini sur 1b. | |||||||

| X | Incluez le registre RX_STATUS_ERROR en réponse, si le bit est défini sur 1b. | |||||||

| X | Incluez le registre RX_STATUS en réponse, si le bit est défini sur 1b. |

4.5.3.1.3 Réponse

Tableau 39. Valeur de réponse EXCHANGE_RF_DATA

| Champ de charge utile | Longueur | Valeur/Description |

| Statut | 1 octets | Statut de l'opération [Tableau 9]. Les valeurs attendues sont les suivantes : |

| PN5190_STATUS_INSTR_SUCCESS PN5190_STATUS_INSTR_ERROR (Aucune autre donnée n'est présente) PN5190_STATUS_TIMEOUT PN5190_STATUS_RX_TIMEOUT PN5190_STATUS_NO_RF_FIELD PN5190_STATUS_TIMEOUT_WITH_EMD_ERROR | ||

| RX_STATUS | 4 octets | Si RX_STATUS est demandé (petit-boutiste) |

| RX_STATUS_ERROR | 4 octets | Si RX_STATUS_ERROR est demandé (petit-boutiste) |

| EVENT_STATUS | 4 octets | Si EVENT_STATUS est demandé (petit-boutiste) |

| Données de réception | 1 – 1024 octets | Si des données RX sont demandées. Données RX reçues pendant la phase de réception RF de l'échange RF. |

4.5.3.1.4 événement

Il n'y a aucun événement pour cette commande.

4.5.3.2 TRANSMIT_RF_DATA

Cette instruction est utilisée pour écrire des données dans le tampon de transmission CLIF interne et démarrer la transmission à l'aide de la commande d'émission-réception en interne. La taille de ce tampon est limitée à 1024 octets. Après l'exécution de cette instruction, une réception RF est automatiquement lancée.

La commande revient immédiatement une fois la transmission terminée, sans attendre la fin de la réception.

4.5.3.2.1 conditions

Le nombre d'octets dans le champ « Données TX » doit être compris entre 1 et 1024 XNUMX inclus.

La commande ne doit pas être appelée pendant une transmission RF en cours.

4.5.3.2.2 Commande

Tableau 40. Valeur de commande TRANSMIT_RF_DATA Écrit les données TX dans le tampon de transmission CLIF interne.

| Champ de charge utile | Longueur | Valeur/Description |

| Nombre de bits valides dans le dernier octet | 1 octets | 0 Tous les bits du dernier octet sont transmis. 1 – 7 Nombre de bits du dernier octet à transmettre. |

| RFU | 1 octets | Réservé |

| Données d'émission | 1 – 1024 octets | Données TX qui seront utilisées lors de la prochaine transmission RF. |

4.5.3.2.3 Réponse

Tableau 41. Valeur de réponse TRANSMIT_RF_DATA

| Champ de charge utile | Longueur | Valeur/Description |

| Statut | 1 octets | Statut de l'opération [Tableau 9]. Les valeurs attendues sont les suivantes : |

| PN5190_STATUS_INSTR_SUCCESS PN5190_STATUS_INSTR_ERROR PN5190_STATUS_NO_RF_FIELD PN5190_STATUS_NO_EXTERNAL_RF_FIELD |

4.5.3.2.4 événement

Il n'y a aucun événement pour cette commande.

4.5.3.3 RETRIEVE_RF_DATA

Cette instruction est utilisée pour lire les données du tampon CLIF RX interne, qui contient les données de réponse RF (le cas échéant) qui y ont été publiées lors de l'exécution précédente de la section 4.5.3.1 avec l'option de ne pas inclure les données reçues dans la réponse ou la section 4.5.3.2. .XNUMX commande.

4.5.3.3.1 Commande

Tableau 42. Valeur de la commande RETRIEVE_RF_DATA Lit les données RX à partir du tampon de réception RF interne.

| Champ de charge utile | Longueur | Valeur/Description |

| Vide | Vide | Vide |

4.5.3.3.2 Réponse

Tableau 43. Valeur de réponse RETRIEVE_RF_DATA

| Champ de charge utile | Longueur | Valeur/Description |

| Statut | 1 octets | Statut de l'opération [Tableau 9]. Les valeurs attendues sont les suivantes : |

| Champ de charge utile | Longueur | Valeur/Description |

| PN5190_STATUS_INSTR_SUCCESS PN5190_STATUS_INSTR_ERROR (Aucune autre donnée n'est présente) | ||

| Données de réception | 1 – 1024 octets | Données RX reçues lors de la dernière réception RF réussie. |

4.5.3.3.3 événement

Il n'y a aucun événement pour cette commande.

4.5.3.4 RECEIVE_RF_DATA

Cette instruction attend les données reçues via l'interface RF du lecteur.

En mode lecteur, cette instruction revient soit s'il y a une réception (erreur ou correcte) ou si un timeout FWT s'est produit. Le temporisateur est démarré avec la FIN de TRANSMISSION et arrêté avec le DÉBUT de RÉCEPTION. La valeur de délai d'attente par défaut préconfigurée dans l'EEPROM doit être utilisée dans le cas où le délai d'attente n'est pas configuré avant l'exécution de la commande Exchange.

En mode cible, cette instruction revient soit en cas de réception (erreur ou correcte) ou d'erreur RF externe.

Note:

Cette instruction doit être utilisée avec la commande TRANSMIT_RF_DATA pour effectuer les opérations TX et RX…

4.5.3.4.1 Commande

Tableau 44. Valeur de la commande RECEIVE_RF_DATA

| Champ de charge utile | Longueur | Valeur/Description |

| RecevoirRFConfig | 1 octets | Configuration de la fonction ReceiverRFConfig. Voir Tableau 45 |

Tableau 45. Masque binaire ReceiverRFConfig

| b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 | Description |

| Les bits 4 à 7 sont des RFU | ||||||||

| X | Inclut les données RX dans la réponse basée sur RX_STATUS, si le bit est défini sur 1b. | |||||||

| X | Incluez le registre EVENT_STATUS en réponse, si le bit est défini sur 1b. | |||||||

| X | Incluez le registre RX_STATUS_ERROR en réponse, si le bit est défini sur 1b. | |||||||

| X | Incluez le registre RX_STATUS en réponse, si le bit est défini sur 1b. |

4.5.3.4.2 Réponse

Tableau 46. Valeur de réponse RECEIVE_RF_DATA

| Champ de charge utile | Longueur | Valeur/description |

| Statut | 1 octets | Statut de l'opération [Tableau 9]. Les valeurs attendues sont les suivantes : |

| PN5190_STATUS_INSTR_SUCCESS PN5190_STATUS_INSTR_ERROR (Aucune autre donnée n'est présente) PN5190_STATUS_TIMEOUT |

| Champ de charge utile | Longueur | Valeur/description |

| PN5190_STATUS_NO_RF_FIELD PN5190_STATUS_NO_EXTERNAL_RF_FIELD | ||

| RX_STATUS | 4 octets | Si RX_STATUS est demandé (petit-boutiste) |

| RX_STATUS_ERROR | 4 octets | Si RX_STATUS_ERROR est demandé (petit-boutiste) |

| EVENT_STATUS | 4 octets | Si EVENT_STATUS est demandé (petit-boutiste) |

| Données de réception | 1 – 1024 octets | Si des données RX sont demandées. Données RX reçues via RF. |

4.5.3.4.3 événement

Il n'y a aucun événement pour cette commande.

4.5.3.5 RETRIEVE_RF_FELICA_EMD_DATA (Configuration FeliCa EMD)

Cette instruction est utilisée pour lire les données du tampon CLIF RX interne, qui contient des données de réponse FeliCa EMD (le cas échéant) qui y ont été publiées lors de l'exécution précédente de la commande EXCHANGE_RF_DATA renvoyant avec le statut « PN5190_STATUS_TIMEOUT_WITH_EMD_ERROR ».

Note: Cette commande est disponible à partir du PN5190 FW v02.03.

4.5.3.5.1 Commande

Lisez les données RX à partir du tampon de réception RF interne.

Tableau 47. Valeur de la commande RETRIEVE_RF_FELICA_EMD_DATA

| Champ de charge utile | Longueur | Valeur/Description | |

| FeliCaRFRetrieveConfig | 1 octets | 00 – FF | Configuration de la fonction RETRIEVE_RF_FELICA_EMD_DATA |

| description de la configuration (masque de bits) | bit 7..2 : RFU bit 1 : Inclut le registre RX_STATUS_ERROR en réponse, si le bit est défini sur 1b. bit 0 : inclut le registre RX_STATUS dans la réponse, si le bit est défini sur 1b. | ||

4.5.3.5.2 Réponse

Tableau 48. Valeur de réponse RETRIEVE_RF_FELICA_EMD_DATA

| Champ de charge utile | Longueur | Valeur/description | |||

| Statut | 1 octets | Statut de l'opération. Les valeurs attendues sont les suivantes : PN5190_STATUS_INSTR_SUCCESS PN5190_STATUS_INSTR_ERROR (Aucune autre donnée n'est présente) | |||

| RX_STATUS | 4 octets | Si RX_STATUS est demandé (petit-boutiste) | |||

| RX_STATUS_ ERREUR | 4 octets | Si RX_STATUS_ERROR est demandé (petit-boutiste) | |||

| Champ de charge utile | Longueur | Valeur/description | |||

| Données de réception | 1…1024 octet | Données FeliCa EMD RX reçues lors de la dernière réception RF infructueuse à l'aide de la commande Exchange. | |||

4.5.3.5.3 événement

Il n'y a aucun événement pour cette commande.

4.5.4 Changement de mode de fonctionnement

Le PN5190 prend en charge 4 modes de fonctionnement différents :

4.5.4.1 Normal

C'est le mode par défaut, où toutes les instructions sont autorisées.

4.5.4.2 Veille

Le PN5190 est en état de veille/veille pour économiser de l'énergie. Les conditions de réveil doivent être définies pour définir quand quitter à nouveau le mode veille.

4.5.4.3 LPCD

Le PN5190 est en mode de détection de carte basse consommation, où il tente de détecter une carte qui entre dans le volume de fonctionnement, avec la consommation d'énergie la plus faible possible.

4.5.4.4 Autocollage

Le PN5190 agit comme un écouteur RF, effectuant l'activation du mode cible de manière autonome (pour garantir les contraintes en temps réel)

4.5.4.5 SWITCH_MODE_NORMAL

La commande Switch Mode Normal a trois cas d’utilisation.

4.5.4.5.1 UseCase1 : Passer en mode de fonctionnement normal à la mise sous tension (POR)

Utilisez pour réinitialiser à l'état inactif pour recevoir/traiter la commande suivante en entrant en mode de fonctionnement normal.

4.5.4.5.2 UseCase2 : Terminer une commande déjà en cours d'exécution pour passer en mode de fonctionnement normal (commande d'abandon)

Utilisez pour réinitialiser à l'état inactif pour recevoir/traiter la commande suivante en mettant fin aux commandes déjà en cours d'exécution.

Les commandes telles que Standby, LPCD, Exchange, PRBS et Autocoll doivent pouvoir être terminées à l'aide de cette commande.

C’est la seule commande spéciale qui n’a pas de réponse. Au lieu de cela, il a une notification EVENT.

Reportez-vous à la section 4.4.3 pour plus d'informations sur le type d'événements qui se produisent lors de l'exécution de différentes commandes sous-jacentes.

4.5.4.5.2.1 Cas d'utilisation 2.1 :

Cette commande doit réinitialiser tous les registres CLIF TX, RX et Field Control à l'état de démarrage. L'émission de cette commande désactivera tout champ RF existant.

4.5.4.5.2.2 Cas d'utilisation 2.2 :

Disponible à partir du PN5190 FW v02.03 :

Cette commande ne modifiera pas les registres CLIF TX, RX et de contrôle de champ, mais déplacera uniquement l'émetteur-récepteur vers l'état IDLE.

4.5.4.5.3 UseCase3 : Mode de fonctionnement normal lors d'une réinitialisation logicielle/sortie de veille, LPCD Dans ce cas, le PN5190 entre directement en mode de fonctionnement normal, en envoyant IDLE_EVENT à l'hôte (Figure 12 ou Figure 13) et " Le bit IDLE_EVENT » est défini dans le tableau 11.

Il n'est pas nécessaire d'envoyer la commande SWITCH_MODE_NORMAL.

Note:

Une fois le circuit intégré passé en mode normal, tous les paramètres de RF sont modifiés à leur état par défaut. Il est impératif que la configuration RF respective et les autres registres associés soient chargés avec les valeurs appropriées avant d'effectuer une opération RF ON ou RF Exchange.

4.5.4.5.4 Trame de commande à envoyer pour différents cas d'utilisation

4.5.4.5.4.1 UseCase1 : La commande passe en mode de fonctionnement normal à la mise sous tension (POR) 0x20 0x01 0x00

4.5.4.5.4.2 UseCase2 : commande pour mettre fin aux commandes déjà en cours d'exécution pour passer en mode de fonctionnement normal

Cas d'utilisation 2.1 :

0x20 0x00 0x00

Cas d'utilisation 2.2 : (à partir du FW v02.02) :

0x20 0x02 0x00

4.5.4.5.4.3 UseCase3 : Commande pour le mode de fonctionnement normal lors d'une réinitialisation logicielle/sortie de veille, LPCD, UPCD

Aucun. Le PN5190 entre directement en mode de fonctionnement normal.

4.5.4.5.5 Réponse

Aucun

4.5.4.5.6 événement

Un BOOT_EVENT (dans le registre EVENT_STATUS) est défini pour indiquer que le mode normal est entré et est envoyé à l'hôte. Reportez-vous à la Figure 12 et à la Figure 13 pour les données d'événement.

Un IDLE_EVENT (dans le registre EVENT_STATUS) est défini pour indiquer que le mode normal est entré et est envoyé à l'hôte. Reportez-vous à la Figure 12 et à la Figure 13 pour les données d'événement.

Un BOOT_EVENT (dans le registre EVENT_STATUS) est défini pour indiquer que le mode normal est entré et est envoyé à l'hôte. Reportez-vous à la Figure 12 et à la Figure 13 pour les données d'événement.

4.5.4.6 SWITCH_MODE_AUTOCOLL

Le Switch Mode Autocoll effectue automatiquement la procédure d’activation de la carte en mode cible.

Le champ « Mode Autocoll » doit être compris entre 0 et 2 inclus.

Dans le cas où le champ « Mode Autocoll » est défini sur 2 (Autocoll) : Le champ « Technologies RF » (Tableau 50) doit contenir un masque de bits indiquant les technologies RF à prendre en charge pendant l'Autocoll.

Aucune instruction ne doit être envoyée en étant dans ce mode.

La fin est indiquée par une interruption.

4.5.4.6.1 Commande

Tableau 49. Valeur de la commande SWITCH_MODE_AUTOCOLL

| Paramètre | Longueur | Valeur/Description | |

| Technologies RF | 1 octets | Masque de bits indiquant la technologie RF à écouter lors de l'Autocoll. | |

| Mode de collecte automatique | 1 octets | 0 | Pas de mode autonome, c'est-à-dire qu'Autocoll se termine lorsque le champ RF externe n'est pas présent. |

| Résiliation en cas de | |||

| • NO RF FIELD ou RF FIELD a disparu | |||

| • PN5190 est ACTIVÉ en mode CIBLE | |||

| 1 | Mode autonome avec veille. Lorsqu'aucun champ RF n'est présent, Autocoll entre automatiquement en mode veille. Une fois le champ RF externe RF détecté, le PN5190 entre à nouveau en mode Autocoll. | ||

| Résiliation en cas de | |||

| • PN5190 est ACTIVÉ en mode CIBLE | |||

| À partir du PN5190 FW v02.03 à partir de : Si le champ EEPROM « bCard ModeUltraLowPowerEnabled » à l'adresse « 0xCDF » est réglé sur « 1 », alors le PN5190 entre en veille à très faible consommation. | |||

| 2 | Mode autonome sans veille. Lorsqu'aucun champ RF n'est présent, le PN5190 attend que le champ RF soit présent avant de démarrer l'algorithme Autocoll. La veille n'est pas utilisée dans ce cas. | ||

| Résiliation en cas de • PN5190 est ACTIVÉ en mode CIBLE | |||

Tableau 50. Masque de bits des technologies RF

| b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 | Description |

| 0 | 0 | 0 | 0 | RFU | ||||