UM11942

UM11942

Capa de instrucións PN5190

Controlador frontend NFC

Manual de usuario

Controlador Frontend NFC PN5190

Información do documento

| Información | Contido |

| Palabras chave | PN5190, NFC, NFC frontend, controlador, capa de instrucións |

| Resumo | Este documento describe os comandos e as respostas da capa de instrucións para traballar desde un controlador host, para avaliar o funcionamento do controlador frontend NFC PN5190 NXP. PN5190 é un controlador de frontend NFC de próxima xeración. O alcance deste documento é describir os comandos de interface para traballar co controlador frontend NFC PN5190. Para obter máis información sobre o funcionamento do controlador frontend PN5190 NFC, consulte a ficha técnica e a súa información complementaria. |

Historial de revisións

| Rev | Data | Descrición |

| 3.7 | 20230525 | • O tipo de documento e o título mudáronse do anexo da ficha de datos do produto ao manual de usuario • Limpeza editorial • Termos editoriais actualizados para sinais SPI • Engadiuse o comando GET_CRC_USER_AREA na Táboa 8 da Sección 4.5.2.3 • Actualizáronse varios detalles diferenciados para PN5190B1 e PN5190B2 na sección 3.4.1 • Resposta actualizada da Sección 3.4.7 |

| 3.6 | 20230111 | Descrición mellorada da resposta de verificación de integridade na sección 3.4.7 |

| 3.5 | 20221104 | Sección 4.5.4.6.3 «Evento»: engadido |

| 3.4 | 20220701 | • Engadiuse o comando CONFIGURE_MULTIPLE_TESTBUS_DIGITAL na Táboa 8 da Sección 4.5.9.3 • Sección actualizada 4.5.9.2.2 |

| 3.3 | 20220329 | A descrición do hardware mellorou na Sección 4.5.12.2.1 "Comando" e na Sección 4.5.12.2.2 "Resposta" |

| 3.2 | 20210910 | Números de versión de firmware actualizados de 2.1 a 2.01 e 2.3 a 2.03 |

| 3.1 | 20210527 | Engadiuse a descrición do comando RETRIEVE_RF_FELICA_EMD_DATA |

| 3 | 20210118 | Primeira versión oficial publicada |

Introdución

1.1 Introdución

Este documento describe a interface de host PN5190 e as API. A interface de host físico utilizada na documentación é SPI. A característica física SPI non se considera no documento.

A separación de cadros e o control de fluxo forman parte deste documento.

1.1.1 Ámbito

O documento describe a capa lóxica, o código de instrucións e as API que son relevantes para o cliente.

Rematou a comunicación do anfitriónview

PN5190 ten dous modos principais de operación para comunicarse co controlador host.

- A comunicación baseada en HDLL úsase cando o dispositivo se activa para introducir:

a. Modo de descarga segura cifrada para actualizar o seu firmware - Comunicación baseada en comandos-respostas TLV (dada como un example).

Modo HDLL 2.1

O modo HDLL úsase para que o formato de intercambio de paquetes funcione cos seguintes modos operativos de IC:

- Modo de descarga de firmware seguro (SFWU), consulte a Sección 3

2.1.1 Descrición de HDLL

HDLL é a capa de ligazón desenvolvida por NXP para garantir unha descarga de FW fiable.

Unha mensaxe HDLL está formada por unha cabeceira de 2 bytes, seguida dunha trama, que comprende o código de operación e a carga útil do comando. Cada mensaxe remata cun CRC de 16 bits, como se describe na seguinte imaxe: A cabeceira HDLL contén:

A cabeceira HDLL contén:

- Un anaco. O que indica se esta mensaxe é o único ou o último fragmento dunha mensaxe (anaco = 0). Ou se, polo menos, segue outro anaco (anaco = 1).

- A lonxitude da carga útil codificada en 10 bits. Entón, a carga útil do marco HDLL pode ir ata 1023 bytes.

A orde de bytes definiuse como big-endian, é dicir, Ms Byte primeiro.

O CRC16 cumpre co estándar X.25 (CRC-CCITT, ISO/IEC13239) co polinomio x^16 + x^12 + x^5 +1 e o valor de precarga 0xFFFF.

Calcúlase sobre todo o cadro HDLL, é dicir, Cabeceira + Cadro.

SampImplementación do código C:

static uint16_t phHal_Host_CalcCrc16(uint8_t* p, uint32_t dwLength)

{

uint32_t i ;

uint16_t crc_new ;

uint16_t crc = 0xffffU;

para (I = 0; i < dwLonxitude; i++)

{

crc_new = (uint8_t)(crc >> 8) | (crc << 8);

crc_new ^= p[i];

crc_new ^= (uint8_t)(crc_new & 0xff) >> 4;

crc_new ^= crc_new << 12;

crc_new ^= (crc_new & 0xff) << 5;

crc = crc_new;

}

devolver crc;

}

2.1.2 Mapeo de transporte sobre o SPI

Para cada afirmación NTS, o primeiro byte é sempre un HEADER (byte de indicación de fluxo), pode ser 0x7F/0xFF con respecto á operación de escritura/lectura.

2.1.2.1 Secuencia de escritura desde o host (dirección DH => PN5190) 2.1.2.2 Ler a secuencia do host (Dirección PN5190 => DH)

2.1.2.2 Ler a secuencia do host (Dirección PN5190 => DH) 2.1.3 Protocolo HDLL

2.1.3 Protocolo HDLL

HDLL é un protocolo de resposta de comandos. Todas as operacións mencionadas anteriormente son activadas a través dun comando específico e validadas en función da resposta.

Os comandos e as respostas seguen a sintaxe da mensaxe HDLL, o comando envía o host do dispositivo e a resposta polo PN5190. O código de operación indica o tipo de comando e resposta.

Comunicacións baseadas en HDLL, só se usan cando se activa o PN5190 para entrar no modo "Descarga segura de firmware".

2.2 Modo TLV

TLV significa Tag Valor de lonxitude.

2.2.1 Definición do marco

Un cadro SPI comeza co bordo descendente de NTS e remata co bordo ascendente de NTS. SPI é dúplex completo por definición física, pero PN5190 usa SPI nun modo semidúplex. O modo SPI está limitado a CPOL 0 e CPHA 0 cunha velocidade de reloxo máxima como se especifica en [2]. Cada trama SPI está composta por unha cabeceira de 1 byte e un corpo de n bytes.

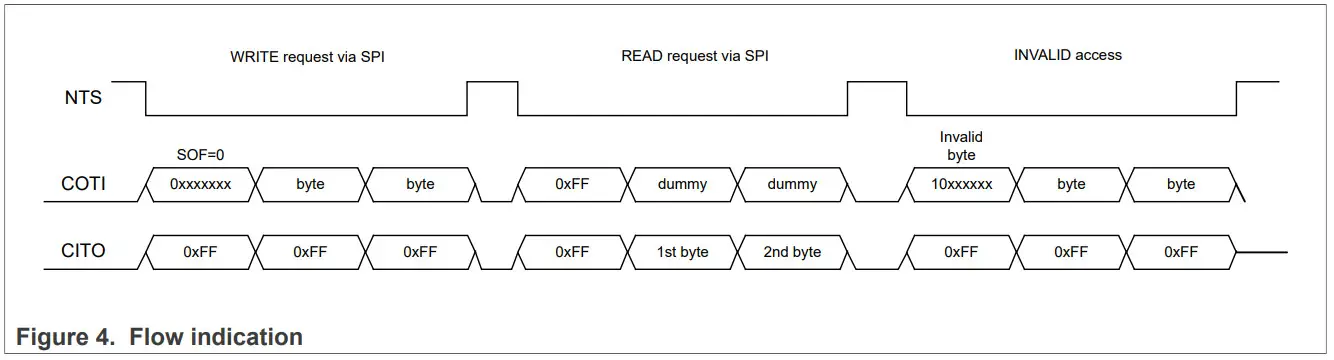

2.2.2 Indicación de caudal O HOST sempre envía como primeiro byte o byte de indicación de fluxo, tanto se quere escribir como ler datos do PN5190.

O HOST sempre envía como primeiro byte o byte de indicación de fluxo, tanto se quere escribir como ler datos do PN5190.

Se hai unha solicitude de lectura e non hai datos dispoñibles, a resposta contén 0xFF.

Os datos despois do byte de indicación de fluxo son unha ou varias mensaxes.

Para cada afirmación NTS, o primeiro byte é sempre un HEADER (byte de indicación de fluxo), pode ser 0x7F/0xFF con respecto á operación de escritura/lectura.

2.2.3 Tipo de mensaxe

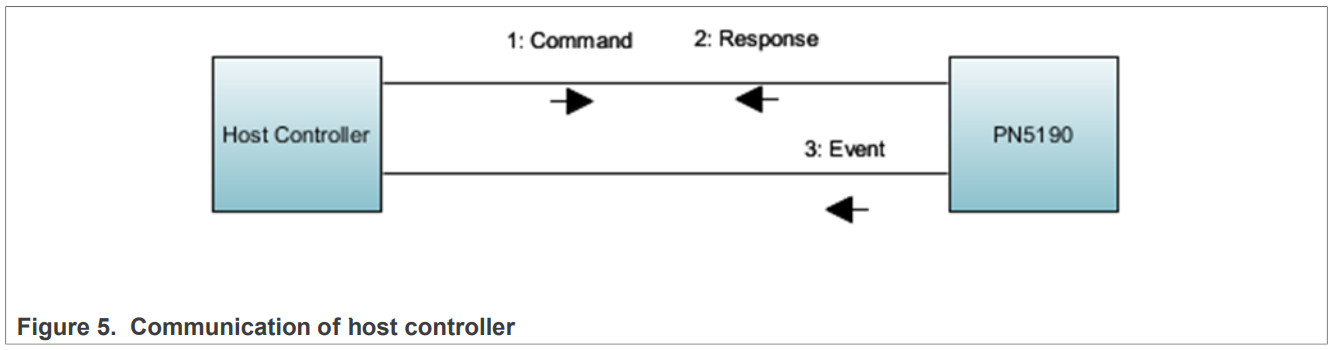

Un controlador host debe comunicarse con PN5190 mediante mensaxes que se transportan dentro de tramas SPI.

Hai tres tipos de mensaxes diferentes:

- Comando

- Resposta

- Evento

O diagrama de comunicación anterior mostra as indicacións permitidas para os diferentes tipos de mensaxes como se indica a continuación:

O diagrama de comunicación anterior mostra as indicacións permitidas para os diferentes tipos de mensaxes como se indica a continuación:

- Mando e resposta.

- Os comandos só se envían desde o controlador host a PN5190.

- As respostas e os eventos só se envían desde PN5190 ao controlador anfitrión.

- As respostas aos comandos sincronízanse mediante o pin IRQ.

- O host só pode enviar os comandos cando o IRQ é baixo.

- O host só pode ler a resposta/evento cando o IRQ é alto.

2.2.3.1 Secuencias e regras permitidas Secuencias permitidas de comandos, respostas e eventos

Secuencias permitidas de comandos, respostas e eventos

- Un comando sempre se recoñece mediante unha resposta, ou un evento ou ambos.

- O controlador do host non ten permiso para enviar outro comando antes de non ter recibido unha resposta ao comando anterior.

- Os eventos poden enviarse de forma asíncrona en calquera momento (NON intercalados nun par comando/resposta).

- As mensaxes de EVENTO nunca se combinan coas mensaxes de RESPOSTA nun marco.

Nota: A dispoñibilidade dunha mensaxe (xa sexa RESPOSTA ou EVENTO) sinalizarase co IRQ en alto, desde o baixo. O IRQ permanece alto ata que se le toda a resposta ou o cadro de eventos. Só despois de que o sinal IRQ sexa baixo, o host pode enviar o seguinte comando.

2.2.4 Formato da mensaxe

Cada mensaxe está codificada nunha estrutura TLV con carga útil de n bytes para cada mensaxe excepto o comando SWITCH_MODE_NORMAL. Cada TLV está composto por:

Cada TLV está composto por: Tipo (T) => 1 byte

Tipo (T) => 1 byte

Bit[7] Tipo de mensaxe

0: Mensaxe de COMANDO ou RESPOSTA

1: Mensaxe de EVENTO

Bit[6:0]: código de instrución

Lonxitude (L) => 2 bytes (debe estar en formato big-endian)

Valor (V) => N bytes de valor/datos do TLV (parámetros de comando/datos de resposta) en función do campo de lonxitude (formato big-endian)

2.2.4.1 Dividir marco

A mensaxe COMMAND debe enviarse nun marco SPI.

As mensaxes de RESPOSTA e EVENTO pódense ler en varios cadros SPI, por exemplo, para ler o byte de lonxitude. As mensaxes de RESPOSTA ou de EVENTO pódense ler nunha única fotograma SPI pero atrasadas por NO-CLOCK no medio, por exemplo, para ler o byte de lonxitude.

As mensaxes de RESPOSTA ou de EVENTO pódense ler nunha única fotograma SPI pero atrasadas por NO-CLOCK no medio, por exemplo, para ler o byte de lonxitude.

Modo de arranque operativo IC: modo de descarga de FW seguro

3.1 Introdución

Parte do código do firmware PN5190 almacénase permanentemente na ROM, mentres que o resto do código e os datos gárdanse no flash incorporado. Os datos do usuario gárdanse en flash e están protexidos por mecanismos anti-ruptura que garanten a integridade e dispoñibilidade dos datos. Para ofrecer aos clientes de NXP funcións que cumpran cos estándares máis recentes (EMVCo, NFC Forum, etc.), pódense actualizar tanto o código como os datos do usuario en FLASH.

A autenticidade e integridade do firmware cifrado está protexida pola firma de chave asimétrica/simétrica e un mecanismo de hash encadeado inverso. O primeiro comando DL_SEC_WRITE contén o hash do segundo comando e está protexido por unha sinatura RSA na carga útil do primeiro cadro. O firmware PN5190 usa a clave pública RSA para autenticar o primeiro comando. O hash encadeado en cada comando úsase para autenticar o comando posterior, para garantir que terceiros non accedan ao código e aos datos do firmware.

As cargas útiles dos comandos DL_SEC_WRITE están cifradas cunha clave AES-128. Despois da autenticación de cada comando, o contido da carga útil é descifrado e escríbese para flash mediante o firmware PN5190.

Para o firmware de NXP, NXP encárgase de ofrecer novas actualizacións seguras de firmware, xunto con novos datos de usuario.

O procedemento de actualización está equipado cun mecanismo para protexer a autenticidade, integridade e confidencialidade do código e dos datos NXP.

O esquema de paquetes de trama baseado en HDLL utilízase para todos os comandos e respostas para o modo de actualización de firmware seguro.

A Sección 2.1 ofrece o máisview do esquema de paquetes de tramas HDLL usado.

Os circuitos integrados PN5190 admiten tanto o protocolo de descarga segura de FW cifrado herdado como o protocolo de descarga segura de FW cifrado asistido por hardware criptográfico, dependendo da variante utilizada.

Os dous tipos son:

- Protocolo de descarga de FW seguro herdado que só funciona coa versión PN5190 B0/B1 IC.

- Protocolo de descarga segura FW asistida por hardware criptográfico que só funciona coa versión PN5190B2 IC, que usa os bloques criptográficos de hardware no chip

As seguintes seccións explican os comandos e respostas do modo de descarga de firmware seguro.

3.2 Como activar o modo "Descarga de firmware segura".

O diagrama a continuación e os pasos posteriores mostran como activar o modo de descarga de firmware seguro. Condición previa: PN5190 está en estado operativo.

Condición previa: PN5190 está en estado operativo.

Escenario principal:

- Condición de entrada na que se usa o pin DWL_REQ para acceder ao modo "Descarga de firmware segura".

a. O host do dispositivo leva o pin DWL_REQ alto (válido só se a actualización segura do firmware a través do pin DWL_REQ) OU

b. O host do dispositivo realiza un restablecemento completo para iniciar o PN5190 - Condición de entrada na que o pin DWL_REQ non se utiliza para entrar no modo "Descarga de firmware segura" (descarga sen pin).

a. O host do dispositivo realiza un restablecemento completo para iniciar o PN5190

b. O host do dispositivo envía SWITCH_MODE_NORMAL (sección 4.5.4.5) para entrar no modo de aplicación normal.

c. Agora, cando IC está no modo normal de aplicación, o host do dispositivo envía SWITCH_MODE_DOWNLOAD (sección 4.5.4.9) para entrar no modo de descarga segura. - O host do dispositivo envía o comando DL_GET_VERSION (sección 3.4.4) ou DL_GET_DIE_ID (sección 3.4.6) ou DL_GET_SESSION_STATE (sección 3.4.5).

- O host do dispositivo le a versión actual de hardware e firmware, sesión, Die-id do dispositivo.

a. O host do dispositivo comproba o estado da sesión se se completou a última descarga

b. O host do dispositivo aplica as regras de comprobación de versións para decidir se se inicia a descarga ou se sae da descarga. - O host do dispositivo carga desde a file o código binario do firmware que se vai descargar

- O host do dispositivo proporciona un primeiro comando DL_SEC_WRITE (Sección 3.4.8) que contén:

a. A versión do novo firmware,

b. Un nonce de 16 bytes de valores arbitrarios usado para ofuscar a chave de cifrado

c. Un valor de resumo do seguinte fotograma,

d. A sinatura dixital do propio cadro - O host do dispositivo carga a secuencia do protocolo de descarga segura no PN5190 con comandos DL_SEC_WRITE (sección 3.4.8)

- Cando se enviou o último comando DL_SEC_WRITE (Sección 3.4.8), o host do dispositivo executa o comando DL_CHECK_INTEGRITY (Sección 3.4.7) para comprobar se as memorias foron escritas correctamente.

- O host do dispositivo le a nova versión de firmware e verifica o estado da sesión se está pechada para informar á capa superior

- O host do dispositivo baixa o pin DWL_REQ (se se usa o pin DWL_REQ para entrar no modo de descarga)

- O host do dispositivo realiza un restablecemento completo (alternando o pin VEN) no dispositivo para reiniciar o PN5190

Condición posterior: o firmware está actualizado; infórmase do novo número de versión do firmware.

3.3 Sinatura de firmware e control de versións

No modo de descarga de firmware PN5190, un mecanismo garante que só se aceptará un firmware asinado e entregado por NXP para o firmware NXP.

O seguinte só é aplicable ao firmware NXP seguro cifrado.

Durante unha sesión de descarga, envíase unha nova versión de firmware de 16 bits. Está composto por un número maior e un número menor:

- Número principal: 8 bits (MSB)

- Número menor: 8 bits (LSB)

O PN5190 comproba se o novo número de versión principal é maior ou igual ao actual. Se non é así, a descarga segura do firmware é rexeitada e a sesión permanecerá pechada.

3.4 Comandos HDLL para descargas cifradas heredadas e asistido por hardware criptográfico descarga cifrada

Esta sección ofrece información sobre os comandos e respostas que se utilizaron para ambos os tipos de descargas para a descarga do firmware NXP.

3.4.1 Códigos OP de comandos HDLL

Nota: Os marcos de comandos HDLL están aliñados en 4 bytes. Os bytes de carga útil non utilizados quedan nulos.

Táboa 1. Lista de códigos OP de comandos HDLL

| PN5190 B0/ B1 (Descarga legado) |

PN5190 B2 (Descarga asistida por criptomonedas) |

Alias de comando | Descrición |

| 0xF0 | 0xE5 | DL_RESET | Realiza un reinicio suave |

| 0xF1 | 0xE1 | DL_GET_VERSION | Devolve os números de versión |

| 0xF2 | 0xDB | DL_GET_SESSION_STATE | Devolve o estado da sesión actual |

| 0xF4 | 0xDF | DL_GET_DIE_ID | Devolve o ID da matriz |

| 0xE0 | 0xE7 | DL_CHECK_INTEGRITY | Comproba e devolve os CRC nas diferentes áreas, así como as bandeiras de estado de aprobación/falla para cada unha |

| 0xC0 | 0x8C | DL_SEC_WRITE | Escribe x bytes na memoria comezando no enderezo absoluto y |

3.4.2 Códigos de operación de resposta HDLL

Nota: Os marcos de resposta HDLL están aliñados en 4 bytes. Os bytes de carga útil non utilizados quedan nulos. Só as respostas DL_OK poden conter valores de carga útil.

Táboa 2. Lista de códigos OP de resposta HDLL

| Opcode | Alias de resposta | Descrición |

| 0x00 | DL_OK | O comando pasou |

| 0x01 | DL_INVALID_ADDR | Enderezo non permitido |

| 0x0B | DL_UNKNOW_CMD | Comando descoñecido |

| 0x0C | DL_ABORTED_CMD | A secuencia de fragmentos é demasiado grande |

| 0x1E | DL_ADDR_RANGE_OFL_ERROR | Enderezo fóra do rango |

| 0x1F | DL_BUFFER_OFL_ERROR | O tampón é demasiado pequeno |

| 0x20 | DL_MEM_BSY | Memoria ocupada |

| 0x21 | DL_SIGNATURE_ERROR | Desaxuste de sinatura |

| 0x24 | DL_FIRMWARE_VERSION_ERROR | Versión actual igual ou superior |

| 0x28 | DL_PROTOCOL_ERROR | Erro de protocolo |

| 0x2A | DL_SFWU_DEGRADED | Corrupción de datos de flash |

| 0x2D | PH_STATUS_DL_FIRST_CHUNK | Primeiro anaco recibido |

| 0x2E | PH_STATUS_DL_NEXT_CHUNK | Agarda o seguinte anaco |

| 0xC5 | PH_STATUS_INTERNAL_ERROR_5 | Desaxuste de lonxitude |

3.4.3 Comando DL_RESET

Intercambio de cadros:

PN5190 B0/B1: [HDLL] -> [0x00 0x04 0xF0 0x00 0x00 0x00 0x18 0x5B]

PN5190 B2: [HDLL] -> [0x00 0x04 0xE5 0x00 0x00 0x00 0xBF 0xB9] [HDLL] <- [0x00 0x04 STAT 0x00 CRC16] O reinicio impide que o PN5190 envíe a resposta DL_STATUS_OK. Polo tanto, só se pode recibir o estado erróneo.

STAT é o estado de retorno.

3.4.4 Comando DL_GET_VERSION

Intercambio de cadros:

PN5190 B0/B1: [HDLL] -> [0x00 0x04 0xF1 0x00 0x00 0x00 0x6E 0xEF]

PN5190 B2: [HDLL] -> [0x00 0x04 0xE1 0x00 0x00 0x00 0x75 0x48] [HDLL] <- [0x00 0x08 STAT HW_V RO_V MODEL_ID FM1V FM2V RFU1 RFU2 CRC16 cadro de carga útil Get TheVersion é:]

Táboa 3. Resposta ao comando GetVersion

| Campo | Byte | Descrición |

| STAT | 1 | Estado |

| HW_V | 2 | Versión de hardware |

| RO_V | 3 | código ROM |

| MODEL_ID | 4 | ID do modelo |

| FMxV | 5-6 | Versión de firmware (utilizada para descargar) |

| RFU1-RFU2 | 7-8 | – |

Os valores esperados de diferentes campos de resposta e a súa asignación son os seguintes:

Táboa 4. Valores esperados da resposta do comando GetVersion

| Tipo IC | Versión HW (hexadecimal) | Versión ROM (hexadecimal) | ID do modelo (hexadecimal) | Versión FW (hexadecimal) |

| PN5190 B0 | 0x51 | 0x02 | 0x00 | xx.aa |

| PN5190 B1 | 0x52 | 0x02 | 0x00 | xx.aa |

| PN5190 B2 | 0x53 | 0x03 | 0x00 | xx.aa |

3.4.5 Comando DL_GET_SESSION_STATE

Intercambio de cadros:

PN5190 B0/B1: [HDLL] -> [0x00 0x04 0xF2 0x00 0x00 0x00 0xF5 0x33]

PN5190 B2: [HDLL] -> [0x00 0x04 0xDB 0x00 0x00 0x00 0x31 0x0A] [HDLL] <- [0x00 0x04 STAT SSTA RFU CRC16] O marco de carga útil da resposta GetSession é:

Táboa 5. Resposta ao comando GetSession

| Campo | Byte | Descrición |

| STAT | 1 | Estado |

| SSTA | 2 | Estado da sesión • 0x00: pechado • 0x01: aberto • 0x02: bloqueado (non se permite máis descargas) |

| RFU | 3-4 |

3.4.6 Comando DL_GET_DIE_ID

Intercambio de cadros:

PN5190 B0/B1: [HDLL] -> [0x00 0x04 0xF4 0x00 0x00 0x00 0xD2 0xAA]

PN5190 B2: [HDLL] -> [0x00 0x04 0xDF 0x00 0x00 0x00 0xFB 0xFB] [HDLL] <- [0x00 0x14 STAT 0x00 0x00 0x00 ID0 ID1 ID2 ID3 ID4 ID5 ID6 ID7 ID8 ID9

ID10 ID11 ID12 ID13 ID14 ID15 CRC16] O marco de carga útil da resposta GetDieId é:

Táboa 6. Resposta ao comando GetDieId

| Campo | Byte | Descrición |

| STAT | 1 | Estado |

| RFU | 2-4 | |

| DIEID | 5-20 | ID do dado (16 bytes) |

3.4.7 Comando DL_CHECK_INTEGRITY

Intercambio de cadros:

PN5190 B0/B1: [HDLL] -> [0x00 0x04 0xE0 0x00 0x00 0x00 CRC16]

PN5190 B2: [HDLL] -> [0x00 0x04 0xE7 0x00 0x00 0x00 0x52 0xD1] [HDLL] <- [0x00 0x20 STAT LEN_DATA LEN_CODE 0x00 [CRC_INFO] [CRC32] O cadro de carga útil da resposta é o CRC16 CheckIn:

Táboa 7. Resposta ao comando CheckIntegrity

| Campo | Byte | Valor/Descrición | |

| STAT | 1 | Estado | |

| DATOS LEN | 2 | Número total de seccións de datos | |

| CÓDIGO LEN | 3 | Número total de seccións de código | |

| RFU | 4 | Reservado | |

| [CRC_INFO] | 58 | 32 bits (little-endian). Se se establece un bit, o CRC da sección correspondente está ben, se non, non está correcto. | |

| Bit | Estado de integridade da área | ||

| [31:28] | Reservado [3] | ||

| [27:23] | Reservado [1] | ||

| [22] | Reservado [3] | ||

| [21:20] | Reservado [1] | ||

| [19] | Área de configuración de RF (PN5190 B0/B1) [2] Reservado (PN5190 B2) [3] | ||

| [18] | Área de configuración de protocolo (PN5190 B0/B1) [2] Área de configuración de RF (PN5190 B2) [2] | ||

| [17] | Reservado (PN5190 B0/B1) [3] Área de configuración de usuario (PN5190 B2) [2] | ||

| [16:6] | Reservado [3] | ||

| [5:4] | Reservado para PN5190 B0/B1 [3] Reservado para PN5190 B2 [1] | ||

| [3:0] | Reservado [1] | ||

| [CRC32] | 9-136 | CRC32 das 32 seccións. Cada CRC é de 4 bytes almacenados en formato little-endian. Os primeiros 4 bytes de CRC son do bit CRC_INFO[31], os seguintes 4 bytes de CRC son do bit CRC_INFO[30] e así por diante. |

|

- [1] Este bit debe ser 1 para que o PN5190 funcione correctamente (con funcións ou descarga de firmware cifrada).

- [2] Este bit está configurado en 1 por defecto, pero a configuración modificada polo usuario invalida o CRC. Sen efecto na funcionalidade PN5190.

- [3] Este valor de bit, aínda que sexa 0, non é relevante. Este valor de bit pódese ignorar.

3.4.8 Comando DL_SEC_WRITE

O comando DL_SEC_WRITE debe considerarse no contexto dunha secuencia de comandos de escritura segura: a "descarga de firmware segura" cifrada (a miúdo denominada eSFWu).

O comando de escritura segura abre primeiro a sesión de descarga e pasa a autenticación RSA. Os seguintes pasan enderezos e bytes cifrados para escribir no PN5190 Flash. Todos menos o último contén o hash dos seguintes, polo que se informa que non son os últimos e se unen criptograficamente os fotogramas de secuencia.

Outros comandos (excepto DL_RESET e DL_CHECK_INTEGRITY) pódense inserir entre os comandos de escritura protexidos dunha secuencia sen rompela.

3.4.8.1 Primeiro comando DL_SEC_WRITE

Un comando de escritura segura é o primeiro se e só se:

- A lonxitude do cadro é de 312 bytes

- Non se recibiu ningún comando de escritura segura desde o último restablecemento.

- O PN5190 verifica a sinatura integrada correctamente.

A resposta ao primeiro comando de fotograma sería a seguinte: [HDLL] <- [0x00 0x04 STAT 0x00 0x00 0x00 CRC16] STAT é o estado de retorno.

Nota: Debe escribirse polo menos un anaco de datos durante un eSFWu aínda que os datos escritos só teñan un byte. Polo tanto, o primeiro comando sempre conterá o hash do seguinte comando, xa que haberá polo menos dous comandos.

3.4.8.2 Comandos DL_SEC_WRITE intermedios

Un comando de escritura segura é un "intermedio" se e só se:

- O código de operación é o descrito na Sección 3.4.1 para o comando DL_SEC_WRITE.

- Xa se recibiu un primeiro comando de escritura segura e xa se verificou con éxito antes

- Non se produciu ningún reinicio desde que recibiu o primeiro comando de escritura segura

- A lonxitude do cadro é igual ao tamaño dos datos + tamaño da cabeceira + tamaño hash: FLEN = SIZE + 6 + 32

- O resumo de todo o fotograma é igual ao valor hash recibido no fotograma anterior

A resposta ao primeiro comando de fotograma sería a seguinte: [HDLL] <- [0x00 0x04 STAT 0x00 0x00 0x00 CRC16] STAT é o estado de retorno.

3.4.8.3 Último comando DL_SEC_WRITE

Un comando de escritura segura é o último se e só se:

- O código de operación é o descrito na Sección 3.4.1 para o comando DL_SEC_WRITE.

- Xa se recibiu un primeiro comando de escritura segura e xa se verificou con éxito antes

- Non se produciu ningún reinicio desde que recibiu o primeiro comando de escritura segura

- A lonxitude do cadro é igual ao tamaño dos datos + tamaño da cabeceira: FLEN = SIZE + 6

- O resumo de todo o fotograma é igual ao valor hash recibido no fotograma anterior

A resposta ao primeiro comando de fotograma sería a seguinte: [HDLL] <- [0x00 0x04 STAT 0x00 0x00 0x00 CRC16] STAT é o estado de retorno.

Modo de arranque operativo IC: modo de operación normal

4.1 Introdución

Xeralmente PN5190 IC debe estar en modo normal de operación para obter a funcionalidade NFC del.

Cando se inicia o PN5190 IC, sempre está esperando a que se reciban comandos dun host para realizar a operación, a non ser que os eventos xerados no PN5190 IC dean como resultado o arranque do PN5190 IC.

4.2 Lista de comandos completadaview

Táboa 8. Lista de comandos PN5190

| Código de comando | Nome do comando |

| 0x00 | WRITE_REGISTER |

| 0x01 | WRITE_REGISTER_OR_MASK |

| 0x02 | WRITE_REGISTER_AND_MASK |

| 0x03 | WRITE_REGISTER_MULTIPLE |

| 0x04 | READ_REGISTER |

| 0x05 | READ_REGISTER_MULTIPLE |

| 0x06 | WRITE_E2PROM |

| 0x07 | READ_E2PROM |

| 0x08 | TRANSMIT_RF_DATA |

| 0x09 | RETRIEVE_RF_DATA |

| 0x0A | EXCHANGE_RF_DATA |

| 0x0B | MFC_AUTHENTICATE |

| 0x0C | EPC_GEN2_INVENTORY |

| 0x0D | LOAD_RF_CONFIGURACIÓN |

| 0x0E | UPDATE_RF_CONFIGURACIÓN |

| 0x0F | GET_ RF_CONFIGURACIÓN |

| 0x10 | RF_ON |

| 0x11 | RF_OFF |

| 0x12 | CONFIGURAR TESTBUS_DIGITAL |

| 0x13 | CONFIGURE_TESTBUS_ANALOG |

| 0x14 | CTS_ENABLE |

| 0x15 | CTS_CONFIGURE |

| 0x16 | CTS_RETRIEVE_LOG |

| 0x17-0x18 | RFU |

| 0x19 | ata FW v2.01: RFU |

| a partir de FW v2.03 en diante: RETRIEVE_RF_FELICA_EMD_DATA | |

| 0x1A | RECEIVE_RF_DATA |

| 0x1B-0x1F | RFU |

| 0x20 | SWITCH_MODE_NORMAL |

| 0x21 | SWITCH_MODE_AUTOCOLL |

| 0x22 | SWITCH_MODE_STANDBY |

| 0x23 | SWITCH_MODE_LPCD |

| 0x24 | RFU |

| 0x25 | SWITCH_MODE_DOWNLOAD |

| 0x26 | GET_DIEID |

| 0x27 | GET_VERSION |

| 0x28 | RFU |

| 0x29 | ata FW v2.05: RFU |

| a partir de FW v2.06 en diante: GET_CRC_USER_AREA | |

| 0x2A | ata FW v2.03: RFU |

| desde FW v2.05 en diante: CONFIGURE_MULTIPLE_TESTBUS_DIGITAL | |

| 0x2B-0x3F | RFU |

| 0x40 | ANTENNA_SELF_TEST (non compatible) |

| 0x41 | PRBS_TEST |

| 0x42-0x4F | RFU |

4.3 Valores de estado de resposta

A continuación móstranse os valores de estado da resposta, que se devolven como parte da resposta de PN5190 despois de que o comando sexa operativo.

Táboa 9. Valores de estado de resposta PN5190

| Estado da resposta | Valor do estado da resposta | Descrición |

| PN5190_STATUS_SUCCESS | 0x00 | Indica que a operación se realizou correctamente |

| PN5190_STATUS_TIMEOUT | 0x01 | Indica que a operación do comando provocou o tempo de espera |

| PN5190_STATUS_INTEGRITY_ERROR | 0x02 | Indica que a operación do comando deu lugar a un erro de integridade dos datos de RF |

| PN5190_STATUS_RF_COLLISION_ERROR | 0x03 | Indica que a operación do comando deu lugar a un erro de colisión de RF |

| PN5190_STATUS_RFU1 | 0x04 | Reservado |

| PN5190_STATUS_INVALID_COMMAND | 0x05 | Indica que o comando dado non é válido/non está implementado |

| PN5190_STATUS_RFU2 | 0x06 | Reservado |

| PN5190_STATUS_AUTH_ERROR | 0x07 | Indica que fallou a autenticación MFC (permiso denegado) |

| PN5190_STATUS_MEMORY_ERROR | 0x08 | Indica que a operación do comando deu lugar a un erro de programación ou un erro de memoria interna |

| PN5190_STATUS_RFU4 | 0x09 | Reservado |

| PN5190_STATUS_NO_RF_FIELD | 0x0A | Indica que non hai ou hai un erro na presenza do campo RF interno (aplicable só no modo iniciador/lector) |

| PN5190_STATUS_RFU5 | 0x0B | Reservado |

| PN5190_STATUS_SYNTAX_ERROR | 0x0C | Indica que se recibe unha lonxitude de cadro de comando non válida |

| PN5190_STATUS_RESOURCE_ERROR | 0x0D | Indica que se produciu un erro de recurso interno |

| PN5190_STATUS_RFU6 | 0x0E | Reservado |

| PN5190_STATUS_RFU7 | 0x0F | Reservado |

| PN5190_STATUS_NO_EXTERNAL_RF_FIELD | 0x10 | Indica que non hai ningún campo RF externo presente durante a execución do comando (aplicable só no modo tarxeta/obxectivo) |

| PN5190_STATUS_RX_TIMEOUT | 0x11 | Indica que non se reciben datos despois de que se inicie RFExchange e que se agote o tempo de espera de RX. |

| PN5190_STATUS_USER_CANCELLED | 0x12 | Indica que o comando actual en curso está abortado |

| PN5190_STATUS_PREVENT_STANDBY | 0x13 | Indica que o PN5190 non pode entrar en modo de espera |

| PN5190_STATUS_RFU9 | 0x14 | Reservado |

| PN5190_STATUS_CLOCK_ERROR | 0x15 | Indica que o reloxo do CLIF non se iniciou |

| PN5190_STATUS_RFU10 | 0x16 | Reservado |

| PN5190_STATUS_PRBS_ERROR | 0x17 | Indica que o comando PRBS devolveu un erro |

| PN5190_STATUS_INSTR_ERROR | 0x18 | Indica que a operación do comando fallou (pode incluír o erro nos parámetros da instrución, o erro de sintaxe, o erro na propia operación, non se cumpren os requisitos previos para a instrución, etc.) |

| PN5190_STATUS_ACCESS_DENIED | 0x19 | Indica que o acceso á memoria interna está denegado |

| PN5190_STATUS_TX_FAILURE | 0x1A | Indica que TX sobre RF fallou |

| PN5190_STATUS_NO_ANTENNA | 0x1B | Indica que non hai antena conectada/presente |

| PN5190_STATUS_TXLDO_ERROR | 0x1C | Indica que hai un erro en TXLDO cando o VUP non está dispoñible e a RF está activada. |

| PN5190_STATUS_RFCFG_NOT_APPLIED | 0x1D | Indica que a configuración de RF non se carga cando a RF está activada |

| PN5190_STATUS_TIMEOUT_WITH_EMD_ERROR | 0x1E | ata FW 2.01: non se espera |

| dende o FW 2.03 en diante: Indica que durante o intercambio con LOG ENABLE BIT está configurado no rexistro FeliCa EMD, observouse un erro FeliCa EMD |

||

| PN5190_STATUS_INTERNAL_ERROR | 0x7F | Indica que fallou a operación NVM |

| PN5190_STATUS_SUCCSES_CHAINING | 0xAF | Indica que, ademais, hai datos pendentes de ler |

4.4 Eventos rematadosview

Hai dúas formas de notificar os eventos ao anfitrión.

4.4.1 Eventos normais sobre o pin IRQ

Estes eventos son as seguintes categorías:

- Sempre activado: o host sempre recibe unha notificación

- Controlado polo anfitrión: o host recibe unha notificación se o bit de habilitación de eventos respectivo está definido no rexistro (EVENT_ENABLE (01h)).

As interrupcións de baixo nivel das IP periféricas, incluído o CLIF, xestionaranse por completo dentro do firmware e só se notificará ao host dos eventos enumerados na sección de eventos.

O firmware implementa dous rexistros de eventos como rexistros RAM que se poden escribir / ler usando comandos da Sección 4.5.1.1 / Sección 4.5.1.5.

O rexistro EVENT_ENABLE (0x01) => Activar notificacións específicas/de todos os eventos.

O rexistro EVENT_STATUS (0x02) => Parte da carga útil da mensaxe do evento.

Os eventos serán borrados polo anfitrión unha vez que o anfitrión lea a mensaxe do evento.

Os eventos son de natureza asíncrona e notifícanse ao host, se están habilitados no rexistro EVENT_ENABLE.

A continuación móstrase a lista de eventos que estarán dispoñibles para o anfitrión como parte da mensaxe do evento.

Táboa 10. Eventos PN5190 (contido de EVENT_STATUS)

| Bit - Rango | Campo [1] | Sempre Activado (S/N) | |

| 31 | 12 | RFU | NA |

| 11 | 11 | CTS_EVENT [2] | N |

| 10 | 10 | IDLE_EVENT | Y |

| 9 | 9 | LPCD_CALIBRATION_DONE_EVENT | Y |

| 8 | 8 | LPCD_EVENT | Y |

| 7 | 7 | AUTOCOLL_EVENT | Y |

| 6 | 6 | TIMER0_EVENT | N |

| 5 | 5 | TX_OVERCURRENT_EVENT | N |

| 4 | 4 | RFON_DET_EVENT [2] | N |

| 3 | 3 | RFOFF_DET_EVENT [2] | N |

| 2 | 2 | STANDBY_PREV_EVENT | Y |

| 1 | 1 | GENERAL_ERROR_EVENT | Y |

| 0 | 0 | BOOT_EVENT | Y |

- Teña en conta que non se disputan dous eventos excepto en caso de erros. En caso de erros durante a operación, establecerase un evento funcional (por exemplo, BOOT_EVENT, AUTOCALL_EVENT, etc.) e GENERAL_ERROR_EVENT.

- Este evento desactivarase automaticamente despois de que se publique no host. O anfitrión debería activar de novo estes eventos se quere que se lle notifiquen estes eventos.

4.4.1.1 Formatos de mensaxes de eventos

O formato da mensaxe do evento varía dependendo das ocorrencias dun evento e dos diferentes estados do PN5190.

O anfitrión debe ler tag (T) e lonxitude da mensaxe (L) e despois le o número de bytes correspondente como valor (V) dos eventos.

En xeral, a mensaxe de evento (consulte a Figura 12) contén o EVENT_STATUS como se define na Táboa 11 e os datos do evento corresponden ao respectivo bit de evento definido en EVENT_STATUS.

Nota:

Para algúns eventos, a carga útil non existe. Por exemplo, se se activa TIMER0_EVENT, só se proporciona EVENT_STATUS como parte da mensaxe do evento.

A Táboa 11 tamén detalla se os datos do evento están presentes para o evento correspondente na mensaxe do evento. GENERAL_ERROR_EVENT tamén pode ocorrer con outros eventos.

GENERAL_ERROR_EVENT tamén pode ocorrer con outros eventos.

Neste escenario, a mensaxe de evento (consulte a Figura 13) contén o EVENT_STATUS como se define na Táboa 11 e GENERAL_ERROR_STATUS_DATA como se define na Táboa 14 e, a continuación, os datos do evento corresponden ao bit de evento respectivo definido en EVENT_STATUS como se define na Táboa 11. Nota:

Nota:

Só despois de BOOT_EVENT ou despois de POR, STANDBY, ULPCD, o host poderá funcionar no modo de funcionamento normal emitindo os comandos indicados anteriormente.

No caso de abortar un comando en execución existente, só despois de IDLE_EVENT, o host poderá traballar no modo de funcionamento normal emitindo os comandos indicados anteriormente.

4.4.1.2 Diferentes definicións de estado de EVENTO

4.4.1.2.1 Definicións de bits para EVENT_STATUS

Táboa 11. Definicións dos bits EVENT_STATUS

| Bit (A – De) | Evento | Descrición | Datos do evento correspondente (se hai) |

|

| 31 | 12 | RFU | Reservado | |

| 11 | 11 | CTS_EVENT | Este bit está establecido cando se xera un evento CTS. | Táboa 86 |

| 10 | 10 | IDLE_EVENT | Este bit está establecido cando se cancela o comando en curso debido á emisión do comando SWITCH_MODE_NORMAL. | Non hai datos de eventos |

| 9 | 9 | LPCD_CALIBRATION_DONE_ EVENTO |

Este bit establécese cando se xera o evento de calibración LPCD feito. | Táboa 16 |

| 8 | 8 | LPCD_EVENT | Este bit está establecido cando se xera o evento LPCD. | Táboa 15 |

| 7 | 7 | AUTOCOLL_EVENT | Este bit está establecido cando se completa a operación AUTOCOLL. | Táboa 52 |

| 6 | 6 | TIMER0_EVENT | Este bit está establecido cando se produce o evento TIMER0. | Non hai datos de eventos |

| 5 | 5 | TX_OVERCURRENT_ERROR_ EVENTO |

Este bit está establecido cando a corrente no controlador TX é superior ao limiar definido na EEPROM. Nesta condición, o campo desactivarase automaticamente antes da notificación ao host. Consulte a Sección 4.4.2.2. | Non hai datos de eventos |

| 4 | 4 | RFON_DET_EVENT | Este bit está establecido cando se detecta o campo de RF externo. | Non hai datos de eventos |

| 3 | 3 | RFOFF_DET_EVENT | Este bit está establecido cando o campo de RF externo xa existente desaparece. | Non hai datos de eventos |

| 2 | 2 | STANDBY_PREV_EVENT | Este bit está establecido cando se evita o modo de espera debido a que existen condicións de prevención | Táboa 13 |

| 1 | 1 | GENERAL_ERROR_EVENT | Este bit fíxase cando existe algunha condición de erro xeral | Táboa 14 |

| 0 | 0 | BOOT_EVENT | Este bit está establecido cando o PN5190 se inicia con POR/Standby | Táboa 12 |

4.4.1.2.2 Definicións de bits para BOOT_STATUS_DATA

Táboa 12. Definicións dos bits BOOT_STATUS_DATA

| Pouco a | Bit de | Estado de arranque | Motivo de arranque debido a |

| 31 | 27 | RFU | Reservado |

| 26 | 26 | ULP_STANDBY | Motivo de inicio debido á saída de ULP_STANDBY. |

| 25 | 23 | RFU | Reservado |

| 22 | 22 | BOOT_ RX_ULPDET | RX ULPDET deu como resultado o arranque en modo ULP-Standby |

| 21 | 21 | RFU | Reservado |

| 20 | 20 | BOOT_SPI | Motivo de arranque debido á baixada do sinal SPI_NTS |

| 19 | 17 | RFU | Reservado |

| 16 | 16 | BOOT_GPIO3 | Motivo de arranque debido á transición de GPIO3 de baixo a alto. |

| 15 | 15 | BOOT_GPIO2 | Motivo de arranque debido á transición de GPIO2 de baixo a alto. |

| 14 | 14 | BOOT_GPIO1 | Motivo de arranque debido á transición de GPIO1 de baixo a alto. |

| 13 | 13 | BOOT_GPIO0 | Motivo de arranque debido á transición de GPIO0 de baixo a alto. |

| 12 | 12 | BOOT_LPDET | Motivo de arranque debido á presenza de campos RF externos durante STANDBY/SUSPEND |

| 11 | 11 | RFU | Reservado |

| 10 | 8 | RFU | Reservado |

| 7 | 7 | BOOT_SOFT_RESET | Motivo de inicio debido ao reinicio suave do IC |

| 6 | 6 | BOOT_VDDIO_LOSS | Motivo de arranque debido á perda de VDDIO. Consulte a Sección 4.4.2.3 |

| 5 | 5 | BOOT_VDDIO_START | Motivo de arranque se entrou en STANDBY con VDDIO LOSS. Consulte a Sección 4.4.2.3 |

| 4 | 4 | BOOT_WUC | Motivo de inicio debido ao contador de espertar transcorrido durante calquera das operacións STANDBY. |

| 3 | 3 | BOOT_TEMP | O motivo de arranque debido á temperatura do IC é superior ao límite do limiar configurado. Consulte a Sección 4.4.2.1 |

| 2 | 2 | BOOT_WDG | Motivo de inicio debido ao restablecemento do watchdog |

| 1 | 1 | RFU | Reservado |

| 0 | 0 | BOOT_POR | Motivo de arranque debido ao restablecemento do acendido |

4.4.1.2.3 Definicións de bits para STANDBY_PREV_STATUS_DATA

Táboa 13. Definicións dos bits STANDBY_PREV_STATUS_DATA

| Pouco a | Bit de | Prevención en espera | O modo de espera impedido debido a |

| 31 | 26 | RFU | RESERVADOS |

| 25 | 25 | RFU | RESERVADOS |

| 24 | 24 | PREV_TEMP | A temperatura de funcionamento dos circuitos integrados está fóra do limiar |

| 23 | 23 | RFU | RESERVADOS |

| 22 | 22 | PREV_HOSTCOMM | Comunicación da interface do host |

| 21 | 21 | PREV_SPI | O sinal SPI_NTS está baixando |

| 20 | 18 | RFU | RESERVADOS |

| 17 | 17 | PREV_GPIO3 | Transición do sinal GPIO3 de baixo a alto |

| 16 | 16 | PREV_GPIO2 | Transición do sinal GPIO2 de baixo a alto |

| 15 | 15 | PREV_GPIO1 | Transición do sinal GPIO1 de baixo a alto |

| 14 | 14 | PREV_GPIO0 | Transición do sinal GPIO0 de baixo a alto |

| 13 | 13 | PREV_WUC | Contador de espertar transcorrido |

| 12 | 12 | PREV_LPDET | Detección de baixa potencia. Prodúcese cando se detecta un sinal de RF externo no proceso de entrar en modo de espera. |

| 11 | 11 | PREV_RX_ULPDET | Detección de potencia ultra baixa RX. Prodúcese cando se detecta un sinal de RF no proceso de ir a ULP_STANDBY. |

| 10 | 10 | RFU | RESERVADOS |

| 9 | 5 | RFU | RESERVADOS |

| 4 | 4 | RFU | RESERVADOS |

| 3 | 3 | RFU | RESERVADOS |

| 2 | 2 | RFU | RESERVADOS |

| 1 | 1 | RFU | RESERVADOS |

| 0 | 0 | RFU | RESERVADOS |

4.4.1.2.4 Definicións de bits para GENERAL_ERROR_STATUS_DATA

Táboa 14. Definicións dos bits GENERAL_ERROR_STATUS_DATA

| Pouco a | Pouco de | Estado de erro | Descrición |

| 31 | 6 | RFU | Reservado |

| 5 | 5 | XTAL_START_ERROR | Fallou o inicio de XTAL durante o arranque |

| 4 | 4 | SYS_TRIM_RECOVERY_ERROR | Produciuse un erro de recorte da memoria interna do sistema, pero fallou a recuperación. O sistema funciona en modo degradado. |

| 3 | 3 | SYS_TRIM_RECOVERY_SUCCESS | Produciuse un erro na memoria de recorte do sistema interno e a recuperación foi satisfactoria. O host debe reiniciar o PN5190 para que a recuperación teña efecto. |

| 2 | 2 | TXLDO_ERROR | Erro de TXLDO |

| 1 | 1 | CLOCK_ERROR | Erro de reloxo |

| 0 | 0 | GPADC_ERROR | Erro ADC |

4.4.1.2.5 Definicións de bits para LPCD_STATUS_DATA

Táboa 15. Definicións para os bytes LPCD_STATUS_DATA

| Pouco a | Bit de | Aplicabilidade dos bits de estado segundo a operación subxacente de LPCD ou ULPCD | A descrición do bit correspondente está definida en byte de estado. | ||

| LPCD | ULPCD | ||||

| 31 | 7 | RFU | Reservado | ||

| 6 | 6 | Abortar_HIF | Y | N | Abortado debido á actividade HIF |

| 5 | 5 | Erro CLKDET | N | Y | Abortado debido a un erro CLKDET |

| 4 | 4 | Tempo de espera XTAL | N | Y | Abortado debido ao tempo de espera de XTAL |

| 3 | 3 | VDDPA LDO Sobrecorriente | N | Y | Abortado debido a unha sobreintensidade de VDDPA LDO |

| 2 | 2 | Campo de RF externo | Y | Y | Abortado debido a un campo de RF externo |

| 1 | 1 | GPIO3 Abortar | N | Y | Abortado debido ao cambio de nivel de GPIO3 |

| 0 | 0 | Tarxeta detectada | Y | Y | Detectouse a tarxeta |

4.4.1.2.6 Definicións de bits para datos de estado LPCD_CALIBRATION_DONE

Táboa 16. Definicións dos bytes de datos de estado LPCD_CALIBRATION_DONE para ULPCD

| Pouco a | Bit de | Estado de LPCD_CALIBRATION DONE evento | A descrición do bit correspondente está definida en byte de estado. |

| 31 | 11 | Reservado | |

| 10 | 0 | Valor de referencia da calibración ULPCD | O valor RSSI medido durante a calibración ULPCD que se usa como referencia durante ULPCD |

Táboa 17. Definicións dos bytes de datos de estado LPCD_CALIBRATION_DONE para LPCD

| Pouco a | Bit de | Aplicabilidade dos bits de estado segundo a operación subxacente de LPCD ou ULPCD | A descrición do bit correspondente está definida en byte de estado. | ||

| 2 | 2 | Campo de RF externo | Y | Y | Abortado debido a un campo de RF externo |

| 1 | 1 | GPIO3 Abortar | N | Y | Abortado debido ao cambio de nivel de GPIO3 |

| 0 | 0 | Tarxeta detectada | Y | Y | Detectouse a tarxeta |

4.4.2 Manexo de diferentes escenarios de arranque

O PN5190 IC xestiona diferentes condicións de erro relacionadas cos parámetros IC como se indica a continuación.

4.4.2.1 Manexo do escenario de sobretemperatura cando o PN5190 está en funcionamento

Sempre que a temperatura interna do PN5190 IC alcanza o valor límite configurado no campo EEPROM TEMP_WARNING [2], o IC entra no modo de espera. E, en consecuencia, se o campo EEPROM ENABLE_GPIO0_ON_OVERTEMP [2] está configurado para enviar unha notificación ao host, entón GPIO0 será elevado para notificar a sobretemperatura do IC.

Cando a temperatura do IC cae por debaixo do valor límite configurado no campo EEPROM TEMP_WARNING [2], o IC arrancará con BOOT_EVENT como na Táboa 11 e o bit de estado de arranque BOOT_TEMP axustarase como na Táboa 12 e GPIO0 baixarase.

4.4.2.2 Manexo de sobreintensidade

Se PN5190 IC detecta a condición de sobreintensidade, o IC desconecta a alimentación de RF e envía o TX_OVERCURRENT_ERROR_EVENT como na Táboa 11.

A duración da condición de sobreintensidade pódese controlar modificando o campo EEPROM TXLDO_CONFIG [2].

Para obter información sobre IC sobre o limiar actual, consulte o documento [2].

Nota:

Se hai outros eventos ou respostas pendentes, enviaranse ao anfitrión.

4.4.2.3 Perda de VDDIO durante o funcionamento

Se o IC PN5190 atopa que non hai VDDIO (perda de VDDIO), o IC entra en modo de espera.

O IC arranca só cando o VDDIO está dispoñible, con BOOT_EVENT como na Táboa 11 e o bit de estado de arranque BOOT_VDDIO_START está configurado como na Táboa 12.

Para obter información sobre as características estáticas de PN5190 IC, consulte o documento [2].

4.4.3 Manexo de escenarios de aborto

O PN5190 IC ten un soporte para abortar os comandos de execución actuais e o comportamento do PN5190 IC, cando tal comando de aborto como a Sección 4.5.4.5.2 se envía ao PN5190 IC é como se mostra na Táboa 18.

Nota:

Cando o PN5190 IC está en modo ULPCD e ULP-Standby, non se pode abortar enviando unha Sección 4.5.4.5.2 OU iniciando unha transacción SPI (ao baixar o sinal SPI_NTS).

Táboa 18. Resposta ao evento esperado cando os diferentes comandos finalizaron coa Sección 4.5.4.5.2

| Comandos | Comportamento cando se envía o comando de cambio de modo normal |

| Todos os comandos nos que non se introduce baixa potencia | EVENT_STAUS está definido como “IDLE_EVENT” |

| Modo de cambio LPCD | EVENT_STATUS está configurado como "LPCD_EVENT" con "LPCD_ STATUS_DATA" que indica os bits de estado como "Abort_HIF" |

| Cambiar modo de espera | EVENT_STAUS está configurado como “BOOT_EVENT” con “BOOT_ STATUS_DATA” que indica os bits “BOOT_SPI” |

| Modo de cambio automático (Sen modo autónomo, modo autónomo con modo de espera e modo autónomo sen modo de espera) | EVENT_STAUS está definido como "AUTOCOLL_EVENT" con bits STATUS_DATA que indican que o comando foi cancelado polo usuario. |

4.5 Detalles das instrucións de funcionamento do modo normal

4.5.1 Manipulación do rexistro

As instrucións desta sección úsanse para acceder aos rexistros lóxicos do PN5190.

4.5.1.1 WRITE_REGISTER

Esta instrución úsase para escribir un valor de 32 bits (little-endian) nun rexistro lóxico.

4.5.1.1.1 Condicións

O enderezo do rexistro debe existir e o rexistro debe ter o atributo READ-WRITE ou WRITE-SOLO.

4.5.1.1.2 Comando

Táboa 19. Valor do comando WRITE_REGISTER Escribe un valor de 32 bits nun rexistro.

| Campo de carga útil | Lonxitude | Valor/Descrición |

| Enderezo de rexistro | 1 byte | Enderezo do rexistro. |

Táboa 19. Valor do comando WRITE_REGISTER…continuación

Escribe un valor de 32 bits nun rexistro.

| Campo de carga útil | Lonxitude | Valor/Descrición |

| Valor | 4 bytes | Valor de rexistro de 32 bits que debe escribirse. (Little-endian) |

4.5.1.1.3 Resposta

Táboa 20. Valor de resposta WRITE_REGISTER

| Campo de carga útil | Lonxitude | Valor/Descrición |

| Estado | 1 byte | Estado da operación [Táboa 9]. Os valores esperados son os seguintes: |

| PN5190_STATUS_SUCCESS | ||

| PN5190_STATUS_INSTR_ERROR |

4.5.1.1.4 evento

Non hai eventos para este comando.

4.5.1.2 WRITE_REGISTER_OR_MASK

Esta instrución úsase para modificar o contido do rexistro mediante unha operación OU lóxica. Lese o contido do rexistro e realízase unha operación OU lóxica coa máscara proporcionada. O contido modificado escribe de novo no rexistro.

4.5.1.2.1 Condicións

O enderezo do rexistro debe existir e o rexistro debe ter o atributo READ-WRITE.

4.5.1.2.2 Comando

Táboa 21. Valor do comando WRITE_REGISTER_OR_MASK Realiza unha operación OU lóxica nun rexistro usando a máscara proporcionada.

| Campo de carga útil | Lonxitude | Valor/descrición |

| Enderezo de rexistro | 1 byte | Enderezo do rexistro. |

| Máscara | 4 bytes | Máscara de bits utilizada como operando para a operación OU lóxica. (Little-endian) |

4.5.1.2.3 Resposta

Táboa 22. Valor de resposta WRITE_REGISTER_OR_MASK

| Campo de carga útil | Lonxitude | Valor/Descrición |

| Estado | 1 byte | Estado da operación [Táboa 9]. Os valores esperados son os seguintes: |

| PN5190_STATUS_SUCCESS | ||

| PN5190_STATUS_INSTR_ERROR |

4.5.1.2.4 evento

Non hai eventos para este comando.

4.5.1.3 ESCRIBIR_REXISTRO_E_MÁSCARA

Esta instrución úsase para modificar o contido do rexistro mediante unha operación AND lóxica. Lese o contido do rexistro e realízase unha operación AND lóxica coa máscara proporcionada. O contido modificado volve escribirse ao rexistro.

4.5.1.3.1 Condicións

O enderezo do rexistro debe existir e o rexistro debe ter o atributo READ-WRITE.

4.5.1.3.2 Comando

Táboa 23. Valor do comando WRITE_REGISTER_AND_MASK Realiza unha operación AND lóxica nun rexistro usando a máscara proporcionada.

| Campo de carga útil | Lonxitude | Valor/descrición |

| Enderezo de rexistro | 1 byte | Enderezo do rexistro. |

| Máscara | 4 bytes | Máscara de bits utilizada como operando para a operación AND lóxica. (Little-endian) |

4.5.1.3.3 Resposta

Táboa 24. Valor de resposta WRITE_REGISTER_AND_MASK

| Campo de carga útil | Lonxitude | Valor/Descrición |

| Estado | 1 byte | Estado da operación [Táboa 9]. Os valores esperados son os seguintes: |

| PN5190_STATUS_SUCCESS | ||

| PN5190_STATUS_INSTR_ERROR |

4.5.1.3.4 evento

Non hai eventos para este comando.

4.5.1.4 WRITE_REGISTER_MULTIPLE

Esta funcionalidade de instrucións é semellante á Sección 4.5.1.1, Sección 4.5.1.2, Sección 4.5.1.3, coa posibilidade de combinalas. De feito, leva unha matriz de conxunto de valores de tipo de rexistro e realiza a acción adecuada. O tipo reflicte a acción que é un rexistro de escritura, unha operación OU lóxica nun rexistro ou unha operación AND lóxica nun rexistro.

4.5.1.4.1 Condicións

O enderezo lóxico respectivo do rexistro dentro dun conxunto debe existir.

O atributo de acceso ao rexistro debe permitir a execución da acción requirida (tipo):

- Acción de escritura (0x01): atributo READ-WRITE ou WRITE-SOLO

- Acción de máscara OR (0x02): atributo READ-WRITE

- Acción de máscara AND (0x03): atributo READ-WRITE

O tamaño da matriz "Set" debe estar no intervalo de 1 a 43, incluídos.

O campo "Tipo" debe estar no intervalo de 1 a 3, inclusive

4.5.1.4.2 Comando

Táboa 25. Valor do comando WRITE_REGISTER_MULTIPLE Realiza unha operación de rexistro de escritura mediante un conxunto de pares de rexistro-valor.

| Campo de carga útil | Lonxitude | Valor/descrición | |||

| Establecer [1…n] | 6 bytes | Enderezo de rexistro | 1 byte | Enderezo lóxico do rexistro. | |

| Tipo | 1 byte | 0x1 | Rexistro de escritura | ||

| 0x2 | Escribir Rexistro OU Máscara | ||||

| 0x3 | Escribe Rexistro E Máscara | ||||

| Valor | 4 bytes | 32 Valor do rexistro de mordida que debe escribirse, ou máscara de bits utilizada para a operación lóxica. (Little-endian) | |||

Nota: No caso dunha excepción a operación non se retrotrae, é dicir, os rexistros que foron modificados ata que se produza unha excepción permanecen en estado modificado. O host debe tomar as accións adecuadas para recuperar un estado definido.

4.5.1.4.3 Resposta

Táboa 26. Valor de resposta WRITE_REGISTER_MULTIPLE

| Campo de carga útil | Lonxitude | Valor/Descrición |

| Estado | 1 byte | Estado da operación [Táboa 9]. Os valores esperados son os seguintes: |

| PN5190_STATUS_SUCCESS | ||

| PN5190_STATUS_INSTR_ERROR |

4.5.1.4.4 evento

Non hai eventos para este comando.

4.5.1.5 READ_REGISTER

Esta instrución úsase para ler o contido dun rexistro lóxico. O contido está presente na resposta, como un valor de 4 bytes en formato little-endian.

4.5.1.5.1 Condicións

O enderezo do rexistro lóxico debe existir. O atributo de acceso do rexistro debe ser LECTURA-ESCRITURA ou SÓ LECTURA.

4.5.1.5.2 Comando

Táboa 27. Valor do comando READ_REGISTER

Ler de novo o contido dun rexistro.

| Campo de carga útil | Lonxitude | Valor/Descrición |

| Enderezo de rexistro | 1 byte | Enderezo do rexistro lóxico |

4.5.1.5.3 Resposta

Táboa 28. Valor de resposta READ_REGISTER

| Campo de carga útil | Lonxitude | Valor/Descrición |

| Estado | 1 byte | Estado da operación [Táboa 9]. Os valores esperados son os seguintes: |

| PN5190_STATUS_SUCCESS PN5190_STATUS_INSTR_ERROR (Non hai máis datos) | ||

| Valor de rexistro | 4 bytes | Valor de rexistro de 32 bits que foi lido. (Little-endian) |

4.5.1.5.4 evento

Non hai eventos para este comando.

4.5.1.6 READ_REGISTER_MULTIPLE

Esta instrución úsase para ler varios rexistros lóxicos á vez. O resultado (contido de cada rexistro) ofrécese na resposta á instrución. O enderezo de rexistro en si non está incluído na resposta. A orde dos contidos do rexistro dentro da resposta correspóndese coa orde dos enderezos do rexistro dentro da instrución.

4.5.1.6.1 Condicións

Deben existir todos os enderezos de rexistro dentro da instrución. O atributo de acceso para cada rexistro debe ser READ-WRITE ou READ-SOLO. O tamaño da matriz de "Enderezo de rexistro" debe estar no rango de 1 a 18, incluídos.

4.5.1.6.2 Comando

Táboa 29. Valor do comando READ_REGISTER_MULTIPLE Realiza unha operación de lectura de rexistro nun conxunto de rexistros.

| Campo de carga útil | Lonxitude | Valor/Descrición |

| Enderezo de rexistro[1…n] | 1 byte | Enderezo de rexistro |

4.5.1.6.3 Resposta

Táboa 30. Valor de resposta READ_REGISTER_MULTIPLE

| Campo de carga útil | Lonxitude | Valor/descrición | ||

| Estado | 1 byte | Estado da operación [Táboa 9]. Os valores esperados son os seguintes: | ||

| PN5190_STATUS_SUCCESS PN5190_STATUS_INSTR_ERROR (Non hai máis datos) | ||||

| Valor de rexistro [1…n] | 4 bytes | Valor | 4 bytes | Valor de rexistro de 32 bits que foi lido (little-endian). |

4.5.1.6.4 evento

Non hai eventos para este comando.

4.5.2 Manipulación de E2PROM

A área accesible en E2PROM é segundo o mapa EEPROM e o tamaño direccionable.

Nota:

1. Sempre que se mencione o "Enderezo E2PROM" nas instrucións seguintes, referirase ao tamaño da área EEPROM direccionable.

4.5.2.1 WRITE_E2PROM

Esta instrución úsase para escribir un ou máis valores en E2PROM. O campo "Valores" contén os datos que se escribirán en E2PROM a partir do enderezo indicado polo campo "Enderezo E2PROM". Os datos escríbense en orde secuencial.

Nota:

Teña en conta que este é un comando de bloqueo, isto significa que o NFC FE está bloqueado durante a operación de escritura. Isto pode levar varios milisegundos.

4.5.2.1.1 Condicións

O campo "Enderezo E2PROM" debe estar no intervalo de [2]. O número de bytes dentro do campo "Valores" debe estar no intervalo de 1 a 1024 (0x0400), incluídos. A operación de escritura non debe ir máis aló do enderezo EEPROM como se menciona en [2]. A resposta de erro enviarase ao host se o enderezo supera o espazo de enderezos EEPROM como en [2].

4.5.2.1.2 Comando

Táboa 31. Valor do comando WRITE_E2PROM Escribe os valores dados secuencialmente en E2PROM.

| Campo de carga útil | Lonxitude | Valor/descrición |

| Enderezo E2PROM | 2 byte | Enderezo na EEPROM desde o que comezará a operación de escritura. (Little-Endian) |

| Valores | 1 – 1024 bytes | Valores que deben escribirse en E2PROM en orde secuencial. |

4.5.2.1.3 Resposta

Táboa 32. Valor de resposta WRITE_EEPROM

| Campo de carga útil | Lonxitude | Valor/Descrición |

| Estado | 1 byte | Estado da operación [Táboa 9]. Os valores esperados son os seguintes: |

| PN5190_STATUS_SUCCESS PN5190_STATUS_INSTR_ERROR PN5190_STATUS_MEMORY_ERROR |

4.5.2.1.4 evento

Non hai eventos para este comando.

4.5.2.2 READ_E2PROM

Esta instrución utilízase para ler datos da área de memoria E2PROM. O campo "Enderezo E2PROM" indica o enderezo de inicio da operación de lectura. A resposta contén os datos lidos desde E2PROM.

4.5.2.2.1 Condicións

O campo "Enderezo E2PROM" debe estar nun intervalo válido.

O campo "Número de bytes" debe estar no intervalo de 1 a 256, incluídos.

A operación de lectura non debe ir máis aló do último enderezo EEPROM accesible.

A resposta de erro enviarase ao host, se o enderezo supera o espazo de enderezos EEPROM.

4.5.2.2.2 Comando

Táboa 33. Valor do comando READ_E2PROM Lea secuencialmente os valores de E2PROM.

| Campo de carga útil | Lonxitude | Valor/descrición |

| Enderezo E2PROM | 2 byte | Enderezo en E2PROM desde o que comezará a operación de lectura. (Little-Endian) |

| Número de bytes | 2 byte | Número de bytes a ler. (Little-endian) |

4.5.2.2.3 Resposta

Táboa 34. Valor de resposta READ_E2PROM

| Campo de carga útil | Lonxitude | Valor/Descrición |

| Estado | 1 byte | Estado da operación [Táboa 9]. Os valores esperados son os seguintes: |

| PN5190_STATUS_SUCCESS | ||

| PN5190_STATUS_INSTR_ERROR (Non hai máis datos) | ||

| Valores | 1 – 1024 bytes | Valores que se leron en orde secuencial. |

4.5.2.2.4 evento

Non hai eventos para este comando.

4.5.2.3 GET_CRC_USER_AREA

Esta instrución utilízase para calcular o CRC para a área de configuración de usuario completa incluída a área de protocolo de PN5190 IC.

4.5.2.3.1 Comando

Táboa 35. Valor do comando GET_CRC_USER_AREA

Ler CRC da área de configuración do usuario incluída a área de protocolo.

| Campo de carga útil | Lonxitude | Valor/Descrición |

| – | – | Non hai datos na carga útil |

4.5.2.3.2 Resposta

Táboa 36. Valor de resposta GET_CRC_USER_AREA

| Campo de carga útil | Lonxitude | Valor/descrición |

| Estado | 1 byte | Estado da operación [Táboa 9]. Os valores esperados son os seguintes: |

| PN5190_STATUS_SUCCESS | ||

| PN5190_STATUS_INSTR_ERROR (Non hai máis datos) | ||

| Valores | 4 bytes | 4 bytes de datos CRC en formato little-endian. |

4.5.2.3.3 evento

Non hai eventos para este comando.

4.5.3 Manipulación de datos CLIF

As instrucións descritas nesta sección describen os comandos para a transmisión e recepción de RF.

4.5.3.1 INTERCAMBIO_DATOS_RF

A función de intercambio RF realiza unha transmisión dos datos TX e está esperando a recepción de calquera dato RX.

A función devolve en caso de recepción (errónea ou correcta) ou de tempo de espera. O temporizador iníciase co FIN da TRANSMISIÓN e detense co INICIO da RECEPCIÓN. O valor de tempo de espera preconfigurado na EEPROM utilizarase no caso de que o tempo de espera non se configure antes da execución do comando de Exchange.

Se transceiver_state é

- en IDLE introdúcese no modo TRANSCEIVE.

- En WAIT_RECEIVE, o estado do transceptor restablece ao MODO TRANSCEIVE se se establece o bit iniciador

- En WAIT_TRANSMIT, o estado do transceptor restablece ao MODO TRANSCEIVE se NON se establece o bit iniciador

O campo "Número de bits válidos no último byte" indica a lonxitude exacta dos datos que se van transmitir.

4.5.3.1.1 Condicións

O tamaño do campo "TX Data" debe estar no intervalo de 0 a 1024, incluídos.

O campo "Número de bits válidos no último byte" debe estar no intervalo de 0 a 7.

Non se debe chamar o comando durante unha transmisión de RF en curso. O mando asegurará o estado correcto do transceptor para transmitir os datos.

Nota:

Este comando só é válido para o modo Lector e o modo iniciador pasivo/activo P2P.

4.5.3.1.2 Comando

Táboa 37. Valor do comando EXCHANGE_RF_DATA

Escriba os datos de TX no búfer de transmisión de RF interno e comeza a transmisión mediante o comando de transceptor e agarde ata a recepción ou o tempo de espera para preparar unha resposta ao host.

| Campo de carga útil | Lonxitude | Valor/Descrición | |

| Número de bits válidos no último byte | 1 byte | 0 | Transmítense todos os bits do último byte |

| 1 - 7 | Número de bits dentro do último byte a transmitir. | ||

| RFExchangeConfig | 1 byte | Configuración da función RFExchange. Detalles ver a continuación | |

Táboa 37. Valor do comando EXCHANGE_RF_DATA…continuación

Escriba os datos de TX no búfer de transmisión de RF interno e comeza a transmisión mediante o comando de transceptor e agarde ata a recepción ou o tempo de espera para preparar unha resposta ao host.

| Campo de carga útil | Lonxitude | Valor/Descrición |

| Datos TX | n bytes | Datos TX que deben enviarse a través de CLIF mediante o comando transceive. n = 0 – 1024 bytes |

Táboa 38. Máscara de bits de RFexchangeConfig

| b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 | Descrición |

| Os bits 4-7 son RFU | ||||||||

| X | Inclúe os datos RX na resposta baseada en RX_STATUS, se o bit se establece en 1b. | |||||||

| X | Incluír o rexistro EVENT_STATUS como resposta, se o bit se establece en 1b. | |||||||

| X | Inclúa o rexistro RX_STATUS_ERROR na resposta, se o bit está configurado en 1b. | |||||||

| X | Inclúa o rexistro RX_STATUS como resposta, se o bit está configurado en 1b. |

4.5.3.1.3 Resposta

Táboa 39. Valor de resposta de EXCHANGE_RF_DATA

| Campo de carga útil | Lonxitude | Valor/Descrición |

| Estado | 1 byte | Estado da operación [Táboa 9]. Os valores esperados son os seguintes: |

| PN5190_STATUS_INSTR_SUCCESS PN5190_STATUS_INSTR_ERROR (Non hai máis datos) PN5190_STATUS_TIMEOUT PN5190_STATUS_RX_TIMEOUT PN5190_STATUS_NO_RF_FIELD PN5190_STATUS_TIMEOUT_WITH_EMD_ERROR |

||

| RX_STATUS | 4 bytes | Se se solicita RX_STATUS (little-endian) |

| RX_STATUS_ERROR | 4 bytes | Se se solicita RX_STATUS_ERROR (little-endian) |

| EVENT_STATUS | 4 bytes | Se se solicita EVENT_STATUS (little-endian) |

| Datos RX | 1 – 1024 bytes | Se se solicitan datos RX. Datos de RX recibidos durante a fase de recepción de RF do intercambio de RF. |

4.5.3.1.4 evento

Non hai eventos para este comando.

4.5.3.2 TRANSMIT_RF_DATA

Esta instrución úsase para escribir datos no búfer de transmisión CLIF interno e iniciar a transmisión mediante o comando transceive internamente. O tamaño deste búfer está limitado a 1024 bytes. Despois de executar esta instrución, iníciase automaticamente unha recepción de RF.

O comando volve inmediatamente despois de que se complete a transmisión sen esperar a que se complete a recepción.

4.5.3.2.1 Condicións

O número de bytes dentro do campo "TX Data" debe estar no intervalo de 1 a 1024, incluídos.

Non se debe chamar o comando durante unha transmisión de RF en curso.

4.5.3.2.2 Comando

Táboa 40. Valor do comando TRANSMIT_RF_DATA Escribe datos TX no búfer de transmisión CLIF interno.

| Campo de carga útil | Lonxitude | Valor/Descrición |

| Número de bits válidos no último byte | 1 byte | 0 Transmítense todos os bits do último byte 1 – 7 Número de bits do último byte a transmitir. |

| RFU | 1 byte | Reservado |

| Datos TX | 1 – 1024 bytes | Datos de TX que se utilizarán durante a próxima transmisión de RF. |

4.5.3.2.3 Resposta

Táboa 41. Valor de resposta TRANSMIT_RF_DATA

| Campo de carga útil | Lonxitude | Valor/Descrición |

| Estado | 1 byte | Estado da operación [Táboa 9]. Os valores esperados son os seguintes: |

| PN5190_STATUS_INSTR_SUCCESS PN5190_STATUS_INSTR_ERROR PN5190_STATUS_NO_RF_FIELD PN5190_STATUS_NO_EXTERNAL_RF_FIELD |

4.5.3.2.4 evento

Non hai eventos para este comando.

4.5.3.3 RECUPERAR_DATOS_RF

Esta instrución utilízase para ler os datos do búfer interno de CLIF RX, que contén os datos de resposta de RF (se os houber) publicados nel desde a execución anterior da Sección 4.5.3.1 coa opción de non incluír os datos recibidos na resposta ou na Sección 4.5.3.2. .XNUMX mando.

4.5.3.3.1 Comando

Táboa 42. Valor do comando RETRIEVE_RF_DATA Ler os datos de RX do búfer de recepción de RF interno.

| Campo de carga útil | Lonxitude | Valor/Descrición |

| Baleiro | Baleiro | Baleiro |

4.5.3.3.2 Resposta

Táboa 43. Valor de resposta RETRIEVE_RF_DATA

| Campo de carga útil | Lonxitude | Valor/Descrición |

| Estado | 1 byte | Estado da operación [Táboa 9]. Os valores esperados son os seguintes: |

| Campo de carga útil | Lonxitude | Valor/Descrición |

| PN5190_STATUS_INSTR_SUCCESS PN5190_STATUS_INSTR_ERROR (Non hai máis datos) |

||

| Datos RX | 1 – 1024 bytes | Datos de RX que se recibiron durante a última recepción exitosa de RF. |

4.5.3.3.3 evento

Non hai eventos para este comando.

4.5.3.4 RECEIVE_RF_DATA

Esta instrución espera os datos recibidos a través da interface RF do lector.

No modo lector, esta instrución volve se hai unha recepción (errónea ou correcta) ou se produciu un tempo de espera FWT. O temporizador iníciase co FIN da TRANSMISIÓN e detense co INICIO da RECEPCIÓN. O valor de tempo de espera predeterminado preconfigurado na EEPROM utilizarase no caso de que o tempo de espera non se configure antes da execución do comando de Exchange.

No modo de destino, esta instrución devolve en caso de recepción (errónea ou correcta) ou erro de RF externo.

Nota:

Esta instrución debe usarse co comando TRANSMIT_RF_DATA para realizar operacións TX e RX...

4.5.3.4.1 Comando

Táboa 44. Valor do comando RECEIVE_RF_DATA

| Campo de carga útil | Lonxitude | Valor/Descrición |

| RecibirRFConfig | 1 byte | Configuración da función ReceiveRFConfig. Ver Táboa 45 |

Táboa 45. Máscara de bits ReceiveRFConfig

| b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 | Descrición |

| Os bits 4-7 son RFU | ||||||||

| X | Inclúe os datos RX na resposta baseada en RX_STATUS, se o bit se establece en 1b. | |||||||

| X | Incluír o rexistro EVENT_STATUS como resposta, se o bit se establece en 1b. | |||||||

| X | Inclúa o rexistro RX_STATUS_ERROR na resposta, se o bit está configurado en 1b. | |||||||

| X | Inclúa o rexistro RX_STATUS como resposta, se o bit está configurado en 1b. |

4.5.3.4.2 Resposta

Táboa 46. Valor de resposta RECEIVE_RF_DATA

| Campo de carga útil | Lonxitude | Valor/descrición |

| Estado | 1 byte | Estado da operación [Táboa 9]. Os valores esperados son os seguintes: |

| PN5190_STATUS_INSTR_SUCCESS PN5190_STATUS_INSTR_ERROR (Non hai máis datos) PN5190_STATUS_TIMEOUT |

| Campo de carga útil | Lonxitude | Valor/descrición |

| PN5190_STATUS_NO_RF_FIELD PN5190_STATUS_NO_EXTERNAL_RF_FIELD |

||

| RX_STATUS | 4 bytes | Se se solicita RX_STATUS (little-endian) |

| RX_STATUS_ERROR | 4 bytes | Se se solicita RX_STATUS_ERROR (little-endian) |

| EVENT_STATUS | 4 bytes | Se se solicita EVENT_STATUS (little-endian) |

| Datos RX | 1 – 1024 bytes | Se se solicitan datos RX. Datos RX recibidos por RF. |

4.5.3.4.3 evento

Non hai eventos para este comando.

4.5.3.5 RETRIEVE_RF_FELICA_EMD_DATA (Configuración de FeliCa EMD)

Esta instrución utilízase para ler os datos do búfer interno de CLIF RX, que contén os datos de resposta de FeliCa EMD (se os houber) enviados a el desde a execución anterior do comando EXCHANGE_RF_DATA que volve co estado 'PN5190_STATUS_TIMEOUT_WITH_EMD_ERROR'.

Nota: Este comando está dispoñible a partir de PN5190 FW v02.03.

4.5.3.5.1 Comando

Ler os datos de RX do búfer interno de recepción de RF.

Táboa 47. Valor do comando RETRIEVE_RF_FELICA_EMD_DATA

| Campo de carga útil | Lonxitude | Valor/Descrición | |

| FeliCaRFRetrieveConfig | 1 byte | 00 - FF | Configuración da función RETRIEVE_RF_FELICA_EMD_DATA |

| descrición da configuración (máscara de bits). | bit 7..2: RFU bit 1: inclúe o rexistro RX_STATUS_ ERROR como resposta, se o bit está configurado en 1b. bit 0: inclúe o rexistro RX_STATUS como resposta, se o bit está configurado en 1b. |

||

4.5.3.5.2 Resposta

Táboa 48. Valor de resposta RETRIEVE_RF_FELICA_EMD_DATA

| Campo de carga útil | Lonxitude | Valor/descrición | |||

| Estado | 1 byte | Estado da operación. Os valores esperados son os seguintes: PN5190_STATUS_INSTR_SUCCESS PN5190_STATUS_INSTR_ERROR (Non hai máis datos) | |||

| RX_STATUS | 4 byte | Se se solicita RX_STATUS (little-endian) | |||

| RX_STATUS_ ERRO | 4 byte | Se se solicita RX_STATUS_ERROR (little-endian) | |||

| Campo de carga útil | Lonxitude | Valor/descrición | |||

| Datos RX | 1…1024 bytes | Datos de FeliCa EMD RX que se recibiron durante a última recepción de RF sen éxito mediante o comando Exchange. | |||

4.5.3.5.3 evento

Non hai eventos para este comando.

4.5.4 Cambio de modo de operación

PN5190 admite 4 modos de operación diferentes:

4.5.4.1 Normal

Este é o modo predeterminado, onde se permiten todas as instrucións.

4.5.4.2 Modo de espera

PN5190 está en estado de espera/suspensión para aforrar enerxía. Débense establecer as condicións de activación para definir cando deixar de novo o modo de espera.

4.5.4.3 LPCD

PN5190 está no modo de detección de tarxetas de baixa potencia, onde tenta detectar unha tarxeta que está entrando no volume operativo, co menor consumo de enerxía posible.

4.5.4.4 Autocoll

PN5190 actúa como oínte de RF, realizando a activación do modo de destino de forma autónoma (para garantir restricións en tempo real)

4.5.4.5 SWITCH_MODE_NORMAL

O comando Cambiar modo normal ten tres casos de uso.

4.5.4.5.1 Caso de uso 1: ingrese ao modo de operación normal ao encenderse (POR)

Use para restablecer o estado inactivo para recibir/procesar o seguinte comando entrando no modo de funcionamento normal.

4.5.4.5.2 UseCase2: finalizando o comando que xa está en execución para cambiar ao modo de operación normal (comando de aborto)

Utilízao para restablecer o estado de inactividade para recibir/procesar o seguinte comando finalizando os comandos que xa están en execución.

Poderán finalizar comandos como standby, LPCD, Exchange, PRBS e Autocoll mediante este comando.

Este é o único comando especial, que non ten resposta. Pola contra, ten unha notificación de EVENTO.

Consulte a Sección 4.4.3 para obter máis información sobre o tipo de eventos que ocorren durante a execución de diferentes comandos subxacentes.

4.5.4.5.2.1 Caso de uso 2.1:

Este comando restablecerá todos os rexistros CLIF TX, RX e de control de campo ao estado de arranque. Ao emitir este comando desactivarase calquera campo de RF existente.

4.5.4.5.2.2 Caso de uso 2.2:

Dispoñible desde PN5190 FW v02.03 en diante:

Este comando non modificará os rexistros CLIF TX, RX e de control de campo, senón que só moverá o transceptor ao estado INACTIVO.

4.5.4.5.3 UseCase3: Modo de funcionamento normal ao reiniciar/saír do modo de espera, LPCD Neste caso, o PN5190 entra directamente no modo de funcionamento normal, enviando o IDLE_EVENT ao host (Figura 12 ou Figura 13) e “ O bit IDLE_EVENT" está definido na Táboa 11.

Non hai ningún requisito para enviar o comando SWITCH_MODE_NORMAL.

Nota:

Despois de que o IC se cambie ao modo normal, todos os axustes de RF modifícanse ao estado predeterminado. É imperativo que a configuración de RF respectiva e outros rexistros relacionados deban cargarse cos valores apropiados antes de realizar unha operación RF ON ou RF Exchange.

4.5.4.5.4 Marco de comandos para enviar para diferentes casos de uso

4.5.4.5.4.1 Caso de uso 1: o comando entra no modo de operación normal ao encenderse (POR) 0x20 0x01 0x00

4.5.4.5.4.2 UseCase2: Comando para finalizar os comandos que xa están en execución para cambiar ao modo de operación normal

Caso de uso 2.1:

0x20 0x00 0x00

Caso de uso 2.2: (a partir de FW v02.02):

0x20 0x02 0x00

4.5.4.5.4.3 UseCase3: comando para o modo de funcionamento normal ao reiniciar/saír do modo de espera, LPCD, ULPCD

Ningún. PN5190 entra directamente en modo de operación normal.

4.5.4.5.5 Resposta

Ningún

4.5.4.5.6 evento

Establécese un BOOT_EVENT (no rexistro EVENT_STATUS) que indica que se ingresa no modo normal e se envía ao host. Consulte a Figura 12 e a Figura 13 para os datos do evento.

Establécese un IDLE_EVENT (no rexistro EVENT_STATUS) que indica que se ingresa o modo normal e que se envía ao host. Consulte a Figura 12 e a Figura 13 para os datos do evento.

Establécese un BOOT_EVENT (no rexistro EVENT_STATUS) que indica que se ingresa o modo normal e que se envía ao host. Consulte a Figura 12 e a Figura 13 para os datos do evento.

4.5.4.6 SWITCH_MODE_AUTOCOLL

O modo de cambio automático Autocoll realiza automaticamente o procedemento de activación da tarxeta no modo de destino.

O campo "Modo Autocoll" debe estar no intervalo de 0 a 2, inclusive.

No caso de que o campo "Modo Autocoll" estea definido como 2 (Autocoll): o campo "Tecnoloxías de RF" (táboa 50) debe conter unha máscara de bits que indique as tecnoloxías de RF compatibles durante o Autocoll.

Non se deben enviar instrucións mentres esteas neste modo.

A terminación indícase mediante unha interrupción.

4.5.4.6.1 Comando

Táboa 49. Valor do comando SWITCH_MODE_AUTOCOLL

| Parámetro | Lonxitude | Valor/Descrición | |

| Tecnoloxías de RF | 1 byte | Máscara de bits que indica a tecnoloxía de RF para escoitar durante o Autocoll. | |

| Modo Autocoll | 1 byte | 0 | Sen modo autónomo, é dicir, o Autocoll remata cando non hai un campo de RF externo. |

| Terminación en caso de | |||

| • NO CAMPO RF ou CAMPO RF desapareceu | |||

| • PN5190 está ACTIVADO no modo OBXECTIVO | |||

| 1 | Modo autónomo con modo de espera. Cando non hai ningún campo de RF presente, Autocoll pasa automaticamente ao modo de espera. Unha vez que se detecta un campo de RF externo de RF, o PN5190 entra de novo en modo Autocoll. | ||

| Terminación en caso de | |||

| • PN5190 está ACTIVADO no modo OBXECTIVO | |||

| Desde PN5190 FW v02.03 en diante: Se o campo EEPROM "bCard ModeUltraLowPowerEnabled" no enderezo "0xCDF" está configurado en "1", entón PN5190 entra en modo de espera de ultra baixa potencia. | |||

| 2 | Modo autónomo sen modo de espera. Cando non hai campo de RF, PN5190 agarda ata que estea presente o campo de RF antes de iniciar o algoritmo Autocoll. Neste caso non se usa o modo de espera. | ||

| Terminación en caso de • PN5190 está ACTIVADO no modo OBXECTIVO |

|||

Táboa 50. Máscara de bits de tecnoloxías de RF

| b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 | Descrición |

| 0 | 0 | 0 | 0 | RFU | ||||

| X | Se se establece en 1b, a escoita de NFC-F Active está habilitada. (Non dispoñible). | |||||||

| X | Se se establece en 1b, a escoita de NFC-A Active está habilitada. (Non dispoñible). | |||||||

| X | Se se establece en 1b, a escoita por NFC-F está habilitada. | |||||||

| X | Se se establece en 1b, a escoita por NFC-A está habilitada. |

4.5.4.6.2 Resposta

A resposta só indica que o comando foi procesado.

Táboa 51. Valor de resposta SWITCH_MODE_AUTOCOLL

| Campo de carga útil | Lonxitude | Valor/Descrición |

| Estado | 1 byte | Estado da operación [Táboa 9]. Os valores esperados son os seguintes: |

| PN5190_STATUS_INSTR_SUCCESS PN5190_STATUS_INSTR_ERROR (Non se introduciu o modo de cambio debido a unha configuración incorrecta) |

4.5.4.6.3 evento

A notificación do evento envíase cando o comando rematou e introdúcese no modo normal. O host debe ler os bytes de resposta en función do valor do evento.

Nota:

Cando o estado non é "PN5190_STATUS_INSTR_SUCCESS", os bytes de datos "Protocol" e "Card_Activated" non están presentes.

A información tecnolóxica obtense dos rexistros mediante os comandos da Sección 4.5.1.5, Sección 4.5.1.6.

A seguinte táboa mostra os datos do evento que se envían como parte da mensaxe do evento Figura 12 e Figura 13.

Táboa 52. EVENT_SWITCH_MODE_AUTOCOLL – Datos AUTOCOLL_EVENT Cambio de modo de operación Evento Autocoll

| Campo de carga útil | Lonxitude | Valor/Descrición | |

| Estado | 1 byte | Estado da operación | |

| PN5190_STATUS_INSTR_SUCCESS | PN5190 está ACTIVADO no modo OBXECTIVO. Máis datos neste evento son válidos. |

||

| PN5190_STATUS_PREVENT_STANDBY | Indica que o PN5190 non pode entrar en modo de espera. Este estado só é válido cando se selecciona o modo Autocoll como "Modo autónomo con modo de espera". | ||

| PN5190_STATUS_NO_EXTERNAL_RF_ CAMPO | Indica que non hai ningún campo de RF externo durante a execución de Autocoll en modo non autónomo | ||

| PN5190_STATUS_USER_CANCELLED | Indica que o comando actual en curso é abortado polo comando normal do modo de cambio | ||

| Protocolo | 1 byte | 0x10 | Activado como tipo pasivo A |

| 0x11 | Activado como tipo pasivo F 212 | ||

| 0x12 | Activado como tipo pasivo F 424 | ||

| 0x20 | Activado como tipo activo A | ||

| 0x21 | Activado como Active TypeF 212 | ||

| 0x22 | Activado como Active TypeF 424 | ||

| Outros valores | Non válido | ||

| Tarxeta_Activada | 1 byte | 0x00 | Sen proceso de activación da tarxeta segundo a norma ISO 14443-3 |

| 0x01 | Indica que o dispositivo está activado en modo pasivo |

Nota:

Despois de ler os datos do evento, os datos recibidos da tarxeta/dispositivo que se activou (como "n" bytes de ATR_REQ/RATS segundo ISO18092/ISO1443-4), leranse mediante o comando da Sección 4.5.3.3.

4.5.4.6.4 Comunicación example

4.5.4.7 SWITCH_MODE_STANDBY

O modo de espera de conmutación configura automaticamente o IC en modo de espera. O IC activarase despois de que as fontes de activación configuradas cumpran as condicións de activación.

Nota:

A caducidade do contador para ULP STANDBY e o aborto HIF para STANDBY están dispoñibles de forma predeterminada para saír dos modos de espera.

4.5.4.7.1 Comando

Táboa 53. Valor do comando SWITCH_MODE_STANDBY

| Parámetro | Lonxitude | Valor/Descrición |

| Config | 1 byte | Máscara de bits que controla a fonte de activación que se utilizará e o modo de espera para entrar. Refírense a Táboa 54 |

| Valor de contador | 2 bytes | Valor usado para o contador de espertar en milisegundos. O valor máximo admitido é 2690 para o modo de espera. O valor máximo admitido é 4095 para o modo de espera ULP. O valor a proporcionar está en formato little-endian. O contido deste parámetro só é válido se a "Máscara de bits de configuración" está activada para activar o contador. |

Táboa 54. Configurar máscara de bits

| b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 | Descrición |

| X | Introduza o modo de espera ULP se o bit está configurado en 1b. Introduza o modo de espera se o bit está configurado en 0b. | |||||||

| 0 | RFU | |||||||

| X | Activa o GPIO-3 cando estea alto, se o bit está configurado en 1b. (Non aplicable para ULP en espera) | |||||||

| X | Activa o GPIO-2 cando estea alto, se o bit está configurado en 1b. (Non aplicable para ULP en espera) | |||||||