Microsemi DG0633 IGLOO2 FPGA CoreTSE MAC 1000 Base-T 環回演示

微半導體總部

一個企業,Aliso Viejo,

CA 92656美國

美國境內:+1 800-713-4113 美國境外:+1 949-380-6100 銷售額:+1 949-380-6136

傳真:+1 949-215-4996

電子郵件: sales.support@microsemi.com www.microsemi.com

©2021 Microsemi,Microchip Technology Inc. 的全資子公司。保留所有權利。 Microsemi 和 Microsemi 徽標是 Microsemi Corporation 的註冊商標。 所有其他商標和服務標誌均為其各自所有者的財產。

Microsemi 對此處包含的信息或其產品和服務對任何特定目的的適用性不作任何保證、陳述或保證,Microsemi 也不承擔因應用或使用任何產品或電路而產生的任何責任。 在此銷售的產品和 Microsemi 銷售的任何其他產品都經過了有限的測試,不應與任務關鍵型設備或應用程序一起使用。 任何性能規格都被認為是可靠的,但未經驗證,買方必須單獨、與任何最終產品一起或安裝在任何最終產品中進行並完成產品的所有性能和其他測試。 買方不得依賴 Microsemi 提供的任何數據和性能規格或參數。 買方有責任獨立確定任何產品的適用性並對其進行測試和驗證。 Microsemi 在此提供的信息是“按原樣、在哪裡”提供的,並且存在所有錯誤,與此類信息相關的全部風險完全由買方承擔。 Microsemi 沒有明確或暗示地向任何一方授予任何專利權、許可或任何其他知識產權,無論是關於此類信息本身還是此類信息所描述的任何內容。 本文檔中提供的信息是 Microsemi 的專有信息,Microsemi 保留隨時對本文檔中的信息或任何產品和服務進行任何更改的權利,恕不另行通知。

關於 Microsemi

Microsemi 是 Microchip Technology Inc.(納斯達克代碼:MCHP)的全資子公司,為航空航天和國防、通信、數據中心和工業市場提供全面的半導體和系統解決方案組合。 產品包括高性能和抗輻射模擬混合信號集成電路、FPGA、SoC和ASIC; 電源管理產品; 計時和同步設備和精確的時間解決方案,設定世界時間標準; 語音處理設備; 射頻解決方案; 分立元件; 企業存儲和通信解決方案、安全技術和可擴展的反tamp呃產品; 以太網解決方案; 以太網供電 IC 和中跨; 以及定制設計能力和服務。 了解更多信息 www.microsemi.com

修訂歷史

修訂歷史記錄描述了文件中實施的變更。變更按修訂版列出,從最新出版物開始。

- 修訂版4.0

以下是此次修訂中所做更改的摘要。

• 更新了Libero SoC v2021.1 的文件。

• 刪除了Libero 版本號的引用。 - 修訂版3.0

以下是本文檔 3.0 版中更改的摘要。

• 更新了Libero SoC 和FlashPro 設計要求。欲了解更多信息,請參閱

設計要求,第 3 頁。

• 在整份文件中,所有相關數字均已更新。 - 修訂版2.0

在本文檔的 2.0 版本中,更新了 Libero SoC v11.7 軟體版本的文件。 - 修訂版1.0

1.0 版是本文檔的首次發布。

IGLOO2 FPGA CoreTSE MAC 1000 Base-T 環回演示

Microsemi 核心三速乙太網路 (CoreTSE) 媒體存取控制器 (MAC) IP 是符合 IEEE 802.3 標準的可設定軟體智慧財產權 (IP) 核心。此演示設計為 IGLOO2 FPGA 提供了乙太網路解決方案,並在 IGLOO1000 評估套件上實現了基於 CoreTSE MAC 的 2 Base-T 環回設計。

CoreTSE MAC 讓系統設計人員能夠實現各種乙太網路設計,從低成本的 10/100 乙太網路到更高效能的 1 GB 連接埠。 CoreTSE MAC 適用於交換器、路由器和資料擷取系統等網路設備。 CoreTSE MAC 也提供與 SmartFusion®2 晶片系統 (SoC) FPGA 系列搭配使用的版本。

CoreTSE MAC 具有以下介面:

- 10/100/1000 Mbps 乙太網路 MAC,具有千兆位元媒體獨立介面 (GMII) 和十位元介面 (TBI),支援串列千兆位元媒體獨立介面 (SGMII)、1000BASE-T 和 1000BASE-X

- GMII 或 TBI 物理層接口連接到以太網 PHY

- MAC 數據路徑接口

- 用於 MAC 設定暫存器和狀態計數器存取的高階週邊匯流排 (APB) 從介面

CoreTSE MAC 可設定為 GMII 或 TBI,用於 10/100/1000 Mbps 資料傳輸速率(線路速度)的乙太網路。

CoreTSE MAC 有兩個不同的版本:

- CoreTSE_AHB:將 AHB 介面用於傳送和接收路徑。該 IP 適用於 SmartFusion2 SoC FPGA。

- CoreTSE(非 AMBA):透過串流資料包介面直接存取 MAC。該 IP 適用於 IGLOO2 FPGA 和 SmartFusion2 SoC FPGA。

CoreTSE 和 CoreTSE_AHB 在支援的功能、暫存器配置和暫存器位址方面與 SmartFusion2 中的 MSS 硬乙太網路 MAC 相同。 IGLOO2 中可以使用多個 CoreTSE MAC IP 來實作乙太網路解決方案。 CoreTSE MAC 可與 MSS 乙太網路 MAC 一起用於 SmartFusion2 設備,以支援多個乙太網路介面。有關 CoreTSE MAC 的更多信息,請參閱 CoreTSE 手冊。

有關乙太網路應用的更多信息,請參閱 AC423:SmartFusion2/IGLOO2 乙太網路應用說明。

筆記: CoreTSE MAC 需要許可證才能在 Libero® 系統單晶片 (SoC) 設計中使用。如需許可證請求,請發送電子郵件至 soc_marketing@microsemi.com

設計要求

下表列出了運行演示的設計要求。

表 1 • 設計要求

筆記:本指南中顯示的 Libero SmartDesign 和設定螢幕截圖僅供說明之用。

打開 Libero 設計以查看最新更新。

先決條件

開始之前:

- 下載並安裝 Libero SoC(如 web此設計的站點)從以下位置在主機 PC 上:

https://www.microsemi.com/product-directory/design-resources/1750-libero-soc - 用於演示設計 filel 下載鏈接: http://soc.microsemi.com/download/rsc/?f=m2gl_dg0633_df

演示設計

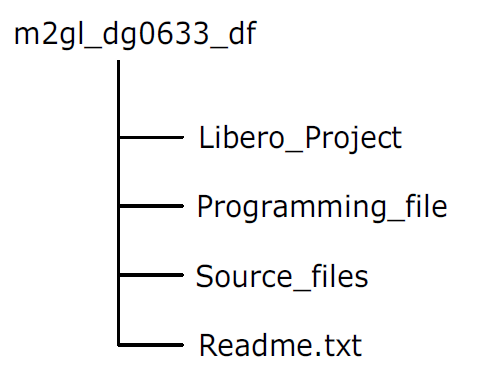

演示設計 file包括:

- 自由人項目

- 程式設計 files

- 來源 files

- 自述文件.txt file

參考Readme.txt file 完整的目錄結構。

下圖顯示了設計的頂層結構 files.

圖 1 演示設計 File頂層結構

圖 2 IGLOO2 CoreTSE MAC 1000 Base-T 環回演示

在此示範設計中,CoreTSE MAC 在 FPGA 結構中實例化,並使用高速串列介面 (SERDES_IF) 連接到板載乙太網路 PHY。

在上圖中,紅色虛線箭頭表示乙太網路封包從主機 PC 到內部 LSRAM 的傳輸,藍色虛線箭頭表示封包從 LSRAM 重新傳輸到主機。

演示設計功能

此示範設計在硬體和模擬中使用 TBI 1000Base-T 中的 CoreTSE MAC 執行乙太網路環回。

以下是演示設計功能:

- CoreTSE MAC 環回設計的模擬模型。

- IGLOO2 評估套件上的 CoreTSE MAC 環回設計。

以下部分介紹了 CoreTSE MAC、SERDES_IF 和環回機制的初始化和配置。

- CoreTSE IP MAC 初始化

CoreTSE MAC 在 TBI 模式下設定。 CoreABC 軟體核心用於初始化 1000 Base-T 和板載乙太網路 PHY 中的 CoreTSE MAC。

註:CoreABC 是 Microsemi 的 RISC 處理器,以邏輯閘實現。 CoreABC IP 可在 Libero SoC 軟體 IP 工具目錄中找到。 - 高速串行介面配置

高速 SERDES_IF 在 Libero GUI 中的外部實體編碼子層 (EPCS) 模式通道 3 中配置,並連接在 CoreTSE MAC 和板載乙太網路 PHY 之間。 - 乙太網路封包環回

本演示中使用了以下以太網環回機制:- 乙太網路封包接收

CoreTSE MAC 透過高速 SERDES_IF 接收來自板載乙太網路 PHY 的乙太網路封包。

CoreTSE MAC 接收 (RX) 路徑透過接收介面邏輯連接到 LSRAM。此介面邏輯在 Verilog RTL 中實現,用於將資料包保存到 LSRAM 記憶體中。 - 乙太網路包傳輸

為了環回乙太網路封包,Verilog RTL 中實現的介面邏輯從 LSRAM 記憶體讀取乙太網路封包數據,並將其保留在 CoreTSE MAC 傳輸 (TX) 路徑上。 CoreTSE MAC 透過高速 SERDES 將乙太網路封包傳輸到板載乙太網路 PHY。

- 乙太網路封包接收

- 以太網測試解決方案

有多種方法可以在 IGLOO1000 評估板上評估 CoreTSE MAC 2 Base-T 環回演示。- 解決方案1

• 安裝在主機PC 上的Cat Karat 封包產生器軟體用於透過RJ45 乙太網路銅纜傳輸乙太網路封包。

• 安裝在主機PC 上的Wireshark 封包接收器軟體透過RJ45 乙太網路銅纜擷取乙太網路封包(環回)。 - 解決方案2

Spirent 測試中心或等效解決方案可用於測試 CoreTSE MAC 環回演示。如需了解更多信息,請參閱附錄 2:使用 Spirent 測試中心運行演示設計,第 18 頁。

- 解決方案1

演示設計說明

此演示設計是透過將 CoreTSE MAC 配置為 TBI 模式來實現的。下圖顯示了此示範設計的 Libero SoC 硬體實作。

Libero 硬件項目使用以下資源:

- 核心TSE MAC

- CoreABC 用於配置 CoreTSE MAC 和板載乙太網路 PHY

- LSRAM介面邏輯使用TPSRAM,接收和發送邏輯在Verilog RTL中實現

- 為 EPCS 通道 3 模式配置的高速串行接口 (SERDES_IF)

- 專用輸入焊盤 0 作為時鐘源

模擬設計

此測試平台設計是為 CoreTSE MAC 環回演示創建的。測試台將乙太網路封包傳送至 CoreTSE MAC 環回示範設計,並從 CoreTSE MAC 環回示範設計接收環回乙太網路封包。

模擬

為了進行模擬,乙太網路封包在文字中定義 file: (m2gl_dg0633_df\Libero_Project\Simulation\CoreTSE_1000BaseT_Demo\simulation\ 資料包file。

The Raw Ethernet Packet frame is: 0102030405060708090a0b0c0d0e5555555555555555555555551b1c1d1e1f202122232425262728292 a2b2c2d2e2f303132333435363738393a3b3c3d3e3f40.

Testbench從文字中讀取乙太網路封包 file 並將乙太網路封包放到CoreTSE MAC環回設計的高速SERDES_IF上。

環回資料包由測試平台接收並顯示在 ModelSim 轉錄視窗上。

下圖和第 5 頁的圖 8 顯示了用於模擬 CoreTSE MAC 環回演示設計的 Libero SmartDesign。模擬測試平台具有以下 Libero 組件:

- 核心TSE MAC

- 高速 SERDES_IF

- 具有資料包發送和資料包接收邏輯的測試平台

testbench智慧設計模組從封包中讀取乙太網路封包file。 file 並透過高速串列介面將其傳送至IGLOO2 CoreTSE MAC環回設計。環回乙太網路封包由測試台透過高速串列介面接收。 ModelSim 在轉錄視窗上顯示收到的乙太網路封包。這樣就完成了乙太網路封包環回模擬。

Libero SmartDesign 頂層模組包含 CoreTSE MAC 環回設計和測試平台模組。

以下步驟說明如何模擬示範:

- 從以下設計開啟Libero項目 files: m2gl_dg0633_df\Libero_Project\Simulation\CoreTSE_1000BaseT_Demo\Libero_Project.prjx。

- 在「設計流程」標籤中的「驗證預綜合設計」下,雙擊「模擬」。 ModelSim 運作設計 180 μs。下圖為ModelSim Transcript 視窗中顯示的接收到的乙太網路封包資訊。

下圖和第 8 頁的圖 9 顯示了波形視窗。突出顯示的部分顯示了發送和接收的乙太網路資料包。

設置演示設計

以下步驟描述瞭如何設置演示:

- 將跳線連接到 IGLOO2 FPGA 評估套件板,如下表所示。

- 將電源連接至 J6 連接器並開啟。

- 將 FlashPro4 程式設計器連接到 IGLOO5 FPGA 評估套件板上的 J2 連接器。

筆記: 將跳線連接到 IGLOO7 FPGA 評估套件時,請確保電源開關 SW2 關閉。

表 2 IGLOO2 FPGA 評估套件跳線設置

| 跳線 | 引腳(來自) | 引腳(到) | 評論 |

| J22 | 1 | 2 | 預設 |

| J23 | 1 | 2 | 預設 |

| J24 | 1 | 2 | 預設 |

| J8 | 1 | 2 | 預設 |

| J3 | 1 | 2 | 預設 |

對設備進行編程

使用作業對 IGLOO2 評量套件板進行編程 file 作為設計的一部分提供 file若要使用 FlashPro Express 軟體,請參閱附錄 1:使用 FlashPro Express 對裝置進行編程,第 15 頁。

將 IGLOO2 評估套件板連接到主機 PC

以下步驟說明如何將 IGLOO2 評估套件板連接到主機 PC:

- 成功編程後,關閉 IGLOO2 評估套件板。

- 使用 RJ13 纜線將主機 PC 連接到 IGLOO2 評估套件上的 J45 連接器。

下圖顯示了 IGLOO2 評估套件板設定。

在硬體上使用 Cat Karat 和 Wireshark 運行演示設計

以下步驟描述瞭如何運行演示設計:

- 打開電源開關 SW7。

- 從源碼在主機PC上安裝Cat Karat packet軟件和Wireshark軟件 files。 (m2gl_dg0633_df\來源 files)

- 在主機 PC 上,開啟 Wireshark 網路分析器。選擇開始,如第 10 頁圖 12 所示。

- 在主機PC上,打開Cat Karat軟件,如下圖所示。

- 根據協議 View,按一下「控制」標籤,然後為「每次突發的資料包數」輸入值 1,如第 12 頁的圖 13 所示。

- 在“資料包流”下,按一下“使用 RAW”,如第 11 頁的圖 13 所示。

- 根據協議 View,選擇RAW選項卡並從來源複製並貼上乙太網路封包 files (m2gl_dg0633_df\源_files\Raw_frame.txt),如圖 11,第 13 頁所示。

- 在介面下,選擇 IGLOO2 評估板的乙太網路連接。

- 從菜單中選擇 Start Transmit,如圖 11,第 13 頁所示,以傳輸數據包。

- 在Wireshark軟件窗口中,雙擊Ethernet-II,如下圖所示。 顯示發送和接收的以太網數據包。

附錄 1:使用 FlashPro Express 對器件進行編程

本節介紹如何使用程式設計作業對 IGLOO2 裝置進行程式設計 file 使用 FlashPro Express。

要對器件進行編程,請執行以下步驟:

- 確保電路板上的跳線設置與第 2 頁表 10 中列出的設置相同。

注意:進行跳線連接時必須關閉電源開關。 - 將電源線連接到電路板上的 J6 連接器。

- 打開電源開關 SW7。

- 在主機 PC 上,啟動 FlashPro Express 軟件。

- 單擊新建或從項目菜單中選擇 New Job Project from FlashPro Express Job 創建一個新的作業項目,如下圖所示。

- 在來自 FlashPro Express 作業的新建作業項目對話框中輸入以下內容:

- 編程工作 file:單擊瀏覽,然後導航到 .job 所在的位置 file 位於並選擇 file。預設位置是: \m2gl_dg0633_df\編程file

- FlashPro Express 作業項目名稱:單擊瀏覽並導航到要保存項目的位置。

- 單擊確定。 所需的編程 file 被選中並準備在設備中進行編程。

- FlashPro Express 窗口如下圖所示。 確認程序員編號出現在程序員字段中。 如果沒有,請確認電路板連接並單擊 Refresh/Rescan Programmers。

- 單擊運行。 當設備燒錄成功後,會顯示 RUN PASSED 狀態,如下圖所示。

- 關閉 FlashPro Express 或在“項目”選項卡中單擊“退出”。

附錄 2:使用 Spirent 測試中心運行演示設計

以下步驟說明如何使用 Spirent 測試中心執行 CoreTSE MAC 環回示範:

- 使用 RJ2 電纜將 IGLOO1 評估套件連接到 Spirent 測試設備上的插槽 45 乙太網路連接埠。

- 在主機 PC 中,開啟 Spirent 測試中心配置器。

- 在Spirent測試中心新增連接埠(乙太網路),如下圖所示。

- 按一下“連接埠”下的“流量產生器”,在流塊編輯器中新增資料包信息,然後按一下“確定”,如第 20 頁的圖 19 所示。

- 點選“開始所有連接埠上的流量”,如圖20所示。

- 觀察總 TX、RX、RX FCS 和 CRC 錯誤計數。圖 20 顯示了思博倫測試中心的 TX、RX、RX FCS 和 CRC 錯誤總數資訊。 0表示資料包發送和接收沒有遺失。

文件/資源

|

Microsemi DG0633 IGLOO2 FPGA CoreTSE MAC 1000 Base-T 環回演示 [pdf] 使用者指南 DG0633 IGLOO2 FPGA CoreTSE MAC 1000 Base-T 環回演示、DG0633、IGLOO2 FPGA CoreTSE MAC 1000 Base-T 環回演示、Base-T 環回演示 |