VHDLwhiz.com

VHDLwhiz.com

د AXI سټایل UART ماډلونه

د کارن لارښود

د AXI سټایل UART ماډلونه

| نسخه: | 1.0.3 |

| نېټه: | د می 18، 2023 |

| محصول URL: | https://vhdlwhiz.com/product/vhdl-module-axi-style-uart/ |

| د اړیکې بریښنالیک: | jonas@vhdlwhiz.com |

دا سند تشریح کوي چې څنګه د VHDLwhiz عمومي هدف، AXI-مطابقت، یونیورسل اسینکرونوس ریسیور-ټرانسمیټر (UART) VHDL ماډلونه کارول کیږي.

جواز

د MIT جواز د سرچینې کوډ د کاپي حق اړتیاوې او د کارولو شرایط پوښي.

LICENSE.txt ته مراجعه وکړئ file په زپ کې file د جزیاتو لپاره.

بدلون

دا بدلونونه پروژې ته اشاره کوي files، او دا سند د دې مطابق تازه کیږي.

| نسخه | څرګندونې | |

| 1.0.0 | ابتدايي خوشې کول | |

| 1.0.1 | • دا کارن لارښود جوړ کړی • په top.vhd کې د ځان بیا تنظیم کولو پروسه بدله شوې file د جلا reset_sync.vhd ماډل سره • د دې بورډونو لپاره د ډیمو UART لوپ بیک پروژې اضافه شوي: o Xilinx Arty A7 35T (Vivado) o Xilinx arty S7 50 (Vivado) o تراسیک DE10-Lite + Digilent Pmod USBUART (Quartus) |

|

| 1.0.2 | • د داخلي کاونټر سمت بدلول ترڅو ډاډ ترلاسه شي چې ماډلونه هم د ابتدايي ری سیٹ سټروب پرته کار کوي | |

| 1.0.3 | • په uart_buffered ماډل کې د TX FIFO ژورې جنریک نقشه غلطه شوې. دا د RX ژوروالي ته نقشه شوې وه. | |

تفصیل

دا پروژه درې عمومي موخې لري، د AXI مطابقت لرونکی، یونیورسل اسینکرونوس ریسیور-ټرانسمیټر (UART) ماډلونه.

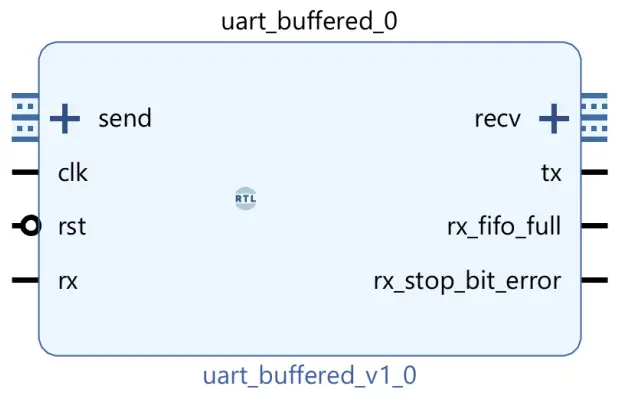

تاسو کولی شئ د جلا ترلاسه کونکي (uart_rx.vhd) او ټرانسمیټر (uart_tx.vhd) ماډلونو یا یو ګډ UART ماډل (uart_buffered.vhd) ترمنځ د جوړ شوي ان پټ او آوټ پوټ بفرینګ سره انتخاب کړئ.  ټول درې ماډلونه د چمتو / باوري لاسي صندقونو کارولو له لارې د جریان کنټرول لري. او ځکه چې د سیګنال نوم ورکولو سکیم د Xilinx AXI معیار سره سمون لري، د لیږلو او recv بندرونه به د ویواډو بلاک ډیزاین مدیر کې د بس انٹرفیس په توګه څرګند شي، لکه څنګه چې په پورته عکس کې ښودل شوي.

ټول درې ماډلونه د چمتو / باوري لاسي صندقونو کارولو له لارې د جریان کنټرول لري. او ځکه چې د سیګنال نوم ورکولو سکیم د Xilinx AXI معیار سره سمون لري، د لیږلو او recv بندرونه به د ویواډو بلاک ډیزاین مدیر کې د بس انٹرفیس په توګه څرګند شي، لکه څنګه چې په پورته عکس کې ښودل شوي.

د سیسټم ساعت فریکوینسي او د بوډ نرخ د تنظیم وړ دي. د ډیټا بټ شمیره 8 (یو بایټ) ته ټاکل شوې ، سټاپ بټ 1 ته ټاکل شوی ، او برابري نه کارول کیږي.

UART RX/TX د بلاک رام بفرینګ سره

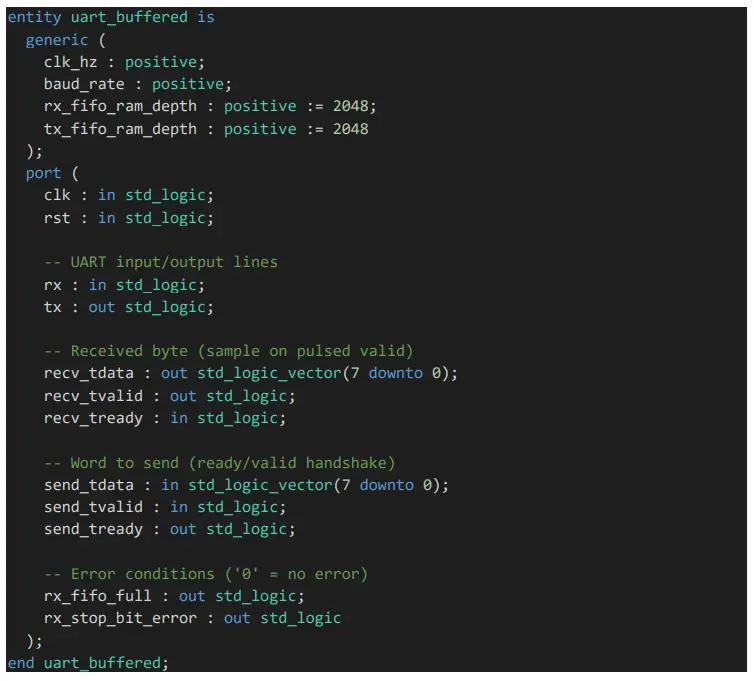

د uart_buffered.vhd ماډل د لیږلو او ترلاسه کولو بندرونو کې د AXI سټایل لوستلو/درست سیګنال سکیم له لارې د جریان کنټرول جوړ شوی دی. د معلوماتو لیږد یوازې هغه وخت پیښیږي کله چې _تحقيق او _tready د ورته لوړیدونکي ساعت څنډې په جریان کې '1' دي.

بفر شوي بایټونه په بلاک رام کې زیرمه کیږي تر هغه چې دوی د دې ماډل لخوا لیږل شوي یا لوستل کیږي. د بلاک RAM ژوروالی د جنریکونو له لارې تنظیم کیدونکی دی، مګر د FIFO اندازه به هغه شمیره منفي یو وي ځکه چې داخلي FIFO تل د بشپړ او خالي حالتونو ترمینځ توپیر کولو لپاره یو سلاټ خلاص ساتي.

لاندې لیست د دې ماډل لپاره وجود ښیې.  UART RX

UART RX

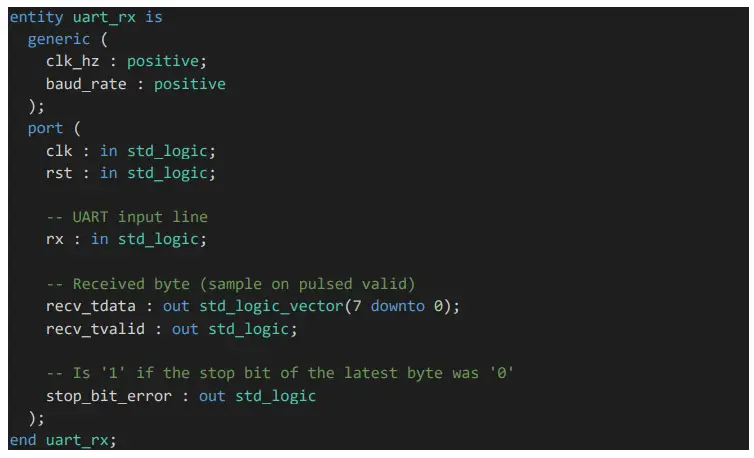

د uart_rx.vhd ماډل یو غیر بفر شوی UART اخیستونکی لري. ترلاسه شوي معلومات د recv_tdata لاین کې ښکاري او د اعتبار وړ وي کله چې recv_tvalid '1' وي.

لاندې لیست د ترلاسه کونکي ماډل لپاره اداره ښیې.  UART TX

UART TX

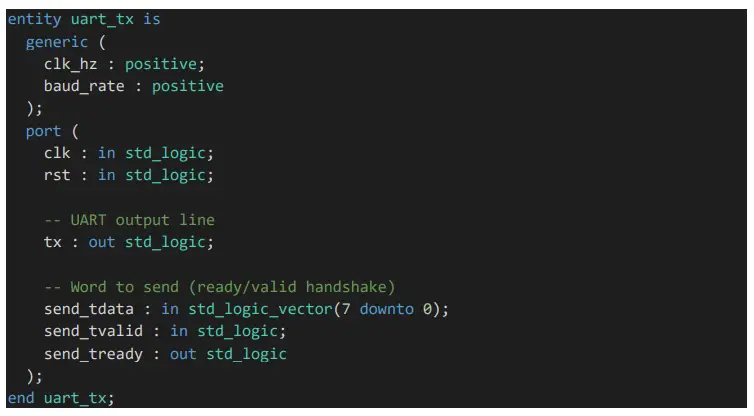

د uart_tx.vhd ماډل یو غیر بفر شوی UART لیږدونکی لري. په send_tdata کې ایښودل شوي ډاټا لیږدول کیږي کله چې send_tvalid '1' وي.

لاندې لیست د لیږدونکي ماډل لپاره اداره ښیې.

زپ File منځپانګه

| ├── loopback_demo | د UART لوپ بیک ډیمو پروژې |

| │ ├── icecube2_icestick | د لاټیس iCEstick بورډ لپاره iCEcube2 پروژه |

| │ ├── quartus_de10_lite | د Terasic DE10-Lite بورډ لپاره د کوارټس پروژه |

| │ ├── top_sim | د ډیمو پروژې لپاره د لوړې کچې ټیسټ بینچ |

| │ ├── top_src | د ډیمو پروژې لپاره د لوړې کچې ماډل |

| │ ├── vivado_arty_a7_35t | د Xilinx Arty A7 35T بورډ لپاره Vivado پروژه |

| │ └── vivado_arty_s7_50 | د Xilinx Arty S7 50 بورډ لپاره Vivado پروژه |

| ├── uart_sim | د UART ماډلونو لپاره ټیسټ بینچ |

| └── uart_src | UART VHDL ماډلونه |

د ډیزاین سمول

په Zip کې دوه د ځان چک کولو ټیسټ بینچونه شتون لري file، یو د uart_buffered ماډل لپاره او یو د عمومي ټاپ ماډل لپاره چې په ډیمو پروژو کې کارول کیږي.

د VHDL ټیسټ بینچ باید په هر وړ VHDL سمیلیټر کې کار وکړي چې د 2008 بشپړ VHDL بیاکتنې ملاتړ کوي ، مګر چمتو شوي run.do سکریپټونه یوازې په ModelSim/Questa کې کار کوي.

د UART ټیسټ بینچ چلول

موډلسیم/کوستا خلاص کړئ او سمیلیټر کنسول کې ټایپ کړئ: cd do uart_sim/run.do runtb

د لوړې کچې ټیسټ بینچ چلول

موډلسیم/کوستا خلاص کړئ او سمیلیټر کنسول کې ټایپ کړئ: cd do loopback_demo/top_sim/run.do runtb

د ډیمو پروژو پلي کول

زپ file د ټاکل شوي پراختیایی بورډونو لپاره ډیمو پروژې لري.

که تاسو غواړئ ډیمو په مختلف بورډ کې هڅه وکړئ، تاسو کولی شئ د loopback_demo/top_src/top.vhd ماډل لپاره یو ریپر جوړ کړئ. پورته معاینه کړئ_ .vhd files او یو د خپل بورډ د پن ترتیب او د ساعت فریکونسۍ سره سم تنظیم کړئ.

د پخوانيample ډیزاین د uart_buffered ماډل انسټاګرام کوي او د UART RX پن څخه د TX پن ته هر بایټ ترلاسه کوي.

د باډ نرخ 115200 ته ټاکل شوی ، مګر تاسو کولی شئ دا د پورتنۍ ریپر VHDL بدلولو سره بدل کړئ files په هر لوپ بیک_ډیمو فرعي فولډر کې.

جالی iCEstick

loopback_demo/icecube2_icestick فولډر کې د لوپ بیک تطبیق شامل دی latticesemi.com/icestick د FPGA بورډ

د تطبیق پروسې پرمخ وړلو لپاره، loopback_demo/icecube2_icestick/icecube2_project/loopback_demo_sbt.project خلاص کړئ file په iCEcube2 | د FPGA ډیزاین سافټویر | لاټیس سیمیکمډکټر ډیزاین سافټویر.

په iCEcube2 GUI کې د پروژې له پورته کولو وروسته، د برنامه کولو بټ میپ تولیدولو لپاره اوزار → ټول چل کړئ کلیک وکړئ file.

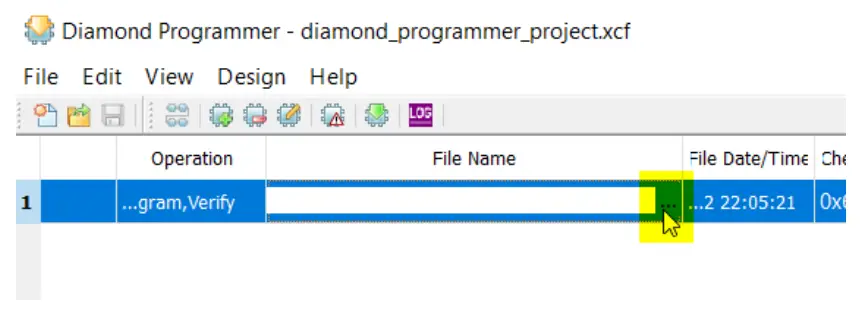

تاسو کولی شئ وکاروئ د لاټیس ډیمنډ پروګرامر او د ځای پرځای کولو وسیله (latticesemi.com) د تولید شوي بټ میپ سره د FPGA تنظیم کولو وسیله file. کله چې د ډیمنډ پروګرامر خلاص شي، د ښه راغلاست ډیالوګ بکس کې د موجوده پروګرامر پروژه پرانیزئ کلیک وکړئ.

پروژه غوره کړئ file په زپ کې موندل کیږي:

loopback_demo/icecube2_icestick/diamond_programmer_project.xcf او OK کلیک وکړئ.  وروسته له دې چې د پروژې لوډ شي، په درې نقطو کلیک وکړئ File د نوم کالم، لکه څنګه چې پورته ښودل شوي. د بټ میپ غوره کولو لپاره لټون وکړئ file چې تاسو په iCEcube2 کې رامینځته کړی:

وروسته له دې چې د پروژې لوډ شي، په درې نقطو کلیک وکړئ File د نوم کالم، لکه څنګه چې پورته ښودل شوي. د بټ میپ غوره کولو لپاره لټون وکړئ file چې تاسو په iCEcube2 کې رامینځته کړی:

loopback_demo/icecube2_icestick/icecube2_project/loopback_demo_Implmnt/sbt/outputs /bitmap/top_icestick_bitmap.bin په پای کې، ستاسو په کمپیوټر کې د USB پورټ سره د iCEstick بورډ سره نښلول، د SPI فلش او GA ترتیبولو لپاره ډیزاین → پروګرام غوره کړئ.

تاسو اوس کولی شئ د سیریل ټرمینل په کارولو سره د لوپ بیک ډیزاین ازموینې ته لاړشئ.

Xilinx Arty A7 35T

تاسو کولی شئ د ډیمو پلي کولو لپاره ومومئ Artix-7 35T آرټي FPGA د ارزونې کټ په loopback_demo/vivado_arty_a7_35t فولډر کې.

خلاص Vivado – ويکيپېډيا او استخراج ته لاړ شئ fileد Tcl کنسول کارول د GUI انٹرفیس په ښکته کې موندل شوي. د ډیمو پروژې فولډر ته د ننوتلو لپاره دا کمانډ ولیکئ:

cd /loopback_demo/vivado_arty_a7_35t/

د Vivado پروژې د بیا جوړولو لپاره create_vivado_proj.tcl Tcl سکریپټ اجرا کړئ:

سرچینه ./create_vivado_proj.tcl

په سائډبار کې د بټ سټریم تولید کلیک وکړئ ترڅو د پلي کولو ټولو مرحلو څخه تیر شي او د برنامه بټ سټریم تولید کړئ file.

په نهایت کې ، د هارډویر مدیر خلاص کړئ کلیک وکړئ او د GUI له لارې FPGA برنامه کړئ.

بټfile باید په دې فولډر کې وي:

<zip_content>/loopback_demo/vivado_arty_a7_35t/loopback_demo.runs/impl_1/top_arty_ a7_35t.bit

تاسو اوس کولی شئ د سیریل ټرمینل په کارولو سره د لوپ بیک ډیزاین ازموینې ته لاړشئ.

Xilinx Arty S7 50

تاسو کولی شئ د ډیمو پلي کولو لپاره ومومئ Spartan-7 FPGA پراختیایی بورډ د شوقیانو لپاره - Digilent Arty S7 - Xilinx په loopback_demo/vivado_arty_s7_50 فولډر کې د پراختیا بورډ.

خلاص Vivado – ويکيپېډيا او استخراج ته لاړ شئ fileد Tcl کنسول کارول د GUI انٹرفیس په ښکته کې موندل شوي. د ډیمو پروژې فولډر ته د ننوتلو لپاره دا کمانډ ولیکئ: cd /loopback_demo/vivado_arty_s7_50/

د Vivado پروژې د بیا جوړولو لپاره create_vivado_proj.tcl Tcl سکریپټ اجرا کړئ: سرچینه ./create_vivado_proj.tcl

په سائډبار کې د بټ سټریم تولید کلیک وکړئ ترڅو د پلي کولو ټولو مرحلو څخه تیر شي او د برنامه بټ سټریم تولید کړئ file.

په نهایت کې ، د هارډویر مدیر خلاص کړئ کلیک وکړئ او د GUI له لارې FPGA برنامه کړئ.

بټfile باید په دې فولډر کې وي: /loopback_demo/vivado_arty_s7_50/loopback_demo.runs/impl_1/top_arty_s 7_50.bit

تاسو اوس کولی شئ د سیریل ټرمینل په کارولو سره د لوپ بیک ډیزاین ازموینې ته لاړشئ.

Terasic DE10-Lite د Digilent Pmod USBUART سره

د لوپ بیک ډیمو لپاره DE10-Lite تخته له Terasic څخه، د Intel's MAX 10 FPGA په کارولو سره، د لوپ بیک_demo/quartus_de10_lite فولډر کې دی.

ځکه چې د DE10-Lite بورډ یو جوړ شوی UART نه USB انٹرفیس نلري، موږ به د Digilent پلګ ایبل وکاروو Pmod USBUART - دقیق حواله د دې لپاره.

| DE10-Lite سرلیک پن | Pmod USBUART پن |

| د Arduino سرلیک IO13 | 2 RXD |

| د Arduino سرلیک IO12 | 3 TXD |

| د Arduino سرلیک GND | 5 GND |

| د Arduino سرلیک VCC3P3 | 6 VCC |

DE10-Lite او Pmod په پورتني جدول کې د پن نقشې مطابق سره وصل کړئ، لکه څنګه چې په لاندې عکس کې ښودل شوي.  پروژه پرانیزئ file په کوارټس کې د ډیزاین بارولو لپاره: /loopback_demo/quartus_de10_lite/loopback_demo.qpf

پروژه پرانیزئ file په کوارټس کې د ډیزاین بارولو لپاره: /loopback_demo/quartus_de10_lite/loopback_demo.qpf

د اړخ بار څخه د تالیف ډیزاین کلیک وکړئ

د سایډبار څخه د برنامه وسیله (خلاص پروګرامر) کلیک وکړئ

برنامه کول file باید په اتوماتيک ډول وټاکل شي. تاسو یې دلته موندلی شئ: /loopback_demo/quartus_de10_lite/output_files/loopback_demo.sof

د UART لوپ بیک ازموینه

تاسو کولی شئ د بورډ سره د خبرو اترو لپاره هر سریال ټرمینل برنامه وکاروئ ، مګر زه وړاندیز کوم sourceforge.net/projects/ya-terminal/ l که تاسو لا دمخه نصب نه وي کړی.

ټرمینل → ترتیباتو ته لاړشئ او د باډ نرخ 115200 ته وټاکئ ، د ډیټا بیټ 8 ته ، هیڅ نه ته برابر کړئ او 1 ته بیټس ودروئ ، لکه څنګه چې لاندې سکرین شاټ کې ښودل شوي.  بورډ یا Pmod UART ماډل خپل کمپیوټر ته د USB له لارې وصل کړئ.

بورډ یا Pmod UART ماډل خپل کمپیوټر ته د USB له لارې وصل کړئ.

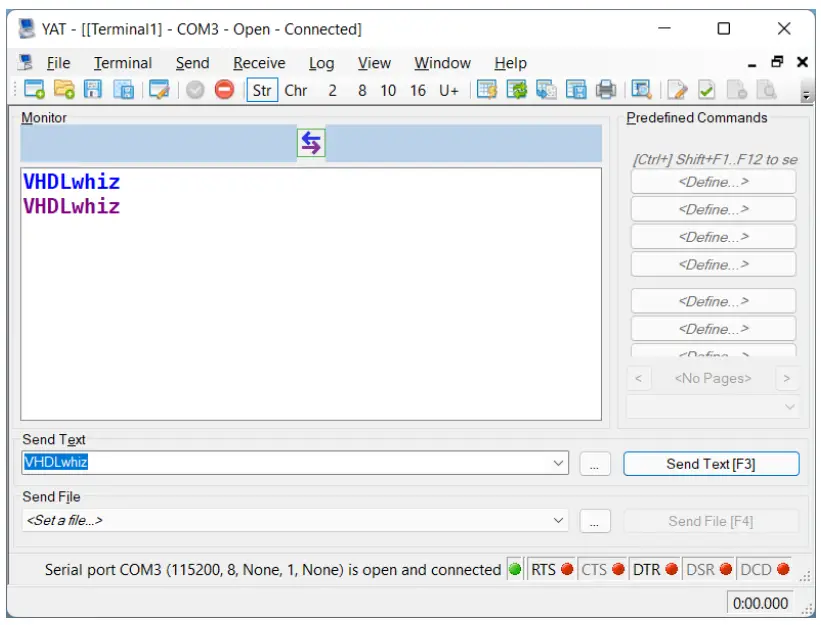

په نهایت کې، ټرمینل → خلاص/ پیل کړئ، د متن لیږلو ساحه کې ځینې حروف دننه کړئ او د متن لیږلو تڼۍ کېکاږئ. لیږل شوی متن به په نیلي کې څرګند شي، او که چیرې FPGA ځواب ورکړي، یو ځل بیا د ارغواني رنګ لاندې به یو ځل بیا راڅرګند شي.

تاسو کولی شئ یو پخوانی وګورئampپه لاندې سکرین شاټ کې د بریالۍ ازموینې څخه.

پیژندل شوي مسایل

د UART ټرانسمیټر ماډل د Yosys اوپن سورس ترکیب سویټ سره سم کار نه کوي.

په uart_tx.vhd کې د clk_counter_wrapped ناپاک فعالیت file لکه څنګه چې په دې وسیله کې هدف نه ترکیب کیږي.

د چاپ حق VHDLwhiz.com

د چاپ حق VHDLwhiz.com

اسناد / سرچینې

|

VHDLwhiz AXI سټایل UART ماډلونه [pdf] د کارونکي لارښود AXI-Style UART ماډلونه، UART ماډلونه، ماډلونه |