## VHDLwhiz AXI-Style UART Modules User Manual

Home » VHDLwhiz » VHDLwhiz AXI-Style UART Modules User Manual

AXI-Style UART Modules

User Manual

#### **Contents**

- 1 AXI-Style UART Modules

- 2 License

- 3 Changelog

- 4 Description

- **5 Zip File Content**

- 6 Simulating the design

- 7 Implementing the demo projects

- 8 Testing the UART loopback

- 9 Known Issues

- 10 Documents / Resources

- 10.1 References

- 11 Related Posts

**AXI-Style UART Modules**

| Version:       | 1.0.3                                                    |

|----------------|----------------------------------------------------------|

| Date:          | May 18, 2023                                             |

| Product URL:   | https://vhdlwhiz.com/product/vhdl-module-axi-style-uart/ |

| Contact email: | jonas@vhdlwhiz.com                                       |

This document describes how to use VHDLwhiz's general-purpose, AXI-compatible, universal asynchronous receiver-transmitter (UART) VHDL modules.

#### License

The MIT license covers the source code's copyright requirements and terms of use. Refer to the LICENSE.txt file in the Zip file for details.

## Changelog

These changes refer to the project files, and this document is updated accordingly.

| Version | Remarks                                                                                                                                                                                                                                                                                                 |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0.0   | Initial release                                                                                                                                                                                                                                                                                         |

| 1.0.1   | Created this user manual     Replaced self-reset process in the top.vhd file with a separate reset_sync.vhd module     Added demo UART loopback projects for these boards:     O Xilinx Arty A7 35T (Vivado)     O Xilinx arty S7 50 (Vivado)     O Terasic DE10-Lite + Digilent Pmod USBUART (Quartus) |

| 1.0.2   | Changing the direction of an internal counter to make sure that the modules also work wi<br>thout an initial reset strobe                                                                                                                                                                               |

| 1.0.3   | Fixed wrong TX FIFO depth generics mapping in the uart_buffered module. It was mapp ed to the RX depth.                                                                                                                                                                                                 |

## **Description**

This project contains three general-purpose, AXI compatible, universal asynchronous receiver-transmitter (UART) modules.

You can choose between the separate receiver (uart\_rx.vhd) and transmitter (uart\_tx.vhd) modules or a combined UART module (uart\_buffered.vhd) with built-in input and output buffering.

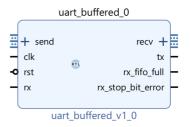

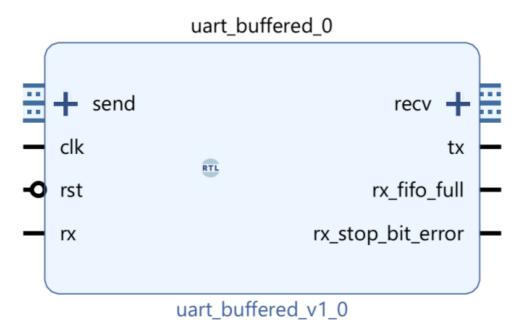

All three modules have built-in flow control through the use of ready/valid handshake signals. And because the signal naming scheme matches the Xilinx AXI standard, the send and recv ports will appear as bus interfaces in the Vivado Block Design editor, as shown in the image above.

The system clock frequency and the baud rate are configurable. Data bit count is fixed to 8 (one byte), stop bits is set to 1, and parity is not used.

#### **UART RX/TX with block RAM buffering**

The uart\_buffered.vhd module has built-in flow control through the AXI-style read/valid signaling scheme on the send and receive ports. Data transfer only happens when <send/recv>\_tvalid and <send/recv>\_tready are '1' during the same rising clock edge.

Buffered bytes are stored in block RAM until they are sent by this module or read from it. The block RAM depth is configurable through generics, but the FIFO size will be that number minus one because the internal FIFO always keeps one slot open to distinguish between the full and empty states.

The listing below shows the entity for this module.

```

entity uart_buffered is

generic (

clk_hz : positive;

baud_rate : positive;

rx_fifo_ram_depth : positive := 2048;

tx_fifo_ram_depth : positive := 2048

);

port (

clk : in std_logic;

rst : in std logic;

rx : in std_logic;

tx : out std_logic;

-- Received byte (sample on pulsed valid)

recv_tdata : out std_logic_vector(7 downto 0);

recv_tvalid : out std_logic;

recv_tready : in std_logic;

-- Word to send (ready/valid handshake)

send_tdata : in std_logic_vector(7 downto 0);

send_tvalid : in std_logic;

send_tready : out std_logic;

-- Error conditions ('0' = no error)

rx_fifo_full : out std_logic;

rx_stop_bit_error : out std_logic

);

end uart_buffered;

```

## **UART RX**

The uart\_rx.vhd module contains an unbuffered UART receiver. Received data appears on the recv\_tdata line and is valid when recv\_tvalid is '1'.

The listing below shows the entity for the receiver module.

```

entity uart_rx is

generic (

clk_hz : positive;

baud_rate : positive

);

port (

clk : in std_logic;

rst : in std_logic;

-- UART input line

rx : in std_logic;

-- Received byte (sample on pulsed valid)

recv_tdata : out std_logic_vector(7 downto 0);

recv_tvalid : out std_logic;

-- Is '1' if the stop bit of the latest byte was '0'

stop_bit_error : out std_logic

);

end uart_rx;

```

#### **UART TX**

The uart\_tx.vhd module contains an unbuffered UART transmitter. Data put on send\_tdata is transmitted when send\_tvalid is '1'.

The listing below shows the entity for the transmitter module.

```

entity uart_tx is

generic (

clk_hz : positive;

baud_rate : positive

);

port (

clk : in std_logic;

rst : in std_logic;

-- UART output line

tx : out std_logic;

-- Word to send (ready/valid handshake)

send_tdata : in std_logic_vector(7 downto 0);

send_tvalid : in std_logic;

send_tready : out std_logic

);

end uart_tx;

```

## **Zip File Content**

| loopback_demo       | UART loopback demo projects                     |

|---------------------|-------------------------------------------------|

| icecube2_icestick   | iCEcube2 project for the Lattice iCEstick board |

| quartus_de10_lite   | Quartus project for the Terasic DE10-Lite board |

|                     | Top-level testbench for the demo project        |

|                     | Top-level module for the demo project           |

| vivado_arty_a7_35t  | Vivado project for the Xilinx Arty A7 35T board |

| L vivado_arty_s7_50 | Vivado project for the Xilinx Arty S7 50 board  |

| uart_sim            | Testbench for the UART modules                  |

| L uart_src          | UART VHDL modules                               |

## Simulating the design

There are two self-checking testbenches in the Zip file, one for the uart\_buffered module and one for the generic top module used in the demo projects.

The VHDL testbench should work in any capable VHDL simulator supporting the full 2008 VHDL revision, but the provided run.do scripts only work in ModelSim/Questa.

#### **Running the UART testbench**

Open ModelSim/Questa and type in the simulator console: cd <zip\_content> do uart\_sim/run.do runtb **Running the top-level testbench**

Open ModelSim/Questa and type in the simulator console: cd <zip\_content> do loopback\_demo/top\_sim/run.do runtb

#### Implementing the demo projects

The Zip file contains demo projects for selected development boards.

If you want to try the demo on a different board, you can create a wrapper for the loopback\_demo/top\_src/top.vhd module. Examine the top\_<board\_name>.vhd files and customize one to suit your board's pin configuration and clock frequency.

The example design instantiates the uart\_buffered module and echoes any bytes it receives over the UART RX pin to the TX pin.

The baud rate is set to 115200, but you can change that by altering the top wrapper VHDL files in each loopback demo subfolder.

#### Lattice iCEstick

The loopback\_demo/icecube2\_icestick folder contains the loopback implementation for the latticesemi.com/icestick FPGA board.

To run through the implementation process, open the loopback\_demo/icecube2\_icestick/icecube2\_project/loopback\_demo\_sbt.project file in the <u>iCEcube2 | FPGA Design Software | Lattice Semiconductor design software.</u>

After loading the project in the iCEcube2 GUI, click Tools→Run All to generate the programming bitmap file.

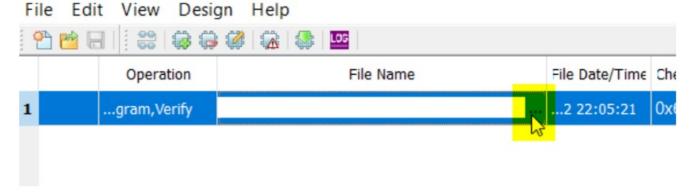

You can use the <u>Lattice Diamond Programmer and Deployment Tool (latticesemi.com)</u> tool to configure the FPGA with the generated bitmap file. When Diamond Programmer opens, click Open an existing programmer project in the welcome dialog box.

Select project file found in the Zip:

loopback demo/icecube2 icestick/diamond programmer project.xcf and click OK.

# Diamond Programmer - diamond\_programmer\_project.xcf

After the project loads, click the three dots in the File Name column, as shown above. Browse to select the bitmap file that you generated in iCEcube2:

loopback\_demo/icecube2\_icestick/icecube2\_project/loopback\_demo\_Implmnt/sbt/outputs /bitmap/top\_icestick\_bitm ap.bin Finally, with the iCEstick board plugged into a USB port on your computer, select Design→Program to program the SPI flash and configure the FPGA.

You can now proceed to test the loopback design using a serial terminal.

## Xilinx Arty A7 35T

You can find the demo implementation for the <u>Artix-7 35T Arty FPGA</u> evaluation kit in the loopback\_demo/vivado\_arty\_a7\_35t folder.

Open <u>Vivado – Wikipedia</u> and navigate to the extracted files using the Tcl console found at the bottom of the GUI interface. Type this command to enter the demo project folder:

cd <zip\_content>/loopback\_demo/vivado\_arty\_a7\_35t/

Execute the create\_vivado\_proj.tcl Tcl script to regenera te the Vivado project:

source ./create\_vivado\_proj.tcl

Click Generate Bitstream in the sidebar to run through all the implementation steps and generate the programming bitstream file.

Finally, click Open Hardware Manager and program the FPGA through the GUI.

The bitfile should be in this folder:

<zip\_content>/loopback\_demo/vivado\_arty\_a7\_35t/loopback\_demo.runs/impl\_1/top\_arty\_ a7\_35t.bit

You can now proceed to test the loopback design using a serial terminal.

#### Xilinx Arty S7 50

You can find the demo implementation for the <u>Spartan-7 FPGA Development Board for Hobbyists – Digilent Arty S7 – Xilinx</u> development board in the loopback\_demo/vivado\_arty\_s7\_50 folder.

Open <u>Vivado – Wikipedia</u> and navigate to the extracted files using the Tcl console found at the bottom of the GUI interface. Type this command to enter the demo project folder: cd

<zip\_content>/loopback\_demo/vivado\_arty\_s7\_50/

Execute the create\_vivado\_proj.tcl Tcl script to regenerate the Vivado project: source ./create\_vivado\_proj.tcl Click Generate Bitstream in the sidebar to run through all the implementation steps and generate the programming bitstream file.

Finally, click Open Hardware Manager and program the FPGA through the GUI.

The bitfile should be in this folder:

<zip\_content>/loopback\_demo/vivado\_arty\_s7\_50/loopback\_demo.runs/impl\_1/top\_arty\_s 7\_50.bit

You can now proceed to test the loopback design using a serial terminal.

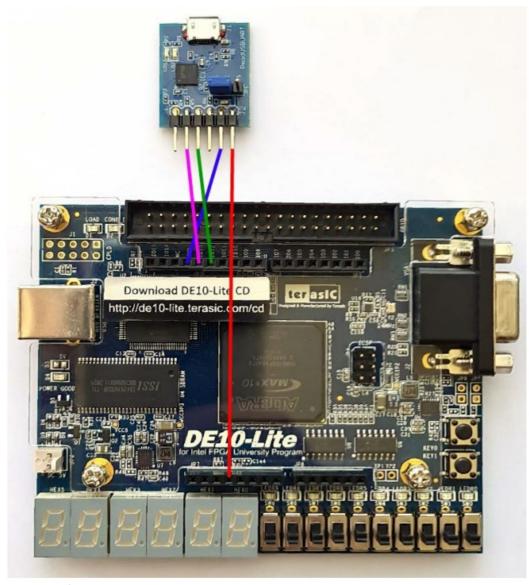

## Terasic DE10-Lite with Digilent Pmod USBUART

The loopback demo for the **DE10-Lite board** from Terasic, using Intel's MAX 10 FPGA, is in the loopback\_demo/quartus\_de10\_lite folder.

Because the DE10-Lite board doesn't have a built-in UART to USB interface, we will use Digilent's pluggable **Pmod USBUART – Digilent Reference** for that.

| DE10-Lite header pin  | Pmod USBUART pin |

|-----------------------|------------------|

| Arduino header IO13   | 2 RXD            |

| Arduino header IO12   | 3 TXD            |

| Arduino header GND    | 5 GND            |

| Arduino header VCC3P3 | 6 VCC            |

Connect the DE10-Lite and Pmod according to the pin mappings in the table above, as shown in the image below.

Open the project file in Quartus to load the design:

<zip\_content>/loopback\_demo/quartus\_de10\_lite/loopback\_demo.qpf

Click Compile Design from the sidebar

Click Program Device (Open Programmer) from the sidebar

The programming file should be selected automatically. You can find it at:

<zip\_content>/loopback\_demo/quartus\_de10\_lite/output\_files/loopback\_demo.sof

## **Testing the UART loopback**

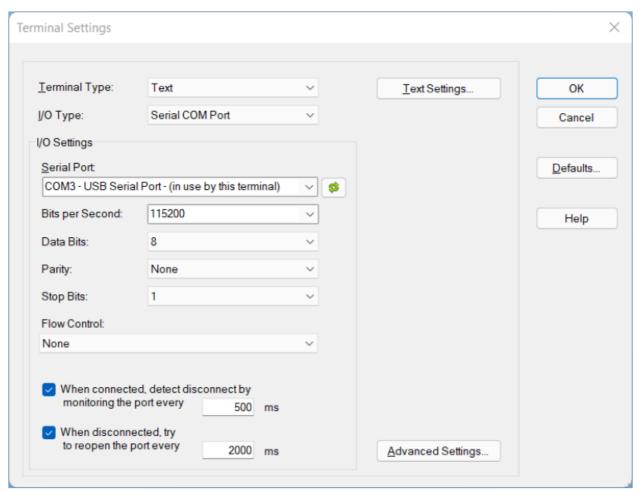

You can use any serial terminal program to communicate with the board, but I recommend **sourceforge.net/projects/y-a-terminal/** I if you don't already have one installed.

Go to Terminal→Settings and set the baud rate to 115200, data bits to 8, parity to none, and stop bits to 1, as shown in the screenshot below.

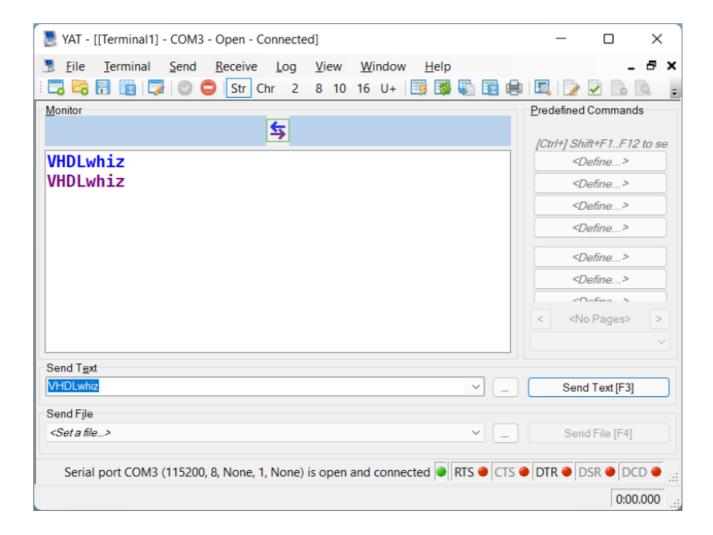

Connect the board or Pmod UART module to your computer over USB.

Finally, select Terminal→Open/Start, enter some characters in the Send Text field and hit the Send Text button. The sent text will appear in blue, and if the FPGA responds, the echoed text will appear once more below in purple color.

You can see an example of a successful test in the screenshot below.

#### **Known Issues**

The UART transmitter module does not work correctly in with the Yosys opensource synthesis suite.

The clk\_counter\_wrapped impure function in the uart\_tx.vhd file doesn't synthesize as intended in this tool.

## **Documents / Resources**

## References

- VHDLwhiz The best resource for VHDL engineers

- V VHDL module: AXI-style UART VHDLwhiz