VHDLwhiz.com

VHDLwhiz.com

ម៉ូឌុល UART រចនាប័ទ្ម AXI

សៀវភៅណែនាំអ្នកប្រើប្រាស់

ម៉ូឌុល UART រចនាប័ទ្ម AXI

| កំណែ៖ | 1.0.3 |

| កាលបរិច្ឆេទ៖ | ថ្ងៃទី 18 ខែឧសភា ឆ្នាំ 2023 |

| ផលិតផល URL: | https://vhdlwhiz.com/product/vhdl-module-axi-style-uart/ |

| អ៊ីមែលទំនាក់ទំនង៖ | jonas@vhdlwhiz.com |

ឯកសារនេះពិពណ៌នាអំពីរបៀបប្រើប្រាស់ម៉ូឌុល VHDL នៃ VHDLwhiz's general-purpose, AXI-compatible, universal asynchronous receiver-transmitter (UART) ។

អាជ្ញាប័ណ្ណ

អាជ្ញាប័ណ្ណ MIT គ្របដណ្តប់លើតម្រូវការរក្សាសិទ្ធិ និងលក្ខខណ្ឌប្រើប្រាស់របស់កូដប្រភព។

យោងទៅ LICENSE.txt file នៅក្នុង Zip file សម្រាប់ព័ត៌មានលម្អិត។

កំណត់ហេតុផ្លាស់ប្តូរ

ការផ្លាស់ប្តូរទាំងនេះសំដៅទៅលើគម្រោង files ហើយឯកសារនេះត្រូវបានធ្វើបច្ចុប្បន្នភាពទៅតាមនោះ។

| កំណែ | សុន្ទរកថា | |

| 1.0.0 | ការចេញផ្សាយដំបូង | |

| 1.0.1 | • បានបង្កើតសៀវភៅណែនាំអ្នកប្រើប្រាស់នេះ។ •បានជំនួសដំណើរការកំណត់ឡើងវិញដោយខ្លួនឯងនៅក្នុង top.vhd file ជាមួយម៉ូឌុល reset_sync.vhd ដាច់ដោយឡែក • បានបន្ថែមគម្រោងរង្វិលជុំត្រឡប់ UART សាកល្បងសម្រាប់ក្តារទាំងនេះ៖ o Xilinx Arty A7 35T (Vivado) o Xilinx arty S7 50 (Vivado) o Terasic DE10-Lite + Digilent Pmod USBUART (Quartus) |

|

| 1.0.2 | • ការផ្លាស់ប្តូរទិសដៅនៃបញ្ជរខាងក្នុង ដើម្បីធ្វើឱ្យប្រាកដថា ម៉ូឌុលក៏ដំណើរការដោយមិនមាន strobe កំណត់ឡើងវិញដំបូងឡើយ។ | |

| 1.0.3 | • ជួសជុលការគូសផែនទីទូទៅជម្រៅ TX FIFO ខុសក្នុងម៉ូឌុល uart_buffered ។ វាត្រូវបានគូសផែនទីទៅជម្រៅ RX ។ | |

ការពិពណ៌នា

គម្រោងនេះមានគោលបំណងទូទៅចំនួនបី ដែលត្រូវគ្នាជាមួយ AXI ម៉ូឌុលទទួល-បញ្ជូនអសមកាលជាសកល (UART) ។

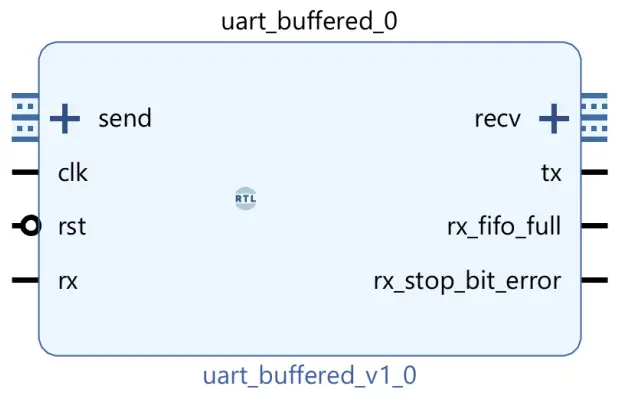

អ្នកអាចជ្រើសរើសរវាងអ្នកទទួលដាច់ដោយឡែក (uart_rx.vhd) និងអ្នកបញ្ជូន (uart_tx.vhd) ម៉ូឌុល ឬម៉ូឌុល UART រួមបញ្ចូលគ្នា (uart_buffered.vhd) ជាមួយនឹងការបញ្ចូលបញ្ចូលក្នុង និងសតិបណ្តោះអាសន្ន។  ម៉ូឌុលទាំងបីមានការគ្រប់គ្រងលំហូរដែលភ្ជាប់មកជាមួយតាមរយៈការប្រើប្រាស់សញ្ញាចាប់ដៃរួចរាល់/ត្រឹមត្រូវ។ ហើយដោយសារតែគ្រោងការណ៍ដាក់ឈ្មោះសញ្ញាត្រូវគ្នានឹងស្តង់ដារ Xilinx AXI ច្រកបញ្ជូន និង recv នឹងបង្ហាញជាចំណុចប្រទាក់ឡានក្រុងនៅក្នុងកម្មវិធីនិពន្ធ Vivado Block Design ដូចដែលបានបង្ហាញក្នុងរូបភាពខាងលើ។

ម៉ូឌុលទាំងបីមានការគ្រប់គ្រងលំហូរដែលភ្ជាប់មកជាមួយតាមរយៈការប្រើប្រាស់សញ្ញាចាប់ដៃរួចរាល់/ត្រឹមត្រូវ។ ហើយដោយសារតែគ្រោងការណ៍ដាក់ឈ្មោះសញ្ញាត្រូវគ្នានឹងស្តង់ដារ Xilinx AXI ច្រកបញ្ជូន និង recv នឹងបង្ហាញជាចំណុចប្រទាក់ឡានក្រុងនៅក្នុងកម្មវិធីនិពន្ធ Vivado Block Design ដូចដែលបានបង្ហាញក្នុងរូបភាពខាងលើ។

ប្រេកង់នាឡិកាប្រព័ន្ធ និងអត្រា baud អាចកំណត់រចនាសម្ព័ន្ធបាន។ ចំនួនប៊ីតទិន្នន័យត្រូវបានជួសជុលទៅ 8 (មួយបៃ) ប៊ីតឈប់ត្រូវបានកំណត់ទៅ 1 ហើយភាពស្មើគ្នាមិនត្រូវបានប្រើទេ។

UART RX/TX ជាមួយនឹងការទប់ស្កាត់ RAM

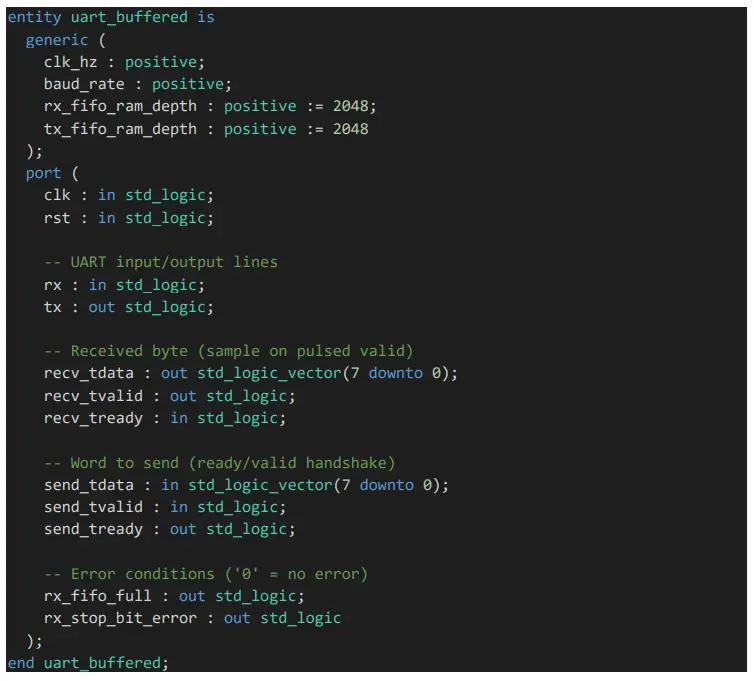

ម៉ូឌុល uart_buffered.vhd មានការគ្រប់គ្រងលំហូរដែលភ្ជាប់មកជាមួយតាមរយៈគ្រោងការណ៍ការអាន/ត្រឹមត្រូវតាមរចនាប័ទ្ម AXI នៅលើច្រកផ្ញើ និងទទួល។ ការផ្ទេរទិន្នន័យកើតឡើងតែនៅពេល _ត្រឹមត្រូវ និង _tready គឺ '1' កំឡុងពេលគែមនាឡិកាកើនឡើងដូចគ្នា។

បៃដែលផ្ទុកឡើងត្រូវបានរក្សាទុកក្នុងប្លុក RAM រហូតដល់ពួកគេត្រូវបានផ្ញើដោយម៉ូឌុលនេះ ឬអានពីវា។ ជម្រៅនៃប្លុក RAM អាចកំណត់រចនាសម្ព័ន្ធបានតាមលក្ខណៈទូទៅ ប៉ុន្តែទំហំ FIFO នឹងជាលេខដកមួយ ព្រោះ FIFO ខាងក្នុងតែងតែរក្សារន្ធដោតតែមួយដើម្បីបែងចែករវាងស្ថានភាពពេញលេញ និងទទេ។

បញ្ជីខាងក្រោមបង្ហាញពីអង្គភាពសម្រាប់ម៉ូឌុលនេះ។  UART RX

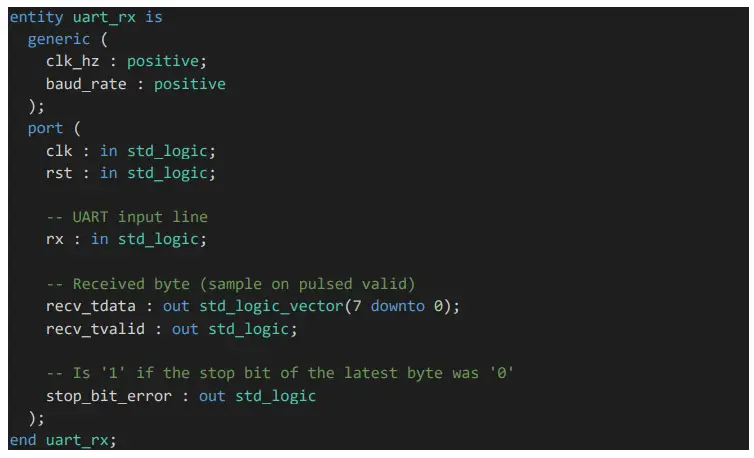

UART RX

ម៉ូឌុល uart_rx.vhd មានអ្នកទទួល UART ដែលមិនមានការរំខាន។ ទិន្នន័យដែលទទួលបានលេចឡើងនៅលើបន្ទាត់ recv_tdata ហើយមានសុពលភាពនៅពេលដែល recv_tvalid គឺ '1' ។

បញ្ជីខាងក្រោមបង្ហាញពីអង្គភាពសម្រាប់ម៉ូឌុលអ្នកទទួល។  UART TX

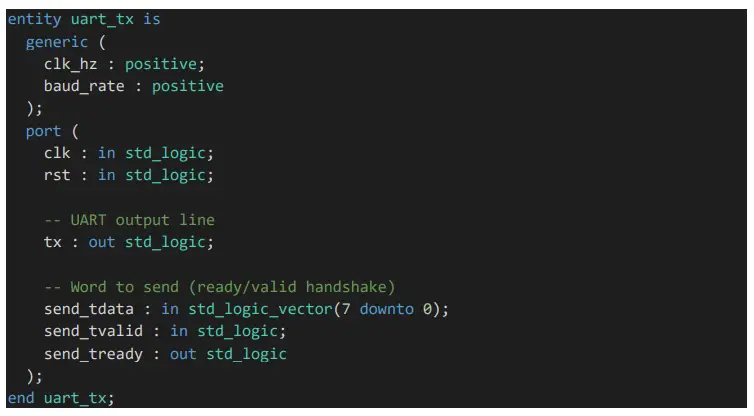

UART TX

ម៉ូឌុល uart_tx.vhd មានឧបករណ៍បញ្ជូន UART ដែលមិនមានការរំខាន។ ទិន្នន័យដែលដាក់នៅលើ send_tdata ត្រូវបានបញ្ជូននៅពេលដែល send_tvalid គឺ '1'។

បញ្ជីខាងក្រោមបង្ហាញពីអង្គភាពសម្រាប់ម៉ូឌុលបញ្ជូន។

ហ្ស៊ីប File មាតិកា

| ├── loopback_demo | គម្រោងសាកល្បង UART loopback |

| │ ├── icecube2_icestick | គម្រោង iCEcube2 សម្រាប់បន្ទះបន្ទះឈើ iCEstick |

| │ ├── quartus_de10_lite | គម្រោង Quartus សម្រាប់បន្ទះ Terasic DE10-Lite |

| │ ├── top_sim | កៅអីសាកល្បងកម្រិតកំពូលសម្រាប់គម្រោងសាកល្បង |

| │ ├── top_src | ម៉ូឌុលកម្រិតកំពូលសម្រាប់គម្រោងសាកល្បង |

| │ ├── vivado_arty_a7_35t | គម្រោង Vivado សម្រាប់បន្ទះ Xilinx Arty A7 35T |

| │ └── vivado_arty_s7_50 | គម្រោង Vivado សម្រាប់បន្ទះ Xilinx Arty S7 50 |

| ├── uart_sim | Testbench សម្រាប់ម៉ូឌុល UART |

| └── uart_src | ម៉ូឌុល UART VHDL |

ការក្លែងធ្វើការរចនា

មានតេស្តត្រួតពិនិត្យដោយខ្លួនឯងចំនួនពីរនៅក្នុង Zip fileមួយសម្រាប់ម៉ូឌុល uart_buffered និងមួយសម្រាប់ម៉ូឌុលកំពូលទូទៅដែលប្រើក្នុងគម្រោងសាកល្បង។

VHDL testbench គួរតែដំណើរការនៅក្នុងម៉ាស៊ីនក្លែងធ្វើ VHDL ដែលមានសមត្ថភាពណាមួយដែលគាំទ្រការកែប្រែ VHDL ឆ្នាំ 2008 ពេញលេញ ប៉ុន្តែស្គ្រីប run.do ដែលផ្តល់អោយដំណើរការតែនៅក្នុង ModelSim/Questa ប៉ុណ្ណោះ។

កំពុងដំណើរការ UART testbench

បើក ModelSim/Questa ហើយវាយក្នុងកុងសូលក្លែងធ្វើ៖ cd ធ្វើ uart_sim/run.do runtb

កំពុងដំណើរការបន្ទប់សាកល្បងកម្រិតកំពូល

បើក ModelSim/Questa ហើយវាយក្នុងកុងសូលក្លែងធ្វើ៖ cd ធ្វើ loopback_demo/top_sim/run.do runtb

ការអនុវត្តគម្រោងសាកល្បង

ហ្ស៊ីប file មានគម្រោងសាកល្បងសម្រាប់ក្រុមប្រឹក្សាអភិវឌ្ឍន៍ដែលបានជ្រើសរើស។

ប្រសិនបើអ្នកចង់សាកល្បងការបង្ហាញនៅលើក្តារផ្សេង អ្នកអាចបង្កើត wrapper សម្រាប់ម៉ូឌុល loopback_demo/top_src/top.vhd ។ ពិនិត្យលើ_ .vhd files និងប្ដូរតាមបំណងមួយឱ្យសមនឹងការកំណត់រចនាសម្ព័ន្ធម្ជុល និងប្រេកង់នាឡិការបស់ក្រុមប្រឹក្សាភិបាលរបស់អ្នក។

អតីតample រចនាធ្វើឱ្យម៉ូឌុល uart_buffered ភ្លាមៗ ហើយបន្ទរបៃណាមួយដែលវាទទួលបានពីលើ UART RX pin ទៅ TX pin ។

អត្រា baud ត្រូវបានកំណត់ទៅ 115200 ប៉ុន្តែអ្នកអាចផ្លាស់ប្តូរវាបានដោយការផ្លាស់ប្តូររុំខាងលើ VHDL files នៅក្នុងថតរង loopback_demo នីមួយៗ។

បន្ទះឈើ iCEstick

ថត loopback_demo/icecube2_icestick មានការអនុវត្តរង្វិលជុំសម្រាប់ latticesemi.com/icestick ក្រុមប្រឹក្សាភិបាល FPGA ។

ដើម្បីដំណើរការតាមរយៈដំណើរការអនុវត្ត សូមបើក loopback_demo/icecube2_icestick/icecube2_project/loopback_demo_sbt.project file នៅក្នុង iCEcube2 | កម្មវិធីរចនា FPGA | បន្ទះឈើ Semiconductor កម្មវិធីរចនា។

បន្ទាប់ពីផ្ទុកគម្រោងក្នុង iCEcube2 GUI សូមចុច Tools → Run All ដើម្បីបង្កើត bitmap កម្មវិធី file.

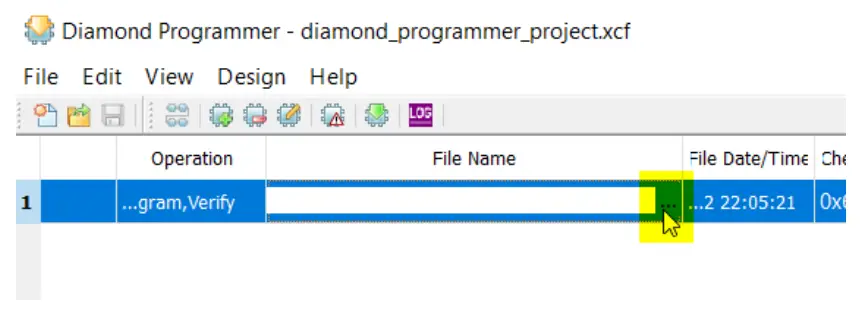

អ្នកអាចប្រើ Lattice Diamond អ្នកសរសេរកម្មវិធី និងឧបករណ៍ប្រើប្រាស់ (latticesemi.com) ឧបករណ៍ដើម្បីកំណត់រចនាសម្ព័ន្ធ FPGA ជាមួយនឹងផែនទីប៊ីតដែលបានបង្កើត file. នៅពេល Diamond Programmer បើក សូមចុច Open an programmer program ដែលមានស្រាប់ក្នុងប្រអប់ស្វាគមន៍។

ជ្រើសរើសគម្រោង file រកឃើញនៅក្នុង Zip៖

loopback_demo/icecube2_icestick/diamond_programmer_project.xcf ហើយចុច OK ។  បន្ទាប់ពីគម្រោងផ្ទុកឡើង សូមចុចចំណុចបីក្នុងប្រអប់ File ឈ្មោះជួរឈរដូចបានបង្ហាញខាងលើ។ រកមើលដើម្បីជ្រើសរើសផែនទីប៊ីត file ដែលអ្នកបានបង្កើតនៅក្នុង iCEcube2:

បន្ទាប់ពីគម្រោងផ្ទុកឡើង សូមចុចចំណុចបីក្នុងប្រអប់ File ឈ្មោះជួរឈរដូចបានបង្ហាញខាងលើ។ រកមើលដើម្បីជ្រើសរើសផែនទីប៊ីត file ដែលអ្នកបានបង្កើតនៅក្នុង iCEcube2:

loopback_demo/icecube2_icestick/icecube2_project/loopback_demo_Implmnt/sbt/outputs /bitmap/top_icestick_bitmap.bin ជាចុងក្រោយ ដោយបន្ទះ iCEstick បានដោតចូលទៅក្នុងរន្ធ USB នៅលើកុំព្យូទ័ររបស់អ្នក សូមជ្រើសរើស រចនា → កម្មវិធី ដើម្បីរៀបចំកម្មវិធី SPI flash និងកំណត់រចនាសម្ព័ន្ធ FPGA ។

ឥឡូវនេះ អ្នកអាចបន្តសាកល្បងការរចនារង្វិលជុំវិញដោយប្រើស្ថានីយសៀរៀល។

Xilinx Arty A7 35T

អ្នកអាចរកឃើញការអនុវត្តការបង្ហាញសម្រាប់ Artix-7 35T Arty FPGA ឧបករណ៍វាយតម្លៃនៅក្នុងថត loopback_demo/vivado_arty_a7_35t ។

បើក វីវ៉ាដូ - វិគីភីឌា និងរុករកទៅការដកស្រង់ fileប្រើកុងសូល Tcl ដែលរកឃើញនៅខាងក្រោមនៃចំណុចប្រទាក់ GUI ។ វាយពាក្យបញ្ជានេះដើម្បីបញ្ចូលថតគម្រោងសាកល្បង៖

ស៊ីឌី /loopback_demo/vivado_arty_a7_35t/

ប្រតិបត្តិស្គ្រីប create_vivado_proj.tcl Tcl ដើម្បីបង្កើតគម្រោង Vivado ឡើងវិញ៖

ប្រភព ./create_vivado_proj.tcl

ចុចបង្កើត Bitstream នៅក្នុងរបារចំហៀងដើម្បីដំណើរការតាមជំហានអនុវត្តទាំងអស់ និងបង្កើត bitstream កម្មវិធី file.

ជាចុងក្រោយ ចុចបើកកម្មវិធីគ្រប់គ្រងផ្នែករឹង ហើយសរសេរកម្មវិធី FPGA តាមរយៈ GUI ។

បន្តិចfile គួរតែនៅក្នុងថតឯកសារនេះ៖

<zip_content>/loopback_demo/vivado_arty_a7_35t/loopback_demo.runs/impl_1/top_arty_ a7_35t.bit

ឥឡូវនេះ អ្នកអាចបន្តសាកល្បងការរចនារង្វិលជុំវិញដោយប្រើស្ថានីយសៀរៀល។

Xilinx Arty S7 50

អ្នកអាចរកឃើញការអនុវត្តការបង្ហាញសម្រាប់ ក្រុមប្រឹក្សាអភិវឌ្ឍន៍ Spartan-7 FPGA សម្រាប់ចំណង់ចំណូលចិត្ត - Digilent Arty S7 - Xilinx បន្ទះអភិវឌ្ឍន៍នៅក្នុងថត loopback_demo/vivado_arty_s7_50 ។

បើក វីវ៉ាដូ - វិគីភីឌា និងរុករកទៅការដកស្រង់ fileប្រើកុងសូល Tcl ដែលរកឃើញនៅខាងក្រោមនៃចំណុចប្រទាក់ GUI ។ វាយពាក្យបញ្ជានេះដើម្បីបញ្ចូលថតគម្រោងសាកល្បង៖ ស៊ីឌី /loopback_demo/vivado_arty_s7_50/

ប្រតិបត្តិស្គ្រីប create_vivado_proj.tcl Tcl ដើម្បីបង្កើតគម្រោង Vivado ឡើងវិញ៖ ប្រភព ./create_vivado_proj.tcl

ចុចបង្កើត Bitstream នៅក្នុងរបារចំហៀងដើម្បីដំណើរការតាមជំហានអនុវត្តទាំងអស់ និងបង្កើត bitstream កម្មវិធី file.

ជាចុងក្រោយ ចុចបើកកម្មវិធីគ្រប់គ្រងផ្នែករឹង ហើយសរសេរកម្មវិធី FPGA តាមរយៈ GUI ។

បន្តិចfile គួរតែនៅក្នុងថតឯកសារនេះ៖ /loopback_demo/vivado_arty_s7_50/loopback_demo.runs/impl_1/top_arty_s 7_50.bit

ឥឡូវនេះ អ្នកអាចបន្តសាកល្បងការរចនារង្វិលជុំវិញដោយប្រើស្ថានីយសៀរៀល។

Terasic DE10-Lite ជាមួយ Digilent Pmod USBUART

ការបង្ហាញអំពីរង្វិលជុំសម្រាប់ បន្ទះក្តារ DE10-Lite ពី Terasic ដោយប្រើ MAX 10 FPGA របស់ Intel គឺស្ថិតនៅក្នុងថត loopback_demo/quartus_de10_lite។

ដោយសារបន្ទះ DE10-Lite មិនមានភ្ជាប់មកជាមួយ UART ទៅ USB នោះយើងនឹងប្រើឧបករណ៍ដោតរបស់ Digilent Pmod USBUART - សេចក្តីយោង Digilent សម្រាប់រឿងនោះ។

| ម្ជុលបឋមកថា DE10-Lite | ម្ជុល USBUART Pmod |

| បឋមកថា Arduino IO13 | 2 RXD |

| បឋមកថា Arduino IO12 | 3 TXD |

| ក្បាល Arduino GND | ៣ ជី |

| បឋមកថា Arduino VCC3P3 | 6 VCC |

ភ្ជាប់ DE10-Lite និង Pmod តាមការគូសវាស pin ក្នុងតារាងខាងលើ ដូចបង្ហាញក្នុងរូបភាពខាងក្រោម។  បើកគម្រោង file នៅក្នុង Quartus ដើម្បីផ្ទុកការរចនា៖ /loopback_demo/quartus_de10_lite/loopback_demo.qpf

បើកគម្រោង file នៅក្នុង Quartus ដើម្បីផ្ទុកការរចនា៖ /loopback_demo/quartus_de10_lite/loopback_demo.qpf

ចុច Compile Design ពីរបារចំហៀង

ចុចឧបករណ៍កម្មវិធី (បើកកម្មវិធីមេ) ពីរបារចំហៀង

ការសរសេរកម្មវិធី file គួរតែត្រូវបានជ្រើសរើសដោយស្វ័យប្រវត្តិ។ អ្នកអាចរកវាបាននៅ៖ /loopback_demo/quartus_de10_lite/output_files/loopback_demo.sof

ការធ្វើតេស្តរង្វិលជុំ UART

អ្នកអាចប្រើកម្មវិធីស្ថានីយសៀរៀលណាមួយ ដើម្បីទំនាក់ទំនងជាមួយក្រុមប្រឹក្សាភិបាល ប៉ុន្តែខ្ញុំសូមណែនាំ sourceforge.net/projects/ya-terminal/ l ប្រសិនបើអ្នកមិនទាន់បានដំឡើងមួយ។

ចូលទៅកាន់ស្ថានីយ → ការកំណត់ ហើយកំណត់អត្រា baud ទៅ 115200 ប៊ីតទិន្នន័យទៅ 8 ស្មើទៅនឹងគ្មាន ហើយបញ្ឈប់ប៊ីតទៅ 1 ដូចបង្ហាញក្នុងរូបថតអេក្រង់ខាងក្រោម។  ភ្ជាប់បន្ទះឬម៉ូឌុល Pmod UART ទៅកុំព្យូទ័ររបស់អ្នកតាមរយៈ USB ។

ភ្ជាប់បន្ទះឬម៉ូឌុល Pmod UART ទៅកុំព្យូទ័ររបស់អ្នកតាមរយៈ USB ។

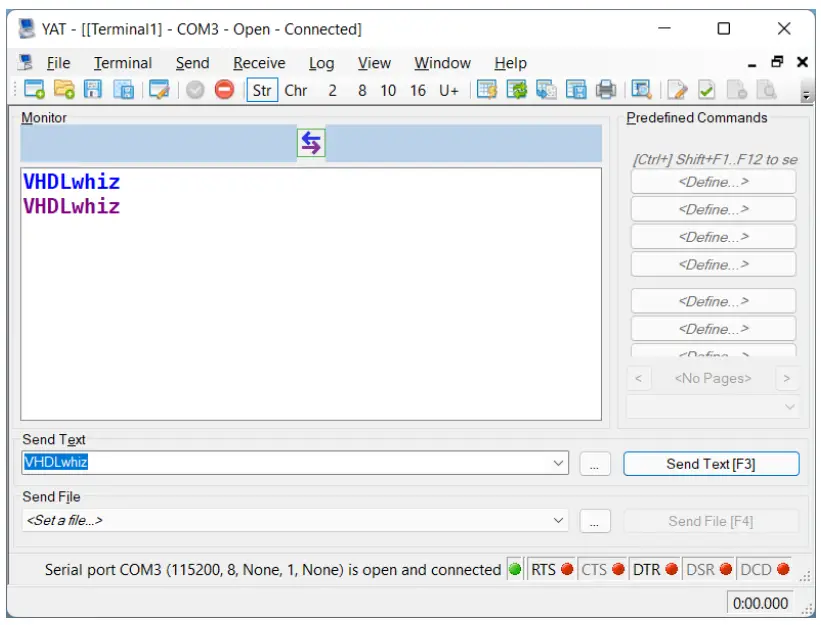

ជាចុងក្រោយ សូមជ្រើសរើស Terminal → Open/Start បញ្ចូលតួអក្សរមួយចំនួនក្នុងប្រអប់ Send Text ហើយចុចប៊ូតុង Send Text។ អត្ថបទដែលបានផ្ញើនឹងបង្ហាញជាពណ៌ខៀវ ហើយប្រសិនបើ FPGA ឆ្លើយតប នោះអត្ថបទដែលបានបន្ទរនឹងបង្ហាញម្តងទៀតខាងក្រោមជាពណ៌ស្វាយ។

អ្នកអាចឃើញអតីតample នៃការធ្វើតេស្តជោគជ័យនៅក្នុងរូបថតអេក្រង់ខាងក្រោម។

បញ្ហាដែលគេស្គាល់

ម៉ូឌុលបញ្ជូន UART មិនដំណើរការត្រឹមត្រូវជាមួយឈុតសំយោគប្រភពបើកចំហ Yosys ទេ។

មុខងារមិនបរិសុទ្ធ clk_counter_wrapped នៅក្នុង uart_tx.vhd file មិនសំយោគដូចបំណងនៅក្នុងឧបករណ៍នេះទេ។

រក្សាសិទ្ធិ VHDLwhiz.com

រក្សាសិទ្ធិ VHDLwhiz.com

ឯកសារ/ធនធាន

|

ម៉ូឌុល UART រចនាប័ទ្ម VHDLwhiz AXI [pdf] សៀវភៅណែនាំអ្នកប្រើប្រាស់ ម៉ូឌុល UART រចនាប័ទ្ម AXI, ម៉ូឌុល UART, ម៉ូឌុល |