Netlist Viewer User Guide

Netlist Viewer User Guide

Libero SoC v2024.2

Introduction (Ask a Question)

As Field Programmable Gate Array (FPGA) designs grow in size and complexity, it has become essential for FPGA designers to traverse the netlist to analyze their designs. The Microchip Netlist Viewer is a graphical representation of the design netlist that displays different views for the different stages of the design process.

Supported Families and Platforms (Ask a Question)

The Netlist Viewer supports SmartFusion ® 2, IGLOO ® 2, RTG4 ™ , PolarFire ® , and PolarFire SoC family devices and runs on Windows ® and Linux ® systems.

![]() Important: Depending on the device selected, some user interface elements such as icons, options, tabs, and dialog boxes may vary slightly in appearance and/or content. Basic Netlist Viewer functionality remains the same, regardless of the device chosen. In this user guide, a PolarFire device is used in the example figures.

Important: Depending on the device selected, some user interface elements such as icons, options, tabs, and dialog boxes may vary slightly in appearance and/or content. Basic Netlist Viewer functionality remains the same, regardless of the device chosen. In this user guide, a PolarFire device is used in the example figures.

Views (Ask a Question)

The Netlist Viewer is a Graphical User Interface (GUI) that displays different views for the different stages of the design process:

- Register Transfer Level (RTL) Netlist view—shows how the Verilog code appears in design format.

Using this view, you can confirm whether software implemented the correct logic. Cross probing between this view and the HDL code aids in troubleshooting when the design does not work as desired. - Hierarchical Post-Synthesis view—hierarchical view of the netlist after synthesis and after technology mapping to the Microchip FPGA technology.

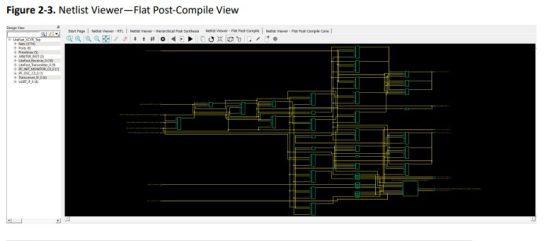

- Flat Post-Compile Netlist view—a flattened netlist after synthesis, technology mapping and further optimization based on the Design Rules Check (DRC) rules of the device family and/or die.

- Flat Post-Compile Cone view—loads the same netlist as the Flat Post-Compile view, but does not initially draw anything on the canvas. Important parts of the design can be added to the canvas from the tree or from the existing items in the view. This view opens much more quickly than the Flat Post-Compile view. It allows you to load only the parts of the design you are interested in. This view is well-suited for use with large designs. This view is not available for all families.

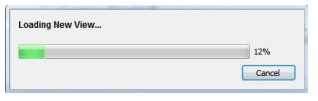

Important: A progress bar indicates that the flattened netlist is being loaded. For a large netlist, the loading may incur some runtime penalty. A Cancel button is available to cancel the loading.

Important: A progress bar indicates that the flattened netlist is being loaded. For a large netlist, the loading may incur some runtime penalty. A Cancel button is available to cancel the loading. Invocation (Ask a Question)

Invocation (Ask a Question)

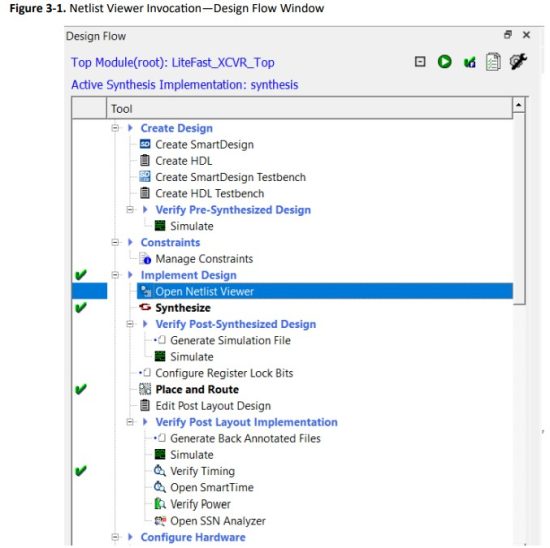

The standalone Netlist Viewer is available for invocation in the Design Flow window. To open the standalone Netlist Viewer in the Flow window, perform one of the following steps:

- Double click Netlist Viewer in the Design Flow window

- Right click Netlist Viewer and select Open Interactively

When Netlist Viewer opens, it makes available for loading and viewing the following views of the netlist:

When Netlist Viewer opens, it makes available for loading and viewing the following views of the netlist:

- RTL—available after design capture/design generation

- Hierarchical Post-Synthesis—available after Synthesis

- Flat Post-Compile—available after Synthesis or Place and Route. If after Place and Route, the Netlist Viewer loads the Flat Post-Compile view to reflect the netlist generated after Place and Route.

- Flat Post-Compile Cone—available after Synthesis or Place and Route. If after Place and Route, the Netlist Viewer loads the Flat Post-Compile view to reflect the netlist generated after Place and

Route. This view does not display any netlist on the canvas until an instance from the design tree is selected and loaded. This view allows you to load in a special area of the design in which you are interested. It also cuts down the runtime.

Netlist Viewer Windows (Ask a Question)

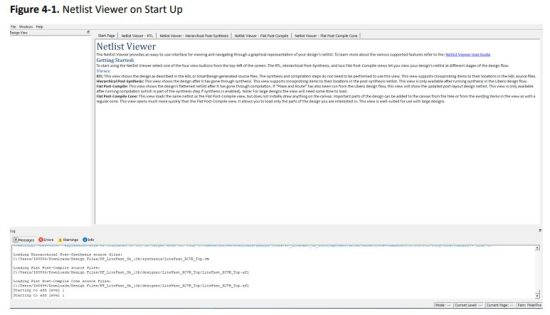

When the standalone Netlist Viewer opens, no netlist views are loaded. The Start Page shows the netlist views that can be opened for viewing.

The Netlist Viewer User Guide is available from the Design Flow window (Netlist Viewer > Help > Netlist Viewer User Guide) and also from the Help menu (Help > Reference Manuals).

4.1 Opening a View (Ask a Question)

Click any of the following views at the top-left corner to load the netlist into the Netlist Viewer for viewing:

- RTL view—pre-synthesis RTL netlist is drawn in the view

- Hierarchical Post-Synthesis view—post-synthesis netlist is drawn in the view

Note: The Hierarchical Post-Synthesis view is not available if synthesis is disabled in the design flow (Project > Project Settings > Design Flow > Enable Synthesis is unchecked). - Flat Post-Compile view—flattened post-compile netlist is drawn in the view

- Flat Post-Compile Cone view—no netlist is drawn until design objects are added to the view

Important:

Important:

- When you open netlist views for the first time in the Netlist Viewer, they load into system memory, where they remain until the Netlist Viewer exits. For very large designs, loading the netlist for the first time may take some time. A pop-up window reports the status of the loading process.

- The Flat Post-Compile Cone view takes very little runtime because no netlist is drawn when this view is first loaded. This view does not display a netlist until instances from the design tree are selected and loaded.

Figure 4-2. Loading New View Popup Window After the netlist views open for the first time, they load into system memory, making them available almost immediately in the Netlist Viewer.

After the netlist views open for the first time, they load into system memory, making them available almost immediately in the Netlist Viewer.

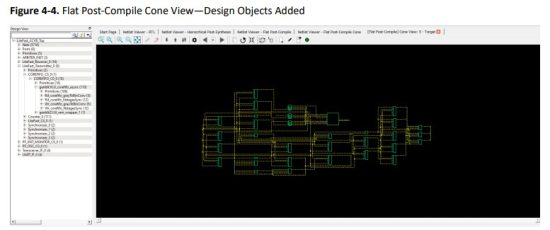

4.1.1 Displaying the Flat Post-Compile Cone View (Ask a Question)

When the Flat Post-Compile Cone view has finished loading, unlike the other three views, nothing is drawn in the canvas. This view is useful when a small or critical part of a very large design needs to be examined. Design objects that can be selected for display in this view include:

This view is useful when a small or critical part of a very large design needs to be examined. Design objects that can be selected for display in this view include:

- Nets

- Ports

- Macros

- Components

To display design objects in the Flat Post-Compiled Cone view, right click the design object (Nets, Macro, Ports, or Component) in the Design Tree and select Load Selection. The design object is added to the view.

Opening a design in the Flat Post-Compile view may incur a runtime penalty. This cone view loads the same AFL netlist source file as the Flat Post-Compile view. However, this cone view, unlike the Flat Post-Compile view, draws nothing until you select a part of the design you want to display. This reduces the runtime penalty associated with drawing a large netlist for display. 4.1.1.1 Adding a Net (Ask a Question)

4.1.1.1 Adding a Net (Ask a Question)

Right click a net in the Design Tree and select Load Selection to add a net to the view. Adding a net to the view adds a solid line net to the view (unless you cancel early), including all the instances and ports the net is connected to. The added net is selected in the view.

Nets that span multiple pages can be followed through the right click menu item Follow Net to Page# to go to different pages that the net is on. 4.1.1.2 Adding a Macro (Ask a Question)

4.1.1.2 Adding a Macro (Ask a Question)

A macro is a basic low-level design object from the Macro Library in the Catalog. Right click a macro in the Design Tree and select Load Selection to add a macro. Adding a macro adds the instance with its connected nets to the view. The connected nets are always dashed yellow lines, even if they are not connected to any logic outside the view. Double clicking the net adds connections (if any) and turns the net from a dashed line to a solid line. A solid line for a net indicates that it is a user-added net. 4.1.1.3 Adding a Port (Ask a Question)

4.1.1.3 Adding a Port (Ask a Question)

To add a port to the view, right click a port in the Design Tree and select Load Selection. Adding a port to the view is the same as adding a net connected to the port.

4.1.1.4 Adding a Component (Ask a Question)

Right click a component in the Design Tree and select Load Selection to add a component to the view. Adding a component to the view is the same as selecting all lower level macros and adding them to the view. The added macros are selected.

Important: To save runtime for very large components with many low level macros, the macros are added, but cannot be selected.

4.1.1.5 Load/Driver Display (Ask a Question)

Design objects can also be added to the view through the right click menu to add load/driver. This action adds any instances at the different logical levels.

4.2 Closing a View (Ask a Question)

To close the opened view, click an opened view at the top of the Netlist Viewer. A closed view stays in system memory as long as the Netlist Viewer remains open. Opening the same netlist view at a later time does not incur runtime penalty, as no loading is required.

4.3 Netlist Viewer Windows (Ask a Question)

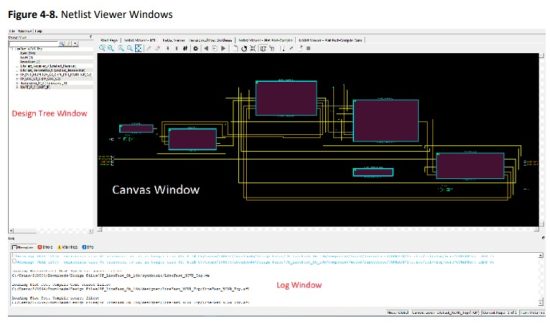

When the Netlist Viewer opens, it displays three windows by default.

- Design Tree window displays the design hierarchy from the top level.

- Canvas window displays the netlist views.

- Log window displays messages, warnings, info, and so on.

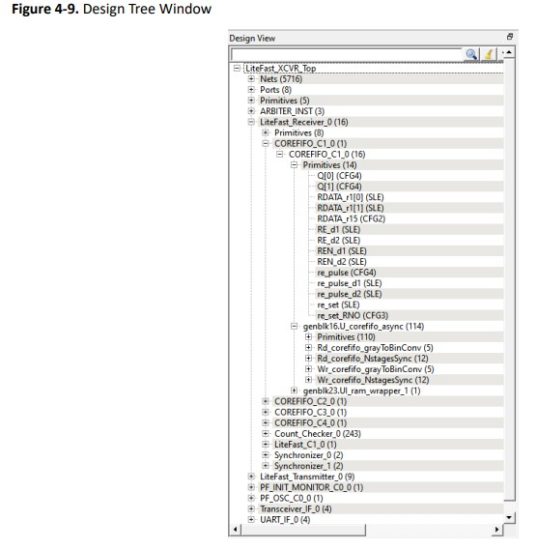

4.4 Design Tree Window (Ask a Question)

4.4 Design Tree Window (Ask a Question)

The Design Tree window displays the design hierarchy from the top level. By default, when the Netlist Viewer opens, it displays the Design Tree window.

Important: The Design Tree window is displayed by default when the Netlist Viewer opens. Hiding the Design Tree view will leave more display area for the Canvas view. To get a bigger display area for the canvas view, hide the Design Tree window (Netlist Viewer > Windows and uncheck Show Tree)

The Design Tree window displays:

- Nets (<integer>)—number in brackets is the total number of nets at the top level

- Ports (<integer>)—number in brackets is the total number of ports at the top level

- Design components under the top level—each component can be collapsed or expanded to expose

– Nets—total number of nets at the component level

– Ports—total number of ports at the component level

– Subcomponents inside the component - Fanout Values (Nets)—when two numbers are displayed in the bracket, the first number is the fanout of the net at the local level (of hierarchy) and the second number is the fanout of the net at the global level. As an example, net_xyz (fanout: 1,3) means the net goes down the levels of hierarchy to three different pins (global fanout 3) and is not connected to any other pins at the current level (local fanout 1).

- Primitives—primitives refer to macros and low-level design objects and can appear in the top level or component level.

The design tree is different with different netlist views. For the Flat Post-Compile view, the design tree displays a much larger number of nets than the RTL view or Hierarchical Post-Synthesis view, because the netlist is flattened in the Post-Compile view and all nets are counted. The nets in the Flat Post-Compile view, unlike the RTL view or the Hierarchical Post-Synthesis view, shows only one value for fanout (global fanout) because it is a flattened view (no hierarchy).

For nets that are part of a NetBundle, the NetBundle name is followed by a number in parentheses that indicates the total number of nets in the NetBundle. 4.4.1 Filter (Ask a Question)

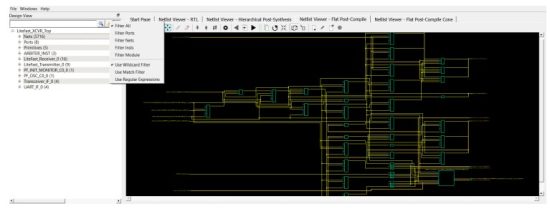

4.4.1 Filter (Ask a Question)

The display of design objects in this view can be filtered based on:

- Ports—displays all ports only, including component level ports.

- Nets—displays all nets only, including component level nets.

- nstances—displays all instances only, including component level instances.

- Modules—displays all modules only.

- Filter All—displays all design objects only.

- Use Wildcard Filter

- Use Match Filter

- Use Regular Expressions

Click the Filter button at the top-right corner of the Design view to filter design objects.

4.4.2 Interoperability Between Windows and Views (Ask a Question)

4.4.2 Interoperability Between Windows and Views (Ask a Question)

When a design object such as a net, an instance or a port is selected in the Design Tree window, the object is selected in the different netlist views. The reverse is also true. An object selected in one netlist view window is also selected in the Design Tree window and other netlist views.

Interoperability works only when the Toggle Cross-probing icon is enabled.

4.5 Canvas Window (Ask a Question)

The Canvas Window displays the:

- RTL view

- Hierarchical Post-Synthesis view

- Flat Post-Compile view

- Flat Post-Compile Cone view

- Cones view

- Opened HDL files (not available in the Flat Post-Compile view)

- Start Page—when no netlist views are opened

When a view is opened, a view tab is added across the top of the Canvas window for ease of switching between views.

![]() Important: To get a larger display area for the Canvas view, hide the Design

Important: To get a larger display area for the Canvas view, hide the Design

Tree Window (Netlist Viewer > Windows > Uncheck Show Tree) and hide the Log window (Netlist Viewer > Windows > Uncheck > Show Log) Hiding the Log window and the Design Tree window leaves more display area for the Canvas window. Alternatively, press CTRL+W to maximize the work area. Icons in the Canvas window allow you to:

Icons in the Canvas window allow you to:

- Traverse vertically up (Pop) or down (Push) the design hierarchy

- Navigate horizontally across different pages of the design view

- Zoom in/out of the design view

- Trace critical nets to the driver/load

- Create logical cones for debugging

- Control the color display the design objects

4.6 Log Window (Ask a Question)

4.6 Log Window (Ask a Question)

The Log window displays the following:

- Informational messages such as the location and name of the files used to display the view.

- Any syntax errors in the HDL file if the HDL file is opened with the Open File Location option (right click design object > Open File Location).

Important: The Log window displays by default when the Netlist Viewer opens.

Hiding the Log window will leave more display area for the Canvas view. To get a larger display area for the Canvas view, hide the Log window (Netlist Viewer > Windows and uncheck (Show Log).

4.6.1 Status Bar (Ask a Question)

The status bar at the bottom-right corner of the Netlist Viewer displays the following:

- Mode—displays Global or Local mode. Global mode means the Netlist Viewer can cross hierarchical boundaries when following nets to drivers or loads. Local means the Netlist Viewer tays in the current level of design hierarchy.

- Current Level—displays the current level of design hierarchy, either TOP_LEVEL instance name or instance name of the component

- Current Page—displays the current page of the Netlist Viewer (Page x of <total>) when traversing across different pages of the Netlist Viewer

- Fam—displays the technology family

Revision History (Ask a Question)

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the most current publication.

| Revision | Date | Description |

| M | 08/2024 | This document is released with Libero SoC Design Suite v2024.2 without changes from v2024.1. |

| L | 08/2023 | Editorial updates only. No technical content updates. |

| K | 08/2023 | Editorial updates only. No technical content updates. |

| J | 05/2023 | Updated the document with the latest and better quality graphics. |

| H | 04/2023 | This document is released with Libero SoC Design Suite v2023.1 without changes from v2022.3. |

| G | 12/2022 | This document is released with Libero SoC Design Suite v2022.3 without changes from v2022.2. |

| F | 08/2022 | This document is released with Libero SoC Design Suite v2022.2 without changes from v2022.1. |

| E | 04/2022 | This document is released with Libero SoC Design Suite v2022.1 without changes from v2021.3. |

| D | 12/2021 | • In section 1. Supported Families and Platforms, added PolarFire SoC to the list of supported devices. • Updated the document with better quality graphics. |

| C | 08/2021 | This document is released with Libero SoC Design Suite v2021.2 without changes from v2021.1. |

| B | 04/2021 | Editorial updates only. No technical content updates. |

| A | 11/2020 | Document converted to Microchip template. |

| 4.0 | 12/2018 | Document template updates and minor text edits |

| 3.0 | 10/2017 | Added Flat Post-Compile Cone View |

| 2.0 | 05/2017 | Minor updates |

| 1.0 | 12/2016 | Initial Revision |

Microchip FPGA Support

Microchip FPGA products group backs its products with various support services, including Customer Service, Customer Technical Support Center, a website, and worldwide sales offices.

Customers are suggested to visit Microchip online resources prior to contacting support as it is very likely that their queries have been already answered.

Contact Technical Support Center through the website at www.microchip.com/support. Mention the FPGA Device Part number, select appropriate case category, and upload design files while creating a technical support case.

Contact Customer Service for non-technical product support, such as product pricing, product upgrades, update information, order status, and authorization.

- From North America, call 800.262.1060

- From the rest of the world, call 650.318.4460

- Fax, from anywhere in the world, 650.318.8044

Microchip Information

The Microchip Website

Microchip provides online support via our website at www.microchip.com/. This website is used to make files and information easily available to customers. Some of the content available includes:

- Product Support – Data sheets and errata, application notes and sample programs, design resources, user’s guides and hardware support documents, latest software releases and archived software

- General Technical Support – Frequently Asked Questions (FAQs), technical support requests, online discussion groups, Microchip design partner program member listing

- Business of Microchip – Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

Product Change Notification Service

Microchip’s product change notification service helps keep customers current on Microchip products. Subscribers will receive email notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, go to www.microchip.com/pcn and follow the registration instructions.

Customer Support

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Embedded Solutions Engineer (ESE)

- Technical Support

Customers should contact their distributor, representative or ESE for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in this document. Technical support is available through the website at: www.microchip.com/support

Microchip Devices Code Protection Feature

Note the following details of the code protection feature on Microchip products:

- Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner, within operating specifications, and under normal conditions.

- Microchip values and aggressively protects its intellectual property rights. Attempts to breach the code protection features of Microchip product is strictly prohibited and may violate the Digital Millennium Copyright Act.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code protection does not mean that we are guaranteeing the product is “unbreakable”. Code protection is constantly evolving. Microchip is committed to continuously improving the code protection features of our products.

Legal Notice

This publication and the information herein may be used only with Microchip products, including to design, test, and integrate Microchip products with your application. Use of this information in any other manner violates these terms. Information regarding device applications is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. Contact your local Microchip sales office for additional support or, obtain additional support at www.microchip.com/en-us/support/design-help/client-support-services.

THIS INFORMATION IS PROVIDED BY MICROCHIP “AS IS”. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE, OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDIRECT, SPECIAL, PUNITIVE, INCIDENTAL, OR CONSEQUENTIAL LOSS, DAMAGE, COST, OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP’S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION.

Use of Microchip devices in life support and/or safety applications is entirely at the buyer’s risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

Trademarks

The Microchip name and logo, the Microchip logo, Adaptec, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, CryptoMemory, CryptoRF, dsPIC, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AgileSwitch, ClockWorks, The Embedded Control Solutions Company, EtherSynch, Flashtec, Hyper Speed Control, HyperLight Load, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, TimeCesium, TimeHub, TimePictra, TimeProvider, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, Augmented Switching, BlueSky, BodyCom, Clockstudio, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, Espresso T1S, EtherGREEN, EyeOpen, GridTime, IdealBridge, IGaT, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, IntelliMOS, Inter-Chip Connectivity, JitterBlocker, Knob-on-Display, MarginLink, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mSiC, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, Power MOS IV, Power MOS 7, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SmartHLS, SMART-I.S., storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, Trusted Time, TSHARC, Turing, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

2024, Microchip Technology Incorporated and its subsidiaries. All Rights Reserved.

ISBN: 978-1-6683-4746-1 ©

Quality Management System

For information regarding Microchip’s Quality Management Systems, please visit www.microchip.com/quality.

Worldwide Sales and Service

| AMERICAS | ASIA/PACIFIC | ASIA/PACIFIC | EUROPE |

| Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: www.microchip.com/support Web Address: www.microchip.com Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455 Austin, TX Tel: 512-257-3370 Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088 Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075 Dallas Addison, TX Tel: 972-818-7423 Fax: 972-818-2924 Detroit Novi, MI Tel: 248-848-4000 Houston, TX Tel: 281-894-5983 Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380 Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800 Raleigh, NC Tel: 919-844-7510 New York, NY Tel: 631-435-6000 San Jose, CA Tel: 408-735-9110 Tel: 408-436-4270 Canada – Toronto Tel: 905-695-1980 Fax: 905-695-2078 |

Australia – Sydney Tel: 61-2-9868-6733 China – Beijing Tel: 86-10-8569-7000 China – Chengdu Tel: 86-28-8665-5511 China – Chongqing Tel: 86-23-8980-9588 China – Dongguan Tel: 86-769-8702-9880 China – Guangzhou Tel: 86-20-8755-8029 China – Hangzhou Tel: 86-571-8792-8115 China – Hong Kong SAR Tel: 852-2943-5100 China – Nanjing Tel: 86-25-8473-2460 China – Qingdao Tel: 86-532-8502-7355 China – Shanghai Tel: 86-21-3326-8000 China – Shenyang Tel: 86-24-2334-2829 China – Shenzhen Tel: 86-755-8864-2200 China – Suzhou Tel: 86-186-6233-1526 China – Wuhan Tel: 86-27-5980-5300 China – Xian Tel: 86-29-8833-7252 China – Xiamen Tel: 86-592-2388138 China – Zhuhai Tel: 86-756-3210040 |

India – Bangalore Tel: 91-80-3090-4444 India – New Delhi Tel: 91-11-4160-8631 India – Pune Tel: 91-20-4121-0141 Japan – Osaka Tel: 81-6-6152-7160 Japan – Tokyo Tel: 81-3-6880- 3770 Korea – Daegu Tel: 82-53-744-4301 Korea – Seoul Tel: 82-2-554-7200 Malaysia – Kuala Lumpur Tel: 60-3-7651-7906 Malaysia – Penang Tel: 60-4-227-8870 Philippines – Manila Tel: 63-2-634-9065 Singapore Tel: 65-6334-8870 Taiwan – Hsin Chu Tel: 886-3-577-8366 Taiwan – Kaohsiung Tel: 886-7-213-7830 Taiwan – Taipei Tel: 886-2-2508-8600 Thailand – Bangkok Tel: 66-2-694-1351 Vietnam – Ho Chi Minh Tel: 84-28-5448-2100 |

Austria – Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark – Copenhagen Tel: 45-4485-5910 Fax: 45-4485-2829 Finland – Espoo Tel: 358-9-4520-820 France – Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79 Germany – Garching Tel: 49-8931-9700 Germany – Haan Tel: 49-2129-3766400 Germany – Heilbronn Tel: 49-7131-72400 Germany – Karlsruhe Tel: 49-721-625370 Germany – Munich Tel: 49-89-627-144-0 Fax: 49-89-627-144-44 Germany – Rosenheim Tel: 49-8031-354-560 Israel – Ra’anana Tel: 972-9-744-7705 Italy – Milan Tel: 39-0331-742611 Fax: 39-0331-466781 Italy – Padova Tel: 39-049-7625286 Netherlands – Drunen Tel: 31-416-690399 Fax: 31-416-690340 Norway – Trondheim Tel: 47-72884388 Poland – Warsaw Tel: 48-22-3325737 Romania – Bucharest Tel: 40-21-407-87-50 Spain – Madrid Tel: 34-91-708-08-90 Fax: 34-91-708-08-91 Sweden – Gothenberg Tel: 46-31-704-60-40 Sweden – Stockholm Tel: 46-8-5090-4654 UK – Wokingham Tel: 44-118-921-5800 Fax: 44-118-921-5820 |

Documents / Resources

|

MICROCHIP v2024.2 Libero SoC Design Suite [pdf] User Guide v2024.2, 12.0, v2024.2 Libero SoC Design Suite, v2024.2, Libero SoC Design Suite, SoC Design Suite, Design Suite, Suite |