CAPITOLU 1 INTRODUZIONE

SISTEMA OVERVIEW

U S4967 Rev: 2B.31 486 Scheda di sistema Cache Hè 2/3 Baby AT-sized, cumplettamente PC / AT compatible è offre prestazioni è caratteristiche eccezziunale.

Cù 128K / 256K / 512K / 1M memoria cache à bordu, sta scheda di sistema hè veramente una macchina à alta velocità chì hè bè adattata per a custruzzione di computer persunali avanzati o stazioni di travagliu.

U $ 4967 Rev: 2B.31 486 Cache sistema di scheda hè cuncepitu cù u chipset SIS 85C496 / 85C497 chì sò assai integrati. Cù stu chipset, ci sò solu uni pochi discreti

dispusitivi nicissarii, chì permette à 4 banche di memoria per esse piazzatu nantu à u bordu. A dimensione di a memoria pò esse scalata da 1 MB à 255 MB.

CARATTERISTICHE

U $ 4967 Rev: 2B.31 486 Cache sistema di scheda supporta (o include) e seguenti caratteristiche:

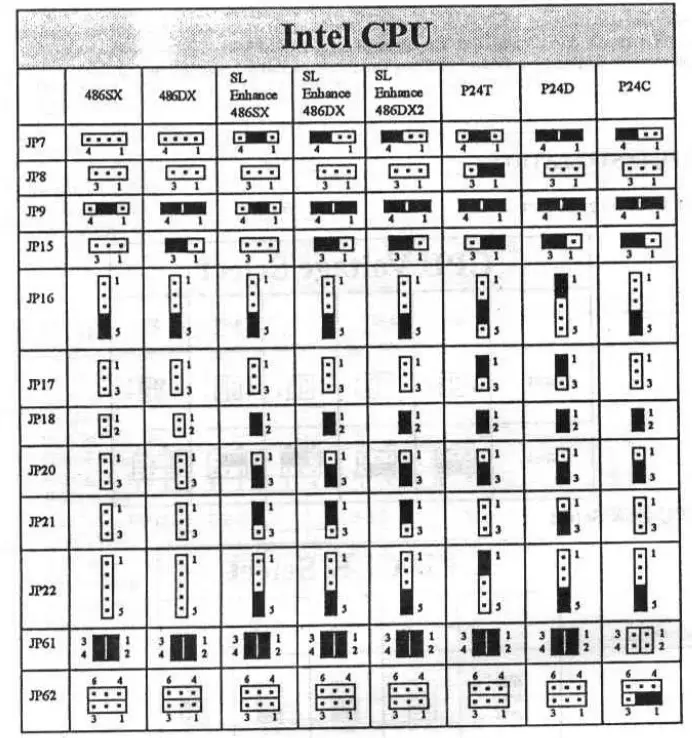

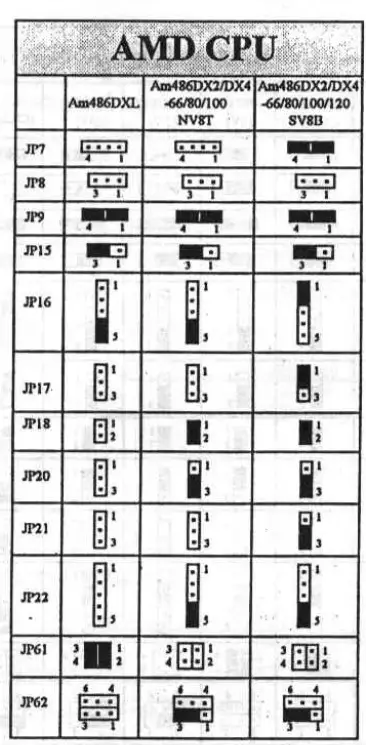

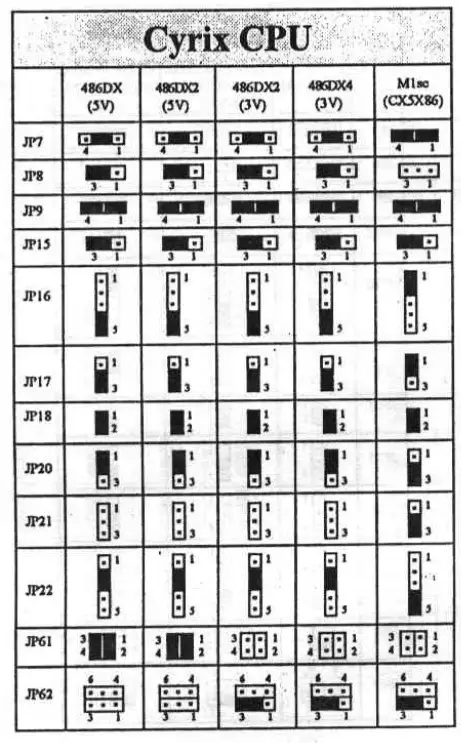

* Supportu

Intel 486SX/SX2/DX/DX2,DX4(3.45V),P24D,P24T AMD DX,DX2/DX4(NV8T),OX2/DX4(SVEB) Cyrix SX/DX/DX2,DX2-V66/VB0(3.45V),DX4(3.45V), 15×86 (3.45V) in 25/33/40/SOMHZ

- Cuncepitu cù chipset SIS 85C496/85C497

- Supportu 128K/256K/512K/1M 2nd Live Cache

- Supporta 4 Banchi DRAM. A DRAM pò esse bul cù altri SIMMs Single-Sided o Double Sided. A memoria massima hè di 255 MB

- RAM ombra cuntrullata da u software per u BIOS di sistema è / o video

- Trè slot di bus locale PCI 32-bit, quattru slot di espansione 16-bk

CAPITOLU 2 SYSTEM BOARD LAYOUT

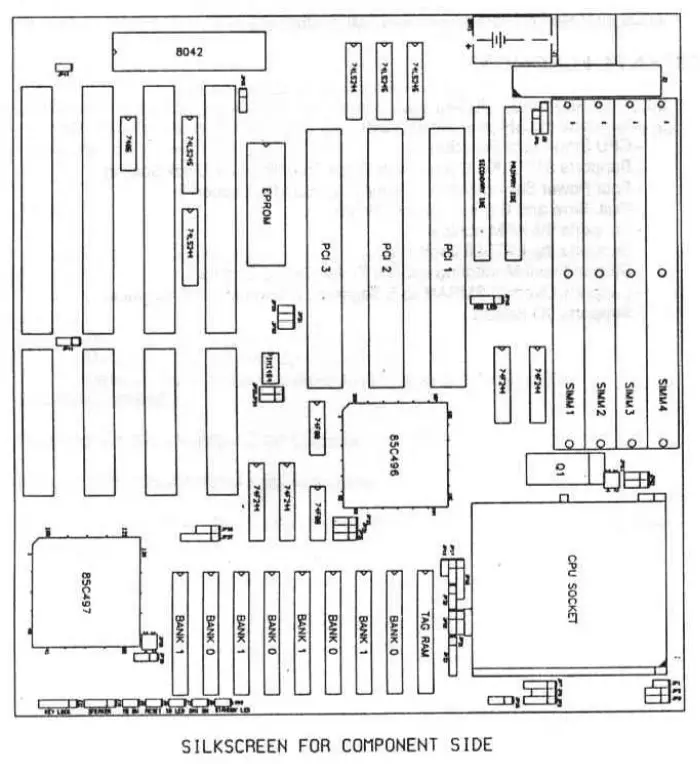

Piazzamentu di u S486 Rev: 2B.31

CAPITOLU 3 CONFIGURAZIONE HARDWARE

Prima chì u sistema hè prontu à operà, u hardware deve esse cunfiguratu per permette diverse funzioni in u sistema. Per cunfigurà u sistema di Cache $ 4967 Rev: 2B.31

bordu hè un compitu sèmplice, solu uni pochi Jumpers, connectors, e sockets ci vole à esse sceltu.

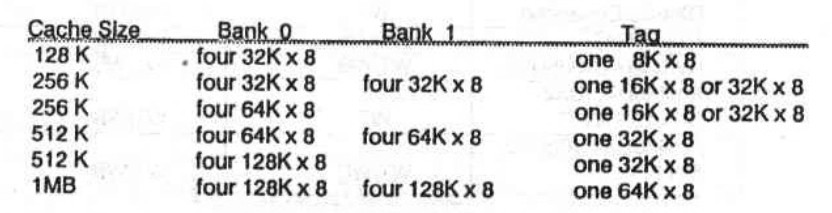

CACIIE SOCKETS DI MEMORIA

U $ 4967 Rev: 2B.31 Cache system board supporta 2 banche di SRAM chì furnisce sia 126/256K/512K/1MB di memoria cache. A tavula seguente lista i dettagli

infurmazione.

L'identificazione di u bancu à a parte currispondente sò i seguenti:

L'identificazione di u bancu à a parte currispondente sò i seguenti:

Banca 0 - U9, U11, U19, U24

Banca 1 - U10, U14, U20, U2

Tag =~ U8 -

| Dimensione cache | Dimensione DRAM cacheable (8 bit tag) |

Dimensione DRAM cacheable (7 bit tag) |

| - 64K byte | 16fvW fe 32M-byte 64M byte |

8 M byte |

| - 128K byte | t6M byte 32 M byte |

|

| 256K byte | ||

| 512 Kb_yte | 128 M byte | 64 M byte |

| 1 M byte | 255 M byte | 128 M byte |

Tabella 3-2 Opzioni di dimensione di cache

| Tipu di processore | Ll Modu Cache | Modu cache L2 |

| 4 86SX/DX/DX2/DX4/SL-Enhanced | WT | WT/WB WTNV B |

| P24D/P24T | WT/WB | |

| Cyrix M7/DX4/M1sc | WT/WB | WT/WB |

| Am486DXL/DX2 DX4-100 NV8T | WE | WT/WB |

| Arn486Dr47100/120 SV8B | WI/WS | WT/WB |

Table 3-3 Lt/L2 Cache Configurations

| Definizione di u ciclu Hiiinii-emory | Total Clocks à l'Interfaccia Host | S0MHz | ||

| 251 V 1 Hz | 33 MHz | 40 MHz | ||

| Lettura singola (L2 Cache Hit) | 2 | 2 | 2 | 2 |

| —-S ri-i-gle-Reacf (12 cache Miss) | 3 | 4 | 5 | 6 |

| -Teurst-Read (L2 Cache Hit) | 2-1-1-1 | 2-1-1-1 | 3-2-2-2 | 3-2-2-2 |

| urst-Lettura (L2 Cache Miss) |

3-2-2-2 | 4-3-3-3 | 5-4-4-4 | 6-5-5-5 |

| -Scrittura unica (L2 Cache Hit) | 2 | 2/VVB,3/WT | 3/W6,4/WT | 3/VVB,5NVI |

| Single-Scrittura (L2 Cache Miss) |

2 2-1-1-1/WB 3-2-2-2/WT 3-2-2-2 |

3 2-1-1-1/WB 3-2-2-2/WT 3-2-2-2 |

4 3-2-2-2/WB 4-3-3-3/WT |

5 3-2-2-2/WB 5-4-4-4/WT |

| * Burst-Write (U Cache Hit) | ||||

| Burst-Scrittura (U Cache Miss) |

4-3-3-3 | 5-4-4-4 | ||

Tabella 3-4 Opzioni di prestazione U Cache/DRAM

OMBRA CACHEABLE

UMB (Upper Memory Block) chì ùn hè micca l'area di memoria principale Hè per difettu micca cacheable. Tuttavia, una volta ombreggiati, i segmenti di RAM 0C0000-OFFFFFh ponu esse più cache in cache di Livellu 2 è Livellu 1. Ogni segmentu di memoria di 32K pò esse attivatu individualmente per esse cacheable sia da a cache di livellu secundariu di 85C495 sia da a cache interna di CPU.SIMM SOCKETS

je $ 4967 Rev: 2B.31 A scheda di sistema di cache sustene 4 banche DRAM, Bank 0 è Bank 1 k 2 è Bank 3 in sockets SIMM utilizanu SIMM 72-pin : u tipu DRAM pò esse 256K, 512K, , 2M, 4M, o 16M da 32/36 bits Single side o Double side Modu di pagina veloce è più veloce in BON.

L'usu di moduli DRAM 256K, 512K, 1M, 2M, 4M o 16M, 1M è finu à 255 M di memoria pò esse ottenutu. L'installazione di DRAM SIMM hè "Table-free", chì

i SIMMs esse stallati in ogni locu siot è ogni cumminazzioni.

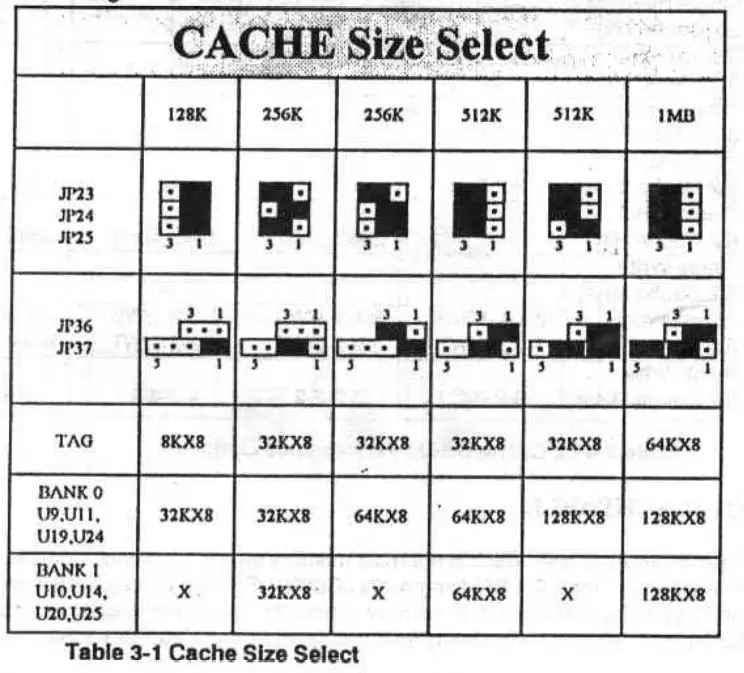

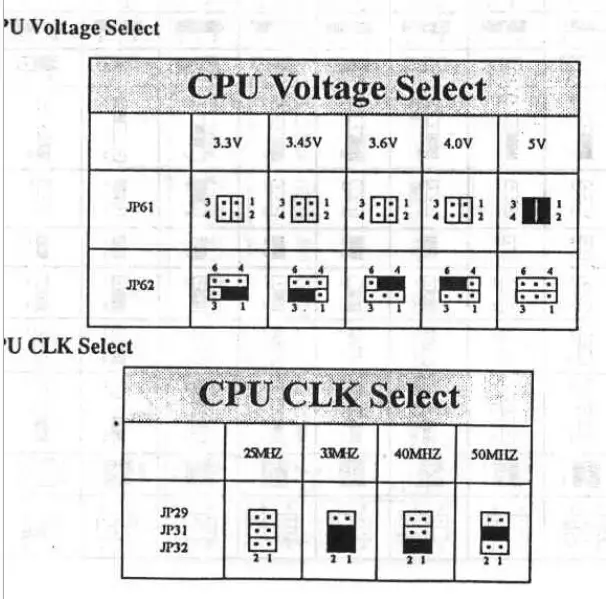

INSTALLAZIONE PU:

Selezzione di u tipu di CPU

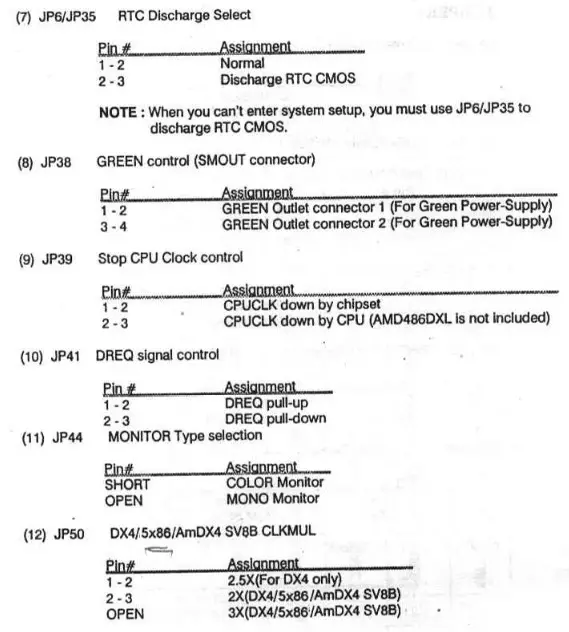

JUMPER:

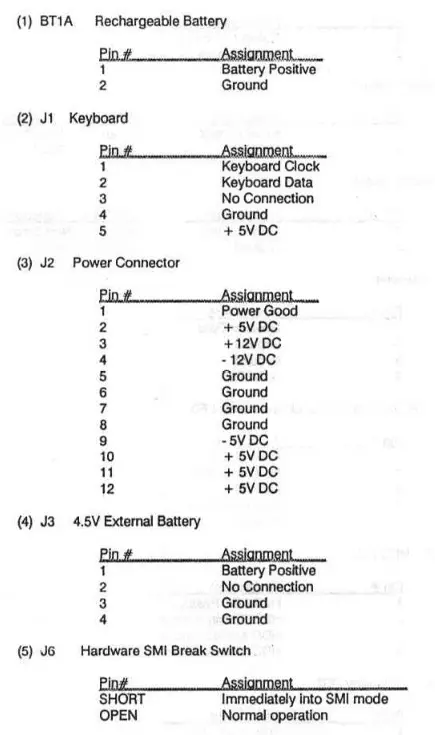

CONNETTORI:

Documenti / Risorse

|

u retro web S4967 486 Cache System Board [pdfManuale d'usu S4967 486 Scheda Sistema Cache, S4967, Scheda Sistema Cache 486, Scheda Sistema Cache, Scheda Sistema, Scheda |