Limitazioni di timing Microsemi RTG4 FPGA

Informazione di u produttu

A RTG4 FPGA Timing Constraints User's Guide furnisce infurmazioni detallate nantu à l'applicazione di limitazioni di timing à l'uggetti di design specifichi utilizendu cumandamenti SDC. Include struzzioni nantu à l'accessu à l'ughjettu, specificazione di l'ughjettu esplicitu versus implicitu, caratteri di wild card, gerarchia è separatori di pin, cunvenzioni di nome di bus, è aghjunghje cumenti.

Specificazioni

- Nome di u produttu: RTG4 FPGA

- Guida d'usu: Limitazioni di timing Guida d'utilizatore

Istruzzioni per l'usu di u produttu

Accessu à l'ughjettu

Per applicà limitazioni di timing à l'uggetti di cuncepimentu:

- Aduprate cumandamenti cum'è get_cells, get_clocks, get_nets, get_pins, get_ports, all_inputs, all_outputs, all_registers basatu annantu à u tipu d'ughjettu.

- Riferite à l'aiutu in linea SmartTime per infurmazione più dettagliata.

Specificazione esplicita vs

SDC supporta a specificazione di l'ughjettu implicita è esplicita:

- A specificazione implicita hè quandu l'uttellu determina u tipu d'ughjettu per circà l'ughjettu.

- A specificazione esplicita implica a specificazione di u tipu d'ughjettu utilizendu cumandamenti d'accessu à l'ughjettu nidificatu per evità ambiguità.

Caratteri Wild Card

Aduprate caratteri wild card in i cumandamenti SDC:

- (backslash) interpreta u caratteru prossimu literalmente.

- * (asteriscu) currisponde à qualsiasi stringa.

Introduzione

In u cuncepimentu di disinni digitali sincroni FPGA, da l'ingressu di u disignu à l'implementazione fisica, raramente ottene u rendimentu di tempu necessariu di u disignu senza iterazione. Spessu deve passà per numerosi iterazioni di u ciculu di cuncepimentu - cattura di cuncepimentu HDL, sintesi, implementazione fisica (Place and Route) è Analisi di Timing - per ottene a chiusura di u timing. Stabbilimentu di Limitazioni di Timing è eseguisce l'Analisi di Timing sò i dui passi più impurtanti in iterazioni di cuncepimentu versu a chiusura di u timing. Per i disinni RTG4, Microsemi ricumanda di stabilisce limitazioni di timing sia per a sintesi sia per i passi di u locu è di a strada. Duvete prima stabilisce e limitazioni di l'affirmazione di u timing; vede "Asserzioni di timing" in a pagina 5. Se u rendiment di u timing ùn hè micca cumpletu in a prima iterazione, cunzidira à stabilisce limitazioni di timing supplementari è più avanzati in a seconda è iterazioni successive. Vede "Eccezioni di timing" à a pagina 6.

Utilizà e restrizioni di cuncepimentu di Synopsys

U Synopsys® Design Constraint (SDC) hè un furmatu basatu in Tcl utilizatu da l'arnesi Synopsys per specificà l'intentu di cuncepimentu è e limitazioni di timing. Microsemi supporta una variazione di u formatu SDC per a gestione di limitazioni.

Pudete utilizà i seguenti tipi di cumandamenti SDC quandu creanu limitazioni SDC per i disinni RTG4:

- Accessu à l'ughjettu

- Asserzioni di timing

- Eccezzioni di timing

Accessu à l'ughjettu

E restrizioni di timing SDC s'applicanu à l'uggetti di cuncepimentu specifichi. A Tabella 1-1 riassume i cumandamenti d'accessu à l'ughjettu supportati da SmartTime (u strumentu d'analisi di timing static Microsemi incorporatu cù l'arnesi di u locu è di a strada). Vede l'aiutu in ligna SmartTime per più infurmazione.

Table 1-1 Cumandamenti d'accessu à l'ughjetti supportati da SmartTime

| Ughjettu di disignu | Cumandamenti |

| Cellule / istanze | get_cells |

| Orologi | get_clocks |

| Reti | get_nets |

| Pins | get_pins |

| Porti | get_ports, all_inputs, all_outputs |

| I registri | tutti_registri |

Specificazione Implicit vs

In generale, i cumandamenti SDC includenu l'oggetti di designu cum'è argumentu. SDC supporta a specificazione di l'ughjettu implicita è esplicita.

Quandu l'uttellu determina u tipu d'ughjettu per circà l'ughjettu, hè chjamatu specificazione di l'ughjettu implicita. Quandu u tipu d'ughjettu hè specificatu (per evità l'ambiguità) utilizendu un cumandamentu d'accessu à l'ughjettu nidificatu, hè chjamatu specificazione di l'ughjettu esplicitu.

Per esampLe: Se tenete una reta chjamata 'my_net1', l'specificazione implicita hè my_net1 è l'specificazione esplicita hè [get_nets my_net1].

Ùn sò micca tutti l'uggetti di disignu sò applicabili à tutti i cumandamenti SDC. Ogni cumandamentu SDC accetta un inseme predefinitu di oggetti di designu cum'è argumenti. Microsemi ricumanda di utilizà u metudu di specificazione di l'ughjettu esplicitu per evità ambiguità in quantu à u tipu d'ughjettu. Se parechji tipi d'uggetti sò tornati dopu a ricerca di una specificazione implicita, i tipi di l'ughjettu sò priurità basati nantu à a lista di l'ughjetti di priorità di l'uttellu.

Vede l'aiutu in ligna SmartTime per più infurmazione.

Caratteri Wild Card

A Tabella 1-2 elenca i caratteri salvatichi dispunibili per l'usu in i cumandamenti SDC.

Table 1-2 Cumandamenti d'accessu à l'ughjetti supportati da SmartTime

| Wild Card | Funzione |

| \ | Interprete u caratteru prossimu literalmente |

| * | Corrisponde à qualsiasi corda |

Nota: A funzione di currispundenza richiede chì aghjunghje un backslash (\) prima di ogni slash in i nomi di pin in casu chì a slash ùn denota micca a gerarchia in u vostru disignu.

Gerarchia è Separatori di Pin

U software Synplify Pro hè predeterminatu per l'usu di '.' (periodu) cum'è a gerarchia è i separatori di pin per i limiti di timing.

Per esampLe: [get_pins {top_level.blockA.instance123.my_pin}] Per cambià u separatore di ierarchia da u predefinitu '.' (periodu) à u '/' (forward slash), utilizate u cumandimu: set_hierarchy_separator { / }

U software SmartTime usa predeterminatu '/' cum'è separatore di gerarchia di designu è ":" cum'è caratteru di separatore di pin.

Per esampLe: [get_pins {top_level/blockA/instance123:my_pin}] Avvisate chì '/' hè u separatore di gerarchia utilizatu per indicà chì 'instance123' hè presente in a ghjerarchia di designu sottu à u top_level 'blockA. U separatore di pin ":" identifica "my_pin" in "instance123".

Cunvenzioni di denominazione di l'autobus

Tutti i busi in a SDC file deve aduprà u nome di cunvenzione di nome in stile Verilog [index].

Per esampLe: [get_ports addr_bus_out[1]] Se vulete specificà a limitazione in tuttu u bus, pudete aduprà [get_port addr_bus_out].

Cumenti

Pudete aghjunghje cumenti à un SDC file precedendu a linea di cumenti cù un signu di libbra (#).

# Questa hè una linea di cumenti

Asserzioni di timing

L'affirmazioni di timing sò destinate à catturà i vostri bisogni di timing di cuncepimentu. Includenu i seguenti cumandamenti SDC:

- Periodu di l'orologio / Frequenza

- crià_clock

- create_generated_clock

- Ritardo di input / output

- set_input_delay

- set_output_delay

- set_external_check

- set_clock_to_output

- Clock-to-clock Incertezza

- set_clock_incertezza

- Clock Source Latency

- set_clock_latency

Vede "Limiti di timing è flussu di disignu" in a pagina 7 per i cumandamenti SDC di Timing Assertion Support Synplify Pro è SmartTime.

Eccezzioni di timing

Aduprate l'eccezzioni di timing per identificà i percorsi di cuncepimentu chì necessitanu di annullà e relazioni predefinite di u tempu di un ciclu unicu. I cumandamenti SDC per l'eccezzioni di timing includenu:

- Falsa strada

- set_false_path

- Strada multiciclu

- set_multicycle_path

- Percorsu di ritardu massimu

- set_max_delay

- Percorsu di ritardu minimu

- set_min_delay

- Archi di cronometraggio disabilitati

- set_disable_timing

Eccezzioni di timing è ordine di precedenza

Quandu u stessu percorsu di timing hà più di una limitazione d'eccezzioni di timing, SmartTime onore a limitazione di timing cù a più alta precedenza è ignora l'altri eccezzioni di timing secondu l'ordine di precedenza mostratu in a Tabella 1-3. Synplify Pro rispetta i limiti di timing secondu l'Ordine di precedenza in a Tabella 1-4.

Table 1-3 Eccezzioni di timing - Ordine di precedenza per SmartTime

| Eccezzioni di timing | Ordine di precedenza |

| set_disable_timing | 1 |

| set_false_path | 2 |

| set_maximum_delay/set_minimum_delay | 3 |

| set_multicycle_path | 4 |

Table 1-4 Eccezzioni di timing - Ordine di precedenza per Synplify Pro

| Eccezzioni di timing | Ordine di precedenza |

| set_false_path | 1 |

| set_max_delay/set_min_delay | 2 |

| set_multicycle_path | 3 |

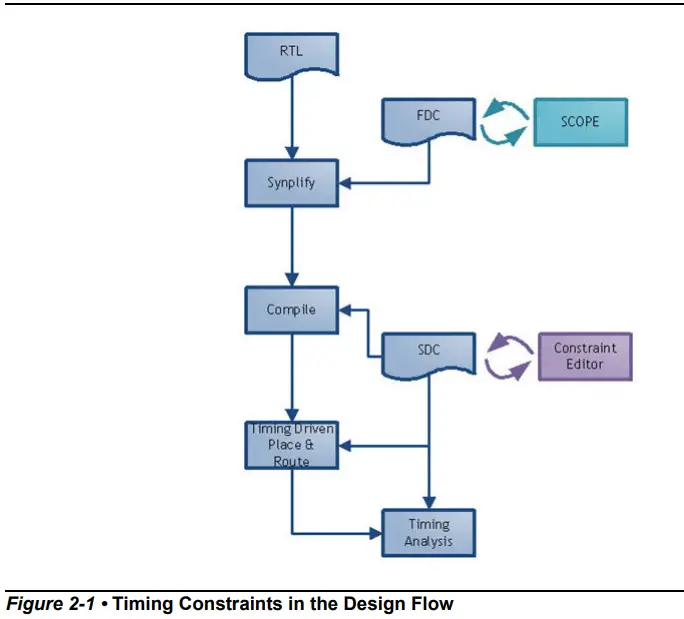

Limitazioni di timing è flussu di disignu

Stu capitulu descrive induve specificà e restrizioni di timing è eseguisce l'analisi di timing in u flussu di cuncepimentu Libero (Figura 2-1). Microsemi consiglia di furnisce Synplify Pro è SmartTime cù limitazioni di timing adeguate è cumplete. Inoltre, duvete ritruvàview i rapporti di timing da Synplify Pro è SmartTime per assicurà chì u disignu hè statu custrettu bè è cumpiendu i scopi di timing.

L'arnesi Libero (Timing Driven Place and Route and SmartTime) supportanu un sottogruppu di limitazioni di timing Synopsys SDC pertinenti per i disinni FPGA.

Microsemi consiglia di creà duie serie di limitazioni di timing in u flussu Libero:

- Limitazioni di timing FDC per a sintesi cù Synplify Pro.

- Limitazioni di timing SDC per e fasi Libero Timing Driven Place è Route è SmartTime.

Limitazioni di timing per Synplify Pro

- Overview

Synplify Pro supporta u furmatu FPGA Design Constraints (FDC). U furmatu FDC include:- Un subset di u standard Synopsys SDC per i limiti di timing

- Formatu di limitazione di timing legacy supportatu da Synplify Pro

Pudete furnisce limitazioni di timing à Synplify Pro da: - Importazione di a limitazione di u tempu file(s) in u prugettu Libero. Identificà a limitazione di u tempu file(s) da trasmette à Synplify Pro in Libero GUI. Cliccate cù u dirittu file(s) è sceglite Use for Synthesis. Per i dettagli nantu à l'importazione di limitazioni di timing in a GUI di Libero, riferite à l'aiutu in linea di Libero.

- Creazione di e limitazioni di timing utilizendu a GUI SCOPE (Synthesis Constraints Optimization Environment) dispunibule in u software Synplify Pro. E restrizioni create cù SCOPE sò salvate in una limitazione file utilizendu u furmatu FDC.

- Limitazioni di timing Synplify Pro supportate

I seguenti limitazioni di timing sò supportati da Synplify Pro per a sintesi FPGA:- crià_clock

- create_generated_clock

- set_input_delay

- set_output_delay

- set_false_path

- set_multicycle_path

- set_max_delay

- set_clock_latency

- set_clock_incertezza

Vede u Synplify Pro per Microsemi Reference Manual per i dettagli nantu à l'opzioni è l'argumenti.

- Limitazioni per i Requisiti di Design

U software di sintesi usa limitazioni di timing per fà scambii chì portanu à l'usu ottimale di risorse per ottene l'ubbiettivi di timing richiesti. E restrizioni di timing sò essenziali per assicurà chì e scelte ghjuste sò fatte da l'uttellu di sintesi mentre realizanu ottimisazioni di logica è mapping di u disignu.

Microsemi consiglia di includere restrizioni di clock e limitazioni di ritardo di input e output.

Ci sò dui tipi di limitazioni di u clock:- crià_clock

- create_generated_clock

Per definisce l'orologi di cuncepimentu per i disinni RTG4,: - Aduprate create_clock constraint per identificà è limità l'oscillatori è i porti di input primariu utilizati cum'è clock.

- Aduprate create_generated_clock constraint per identificà è limità i pins di output CCC di u fabricu utilizati cum'è clock.

- FDC Example cù create_clock è create_generated_clock

In l'example sottu una cumminazione di create_clock è create_generated_clock constraints sò usati per definisce e restrizioni di clock necessarie.

Prima, a fonte di u clock hè identificata cum'è u portu di input clk_in à 50 MHz.

Allora sta fonte di clock hè aduprata per generà un clock 200 MHz (clk_core) cù un CCC:

Nota: U caratteru backslash "\" face parte di a sintassi Tcl. Si rompe un cumandamentu unicu longu in parechje linee.

Nota: U software Synplify Pro hè predeterminatu per l'usu di '.' (periodu) cum'è u separatore di gerarchia per i limiti di tempu. Aduprate u cumandimu set_hierarchy_separator in u FDC file per ridefinisce u caratteru di separatore di gerarchia. Per esample:set_hierarchy_separator {/}

I fatturi divide_by è multiplicly_by sò derivati da u diagrama PLL affissatu nantu à a tabulazione "Avanzata" di u configuratore CCC di tissu. U software Synplify Pro hè predeterminatu à 100 MHz di frequenza di clock necessaria per tutti l'orologi chì mancanu una limitazione di timing. - FDC Example cù set_input_delay è set_output_delay

In questu example, set_input_delay è set_output_delay constraints sò usati per definisce e restrizioni di timing di ritardu di input è output. Queste limitazioni sò necessarie per definisce u budget di timing necessariu per l'interfaccia I/O.

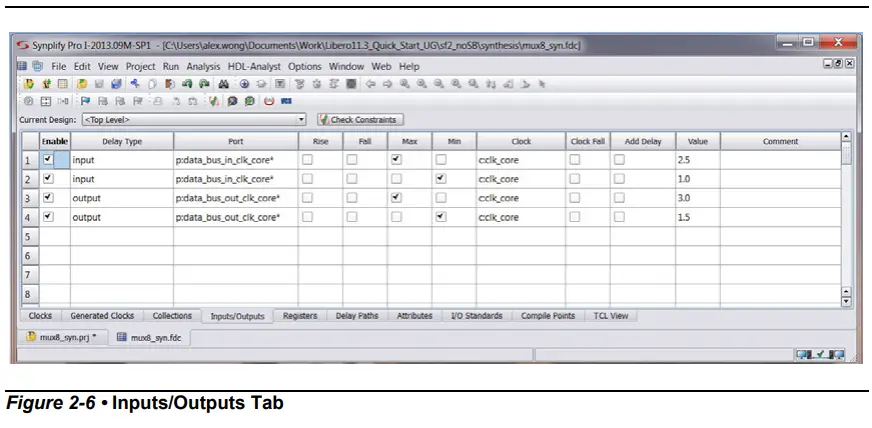

In questu example, tutte e restrizioni usanu clk_core da l'ex precedenteample cum'è u clock di riferimentu.

U ritardu di input nantu à i porti di input data_bus_in_clk_core hè 2.5ns (max) è 1.0ns (min).

U ritardu di output nantu à i porti di output data_bus_out_clk_core hè 3.0ns (max) è 1.5ns (min).

# ritardu di input

set_input_delay -clock [get_clocks clk_core] \

-max 2.5 \

[get_ports {data_bus_in_clk_core*}] set_input_delay -clock [get_clocks clk_core] \

-min 1.0 \

[get_ports {data_bus_in_clk_core*}] # ritardi di output

set_output_delay -clock [get_clocks clk_core]\

-max 3.0 \

[get_ports {data_bus_out_clk_core*}] set_output_delay -clock [get_clocks clk_core] \

-min 1.5 \

[get_ports {data_bus_out_clk_core*}] - Verificatore di limitazione

Microsemi ricumanda di cunvalidà FDC o limitazioni di timing dopu avè impurtatu o creanu. Questu hè soprattuttu impurtante se i limitazioni di u tempu file hè impurtatu.

Synplify Pro furnisce una utilità di verificatore di limitazione chì pudete aduprà per validà e restrizioni di timing SDC. U verificatore di limitazione hè accessibile da u menù di u prughjettu (Esegui> Verificazione di limitazione) in a GUI Synplify Pro. Genera un rapportu di cuntrollu di limitazione (*_cck.rpt) cù dettagli nantu à qualsiasi prublemi cù limitazioni di timing. A rùbbrica riassuntu deve indicà chì ùn sò micca stati trovati prublemi cù e limitazioni di timing.

Aduprate u rapportu di verificatore di limitazione per correggere i sbagliati ligati à una sintassi incorrecta o nomi d'uggetti.

Per i dettagli nantu à u Synplify Pro Constraint Checker, riferite à u Synplify Pro for Microsemi User Guide. - Limitazioni per ottimisà u vostru disignu

Una volta verificate e restrizioni di timing, Microsemi ricumanda di utilizà a funzione di analisi di timing in Synplify Pro per determinà se tutte e restrizioni di cuncepimentu necessarie sò state furnite. Pudete utilizà a lista di i percorsi di cuncepimentu violazione in u rapportu di timing per identificà qualsiasi limitazione di timing mancante o imprecisa.

Nota: Siccomu u disignu ùn hè ancu piazzatu, u rapportu di timing utilizeghja stimi basati nantu à mudelli di carica di filu per i ritardi netti. Questu hè u mutivu chì i violazioni di u timing in questu stagE pò esse o ùn pò micca appare dopu à u locu è a strada.

Microsemi ricumanda di passà per un passu di u flussu tutale di u disignu, cumpresi Timing Driven Place and Route prima di aghjunghje eccezzioni di timing per a sintesi. Pudete tandu aduprà u rapportu di analisi di u locu più precisu è u tempu di rotta per determinà e restrizioni richieste.

E restrizioni di Clock, Input and Output Delay sò l'inseme minimu di limitazioni di timing necessarie per tutti i disinni. Certi disinni ponu esse bisognu di restrizioni di timing supplementari cunnisciute cum'è eccezioni di timing. Per esampLe:- Falsi percorsi (set_false_path),

- Percorsi multicicli (set_multicycle_path)

- Ritardo Massimu di Path (set_max_delay)

Pudete utilizà l'eccezzioni di timing per identificà i percorsi di cuncepimentu chì necessitanu chì e relazioni predefinite di u ciclu unicu per esse annullate. Duvete guidà l'ottimisazioni di l'uttellu di sintesi identificendu i percorsi di cuncepimentu chì: - Ùn avete micca una relazione di timing (set_false_path)

- Avè una relazione di timing chì ùn hè micca un ciculu unicu (set_multicycle_path o set_max_delay)

- A precedenza

Per risolve i cunflitti di limitazione di timing quandu parechje eccezzioni di timing sò applicate à u stessu oggettu di designu, si applicanu e seguenti regule di precedenza:

set_disable_timing hà a precedenza annantu à tutte l'altri limitazioni di eccezzioni di timing.

A limitazione False Path hà a precedenza annantu à Ritardo Massimu di Percorsu / Ritardo Minimu di Percorsu o Restrizzione di Percorsu Multiciclu.

A limitazione Maximum Path Delay/Minimu Path Delay hà a precedenza annantu à a limitazione Multicycle Path.

Table 2-1 Cumandamenti d'accessu à l'ughjetti supportati da SmartTimeEccezzioni di timing Ordine di precedenza set_disable_timing 1 set_false_path 2 set_maximum_delay / set_minimum_delay 3 set_multicycle_path 4 - Ottimisazione per Timing versus Area

Quandu eseguite a sintesi di Synplify Pro, l'uttellu compie prima u disignu è poi mape à e cellule di a tecnulugia Microsemi.

Per automaticamente, Synplify Pro faci automaticamente scambii efficaci trà u rendiment di l'area è di u timing per ottene u megliu risultati. Tuttavia, pudete guidà Synplify Pro per ottimisà u disignu per u rendiment di timing à a spesa di l'area. À u cuntrariu, pudete guidà Synplify Pro per ottimisà u disignu per l'area à a spesa di u rendiment di timing.

In generale, l'ottimisazione per a prestazione di timing consuma più risorse FPGA (area) è l'optimizazione per l'area spessu significa ritardi più grande (prestazione di timing più debule). Duvete ponderà i vostri bisogni di prestazione di timing contru i vostri bisogni di l'area per determinà ciò chì funziona megliu per u vostru disignu.

Consultate u Capitulu 10 di u Synplify Pro per Microsemi User Guide per più infurmazione nantu à l'opzioni di ottimisazione. - Analisi di Timing Post-Sintesi cù Synplify Pro

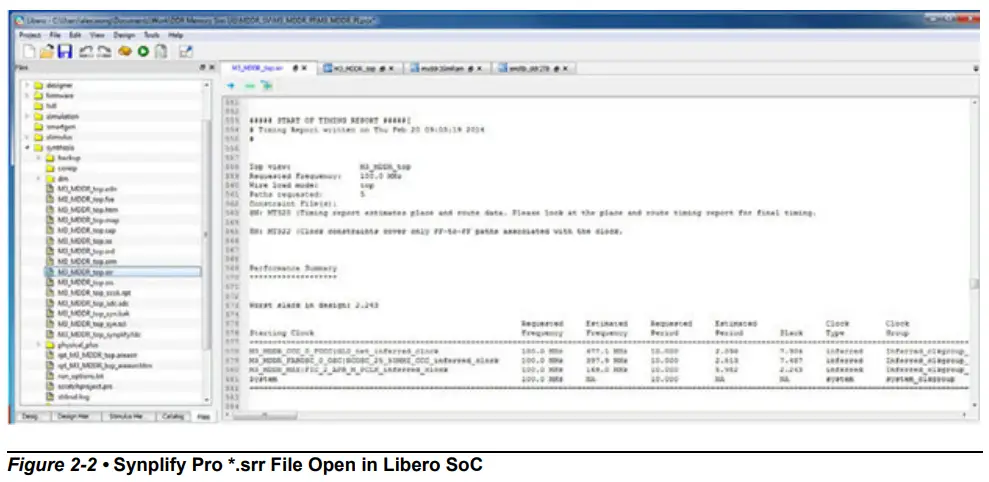

Synplify Pro genera un rapportu di timing dopu chì a sintesi hè cumpleta. Dopu avè eseguitu a sintesi, cliccate nantu View Log buttone per apre u logu file in Synplify Pro.

U logu di sintesi file hè ancu dispunibule da Libero SoC, sottu Sintesi in u pane Reports.

U file si trova sottu à u cartulare di sintesi cù l'estensione *.srr è viewcapace in Libero SoC. Cliccate u File tab in u vostru Prughjettu SoC Libero. Espandi a Sintesi file gruppu. Cliccate doppiu u *.srr file per apre in u Libero SoC Editor View pane. Scroll down to the section intitulata START OF TIMING REPORT (Figura 2-2).

U rapportu di timing Synplify Pro hè spartutu in e seguenti sezioni:- Riassuntu di Rendimentu

- Relazioni di clock

- Informazioni di l'interfaccia

- Rapportu detallatu per l'orologi

Aduprate u rapportu di timing di sintesi per cunfirmà: - E restrizioni sò state pigliate è applicate cum'è previstu.

- U disignu ùn hà micca una violazione significativa di u tempu

Siccomu u disignu ùn hè ancu piazzatu, u rapportu di sintesi di timing stima i ritardi netti utilizendu mudelli di carica di filu. Tuttavia, i ritardi di cellula utilizati in u rapportu di timing sò precisi.

Una violazione di u timing di a cunfigurazione pò esse cunsiderata significativa, se u ritardu di u percorsu escludendu u ritardu netu supera u tempu necessariu. Questu hè di solitu un'indicazione chì o u requisitu di timing ùn hè micca realisticu o chì u percorsu di cuncepimentu richiede un pipelining supplementu. In ogni casu, hè assai improbabile chì una strada di cuncepimentu cù ritardu di cellula chì supera u tempu necessariu scuntrà u scopu di timing dopu locu è rotta.

- Eccezzioni di timing

Se l'analisi di u timing post-sintesi informa chì u disignu ùn risponde micca à e specificazioni di timing per a velocità di u clock o i ritardi di l'I / O, Microsemi ricumanda d'utilizà eccezzioni di timing per aiutà a sintesi.

Microsemi ricumanda di passà per un passaghju di u flussu tutale di u disignu, cumpresi Timing Driven Place and Route, prima di aghjunghje eccezzioni di timing per a sintesi. Pudete tandu aduprà u rapportu di analisi di u locu più precisu è u tempu di rotta per determinà e restrizioni richieste. Aduprate limitazioni di timing falsi per identificà percorsi di design specifichi chì ùn propaganu micca cambiamenti di livellu logicu è ùn deve esse cunsideratu durante l'analisi di u tempu. L'uttellu di sintesi ignora i percorsi di cuncepimentu identificati utilizendu sta limitazione per l'ottimisazioni di logica è cartografia. Aduprate e restrizioni di timing Path Multicycle, False Path è Maximum Path Delay per identificà i percorsi di cuncepimentu chì anu una relazione di timing diversa da a relazione predefinita di u ciclu unicu. U strumentu di sintesi usa a nova relazione per ottimisazioni.

E restrizioni di u Path Multiciclu è False Path sò tipicamente risultatu in rilassante u requisitu di u tempu di u ciclu di u clock unicu originale. A limitazione Maximum Path Delay pò risultà à rilassà o rinfurzà u requisitu di timing originale basatu annantu à u valore di u tempu specificatu da l'utilizatore.

FDC Examples

# Falsa Strada

set_false_path -from [get_ports uart_ctrl] # Ritardo Massimu Path

set_max_delay -to [get_ports {ram_rd_enable}] 4.0

# Percorsu Multiciclu

set_multicycle_path 4 -to [get_ports {I2C*}]

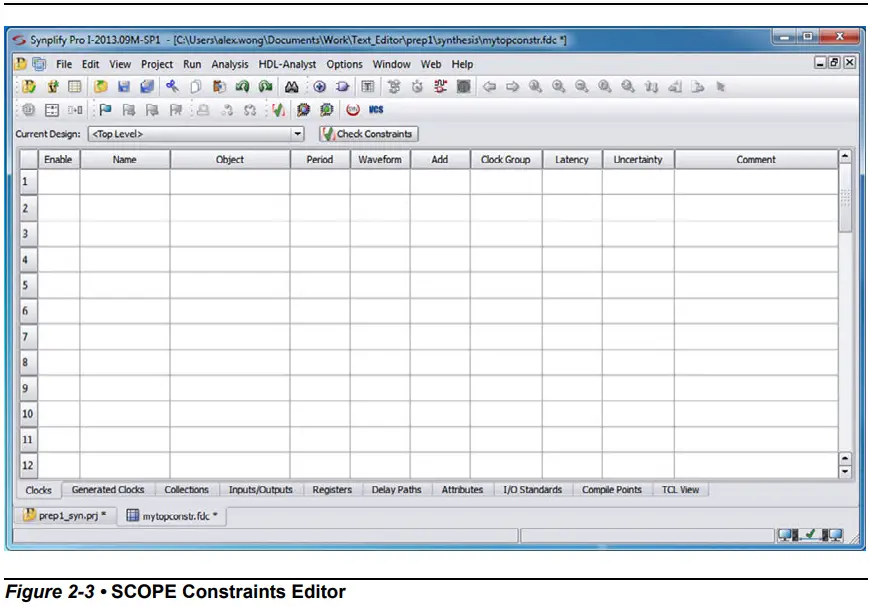

SCOPE è Utilizendu u SDC annotatu avanti

Pudete aduprà SCOPE da Synplify Pro per inserisce restrizioni per u passu di sintesi. Dopu a sintesi, Synplify Pro genera un *_sdc.sdc file, chì cuntene i limiti di timing annotati in avanti. Vede "Using the Forward Annotated SDC" à a pagina 15 per i dettagli. U flussu cunsigliatu hè di creà limitazioni separati per i passi di Sintesi è Timing-Driven Place è Route.

- Ingressu di limitazione di timing cù SCOPE

SCOPE hè un editore furnitu cù Synplify Pro per inserisce è gestisce i limiti di timing è l'attributi di sintesi (Figura 2-3).

I trè tippi di limitazioni cumuni à a maiò parte di i disinni sò:- Limitazioni di l'orologio - Tutti i disinni sincroni sò guidati da qualchì tipu di orologi. Violazioni di u tempu, cum'è a cunfigurazione è e violazioni di u tempu di mantene, ùn sò micca significati senza una limitazione di u clock.

- Limitazioni di ritardo di input è output - I ritardi di l'Input è di l'Output permette di ritardi di strada esterni à u FPGA. Queste limitazioni sò parte di u requisitu di ritardu di bilanciu.

- Eccezzioni - Quandu un disignu ùn riesce à risponde à i requisiti di timing, pudete avè bisognu di restrizioni più avanzate per portà u disignu à a chjusura di u timing. Quandu sò applicate à percorsi specifichi in u disignu, queste eccezzioni di timing annullanu u cumpurtamentu predeterminatu di Synplify Pro quandu questi percorsi di timing sò cunsiderati durante l'ottimisazione.

Prima di entre in ogni limitazione, prima compilate u disignu in Synplify Pro (Run> Compile Only). Eseguisce a compilazione in Synplify Pro pre-populate SCOPE cù nomi d'ughjettu. Questu puderia risparmià tempu è sforzu per inserisce i nomi di l'ughjetti.

- Identificatori di prefissi supportati da SCOPE è FDC

Synplify Pro usa l'identificatori di l'ughjettu definiti in a tabella seguente per e restrizioni definite in SCOPE o FDC files (Table 2-2).

Table 2-2 Identificatori di prefissi è oggetti di disignuIdentificatore di prefissu (FDC) Equivalente à SDC Oggetti di design per esse appiicati v: design_name n/a Moduli c: nome_clock get_clocks Orologi i: nome_istanza get_cells Instanzi p: nome_portu get_ports Porti t: pin_name get_pins Porti gerarchici o pin di cellule istanciate b: bus_name get_pins Pezzi di autobus n: net_name get_nets I nomi di rete - Limitazioni di l'orologio

Ci hè dui tipi di restrizioni di clock: create_clock è create_generated_clock. SCOPE hà duie tabulazioni separate per queste duie restrizioni.

Aduprate a tabulazione Clocks per identificà e fonti di clock (create_clock). Vede a Figura 2-4.

Aduprate a tabulazione Generated Clocks per identificà i clock generati (create_generated_clock) in u disignu. Vede a Figura 2-5.

Per i disinni RTG4:- Oscillatori o porti di Clock Input sò fonti tipiche di clock.

- L'outputs di Fabric CCC sò tipici orologi generati.

Synplify Pro supporta una funzione avanzata di copia è incolla. Hè pussibule copià l'uggetti da u schematicu views è incollà i so nomi in SCOPE.

Per esampLe: Evidenziate u pin terminale di output di l'oscillatore (in u RTL view schematic), copia (CTRL + C) è poi incollà (CTRL + V) in SCOPE.

- Limitazioni di ritardo I/O

E restrizioni di clock ùn sò micca abbastanza per limità i porti I/O. Utilizà e restrizioni di ritardu di input è output

(set_input_delay, set_output_delay) limitazioni per specificà e restrizioni I/O. Navigate à a tabulazione Inputs/Outputs in SCOPE per fà cusì (Figura 2-6).

- Verificatore di limitazione

Per verificà e restrizioni entrate finu à avà, cliccate nant'à u buttone Verificate e restrizioni in a barra di menu. Synplify Pro genera un rapportu di cuntrollu di restrizioni di clock (*_cck.rpt). U riassuntu deve indicà chì ùn ci sò micca prublemi cù e limitazioni di timing.

U verificatore di limitazione hè ancu accessibile da u menù di Prughjettu (Project> Run> Constraint Check). - Eccezzioni

Certi disinni necessitanu restrizioni di timing supplementari cunnisciute cum'è eccezzioni di timing, cum'è:- set_false_path

- set_max_delay

- set_multicycle_path

Per inserisce eccezioni di timing in SCOPE navigate à a tabulazione Percorsi di ritardu. Dopu à salvà u file, da u File menu sceglite Close per vultà à u Prughjettu view.

- Utilizà u SDC annotatu avanti

Dopu a sintesi, Synplify Pro genera un SDC file chì pudete aduprà per i passi restante in u flussu Libero. Questu file (cù l'estensione *_sdc.sdc) hè dispunibule sottu Limitazioni di Timing in u Prughjettu Libero view.

Per automaticamente, questu file ùn hè micca usatu da Libero. U flussu cunsigliatu hè di creà limitazioni separati per i passi di Sintesi è Timing-Driven Place è Route.

L'utilizatori devenu riview lu file cuntenutu di u Synplify generatu avanti annotatu file prima di attivà u file per l'implementazione. Per attivà un SDC file per Timing-Driven Place è Route, cliccate right-click u file è sceglite Use for Compile. Libero usa stu SDC file per i passi rimanenti in u flussu di disignu, partendu da Compile. - Limitazioni

- A SDC annotata in avanti file da Synplify Pro ùn include micca alcuna limitazione set_clock_latency presente in u SDC d'utilizatore originale file.

- Synplify Pro ùn genera micca automaticamente restrizioni di clock per oscillatori o istanze CCC. Duvete furnisce restrizioni di clock precise (create_clock, create_generated_clock) à Synplify Pro. Queste restrizioni sò dopu annotate in avanti in u *_sdc.sdc file.

Limitazioni Timing per Timing-Driven Place è Route

L'arnesi Libero (Timing Driven Place and Route and SmartTime) supportanu un sottogruppu di limitazioni di timing Synopsys SDC pertinenti per i disinni FPGA. Per stabilisce e limitazioni di timing, pudete aduprà:

- SmartTime Constraint Wizard

- Editore di restrizioni SmartTime

- SDC file(s)

Per urganizà a limitazione di u tempu files, aduprate u "Organizzà a limitazione Files” finestra di dialogu. Quandu importa un SDC file per Timing Driven Place and Route, assicuratevi di includellu per l'usu da u strumentu Compile. Per attivà un SDC file digià impurtatu in Libero, cliccate right-click nant'à u file è sceglite Use for Compile (riferite à Figura 2-7).

- Timing-Driven Place è Route Constraints

L'Analisi di Timing SmartTime supporta u seguitu settore di limitazioni di timing SDC:- crià_clock

- create_generated_clock

- set_input_delay

- set_output_delay

- set_clock_esterno

- set_clock_to_output

- set_false_path

- set_multicycle_path

- set_max_delay

- set_min_delay

- set_clock_latency

- set_clock_incertezza

- set_disable_timing

Per i dettagli nantu à l'opzioni è l'argumenti di i cumandamenti SDC, riferite à l'aiutu in linea SmartTime.

- Limitazioni per i Requisiti di Design

Microsemi ricumanda di utilizà u flussu seguente per inserisce limitazioni di timing:- SmartTime Constraint Wizard - Identificà l'orologi, i limiti di ritardu di input è output

- Editor di attributi I/O - Fornite infurmazione cumpleta di attributi I/O per u disignu

- Generate è analizà u rapportu di Copertura di Limitazioni

- SmartTime Constraint Wizard

SmartTime include un Assistant di Restrizzione chì permette l'entrata rapida è faciule per e restrizioni di clock è I/O (Figura 2-8).

Invoca l'Assistente di Restrizzione da SmartTime (Utensili> Assistente di Restrizzione). L'Assistente di restrizioni vi permette di aghjunghje restrizioni in l'ordine seguente:- Restrizzione generale di u clock

- Restrizzione I/O generale

- Limitazioni specifiche di u clock

- Limitazioni di clock generate

- Limitazioni di input specifichi

- Limitazioni specifiche di output

Aduprate e tabulazioni di restrizioni generali per stabilisce e restrizioni predeterminate per i clock è l'I/O.

I limiti predeterminati ponu esse rimpiazzati da e restrizioni specifiche per i clock è I/O.

- Limitazioni di l'orologio

Aduprate e tabulazioni di u Clock specificu è Generated clock constraint per:- Oscillatori usati cum'è fonti di clock.

- Fabric CCC outputs usati cum'è clock generati

- Orologi da altre fonti

- Limitazioni I/O

Aduprate a tabulazione Restrizzione I/O generale per stabilisce e restrizioni predeterminate per tutti i porti di input è output in u disignu. I limiti di I/O predeterminati ponu esse rimpiazzati in e tabulazioni di restrizioni di input specifichi è di output specifichi per i porti selezziunati.

Per i dettagli nantu à u Constraint Wizard, riferite à l'aiutu in linea SmartTime. - Attributi I/O è l'Editor di attributi I/O

A prestazione di timing di i percorsi I/O hè significativamente influenzata da l'attributi I/O.

Aduprate a funzione I/O Attribute Editor in MultiView Strumenta Navigator (MVN) per furnisce l'infurmazione cumpleta di l'attributi I/O per u disignu.

Per i dettagli nantu à l'Editor di attributi I/O, riferite à MultiView Navigatore aiutu in linea. - Copertura di limitazione

Hè impurtante di generà un Rapportu di Copertura di Limitazioni (Figura 2-9), perchè u rapportu di timing analizeghja solu u rendiment di timing per i percorsi di cuncepimentu cù limitazioni di timing. I camini di timing senza limitazioni di timing ponu avè violazioni di timing è ùn sò micca signalati. Invocate u rapportu di Copertura di Restrizzione da SmartTime Analyzer (Strumenti> Rapporti> Copertura di Restrizzione).

I percorsi di cuncepimentu o l'uggetti cù limitazioni mancanti sò listati sottu Suggerimenti di Migliura. Review ogni suggerimentu è furnisce limitazioni adatte per assicurà chì tutti i percorsi di cuncepimentu anu limitazioni di timing.

Per i dettagli nantu à u Rapportu di Copertura di Constraint, riferite à l'aiutu in linea SmartTime. - Limitazioni per ottimisà u vostru disignu

E restrizioni di timing di cuncepimentu pò avè bisognu à esse ottimisate se u disignu ùn riesce à scuntrà i requisiti di timing, ancu dopu avè finitu Timing Driven Place and Route (TPDR).

U flussu cunsigliatu per ottimisà e restrizioni di disignu hè:- Run Timing Driven Place è Route. Assicuratevi chì l'opzione Timing-driven hè attivata durante Place and Route.

- Generate è Inspeccione rapporti di Analisi di Timing. Analizà i rapporti di l'Analisi di Ritardo Massimu è Minimu.

- Aprite l'Editor di restrizioni SmartTime è furnisce restrizioni supplementari, cumprese l'eccezzioni di timing.

- Per migliurà u rendiment di Placer:

- Debug percorsi di cuncepimentu cù violazioni di timing.

- Aduprate set_max_delay per limità i percorsi di duminiu inter-clock.

- Utilizà u locu è u percorsu guidatu da u timing (TDPR)

L'obiettivu primariu di TDPR hè di scuntrà i limiti di timing. Se ùn sceglite micca l'opzione Timing-driven, Place and Route ùn cunsiderà micca e limitazioni di timing.

Assicuratevi chì Timing-driven hè sceltu prima di eseguisce Place and Route (cliccate right-click Place and Route è sceglite Configure Options in a suite di strumenti Libero). Questa opzione hè sceltu per automaticamente per RTG4. - Rapporti di analisi di u tempu

SmartTime genera dui tipi di rapporti di timing per automaticamente per l'analisi di Ritardo Max è Minu:-

- Rapportu di timing - Stu rapportu mostra l'infurmazioni di timing urganizata da u duminiu di u clock.

- Rapportu di violazioni di timing - Stu rapportu di slack flat furnisce infurmazioni nantu à e violazioni di limitazione. Per generà rapporti di analisi di timing in Libero, fate un clic right Verify Timing è sceglite Run.

- Cuntenutu di u rapportu di timing

U rapportu di timing cuntene e seguenti sezioni:- Header - elenca u tipu di rapportu, a versione, a data è l'ora di u rapportu è l'infurmazione generale di u disignu

- Riassuntu - riporta l'infurmazioni di timing per ogni duminiu di u clock

- Path Selections - elenca l'infurmazioni di timing per diversi tipi di camini in u disignu. Per i dettagli, fate riferimentu à l'aiutu in ligna SmartTime.

- Cuntenutu di u rapportu di violazione di u tempu

U rapportu di violazione di u timing cuntene e seguenti sezioni: - Intestazione

L'intestazione liste:- Tipu di rapportu

- Versione di SmartTime utilizata per generà u rapportu

- Data è ora chì u rapportu hè statu generatu

- Informazione generale di u disignu (nome, famiglia, etc.)

- Camini

A sezione di camini elenca l'infurmazioni di u tempu per i camini violati in u disignu.

Per automaticamente, u limitu di slack hè 0 è u numeru di camini hè limitatu. U numeru massimu predeterminatu di camini rappurtati hè 100.

Tutti i domini di l'orologi sò mischiati in stu rapportu. I camini sò elencati per diminuzione di slack.

-

- Editore di restrizioni SmartTime

L'Editor di restrizioni SmartTime hè un strumentu chì vi permette di creà, view è edità tutte e limitazioni di u tempu di cuncepimentu. Limitazioni furnite attraversu l'assistente di restrizioni o SDC files sò dispunibuli per edità in l'Editor di restrizioni SmartTime.

Aduprate l'Assistente di Restrizzione per furnisce facilmente limitazioni di timing basi per l'orologi è i porti I/O. Per limitazioni di timing avanzate, cum'è eccezzioni di timing, utilizate l'Editor di restrizioni.- Eccezzioni di timing

Basatu nantu à a cumplessità di u disignu, l'eccezzioni di u tempu pò esse dumandate. L'eccezzioni di timing sò limitazioni di tempu stabilite nantu à percorsi specifichi in u disignu. Per esampLe:- set_false_path

- set_max_delay

- set_multicycle_path

Furnisce queste limitazioni richiede a cunniscenza di i percorsi di dati in u disignu è e so esigenze di timing. Per automaticamente, SmartTime usa un ciculu di clock unicu per analizà ogni percorsu di u tempu chì hà una limitazione di clock impostata. L'eccezzioni di timing sò aduprate per annullà a limitazione di u clock predeterminatu per u percorsu di disignu.

Per i dettagli nantu à l'Eccezzioni di Timing, riferite à l'aiutu in linea SmartTime.

Nota: Basatu nantu à a gravità di e violazioni di u timing, pò ancu esse necessariu di furnisce limitazioni di eccezzioni di timing à u software di sintesi. Per furnisce limitazioni di l'eccezzioni di timing à u software di sintesi, include queste limitazioni in u FDC file esse furnitu à Synplify Pro.

- Eccezzioni di timing

Migliurà u rendiment di u Placer

Quandu u disignu ùn riesce à scuntrà i scopi di u timing, i percorsi di cuncepimentu falluti devenu esse analizati cù cura. Dui prublemi anu da esse analizati:

- Pò esse migliuratu u funziunamentu di u timing di u percorsu (s) fallimentu se u piazzamentu di l'istanza hè statu mudificatu?

I ritardi longu di a strada per i percorsi di cuncepimentu cù violazioni di a stallazione ponu indicà chì a piazza di l'istanza ùn era micca ottimale. U piazzamentu di u percorsu di u disignu pò esse esaminatu cù u strumentu "Chip Planner", chì face parte di u MultiView Navigatore. - Sò i limitazioni di u tempu chì sò abbastanza per u placer per identificà è travaglià nantu à i veri percorsi critichi in u disignu?

Assicuratevi chì un inseme cumpletu di limitazioni di timing hè creatu è passatu à l'uttellu di piazzatore. Aduprate a limitazione set_max_delay per limità bè i percorsi di cuncepimentu di u duminiu inter-clock. E sezzioni seguenti anu più dettagli nantu à passà e restrizioni è aduprà set_max_delay constraints.

- Performance Placer - Limitazioni supportate

Pudete passà limitazioni di timing à u Placer da:- Urganizà a limitazione di u tempu files aduprendu l'Organizazione Constraint Files finestra di dialogu. Quandu importa un SDC file per u placer, assicuratevi di includellu per l'usu da l'uttellu Compile. Per attivà un SDC file digià impurtatu in Libero, cliccate right-click u file è sceglite Use for Compile.

- Ingressu di limitazioni in a GUI SmartTime - Se utilizate scenarii, assicuratevi chì u scenariu hè attivatu per TDPR.

- Limitazioni

- U piazzatore supporta attualmente e seguenti limitazioni:

- crià_clock

- create_generated_clock

- set_clock_latency

- set_input_delay

- set_output_delay

- set_max_delay

- set_false_path

- I seguenti limitazioni ùn sò micca supportati da u placer:

- set_clock_incertezza

- set_multicycle_path

- set_min_delay

- U placer ùn sustene micca u timing di u duminiu inter-clock. U piazzatore ottimizza l'orologi in u so duminiu, ma micca trà i duminii. Per attivà l'ottimisazioni di u placer per i percorsi di domini inter-clock, utilizate a limitazione set_max_delay. Questu hè descrittu in a sezione dopu.

- U piazzatore ùn include micca u percorsu di generazione di u clock in u calculu di u tempu d'arrivu / richiede quandu si usa a limitazione set_max_delay.

- U piazzatore supporta attualmente e seguenti limitazioni:

- Utilizà set_max_delay per migliurà i risultati di u Placer

Pò esse pussibule di migliurà i risultati di u placer usendu set_max_delay limitazione di timing in percorsi di cuncepimentu cù violazioni di timing. Cunsiderate l'usu di stu approcciu se u percorsu violazione:-

- Hè una strada di duminiu inter-clock.

- Contene ritardi di generazione di clock chì sò significativamente diffirenti trà i punti di iniziu è di fine.

- Per include restrizioni di timing supplementari per u placer:

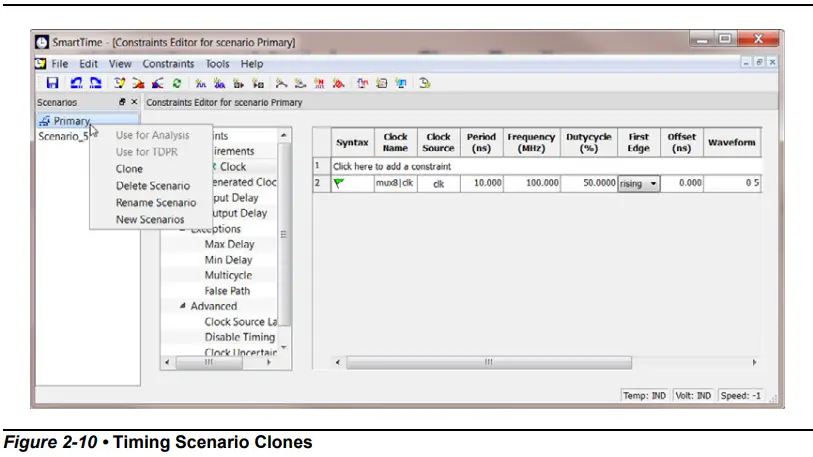

- Clona u scenariu di limitazioni di timing esistenti in SmartTime. Da u Constraint Editor, cliccate right-click Primary scenario è sceglite Clone (Figura 2-10).

- Mantene a limitazione originale (Primaria) per l'analisi di timing

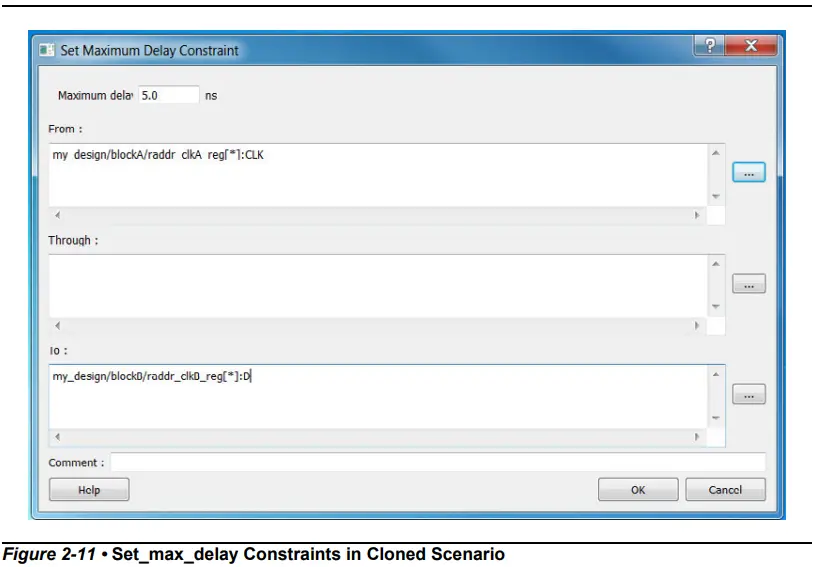

- Inserite set_max_delay constraints per i percorsi di cuncepimentu chì attraversanu i domini di clock (Figura 2-11).

- Aduprate u sicondu settore di limitazioni (scenariu clonatu) esclusivamente per TDPR. Cliccate cù u dirittu Scenariu clonatu è sceglite Use for TDPR (Figura 2-12).

- Clona u scenariu di limitazioni di timing esistenti in SmartTime. Da u Constraint Editor, cliccate right-click Primary scenario è sceglite Clone (Figura 2-10).

-

Per i dettagli nantu à a limitazione set_max_delay, riferite à l'aiutu in linea SmartTime.

Limitazioni per i blocchi IP RTG4

Stu capitulu descrive i requisiti di limitazione per i seguenti blocchi:

- Oscillatori

- Circuiti di cundizzioni di l'orologio di tissu (CCC)

- Interfaccia seriale à alta velocità (SERDES)

Oscillatori

L'oscillatore hà una sola output CLKOUT di 50 MHz. L'output pò esse cunnessu solu à u configuratore CCC.

- Limitazioni di sintesi di oscillatori

Avete da specificà una limitazione di clock per l'oscillatore utilizatu da u disignu.

Figura 3-2 mostra u bloccu vistu da sintesi.

E seguenti limitazioni funzionaranu per un oscillatore cù RCOSC_50MHZ_0 cum'è nome d'istanza. L'oscillatore RC hè cunfiguratu per 50 MHz.

create_clock -name osc_50MHz -period 20 \

[get_pins {RCOSC_50MHZ_0.CLKOUT}] - Oscillator Place and Route Constraints

Per SmartTime, i limiti per u configuratore di l'oscillatore cunnessu à l'istanza CCC RTG4FCCC_0 sò:

create_clock -name osc_50MHz -period 20 [get_pins {RCOSC_50MHZ_0:CLKOUT}]

Circuitu di cundizzioni di l'orologio di tissu RTG4 (CCC)

I CCC sò usati per multiplicà, dividite o ritardà l'orologi. U so effettu hè megliu discrittu utilizendu orologi generati.

- RTG4 Fabric CCC Synthesis Constraints

Per creà una restrizione RTG4FCCC per a sintesi via un clock generatu, avete bisognu di utilizà RTG4FCCC multiplici è divide fattori. Questa infurmazione hè dispunibule in a tabulazione Avanzata in u CCC Configurator accessibile per mezu di u software Libero (Figura 3-3).

A cunfigurazione CCC mostrata in a Figura 3-3 genera quattru clock:- In GL0, un clock 150 MHz generatu da u clock di input 50 MHz utilizendu u PLL

- In GL1, un 200 MHz generatu da u listessu PLL

- In GL2, un clock 25 MHz generatu da l'oscillatore 50 MHz.

- In GL3, un clock 100MHz generatu da CLK3_PAD è CLK_PAD2.

A divisione esatta è i fattori di multiplicazione ponu esse calculati in basa di e cunfigurazioni di divisore mostrate in u cunfiguratore. I fatturi utilizati per GL0 sò circundati. Quandu u CCC hè utilizatu, u fattore di multiplicazione hè datu da u divisore di feedback (circulatu in blu); u fattore di divisione hè datu multiplicà u divisore di riferimentu (circulatu in rossu) da u divisore di output (GPD) (circulatu in verde).

L'orologi generati currispondenti sò:

create_clock -name CLK0_PAD -period 20 [get_pins {RTG4FCCC_0.CLK0_PAD}] create_clock -name CLK2_PADP -period 10 [get_pins {RTG4FCCC_0.CLK2_PADP}] create_clock -name CLK3_PADP [get_clock -name CLK10_PADP -genera ted_clock -name clk_4mhz - divide_per 0 -multiplica_per 3 \

-source [get_pins {RTG4FCCC_0.CLK0_PAD}] \

[get_pins {RTG4FCCC_0.GL0}] create_generated_clock -name clk_200mhz -divide_by 12 -multiply_by 24 \

-source [get_pins {RTG4FCCC_0.CLK0_PAD}]\

[get_pins {RTG4FCCC_0.GL1}] create_generated_clock -name clk_25mhz -divide_by 2 \

-source [get_pins {RTG4FCCC_0.RCOSC_50MHZ}] \

[get_pins {RTG4FCCC_0.GL2}] create_generated_clock -name clk_100mhz -divide_by 1 -multiply_by 1 \

-source [get_pins {RTG4FCCC_0.CLK2_PADP}] \

[get_pins {RTG4FCCC_0.GL3}]

- RTG4 Fabric CCC Place and Route Constraints

Per SmartTime, i limiti per u configuratore CCC sò:

create_clock -name CLK0_PAD -period 20 [get_ports {CLK0_PAD}] create_clock -name CLK2_PADP -period 10 [get_ports {CLK2_PADP}] create_clock -name CLK3_PADP -period 10 [get_ports {CLK3_PADP}_clock_clock -_m_generatedk_clock

-divide_per 16 \

-multiplica_per 24 \

-source {RTG4FCCC_0/CCC_INST/INST_CCC_IP:CLK0_PAD} \

{RTG4FCCC_0/CCC_INST/INST_CCC_IP:GL0}

create_generated_clock -name clk_200mhz \

-divide_per 12 \

-multiplica_per 24 \

-source {RTG4FCCC_0/CCC_INST/INST_CCC_IP:CLK0_PAD} \

{RTG4FCCC_0/CCC_INST/INST_CCC_IP:GL1}

create_generated_clock -name clk_25mhz \

-divide_per 2 \

-source {RTG4FCCC_0/CCC_INST/INST_CCC_IP:RCOSC_50MHZ} \

{RTG4FCCC_0/CCC_INST/INST_CCC_IP:GL2}

create_generated_clock -name clk_100mhz \

-divide_per 1 \

-multiplica_per 1 \

-source {RTG4FCCC_0/CCC_INST/INST_CCC_IP:CLK2_PAD} \

{RTG4FCCC_0/CCC_INST/INST_CCC_IP:GL3}

Bloccu di l'interfaccia seriale à alta velocità (SERDES).

U bloccu di l'interfaccia seriale d'alta velocità o l'interfaccia serializer/deserializer (SERDESIF) integra parechji blocchi funzionali per sustene parechji protokolli seriali d'alta velocità in u FPGA. U bloccu SERDESIF hà e seguenti caratteristiche:

- Supportu di u protokollu di l'interconnessione di cumpunenti periferichi (PCIe-PCI Express®).

- Supportu di protokollu 10 Gigabit Attachment Unit Interface (XAUI).

- L'interfaccia di Sub-layer di codificazione fisica esterna (EPCS) supporta qualsiasi protokollu seriale d'alta velocità definitu da l'utilizatori, cum'è u supportu di protokollu seriale Gigabit media indipendenti (SGMII)

Modalità di funziunamentu di protocolu seriale unicu o duale. In i modi di protokollu seriale Dual, dui protokolli ponu esse implementati nantu à i quattru corsi fisichi di u bloccu SERDESIF Bloccu SERDESIF cumunicazioni à u tissu FPGA attraversu una interfaccia AXI / AHBL o interfaccia EPCS

- Modu di protocolu PCI Express

In questu modu, u bloccu SERDESIF cumunicà cù l'FPGA utilizendu l'interfaccia AXI / AHBL è l'interfaccia APB3 per a cunfigurazione; ùn ci hè micca bisognu di limitazioni specifiche à stu bloccu. - Modu di protocolu EPCS

In u modu EPCS, u SERDESIF pò sustene finu à quattru corsi. In u modu EPCS, u bloccu SERDESIF usa trè clock:- APB_S_PCLK per u bus di cunfigurazione APB3

- EPCS_0_RXFWF_RCLK per riceve l'interfaccia di tissu fifo volante di dati

- EPCS_0_TXFWF_WCLK per a trasmissione di dati di l'interfaccia di tissu fifo volante di mosca

L'orologio APB_S_PCLK, EPCS_0_RXFWF_RCLK è EPCS_0_TXFWF_WCLK deve esse definitu à a so fonte. Nisuna limitazione specifica à stu bloccu hè necessariu.

- Modu di protocolu XAUI

In u modu XAUI, u bloccu SERDESIF usa cinque clock:- REFCLK_P - Input per u TxPLL

- APB_S_CLK per u bus di cunfigurazione APB3

- XAUI_MMD_MDC cum'è u clock di l'interfaccia MDIO

- XAUI_RX_CLK_IN - I dati ricevuti sò sincronizati in u volante FIFO à questu clock

- XAUI_TX_CLK_OUT - Dati trasmessi hè sampguidatu cù un clock sincronizatu se a compensazione di clock hè attivata. XAUI_TX_CLK_OUT deve esse cunnessu à XAUI_FB_CLK per attivà a compensazione di u clock.

L'orologio REFCLK_P, APB_S_PCLK, XAUI_MMD_MDC è XAUI_RX_CLK_IN deve esse definitu à a so fonte.

L'orologio XAUI_TX_CLK_OUT pò esse definitu nantu à i porti di output GL0 / GL1 di u bloccu SERDESIF. L'exampu sottu crea questi clock per i blocchi NPSS è PCIE SERDES.

- Limitazioni di sintesi XAUI

- NPSS SERDES

create_clock -name { gl_clock1 } \

-periodu 6.400 \

[get_pins {NPSS_SERDES_IF_0.SERDESIF_INST.GL*}] - PCIE SERDES

create_clock -name { gl_clock2 } \

-periodu 6.400 \

[get_pins {PCIE_SERDES_IF_0.SERDESIF_INST.GL*}]

- NPSS SERDES

- XAUI Place and Route Constraints

- NPSS SERDES

create_clock -name { gl_clock1 } \

-periodu 6.400 \

[get_pins {NPSS_SERDES_IF_0/SERDESIF_INST/INST_NPSS_IP:GL*}] - PCIE SERDES

create_clock -name { gl_clock2 } \

-periodu 6.400 \

[get_pins {PCIE_SERDES_IF_0/SERDESIF_INST/INST_PCIE_IP:GL*}

- NPSS SERDES

Supportu di u produttu

Microsemi SoC Products Group sustene i so prudutti cù diversi servizii di supportu, cumpresu u Serviziu Clienti, u Centru di Supportu Tecnicu di Clienti, un websitu, posta elettronica, è uffizii di vendita in u mondu. Questu appendice cuntene infurmazioni nantu à cuntattà u Gruppu di Prodotti Microsemi SoC è l'usu di sti servizii di supportu.

Serviziu à i clienti

Cuntattate u Serviziu Clienti per un supportu di produttu micca tecnicu, cum'è u prezzu di u produttu, l'aghjurnamenti di u produttu, l'infurmazioni di l'aghjurnamentu, u statu di l'ordine è l'autorizazione.

- Da l'America di u Nordu, chjamate 800.262.1060

- Da u restu di u mondu, chjamate 650.318.4460

- Fax, da ogni locu in u mondu, 408.643.6913

Centru di Assistenza Tecnica di Clienti

Microsemi SoC Products Group furnisce u so Centru di Supportu Tecnicu à i Clienti cù ingegneri altamente qualificati chì ponu aiutà à risponde à e vostre dumande di hardware, software è cuncepimentu nantu à i Prodotti Microsemi SoC. U Centru di Assistenza Tecnica di u Cliente passa assai tempu per creà note d'applicazione, risposte à e dumande cumuni di u ciclu di cuncepimentu, documentazione di prublemi cunnisciuti è diverse FAQ. Allora, prima di cuntattateci, visitate e nostre risorse in linea. Hè assai prubabile chì avemu digià rispostu à e vostre dumande.

Assistenza tecnica

Visita l'Assistenza Clienti websitu (www.microsemi.com/soc/support/search/default.aspx) per più infurmazione è supportu. Parechje risposte dispunibili nantu à u searchable web risorsa include diagrammi, illustrazioni, è ligami à altre risorse nantu à u websitu.

Websitu

Pudete cercà una varietà di infurmazioni tecniche è micca tecniche nantu à a pagina principale di SoC, à www.microsemi.com/soc.

Cuntattate u Centru di Assistenza Tecnica di Clienti

Ingegneri altamente qualificati stanu u Centru di Supportu Tecnicu. U Centru di Supportu Tecnicu pò esse cuntattatu per email o attraversu u Gruppu di Prodotti Microsemi SoC websitu.

E-mail

Pudete cumunicà e vostre dumande tecniche à u nostru indirizzu email è riceve risposte per email, fax, o telefunu. Inoltre, se avete prublemi di disignu, pudete email u vostru disignu files per riceve assistenza. Monitoremu constantemente u contu di email in tuttu u ghjornu. Quandu ci mandendu a vostra dumanda, assicuratevi di includere u vostru nome cumpletu, u nome di a cumpagnia, è a vostra infurmazione di cuntattu per un trattamentu efficace di a vostra dumanda.

L'indirizzu email di supportu tecnicu hè soc_tech@microsemi.com.

I mo casi

I clienti di Microsemi SoC Products Group ponu invià è seguità casi tecnichi in linea andendu à I mo casi.

Fora di i Stati Uniti

I clienti chì necessitanu assistenza fora di i fusi orari di i Stati Uniti ponu cuntattà l'assistenza tecnica per email (soc_tech@microsemi.com) o cuntattate un uffiziu di vendita lucale. L'elenco di l'uffizii di vendita ponu esse truvati à www.microsemi.com/soc/company/contact/default.aspx.

Assistenza tecnica ITAR

Per supportu tecnicu nantu à FPGA RH è RT chì sò regulati da u Regolamentu Internaziunale di Traffic in Arms (ITAR), cuntattateci via soc_tech_itar@microsemi.com. In alternativa, in I miei casi, selezziunate Sì in a lista a tendina ITAR. Per una lista completa di Microsemi FPGA regulati da ITAR, visitate l'ITAR web pagina.

Microsemi Corporation (Nasdaq: MSCC) offre una cartera cumpleta di soluzioni di semiconduttori è sistemi per i mercati di cumunicazione, difesa è sicurità, aerospaziale è industriale. I prudutti includenu circuiti integrati di signali misti analogici d'alta prestazione è radiazioni, FPGA, SoC è ASIC; prudutti di gestione di energia; i dispusitivi di timing è di sincronizazione è suluzione di u tempu precisu, chì stabiliscenu u standard di u mondu per u tempu; dispusitivi di trasfurmazioni di voce; suluzione RF; cumpunenti discreti; tecnulugia di sicurità è scalable anti-tampi prudutti; Power-over-Ethernet IC è midspans; cume capacità è servizii di cuncepimentu persunalizati. Microsemi hà a sede in Aliso Viejo, California è hà circa 3,400 impiegati in u mondu. Sapete più à www.microsemi.com.

Sede centrale di Microsemi

One Enterprise, Aliso Viejo CA 92656 USA

Dentru i Stati Uniti: +1 800-713-4113

Fora di i Stati Uniti: +1 949-380-6100

Vendite: +1 949-380-6136

Fax: +1 949-215-4996

E-mail: sales.support@microsemi.com

©2015 Microsemi Corporation. Tutti i diritti riservati. Microsemi è u logu Microsemi sò marchi di cummerciale di

Microsemi Corporation. Tutti l'altri marchi è marchi di serviziu sò a pruprietà di i so rispettivi pruprietarii.

Documenti / Risorse

|

Limitazioni di timing Microsemi RTG4 FPGA [pdfGuida di l'utente RTG4 FPGA Limitazioni di timing, RTG4 FPGA, Limitazioni di timing, Limitazioni |