Microsemi RTG4 FPGA 时序约束

产品信息

RTG4 FPGA 时序约束用户指南提供了使用 SDC 命令将时序约束应用于特定设计对象的详细信息。其中包括对象访问、显式与隐式对象规范、通配符、层次结构和引脚分隔符、总线命名约定以及添加注释的说明。

规格

- 产品名称: RTG4 FPGA

- 用户指南: 时间约束用户指南

产品使用说明

对象访问

要将时序约束应用于设计对象:

- 根据对象类型使用 get_cells、get_clocks、get_nets、get_pins、get_ports、all_inputs、all_outputs、all_registers 等命令。

- 有关更多详细信息,请参阅 SmartTime 在线帮助。

显式与隐式规范

SDC 支持隐式和显式对象指定:

- 隐式指定是指工具通过搜索对象来确定对象类型。

- 明确指定涉及使用嵌套对象访问命令指定对象类型以避免歧义。

外卡角色

在 SDC 命令中使用通配符:

- (反斜杠)按字面意思解释下一个字符。

- *(星号)匹配任何字符串。

介绍

在设计 FPGA 同步数字设计时,从设计输入到物理实现,如果不进行迭代,很少能达到设计所需的时序性能。通常必须经过设计周期的多次迭代 — HDL 设计捕获、综合、物理实现(布局布线)和时序分析 — 才能实现时序收敛。设置时序约束和执行时序分析是设计迭代中实现时序收敛的两个最重要步骤。对于 RTG4 设计,Microsemi 建议为综合和布局布线步骤设置时序约束。必须首先设置时序断言约束;请参阅第 5 页上的“时序断言”。如果在第一次迭代中未满足时序性能,请考虑在第二次及后续迭代中设置更多更高级的时序约束。请参阅第 6 页上的“时序例外”。

使用 Synopsys 设计约束

Synopsys® 设计约束 (SDC) 是一种基于 Tcl 的格式,Synopsys 工具使用它来指定设计意图和时序约束。Microsemi 支持使用 SDC 格式的变体进行约束管理。

为 RTG4 设计创建 SDC 约束时,可以使用以下类型的 SDC 命令:

- 对象访问

- 时间断言

- 时序例外

对象访问

SDC 时序约束适用于特定设计对象。表 1-1 总结了 SmartTime(Microsemi 静态时序分析工具与布局布线工具结合使用)支持的对象访问命令。有关详细信息,请参阅 SmartTime 在线帮助。

表 1-1 SmartTime 支持的对象访问命令

| 设计对象 | 命令 |

| 单元/实例 | 获取单元格 |

| 时钟 | 获取时钟 |

| 网 | 获取网络 |

| 别针 | 获取引脚 |

| 端口 | 获取端口、所有输入、所有输出 |

| 寄存器 | 所有寄存器 |

隐式规范与显式规范

一般而言,SDC 命令包含设计对象作为参数。SDC 支持隐式和显式对象规范。

当工具通过搜索对象来确定对象类型时,这称为隐式对象指定。当使用嵌套对象访问命令指定对象类型(以避免歧义)时,这称为显式对象指定。

例如amp乐: 如果您有一个名为“my_net1”的网络,则隐式规范为 my_net1,显式规范为 [get_nets my_net1]。

并非所有设计对象都适用于所有 SDC 命令。每个 SDC 命令都接受一组预定义的设计对象作为参数。Microsemi 建议您使用显式对象规范方法来避免对象类型的歧义。如果在搜索隐式规范后返回多个对象类型,则根据工具的优先级对象列表对对象类型进行优先排序。

有关详细信息,请参阅 SmartTime 在线帮助。

外卡角色

表 1-2 列出了 SDC 命令中可用的通配符。

表 1-2 SmartTime 支持的对象访问命令

| 外卡 | 功能 |

| \ | 按字面意思解释下一个字符 |

| * | 匹配任意字符串 |

笔记: 匹配功能要求您在引脚名称中的每个斜杠前添加反斜杠 (\),以防斜杠不能表示设计中的层次结构。

层次结构和引脚分隔符

Synplify Pro 软件默认使用“.”(句点)作为时序约束的层次结构和引脚分隔符。

例如amp乐: [get_pins {top_level.blockA.instance123.my_pin}] 要将层次结构分隔符从默认的“。” (句点) 更改为“/”(正斜杠),请使用以下命令:set_hierarchy_separator { / }

SmartTime 软件默认使用‘/’作为设计层次分隔符,使用“:”作为引脚分隔符。

例如amp乐: [get_pins {top_level/blockA/instance123:my_pin}] 请注意,“/”是层次结构分隔符,用于指示“instance123”存在于 top_level 'blockA 下方的设计层次结构中。“:”引脚分隔符标识“instance123”上的“my_pin”。

总线命名约定

SDC 内的所有公交车 file 必须使用 Verilog 风格的命名约定 name[index]。

例如amp乐: [get_ports addr_bus_out[1]] 如果要指定对整个总线的约束,可以使用[get_port addr_bus_out]。

评论

您可以向 SDC 添加评论 file 在注释行前加上井号 (#)。

# 这是注释行

时间断言

时序断言旨在捕获您的设计时序要求。它们包括以下 SDC 命令:

- 时钟周期/频率

- 创建时钟

- 创建生成的时钟

- 输入/输出延迟

- 设置输入延迟

- 设置输出延迟

- 设置外部检查

- 设置时钟到输出

- 时钟间不确定性

- 设置时钟不确定性

- 时钟源延迟

- 设置时钟延迟

有关时序断言 SDC 命令 Synplify Pro 和 SmartTime 支持,请参阅第 7 页上的“时序约束和设计流程”。

时序例外

使用时序异常来识别需要覆盖默认单周期时序关系的设计路径。时序异常的 SDC 命令包括:

- 错误路径

- 设置假路径

- 多循环路径

- 设置多周期路径

- 最大延迟路径

- 设置最大延迟

- 最小延迟路径

- 设置最小延迟

- 已禁用时序弧

- 设置禁用定时

时间例外和优先顺序

当同一时序路径具有多个时序异常约束时,SmartTime 将遵循具有最高优先级的时序约束,并根据表 1-3 中所示的优先级顺序忽略其他时序异常。Synplify Pro 将根据表 1-4 中的优先级顺序遵循时序约束。

表 1-3 时间例外 – SmartTime 的优先顺序

| 时序例外 | 优先顺序 |

| 设置禁用定时 | 1 |

| 设置假路径 | 2 |

| 设置最大延迟/设置最小延迟 | 3 |

| 设置多周期路径 | 4 |

表 1-4 时序例外 – Synplify Pro 的优先顺序

| 时序例外 | 优先顺序 |

| 设置假路径 | 1 |

| 设置最大延迟/设置最小延迟 | 2 |

| 设置多周期路径 | 3 |

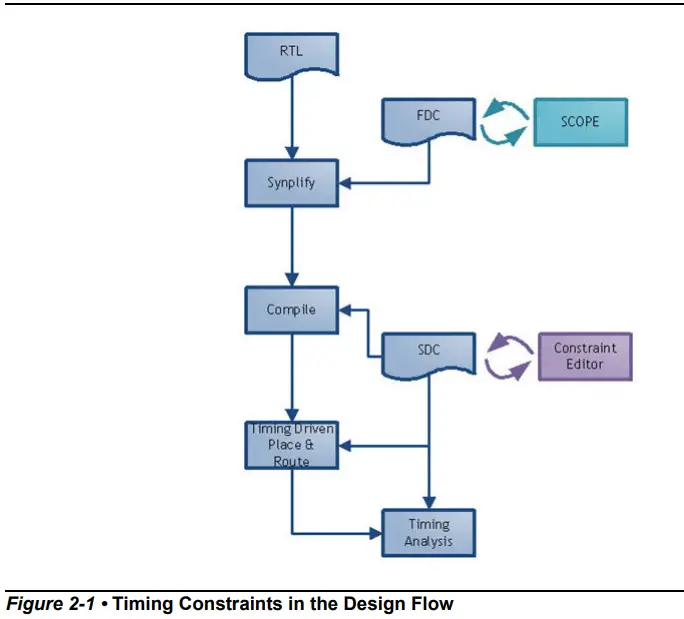

时序约束和设计流程

本章介绍在 Libero 设计流程中指定时序约束和执行时序分析的位置(图 2-1)。Microsemi 建议您为 Synplify Pro 和 SmartTime 提供充分且完整的时序约束。此外,您必须重新view Synplify Pro 和 SmartTime 的时序报告确保设计得到适当约束并且满足时序目标。

Libero 工具(时序驱动布局布线和 SmartTime)支持与 FPGA 设计相关的 Synopsys SDC 时序约束子集。

Microsemi 建议您在 Libero 流程中创建两组时序约束:

- 使用 Synplify Pro 进行综合的 FDC 时序约束。

- Libero Timing Driven Place and Route 和 SmartTime 阶段的 SDC 时序约束。

Synplify Pro 的时间约束

- 超过view

Synplify Pro 支持 FPGA 设计约束 (FDC) 格式。FDC 格式包括:- Synopsys SDC 标准的一个子集,用于时序约束

- Synplify Pro 支持的传统时序约束格式

您可以通过以下方式为 Synplify Pro 提供时序约束: - 导入时间约束 file(s)进入 Libero 项目。确定时间约束 file(s)将传递到 Libero GUI 中的 Synplify Pro。右键单击 file(s)并选择用于综合。有关在 Libero GUI 中导入时序约束的详细信息,请参阅 Libero 在线帮助。

- 使用 Synplify Pro 软件中的 SCOPE(综合约束优化环境)GUI 创建时序约束。使用 SCOPE 创建的约束保存到约束 file 使用FDC格式。

- 支持的 Synplify Pro 时序约束

Synplify Pro 支持针对 FPGA 综合的以下时序约束:- 创建时钟

- 创建生成的时钟

- 设置输入延迟

- 设置输出延迟

- 设置假路径

- 设置多周期路径

- 设置最大延迟

- 设置时钟延迟

- 设置时钟不确定性

有关选项和参数的详细信息,请参阅 Synplify Pro for Microsemi 参考手册。

- 设计要求的约束

综合软件使用时序约束进行权衡,从而以最佳方式利用资源,实现所需的时序目标。时序约束对于确保综合工具在执行设计的逻辑和映射优化时做出正确选择至关重要。

Microsemi 建议您包括时钟约束和输入和输出延迟约束。

时钟约束有两种类型:- 创建时钟

- 创建生成的时钟

要定义 RTG4 设计的设计时钟: - 使用 create_clock 约束来识别和约束用作时钟的振荡器和主输入端口。

- 使用 create_generated_clock 约束来识别和约束用作时钟的结构 CCC 输出引脚。

- FDC防爆amp使用 create_clock 和 create_generated_clock

在前amp下面的 create_clock 和 create_generated_clock 约束的组合用于定义所需的时钟约束。

首先,时钟源被确定为50MHz的输入端口clk_in。

然后该时钟源通过CCC生成200MHz时钟(clk_core):

笔记: 反斜杠“\”字符是 Tcl 语法的一部分。它将一条较长的命令拆分为多行。

笔记: Synplify Pro 软件默认使用 '.'(句点)作为时序约束的层次分隔符。使用 FDC 中的 set_hierarchy_separator 命令 file 重新定义层次结构分隔符。例如ample:设置层次结构分隔符

divide_by 和 multiply_by 因子来自结构 CCC 配置器“高级”选项卡上显示的 PLL 图。Synplify Pro 软件默认所有缺少时序约束的时钟所需时钟频率为 100 MHz。 - FDC防爆amp使用 set_input_delay 和 set_output_delay

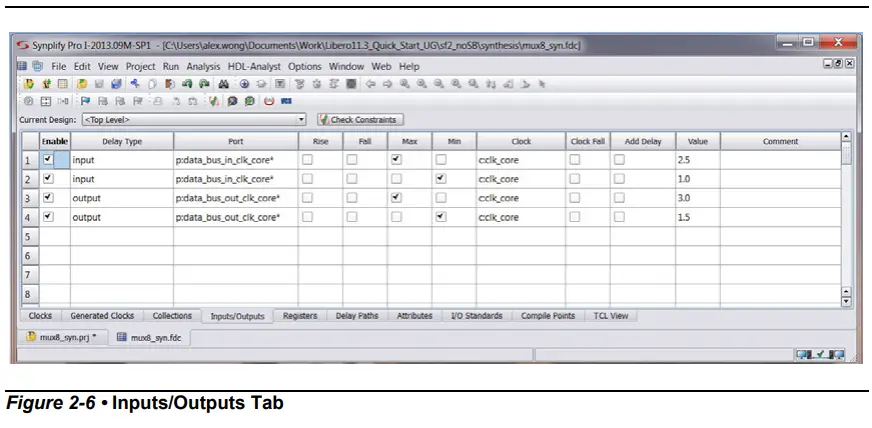

在此例中ample、set_input_delay 和 set_output_delay 约束用于定义所需的输入和输出延迟时序约束。这些约束是定义 I/O 接口所需的时序预算所必需的。

在此例中ample,所有约束都使用上一个ex中的clk_coreample作为参考时钟。

输入端口 data_bus_in_clk_core 上的输入延迟为 2.5ns(最大值)和 1.0ns(最小值)。

输出端口 data_bus_out_clk_core 上的输出延迟为 3.0ns(最大值)和 1.5ns(最小值)。

# 输入延迟

设置输入延迟-时钟[获取时钟clk_core] \

-最大 2.5 \

[获取端口 {data_bus_in_clk_core*}] 设置输入延迟 -时钟 [获取时钟 clk_core] \

-最小 1.0 \

[get_ports {data_bus_in_clk_core*}] # 输出延迟

设置输出延迟-时钟[获取时钟clk_core]\

-最大 3.0 \

[获取端口 {data_bus_out_clk_core*}] 设置输出延迟 -时钟 [获取时钟 clk_core] \

-最小 1.5 \

[获取端口 {数据总线输出时钟核心*}] - 约束检查器

Microsemi 建议您在导入或创建 FDC 或时序约束后对其进行验证。如果时序约束 file 是进口的。

Synplify Pro 提供了一个约束检查器实用程序,您可以使用它来验证 SDC 时序约束。约束检查器可从 Synplify Pro GUI 内的项目菜单(运行 > 约束检查)访问。它会生成一个约束检查报告 (*_cck.rpt),其中包含有关时序约束问题的详细信息。摘要部分应表明未发现时序约束问题。

使用约束检查器报告来修复与不正确的语法或对象名称相关的错误。

有关 Synplify Pro Constraint Checker 的详细信息,请参阅 Synplify Pro for Microsemi 用户指南。 - 优化设计的约束

检查完时序约束后,Microsemi 建议您使用 Synplify Pro 中的时序分析功能来确定是否已提供所有必需的设计约束。您可以使用时序报告中的违规设计路径列表来识别任何缺失或不准确的时序约束。

笔记: 由于设计尚未布局,时序报告使用基于线路负载模型的估计值来计算网络延迟。这就是此时时序违规的原因tage 可能会或可能不会出现在布局布线之后。

Microsemi 建议您先完成整个设计流程(包括时序驱动布局布线),然后再添加时序例外进行综合。然后,您可以使用更准确的布局布线后时序分析报告来确定所需的约束。

时钟、输入和输出延迟约束是所有设计所需的最小时序约束集。某些设计可能需要额外的时序约束,称为时序例外。例如amp乐:- 错误路径(set_false_path),

- 多周期路径(set_multicycle_path)

- 最大路径延迟(set_max_delay)

您可以使用时序例外来识别需要覆盖默认单周期时序关系的设计路径。您必须通过识别以下设计路径来指导综合工具优化: - 没有时序关系(set_false_path)

- 具有非单个周期的时序关系(set_multicycle_path 或 set_max_delay)

- 优先级

当多个时序例外应用于同一设计对象时,为了解决时序约束冲突,应遵循以下优先规则:

set_disable_timing 优先于所有其他时序异常约束。

错误路径约束优先于最大路径延迟/最小路径延迟或多周期路径约束。

最大路径延迟/最小路径延迟约束优先于多周期路径约束。

表 2-1 SmartTime 支持的对象访问命令时间例外 优先顺序 设置禁用定时 1 设置假路径 2 设置最大延迟 / 设置最小延迟 3 设置多周期路径 4 - 优化时序与面积

当您运行 Synplify Pro 综合时,该工具首先编译设计,然后将其映射到 Microsemi 技术单元。

默认情况下,Synplify Pro 会自动在面积和时序性能之间进行有效权衡,以实现最佳结果。但是,您可以引导 Synplify Pro 以牺牲面积为代价来优化设计以获得时序性能。相反,您可以引导 Synplify Pro 以牺牲时序性能为代价来优化设计以获得面积。

一般而言,优化时序性能会消耗更多 FPGA 资源(面积),而优化面积通常意味着更大的延迟(较弱的时序性能)。您必须权衡时序性能需求与面积需求,以确定哪种方案最适合您的设计。

有关优化选项的更多信息,请参阅 Synplify Pro for Microsemi 用户指南的第 10 章。 - 使用 Synplify Pro 进行综合后时序分析

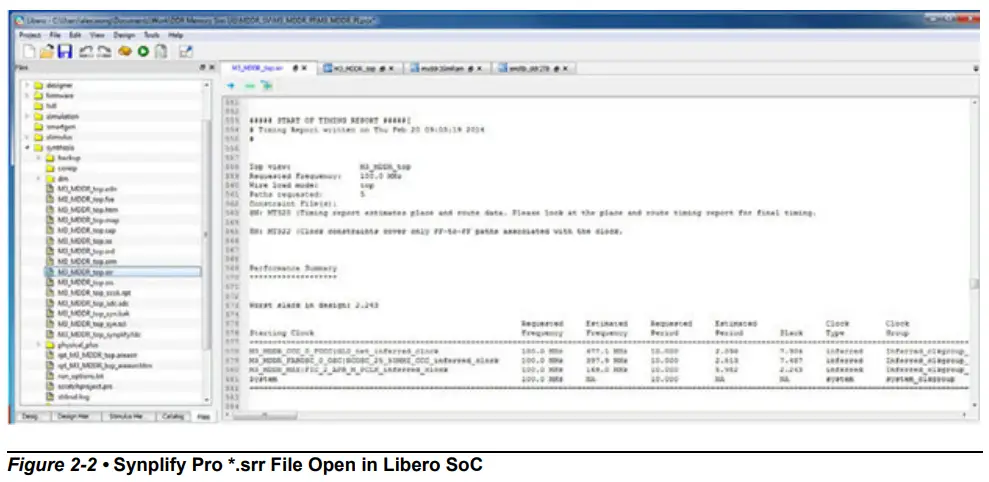

Synplify Pro 在综合完成后生成时序报告。运行综合后,单击 View 日志按钮打开日志 file 在 Synplify Pro 中。

综合日志 file 也可以从 Libero SoC 的“报告”窗格中的“合成”下获得。

这 file 位于综合目录下,扩展名为 *.srr, viewLibero SoC 中可用。单击 File Libero SoC 项目中的 Synthesis 选项卡。展开 Synthesis file 组。双击 *.srr file 在 Libero SoC 编辑器中打开它 View 窗格。向下滚动到标题为“时序报告开始”的部分(图 2-2)。

Synplify Pro 时序报告分为以下几个部分:- 表现摘要

- 时钟关系

- 接口信息

- 时钟详细报告

使用综合时序报告确认: - 约束正在按预期被选取和应用。

- 该设计没有任何重大的时序违规

由于设计尚未布局,综合时序报告使用线路负载模型估算网络延迟。但是,时序报告中使用的单元延迟是准确的。

如果路径延迟(不包括网络延迟)超过所需时间,则可认为设置时序违规严重。这通常表明时序要求不切实际,或者设计路径需要额外的流水线。无论哪种情况,单元延迟超过所需时间的设计路径在布局和布线后都不太可能满足时序目标。

- 时序例外

如果综合后时序分析报告设计不符合时钟速度或 I/O 延迟的时序规范,Microsemi 建议您使用时序异常来帮助综合。

Microsemi 建议您先完成整个设计流程,包括时序驱动布局布线,然后再添加时序例外以供综合。然后,您可以使用更准确的布局布线后时序分析报告来确定所需的约束。使用虚假路径时序约束来识别不传播逻辑级变化且不应在时序分析期间考虑的特定设计路径。综合工具会忽略使用此约束识别的设计路径,以进行逻辑和映射优化。使用多周期路径、虚假路径和最大路径延迟时序约束来识别具有与默认单周期关系不同的时序关系的设计路径。综合工具将使用新关系进行优化。

多周期路径和伪路径约束通常会导致放宽原始单时钟周期时序要求。最大路径延迟约束可以根据用户指定的时间值放宽或收紧原始时序要求。

FDC防爆amp莱斯

# 错误路径

set_false_path -from [get_ports uart_ctrl] # 最大路径延迟

设置最大延迟 - 至 [获取端口 {ram_rd_enable}] 4.0

# 多周期路径

设置多周期路径 4 -to [获取端口 {I2C*}]

范围和使用前向注释的 SDC

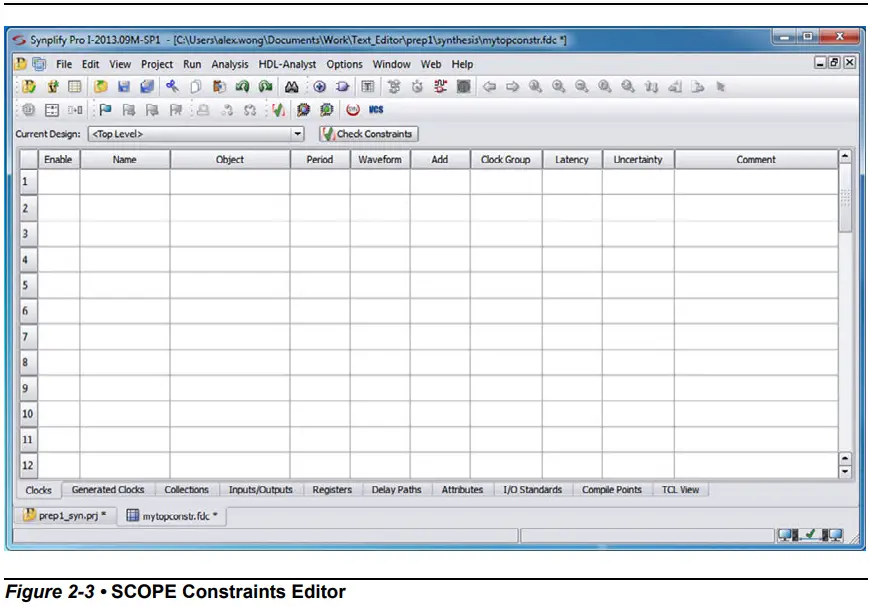

您可以使用 Synplify Pro 中的 SCOPE 输入综合步骤的约束。综合后,Synplify Pro 会生成一个 *_sdc.sdc file,其中包含正向注释的时序约束。有关详细信息,请参阅第 15 页上的“使用正向注释的 SDC”。建议的流程是为综合和时序驱动的布局和布线步骤创建单独的约束。

- 使用 SCOPE 输入时序约束

SCOPE 是 Synplify Pro 提供的编辑器,用于输入和管理时序约束和综合属性(图 2-3)。

大多数设计中常见的三种约束类型是:- 时钟约束 – 所有同步设计都是由某种时钟驱动的。如果没有时钟约束,诸如建立时间和保持时间违规之类的时序违规都是毫无意义的。

- 输入和输出延迟约束 – 输入和输出延迟考虑了 FPGA 外部的路径延迟。这些约束是延迟预算要求的一部分。

- 例外情况 – 当设计无法满足时序要求时,您可能需要更高级的约束以使设计达到时序收敛。当应用于设计中的特定路径时,这些时序例外将覆盖 Synplify Pro 在优化过程中考虑这些时序路径时的默认行为。

在输入任何约束之前,首先在 Synplify Pro 中编译设计(运行 > 仅编译)。在 Synplify Pro 中执行编译会预先用对象名称填充 SCOPE。这可以节省您输入对象名称的时间和精力。

- SCOPE 和 FDC 支持的前缀标识符

Synplify Pro 使用下表中定义的对象标识符来定义在 SCOPE 或 FDC 中的约束 file(表2-2)。

表 2-2 前缀标识符和设计对象前缀标识符 (FDC) SDC 等效 设计应用对象 v: 设计名称 无 模块 c: 时钟名称 获取时钟 时钟 i: 实例名称 获取单元格 实例 p: 端口名称 获取端口 端口 t: 引脚名称 获取引脚 实例化单元的分层端口或引脚 b: 总线名称 获取引脚 公交车零件 n: 网络名称 获取网络 网络名称 - 时钟约束

时钟约束有两种类型:create_clock 和 create_generated_clock。SCOPE 针对这两种约束提供了两个单独的选项卡。

使用“Clocks”选项卡来识别时钟源(create_clock)。参考图 2-4。

使用 Generated Clocks 选项卡来识别设计中的生成时钟 (create_generated_clock)。参考图 2-5。

对于 RTG4 设计:- 振荡器或时钟输入端口是典型的时钟源。

- 结构 CCC 输出是典型的生成时钟。

Synplify Pro 支持高级复制和粘贴功能。可以从原理图复制对象 view并将其名称粘贴到 SCOPE 中。

例如amp乐: 突出显示振荡器的输出端子引脚(在 RTL view 原理图),复制(CTRL + C)然后粘贴(CTRL + V)到 SCOPE 中。

- I/O 延迟约束

时钟约束不足以约束 I/O 端口。使用输入和输出延迟约束

(set_input_delay、set_output_delay)约束指定 I/O 约束。导航至 SCOPE 中的“输入/输出”选项卡即可执行此操作(图 2-6)。

- 约束检查器

要检查迄今为止输入的约束,请单击菜单栏上的“检查约束”按钮。Synplify Pro 会生成时钟约束检查报告 (*_cck.rpt)。摘要应表明未发现时序约束方面的问题。

还可以从项目菜单(项目 > 运行 > 约束检查)访问约束检查器。 - 例外

一些设计需要额外的时序约束(称为时序例外),例如:- 设置假路径

- 设置最大延迟

- 设置多周期路径

要在 SCOPE 中输入时序例外,请导航至“Delay Paths”选项卡。保存后 file,从 File 菜单选择“关闭”返回项目 view.

- 使用前向注释的 SDC

综合后,Synplify Pro 生成 SDC file 您可以使用它来完成 Libero 流程的剩余步骤。这 file (扩展名为 *_sdc.sdc)可在 Libero 项目的 Timing Constraints 下找到 view.

默认情况下,这 file Libero 不使用。建议的流程是为综合和时序驱动布局和布线步骤创建单独的约束。

用户必须重新view 这 file Synplify 生成的前向注释的内容 file 在启用 file 实现。要启用 SDC file 对于时序驱动布局布线,右键单击 file 并选择用于编译。Libero 使用此 SDC file 对于设计流程中的剩余步骤,从编译开始。 - 限制

- 前向注释的 SDC file Synplify Pro 不包含原始用户 SDC 中存在的任何 set_clock_latency 约束 file.

- Synplify Pro 不会自动为振荡器或 CCC 实例生成时钟约束。您必须向 Synplify Pro 提供准确的时钟约束(create_clock、create_generated_clock)。然后这些约束在 *_sdc.sdc 中被前向注释 file.

时序驱动布局布线的时序约束

Libero 工具(时序驱动布局布线和 SmartTime)支持与 FPGA 设计相关的 Synopsys SDC 时序约束子集。要设置时序约束,您可以使用:

- SmartTime 约束向导

- SmartTime 约束编辑器

- 南达科他州 file(編號)

组织时间约束 files,使用“组织约束 Files”对话框。导入 SDC 时 file 对于时序驱动布局布线,请确保将其包括在编译工具中以供使用。要启用 SDC file 已导入 Libero,右键单击 file 并选择用于编译(参见图2-7)。

- 时序驱动布局和布线约束

SmartTime 时序分析支持以下一组 SDC 时序约束:- 创建时钟

- 创建生成的时钟

- 设置输入延迟

- 设置输出延迟

- 设置外部时钟

- 设置时钟到输出

- 设置假路径

- 设置多周期路径

- 设置最大延迟

- 设置最小延迟

- 设置时钟延迟

- 设置时钟不确定性

- 设置禁用定时

有关 SDC 命令的选项和参数的详细信息,请参阅 SmartTime 在线帮助。

- 设计要求的约束

Microsemi 建议您使用以下流程输入时序约束:- SmartTime 约束向导 – 识别时钟、输入和输出延迟约束

- I/O 属性编辑器 – 为设计提供完整的 I/O 属性信息

- 生成并分析约束覆盖率报告

- SmartTime 约束向导

SmartTime 包含一个约束向导,可以快速轻松地输入时钟和 I/O 约束(图 2-8)。

从 SmartTime 调用约束向导(工具 > 约束向导)。约束向导允许您按以下顺序添加约束:- 总体时钟约束

- 总体 I/O 限制

- 特定时钟限制

- 生成时钟约束

- 特定输入约束

- 具体产出约束

使用整体约束选项卡设置时钟和 I/O 的默认约束。

时钟和 I/O 的特定约束可以覆盖默认约束。

- 时钟约束

使用特定时钟和生成的时钟约束选项卡可以完成以下任务:- 振荡器用作时钟源。

- 结构 CCC 输出用作生成时钟

- 其他来源的时钟

- I/O 约束

使用“总体 I/O 约束”选项卡设置设计中所有输入和输出端口的默认约束。可以在“特定输入”和“特定输出约束”选项卡中覆盖所选端口的默认 I/O 约束。

有关约束向导的详细信息,请参阅 SmartTime 在线帮助。 - I/O 属性和 I/O 属性编辑器

I/O 路径的时序性能受到 I/O 属性的显著影响。

使用多输入/输出属性编辑器功能View 导航器(MVN)工具为设计提供完整的I/O属性信息。

有关 I/O 属性编辑器的详细信息,请参阅多View 导航器在线帮助。 - 约束覆盖

生成约束覆盖率报告(图 2-9)非常重要,因为时序报告仅分析具有时序约束的设计路径的时序性能。没有时序约束的时序路径可能存在时序违规,因此不会被报告。从 SmartTime Analyzer 调用约束覆盖率报告(工具 > 报告 > 约束覆盖率)。

缺少约束的设计路径或对象列在增强建议下。view 每个建议并提供适当的约束,以确保所有设计路径都有时序约束。

有关约束覆盖率报告的详细信息,请参阅 SmartTime 在线帮助。 - 优化设计的约束

如果设计未能满足时序要求,即使完成了时序驱动布局布线 (TPDR),也可能需要优化设计时序约束。

优化设计约束的推荐流程是:- 运行时序驱动布局布线。确保在布局布线过程中启用了时序驱动选项。

- 生成并检查时序分析报告。分析最大和最小延迟分析报告。

- 打开 SmartTime Constraints Editor 并提供额外的约束,包括时间例外。

- 为了提高 Placer 性能:

- 调试时序违规的设计路径。

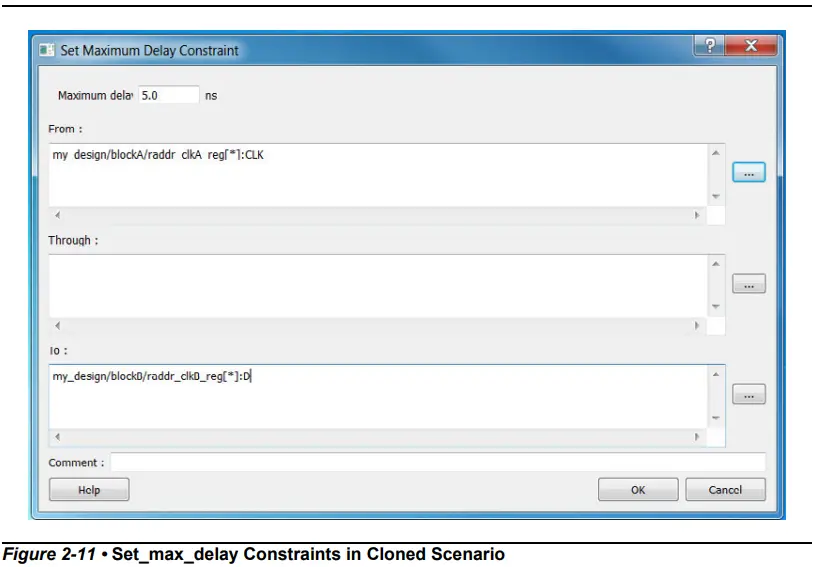

- 使用set_max_delay来约束时钟域间路径。

- 使用时序驱动布局布线 (TDPR)

TDPR 的主要目标是满足时序约束。如果您不选择 Timing-driven 选项,则 Place and Route 将不考虑时序约束。

确保在运行 Place and Route 之前选择了 Timing-driven(右键单击 Place and Route 并选择 Libero 工具套件中的 Configure Options)。RTG4 默认选择此选项。 - 时序分析报告

SmartTime 默认为最大和最小延迟分析生成两种类型的时序报告:-

- 时序报告——此报告显示按时钟域组织的时序信息。

- 时序违规报告 – 此平面余量报告提供有关约束违规的信息。要在 Libero 中生成时序分析报告,请右键单击“验证时序”并选择“运行”。

- 时序报告内容

时序报告包含以下部分:- 标题——列出报告类型、版本、报告日期和时间以及一般设计信息

- 摘要——报告每个时钟域的时序信息

- Path Selections – 列出设计中不同类型路径的时序信息。有关详细信息,请参阅 SmartTime 在线帮助。

- 时序违规报告内容

时序违规报告包含以下部分: - 标头

标题列出:- 报告类型

- 用于生成报告的 SmartTime 版本

- 报告生成的日期和时间

- 一般设计信息(姓名、家族等)

- 路径

路径部分列出了设计中违反路径的时序信息。

默认情况下,slack 阈值为 0,路径数量受限。默认报告的最大路径数量为 100。

本报告中混合了所有时钟域。路径按递减顺序列出。

-

- SmartTime 约束编辑器

SmartTime 约束编辑器是一款可以让你创建、 view 并编辑所有设计时序约束。通过约束向导或 SDC 提供的约束 file可以在 SmartTime Constraints Editor 中编辑。

使用约束向导可轻松为时钟和 I/O 端口提供基本时序约束。对于时序异常等高级时序约束,请使用约束编辑器。- 时序例外

根据设计的复杂性,可能需要时序例外。时序例外是在设计中的特定路径上设置的时序约束。例如amp乐:- 设置假路径

- 设置最大延迟

- 设置多周期路径

提供这些约束需要了解设计中的数据路径及其时序要求。默认情况下,SmartTime 使用单个时钟周期来分析任何设置了时钟约束的时序路径。时序异常用于覆盖设计路径的默认时钟约束。

有关时间异常的详细信息,请参阅 SmartTime 在线帮助。

笔记: 根据时序违规的严重程度,可能还需要向综合软件提供时序异常约束。要向综合软件提供时序异常约束,请将这些约束包含在 FDC 中 file 提供给 Synplify Pro。

- 时序例外

提高铺放机性能

当设计未能满足时序目标时,必须仔细分析失败的设计路径。需要分析两个问题:

- 如果修改实例放置,是否可以改善失败路径的时序性能?

存在设置违规的设计路径的长布线延迟可能表明实例布局不是最佳的。可以使用“Chip Planner”工具检查设计路径布局,该工具是 MultiView 航海家。 - 时序约束是否足以让布局人员识别并处理设计中的真正关键路径?

确保创建完整的时序约束集并将其传递给布局工具。使用 set_max_delay 约束来正确约束时钟域间设计路径。以下部分详细介绍了传递约束和使用 set_max_delay 约束。

- 布局器性能 – 支持的约束

您可以通过以下方式将时序约束传递给 Placer:- 组织时间约束 file使用组织约束 Files 对话框。导入 SDC 时 file 对于布局器,请确保将其包括在编译工具中以供使用。要启用 SDC file 已导入 Libero,右键单击 file 并选择用于编译。

- 在 SmartTime GUI 中输入约束 - 如果使用场景,请确保该场景已为 TDPR 启用。

- 限制

- 布局器当前支持以下约束:

- 创建时钟

- 创建生成的时钟

- 设置时钟延迟

- 设置输入延迟

- 设置输出延迟

- 设置最大延迟

- 设置假路径

- 布局器不支持以下约束:

- 设置时钟不确定性

- 设置多周期路径

- 设置最小延迟

- 布局器不支持时钟域间时序。布局器优化其域内的时钟,但不优化域之间的时钟。要启用时钟域间路径的布局器优化,请使用 set_max_delay 约束。这将在下一节中描述。

- 当使用 set_max_delay 约束时,布局器不会将时钟生成路径纳入到达/需要时间计算中。

- 布局器当前支持以下约束:

- 使用 set_max_delay 来改善布局结果

通过在存在时序违规的设计路径上使用 set_max_delay 时序约束,可以改善布局器结果。如果违规路径如下,请考虑使用此方法:-

- 是一条跨时钟域的路径。

- 包含起点和终点之间明显不同的时钟生成延迟。

- 要为布局器添加额外的时序约束:

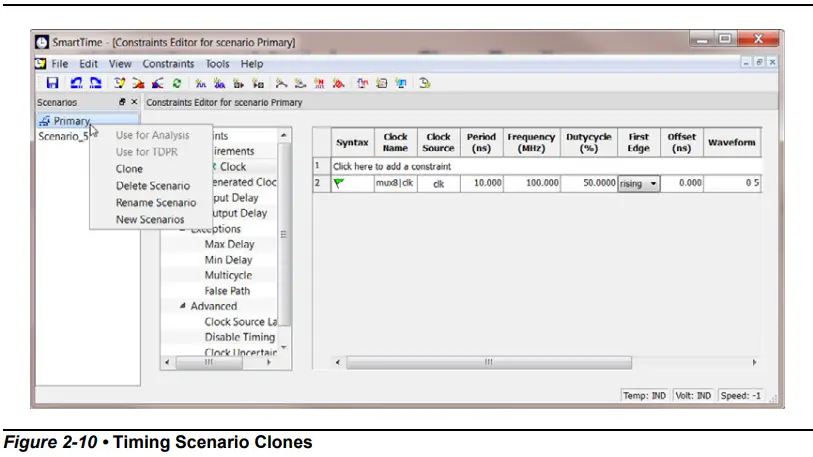

- 在 SmartTime 中克隆现有的时序约束场景。在约束编辑器中,右键单击主要场景并选择克隆(图 2-10)。

- 保留原始(主要)约束集以进行时序分析

- 输入跨时钟域的设计路径的set_max_delay约束(图2-11)。

- 将第二组约束(克隆场景)专门用于 TDPR。右键单击克隆场景并选择用于 TDPR(图 2-12)。

- 在 SmartTime 中克隆现有的时序约束场景。在约束编辑器中,右键单击主要场景并选择克隆(图 2-10)。

-

有关 set_max_delay 约束的详细信息,请参阅 SmartTime 在线帮助。

RTG4 IP 块的约束

本章描述了以下块的约束要求:

- 振荡器

- 结构时钟调节电路 (CCC)

- 高速串行接口 (SERDES)

振荡器

振荡器仅有一个 50 MHz 的输出 CLKOUT。该输出只能连接到 CCC 配置器。

- 振荡器合成约束

您必须为设计使用的振荡器指定时钟约束。

图 3-2 显示了综合后的模块。

以下约束适用于实例名称为 RCOSC_50MHZ_0 的振荡器。RC 振荡器配置为 50 MHz。

创建时钟-名称osc_50MHz-周期20 \

[获取引脚 { RCOSC_50MHZ_0.CLKOUT}] - 振荡器布局和布线约束

对于 SmartTime,连接到 CCC 实例 RTG4FCCC_0 的振荡器配置器的约束是:

创建时钟-名称 osc_50MHz-周期 20 [获取引脚 {RCOSC_50MHZ_0:CLKOUT}]

RTG4 结构时钟调节电路 (CCC)

CCC 用于倍增、分频或延迟时钟。使用生成的时钟可以最好地描述其效果。

- RTG4 织物 CCC 合成约束

要通过生成的时钟创建 RTG4FCCC 综合约束,您需要使用 RTG4FCCC 倍数和除法因子。此信息可在 CCC 配置器中的高级选项卡中找到,可通过 Libero 软件访问(图 3-3)。

图 3-3 所示的 CCC 配置生成四个时钟:- 在 GL0 上,使用 PLL 从 150 MHz 输入时钟生成 50 MHz 时钟

- 在 GL1 上,从同一 PLL 生成 200 MHz

- 在 GL2 上,由 25 MHz 振荡器生成 50 MHz 时钟。

- 在 GL3 上,由 CLK100_PAD 和 CLK_PAD3 生成 2MHz 时钟。

可以根据配置器中显示的分频器配置来计算准确的分频和乘法因子。用于 GL0 的因子已圈出。使用 CCC 时,乘法因子由反馈分频器(蓝色圈出)给出;分频因子由参考分频器(红色圈出)乘以输出 (GPD) 分频器(绿色圈出)给出。

相应生成的时钟是:

create_clock -name CLK0_PAD -period 20 [get_pins {RTG4FCCC_0.CLK0_PAD}] create_clock -name CLK2_PADP -period 10 [get_pins {RTG4FCCC_0.CLK2_PADP}] create_clock -name CLK3_PADP -period 10 [get_pins {RTG4FCCC_0.CLK3_PADP}] create_generated_clock -name clk_150mhz -divide_by 16 -multiply_by 24 \

-源[获取引脚{RTG4FCCC_0.CLK0_PAD}] \

[获取引脚 {RTG4FCCC_0.GL0}] 创建生成的时钟 -名称 clk_200mhz -除以 12 -乘以 24 \

-源[获取引脚{RTG4FCCC_0.CLK0_PAD}]\

[获取引脚 {RTG4FCCC_0.GL1}] 创建生成的时钟 -名称 clk_25mhz -divide_by 2 \

-源[获取引脚{RTG4FCCC_0.RCOSC_50MHZ}] \

[获取引脚 {RTG4FCCC_0.GL2}] 创建生成的时钟 -名称 clk_100mhz -除以 1 -乘以 1 \

-源[获取引脚{RTG4FCCC_0.CLK2_PADP}] \

[获取引脚 {RTG4FCCC_0.GL3}]

- RTG4 结构 CCC 布局和布线约束

对于 SmartTime,CCC 配置器的约束是:

create_clock -名称 CLK0_PAD -周期 20 [get_ports {CLK0_PAD}] create_clock -名称 CLK2_PADP -周期 10 [get_ports {CLK2_PADP}] create_clock -名称 CLK3_PADP -周期 10 [get_ports {CLK3_PADP}] create_generated_clock -名称 clk_150mhz \

-divide_by 16 \

-multiply_by 24 \

-源{RTG4FCCC_0/CCC_INST/INST_CCC_IP:CLK0_PAD} \

{RTG4FCCC_0/CCC_INST/INST_CCC_IP:GL0}

创建生成的时钟-名称 clk_200mhz \

-divide_by 12 \

-multiply_by 24 \

-源{RTG4FCCC_0/CCC_INST/INST_CCC_IP:CLK0_PAD} \

{RTG4FCCC_0/CCC_INST/INST_CCC_IP:GL1}

创建生成的时钟-名称 clk_25mhz \

-divide_by 2 \

-源{RTG4FCCC_0/CCC_INST/INST_CCC_IP:RCOSC_50MHZ} \

{RTG4FCCC_0/CCC_INST/INST_CCC_IP:GL2}

创建生成的时钟-名称 clk_100mhz \

-divide_by 1 \

-multiply_by 1 \

-源{RTG4FCCC_0/CCC_INST/INST_CCC_IP:CLK2_PAD} \

{RTG4FCCC_0/CCC_INST/INST_CCC_IP:GL3}

高速串行接口 (SERDES) 模块

高速串行接口模块或串行器/解串器接口 (SERDESIF) 集成了多个功能模块,以支持 FPGA 内的多种高速串行协议。SERDESIF 模块具有以下特点:

- 外围组件互连快速 (PCIe-PCI Express®) 协议支持

- 10 千兆位连接单元接口 (XAUI) 协议支持

- 外部物理编码子层 (EPCS) 接口支持任何用户定义的高速串行协议,例如串行千兆媒体独立接口 (SGMII) 协议支持

单或双串行协议操作模式。在双串行协议模式下,可以在 SERDESIF 块的四个物理通道上实现两种协议,SERDESIF 块通过 AXI/AHBL 接口或 EPCS 接口与 FPGA 结构进行通信

- PCI Express 协议模式

在这种模式下,SERDESIF 块使用 AXI/AHBL 接口和 APB3 接口与 FPGA 通信进行配置;不需要特定于此块的约束。 - EPCS 协议模式

在 EPCS 模式下,SERDESIF 最多可支持 4 个通道。在 EPCS 模式下,SERDESIF 模块使用三个时钟:- APB_S_PCLK 用于 APB3 配置总线

- EPCS_0_RXFWF_RCLK 用于接收数据飞轮 fifo 结构接口

- EPCS_0_TXFWF_WCLK 用于传输数据飞轮 fifo 结构接口

APB_S_PCLK、EPCS_0_RXFWF_RCLK 和 EPCS_0_TXFWF_WCLK 时钟必须在其源处定义。无需针对此块设置任何特定约束。

- XAUI 协议模式

在 XAUI 模式下,SERDESIF 模块使用五个时钟:- REFCLK_P – TxPLL 的输入

- APB_S_CLK 用于 APB3 配置总线

- XAUI_MMD_MDC 作为 MDIO 接口时钟

- XAUI_RX_CLK_IN – 接收数据在飞轮 FIFO 中与此时钟同步

- XAUI_TX_CLK_OUT – 传输的数据是amp如果启用了时钟补偿,则使用同步时钟。XAUI_TX_CLK_OUT 必须连接到 XAUI_FB_CLK 才能启用时钟补偿。

REFCLK_P、APB_S_PCLK、XAUI_MMD_MDC 和 XAUI_RX_CLK_IN 时钟必须在其源处定义。

XAUI_TX_CLK_OUT 时钟可以在 SERDESIF 块的 GL0/GL1 输出端口上定义。examp下面的文件为 NPSS 和 PCIE SERDES 块创建这些时钟。

- XAUI 综合约束

- NPSS 串行器/解串器

创建时钟-名称 { gl_clocks1 } \

-周期 6.400 \

[获取引脚 {NPSS_SERDES_IF_0.SERDESIF_INST.GL*}] - PCIE 串行器/解串器

创建时钟-名称 { gl_clocks2 } \

-周期 6.400 \

[获取引脚 {PCIE_SERDES_IF_0.SERDESIF_INST.GL*}]

- NPSS 串行器/解串器

- XAUI 布局和布线约束

- NPSS 串行器/解串器

创建时钟-名称 { gl_clocks1 } \

-周期 6.400 \

[获取引脚 {NPSS_SERDES_IF_0/SERDESIF_INST/INST_NPSS_IP:GL*}] - PCIE 串行器/解串器

创建时钟-名称 { gl_clocks2 } \

-周期 6.400 \

[获取引脚 {PCIE_SERDES_IF_0/SERDESIF_INST/INST_PCIE_IP:GL*}

- NPSS 串行器/解串器

产品支持

美高森美 SoC 产品部为其产品提供各种支持服务,包括客户服务、客户技术支持中心、 web网站、电子邮件和全球销售办事处。 本附录包含有关联系 Microsemi SoC 产品组和使用这些支持服务的信息。

客户服务

联系客户服务以获得非技术产品支持,例如产品定价、产品升级、更新信息、订单状态和授权。

- 从北美拨打 800.262.1060

- 从世界其他地方拨打 650.318.4460

- 传真,来自世界各地,408.643.6913

客户技术支持中心

美高森美 SoC 产品部在其客户技术支持中心配备了技术精湛的工程师,他们可以帮助回答有关美高森美 SoC 产品的硬件、软件和设计问题。 客户技术支持中心花费大量时间创建应用说明、常见设计周期问题的答案、已知问题的文档以及各种常见问题解答。 因此,在联系我们之前,请访问我们的在线资源。 我们很可能已经回答了您的问题。

技术支援

访问客户支持 web网站(www.microsemi.com/soc/support/search/default.aspx) 以获得更多信息和支持。 可搜索的许多答案 web 资源包括图表、插图和指向其他资源的链接 web地点。

Web地点

您可以在 SoC 主页上浏览各种技术和非技术信息,网址为 www.microsemi.com/soc.

联系客户技术支持中心

技术支持中心拥有高技能的工程师。 可以通过电子邮件或通过 Microsemi SoC 产品组联系技术支持中心 web地点。

电子邮件

您可以将您的技术问题发送到我们的电子邮件地址,并通过电子邮件、传真或电话收到回复。 此外,如果您有设计问题,您可以通过电子邮件发送您的设计 file接受帮助。 我们全天不断地监控电子邮件帐户。 向我们发送您的请求时,请务必包含您的全名、公司名称和您的联系信息,以便高效地处理您的请求。

技术支持电子邮件地址是 soc_tech@microsemi.com.

我的案例

美高森美 SoC 产品组客户可以通过转到“我的案例”在线提交和跟踪技术案例。

美国境外

在美国时区以外需要帮助的客户可以通过电子邮件联系技术支持 (soc_tech@microsemi.com) 或联系当地的销售办事处。 销售办事处列表可在以下位置找到 www.microsemi.com/soc/company/contact/default.aspx.

ITAR 技术支持

如需获得受《国际武器贸易条例》(ITAR)监管的 RH 和 RT FPGA 的技术支持,请通过 soc_tech_itar@microsemi.com 联系我们。或者,在我的案例中,在 ITAR 下拉列表中选择“是”。如需查看受 ITAR 监管的 Microsemi FPGA 的完整列表,请访问 ITAR web 页。

Microsemi Corporation(纳斯达克股票代码:MSCC)为通信、国防和安全、航空航天和工业市场提供全面的半导体和系统解决方案组合。 产品包括高性能和抗辐射模拟混合信号集成电路、FPGA、SoC 和 ASIC; 电源管理产品; 计时和同步设备以及精确的时间解决方案,为时间设定了世界标准; 语音处理设备; 射频解决方案; 分立元件; 安全技术和可扩展的反 tamp呃产品; 以太网供电 IC 和中跨; 以及定制设计能力和服务。 Microsemi 总部位于加利福尼亚州 Aliso Viejo,在全球拥有约 3,400 名员工。 了解更多信息 www.microsemi.com.

美高森美公司总部

One Enterprise, Aliso Viejo CA 92656 美国

在美国境内: +1 800-713-4113

美国境外: +1 949-380-6100

销售量: +1 949-380-6136

传真: +1 949-215-4996

电子邮件: sales.support@microsemi.com

©2015 Microsemi Corporation。保留所有权利。Microsemi 和 Microsemi 徽标是

微半导体公司。 所有其他商标和服务标志均为其各自所有者的财产。

文件/资源

|

Microsemi RTG4 FPGA 时序约束 [pdf] 用户指南 RTG4 FPGA 时序约束,RTG4 FPGA,时序约束,约束 |