AN5827

Nota ta' applikazzjoni

Linji gwida għad-dħul fl-istat RMA fuq MPUs tas-Serje STM32MP1

Introduzzjoni

Il-mikroproċessuri tas-Serje STM32MP1 jinkludu apparati STM32MP15xx u STM32MP13xx .. Din in-nota tal-applikazzjoni tipprovdi informazzjoni biex tappoġġja l-proċess tad-dħul tal-istat tal-analiżi tal-materjal tar-ritorn, imsejjaħ RMA f'dan id-dokument.

Informazzjoni ġenerali

Dan id-dokument japplika għall-mikroproċessuri tas-Serje STM32MP1 ibbażati fuq il-qlub Arm® Cortex®

Nota: Arm hija trademark reġistrata ta' Arm Limited (jew is-sussidjarji tagħha) fl-Istati Uniti u/jew xi mkien ieħor.

Dokumenti ta' referenza

| Referenza | Titolu tad-dokument |

| STM32MP13xx | |

| AN5474 | Nibdew bl-iżvilupp tal-ħardwer tal-linji STM32MP13x |

| DS13878 | Arm® Cortex®-A7 sa 1 GI-ft, 1xETH, 1 xADC, 24 tajmer, awdjo |

| DS13877 | Arm® Cortex®-A7 sa 1 GHz, 1xETH, 1 xADC, 24 tajmer, awdjo, kripto u adv. sigurtà |

| DS13876 | Arm® Cortex®-A7 sa 1 GI-ft, 2xETH, 2xCAN FD, 2xADC. 24 tajmer, awdjo |

| DS13875 | Arm® Cortex®-A7 sa 1 GHz, 2xETH, 2xCAN FD, 2xADC, 24 tajmer, awdjo, kripto u adv. sigurtà |

| DS13874 | Arm® Cortex®-A7 sa 1 GHz, LCD-TFT, interface tal-kamera, 2xETH, 2xCAN FD, 2xADC, 24 tajmer, awdjo |

| DS13483 | Arm® Cortex®-A7 sa 1 GHz, LCD-TFT, interface tal-kamera, 2xETH, 2xCAN FD, 2xADC, 24 tajmer, awdjo, kripto u adv. sigurtà |

| RM0475 | STM32MP13xx avvanzati MPUs 0-bit ibbażati fuq Arm32 |

| STM32MP15xx | |

| AN5031 | Nibdew bl-iżvilupp tal-ħardwer tal-linja STM32MP151, STM32MP153 u STM32MP157 |

| DS12500 | Arm® Cortex®-A7 800 MHz + Cortex®-M4 MPU, TFT, 35 comm. interfaces, 25 tajmer, adv. analogu |

| DS12501 | Arm® Cortex®-A7 800 MHz + Cortex®-M4 MPU, TFT, 35 comm. interfaces, 25 tajmer, adv. analogu, kripto |

| DS12502 | Arm® dual Cortex®-A7 800 MHz + Cortex®-M4 MPU, TFT, 37 comm. interfaces, 29 tajmer, adv. analogu |

| DS12503 | Arm® dual Cortex®-A7 800 MHz + Cortex®-M4 MPU, TFT, 37 comm. interfaces, 29 tajmer, adv. analogu, kripto |

| DS12504 | Arm® dual Cortex®-A7 800 MHz + Cortex®-M4 MPU, 3D GPU, TFT/DSI, 37 comm. interfaces, 29 tajmer, adv. analogu |

| DS12505 | Arm® dual Cortex®-A7 800 MHz + Cortex®-M4 MPU, 3D GPU, TFT/DSI, 37 comm. interfaces, 29 tajmer, adv. analogu, kripto |

| RM0441 | STM32MP151 MPUs 32-bit ibbażati fuq Arm® avvanzati |

| RM0442 | STM32MP153 avvanzati MPUs 32-bit bbażati fuq Arnie |

| RM0436 | STM32MP157 MPUs 0-bit ibbażati fuq Arm32 avvanzati |

Termini u akronimi

Tabella 2. Definizzjoni tal-akronimi

| Terminu | Definizzjoni |

| BOGĦOD | Talba għall-analiżi tal-falliment: fluss użat biex jirritorna apparat suspettuż għall-analiżi lil STMicroelectronics. Biex ittejjeb il-sħiħ testability tal-apparat waqt analiżi bħal din, l-apparat għandu jkun fi stat RMA. |

| JTAG | Grupp ta' azzjoni tat-test konġunt (interface tad-debug) |

| PMIC | Ċirkwit estern tal-ġestjoni tal-enerġija li jipprovdi diversi provvisti tal-enerġija tal-pjattaforma, b'kontrollabbiltà kbira permezz sinjali u interface serjali. |

| RMA | Analiżi tal-materjal tar-ritorn: stat speċifiku tal-apparat fiċ-ċiklu tal-ħajja li jippermetti l-attivazzjoni tal-modalità tat-test sħiħ kif meħtieġ minn STMicroelectronics għall-iskop ta 'analiżi ta' falliment. |

1. F'dan id-dokument, l-akronimu RMA ma jirreferi mkien għal "aċċettazzjoni ta' materjal ta' ritorn" li huwa l-fluss użat biex jirritorna partijiet mhux użati (stokk tal-klijent għal example).

Stat RMA fi ħdan il-fluss FAR

Il-fluss FAR jikkonsisti fir-ritorn ta' apparat lil STMicroelectronics għal analiżi aktar profonda tal-fallimenti f'każ ta' kwistjoni ta' kwalità suspettata. Il-parti għandha tiġi rritornata testable lil ST sabiex l-analiżi tkun tista 'titwettaq.

- Il-parti trid tkun fl-istat RMA

- Il-parti għandha tkun fiżikament kompatibbli mal-apparat oriġinali (daqs tal-ballun, żift, eċċ.)

Ċiklu tal-ħajja tal-prodott STM32MP13xx

Fuq apparati STM32MP13xx, qabel ma jirritorna l-apparat, il-klijent għandu jidħol fi stat RMA b'password ta' 32-bit predefinita mill-klijent imdaħħla permezz tal-JTAG (ara t-Taqsima 3). Ladarba jiddaħħal fl-istat RMA, l-apparat ma jkunx aktar użabbli għall-produzzjoni (ara l-Figura 1) u l-mod tat-test sħiħ jiġi attivat biex STMicroelectronics ikompli l-investigazzjoni filwaqt li s-sigrieti kollha tal-klijenti (OTP ta’ fuq kif deskritt fil-manwal ta’ referenza) jinżammu inaċċessibbli. mill-ħardwer.

Il-figura hawn taħt turi ċ-ċiklu tal-ħajja tal-prodott tal-apparati STM32MP13xx. Juri li ladarba l-istat RMA jiddaħħal l-apparat ma jistax imur lura għal modi oħra.

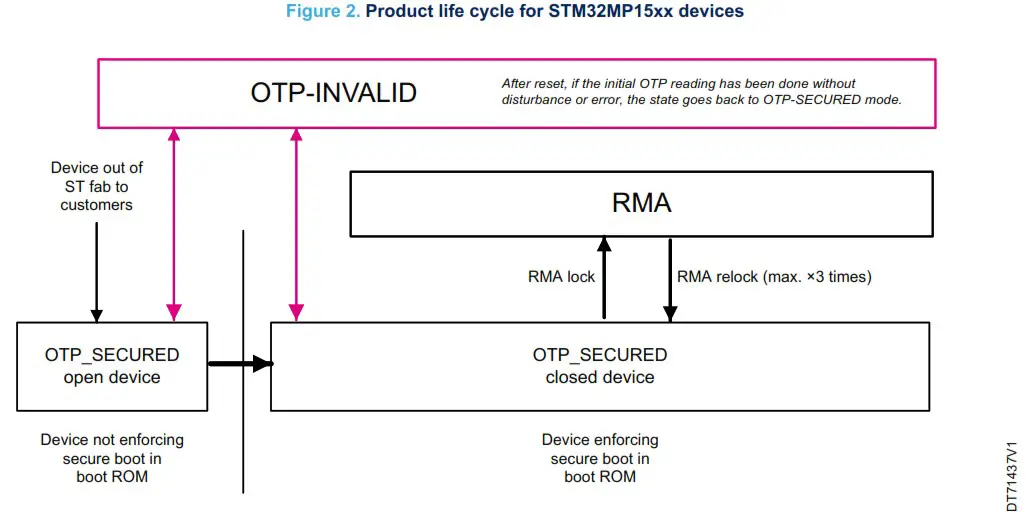

Ċiklu tal-ħajja tal-prodott STM32MP15xx

Fuq apparati STM32MP15xx, qabel ma jirritorna l-apparat, il-klijent għandu jidħol fi stat RMA b'password ta' 15-bit predefinita mill-klijent imdaħħla permezz tal-JTAG (ara t-Taqsima 3). Ladarba jiddaħħal fl-istat RMA, l-apparat jista 'jmur lura għall-istat SECURE_CLOSED billi jdaħħal password "RMA_RELOCK" predefinita mill-klijent. Huma permessi biss 3 RMA għal RMA_RELOCKED provi tal-istat ta' tranżizzjoni (ara l-Figura 2). Fl-istat RMA, il-mod tat-test sħiħ huwa attivat għal STMicroelectronics biex ikompli l-investigazzjoni filwaqt li s-sigrieti kollha tal-klijenti (OTP ta 'fuq kif deskritt fil-manwal ta' referenza) jinżammu inaċċessibbli mill-hardware.

Il-figura hawn taħt turi ċ-ċiklu tal-ħajja tal-prodott tal-apparati STM32MP15x.

Limitazzjonijiet tal-bord tal-istat tal-RMA

Biex jiġi attivat l-istat RMA, huma meħtieġa r-restrizzjonijiet li ġejjin.

Il-JTAG l-aċċess għandu jkun disponibbli

Is-sinjali NJTRST u JTDI, JTCK, JTMS, JTDO (pin PH4, PH5, PF14, PF15 fuq apparati STM32MP13xx) għandhom ikunu aċċessibbli. Fuq xi għodod, il-JTDO mhux meħtieġ (eżample, Trace32) fuq oħrajn bħal OpenOCD l-għodda tiċċekkja l-apparat JTAG ID permezz tal-JTDO qabel ma tesegwixxi l-JTAG sekwenza.

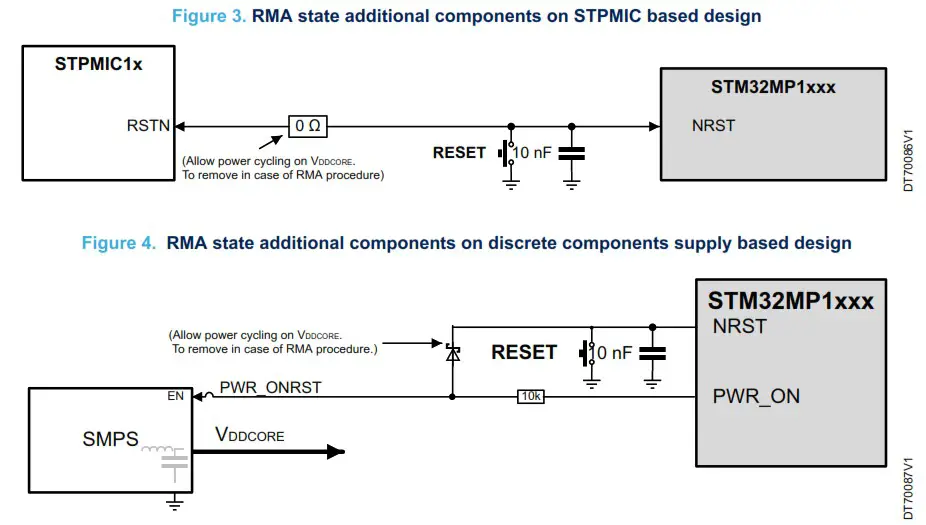

Il-provvisti tal-enerġija VDDCORE u VDD m'għandhomx jiġu mitfija meta l-pin NRST jiġi attivat

Fuq id-disinn ta 'referenza ST, l-NRST jattiva ċiklu tal-enerġija tal-STPMIC1x jew regolaturi tal-qawwa tal-komponenti diskreti esterni. Implimentazzjoni possibbli hija murija fid-disinn ta 'referenza example pprovduta fin-nota tal-applikazzjoni Nibdew bl-iżvilupp tal-ħardwer tal-linji STM32MP13x (AN5474) . Figura 3 u Figura 4 huma verżjonijiet simplifikati li juru biss il-komponenti relatati mal-istat RMA. L-istess japplika għall-apparati STM32MP15xx.

Bord sempliċi bil-JTAG pin u socket xieraq jistgħu jintużaw għal skopijiet ta' password RMA biss (f'każ li ma jkunx possibbli li wieħed jaċċessa JTAG fuq il-bord tal-produzzjoni). F'każ bħal dan il-klijent għandu l-ewwel jissalda l-apparat mill-bord tal-produzzjoni u jerġa 'jippopola l-boċċi tal-pakkett.

Il - bord għandu jkollu l - pinnijiet STM32MP1xxx elenkati fit - Tabella 3 konnessi kif indikat . Labar oħra jistgħu jitħallew f'wiċċ l-ilma.

Tabella 3. Konnessjoni tal-pin għal bord sempliċi użat għad-dħul tal-password RMA

| Isem tal-pin (sinjal) | Konnessi ma' | Ikkummenta | |

| STM32MP13xx | STM32MP15xx | ||

| JTAG u reset | |||

| NJTRST | NJRST | JTAG konnettur | |

| PH4 (JTDI) | JTDI | ||

| PH5 (JTDO) | JTDO | Mhux meħtieġ fuq xi għodda tad-debug bħal Trace32 | |

| PF14 (JTCK) | JTCK | ||

| PF15 (JTMS) | JTMS | ||

| NRST | NRST | Irrisettja buttuna | B'capacitor ta '10 nF għal VSS |

| Provvisti tal-enerġija | |||

| VDDCORE. VDDCPU | VDDCORE | Provvista esterna | Irreferi għad-datasheet tal-prodott għal tipiċi valur |

| VDD. VDDSD1. VDDSD2. VDD_PLL. VDD_PLL2. VBAT. VDD_ANA. PDR_ON |

VDD. VDD_PLL. VDD_PLL2. VBAT. VDD_ANA. PDR_ON. PDR_ON_CORE |

3.3 V estern provvista |

Għandhom ikunu disponibbli l-ewwel u mneħħija l-aħħar (jistgħu jkunu flimkien ma' oħrajn provvisti) |

| VDDA, VREF+, VDD3V3_USBHS. VDDO_DDR |

VDDA. VREF+. VDD3V3_USBHS. VDDO_DDR. VDD_DSI. VDD1V2_DSI_REG. VDD3V3_USBFS |

0 | ADC. VREFBUF, USB, DDR mhux użati |

| VSS. VSS_PLL. VSS_PLL2. VSSA. VSS_ANA. VREF-. VSS_US131-IS |

VSS. VSS_PLL, VSS_PLL2. VSSA. VSS_ANA. VREF-. VSS_USBHS. VSS_DSI |

0 | |

| VDDA1V8_REG. VDDA1V1_REG |

VDDA1V8_REG. VDDA1V1_REG |

f'wiċċ l-ilma | |

| Oħrajn | |||

| BYPASS_REG1V8 | BYPASS_REG1V8 | 0 | Regolatur 1V8 attivat awtomatikament (REG 18E = 1) |

| PC15- OSC32_OUT | PC15- OSC32_OUT | f'wiċċ l-ilma | |

| PC14- OSC32_IN | PC14- OSC32_IN | Oxxillaturi esterni mhux użati (boot ROM biex tuża oxxillatur intern HSI) |

|

| PHO-OSC_IN | PHO-OSC_IN | ||

| PH1-0SC_OUT | PH1-0SC_OUT | ||

| USB_RREF | USB_RREF | f'wiċċ l-ilma | USB mhux użat |

| P16 (BOOT2) | BOT2 | X | Id-dħul fl-istat RMA jaħdem ikunu xi jkunu l-valuri tal-boot(2:0). |

| PI5 (BOOT1) | 60011 | X | |

| PI4 (BOOTO) | BOOTO | X | |

| NRST_CORE | 10 nF għal VSS | Ġbid intern fuq NRST_CORE | |

| PA13 (BOOTFAILN) | PA13 (BOOTFAILN) | LED | Fakultattiv |

Rekwiżiti minn qabel biex jippermettu d-dħul ta 'stat RMA futur

Il-possibbiltà li tidħol fl-istat RMA trid tiġi stabbilita mill-klijent billi ddaħħal password waqt il-produzzjoni tal-klijent wara forniment sigriet

- L-apparat meta jintbagħat minn STMicroelectronics huwa fi stat miftuħ OTP_SECURED.

- L-apparat fih sigrieti ST li huma protetti minn boot ROM, u l-ebda sigriet tal-klijent.

- Fl-irrisettjar jew wara l-eżekuzzjoni tal-boot ROM, l-aċċess DAP jista 'jinfetaħ mill-ġdid permezz tal-Linux jew permezz tal-modalità "boot tal-iżvilupp" tal-boot ROM (OTP_SECURED miftuħa + boot pins BOOT[2:0]=1b100 + reset).

- Waqt li jkun OTP_SECURED miftuħ, il-klijent għandu jipprovdi s-sigrieti tiegħu f'OTP:

- direttament mill-klijent għar-riskju proprju jew

- sikur permezz tal-kanal encrypted bl-użu tal-"karatteristika SSP" tal-boot ROM flimkien ma 'għodod STM32.

- Fl-aħħar tal-forniment tas-sigrieti, il-klijent jista 'jgħaqqad:

- Fuq STM32MP13xx password RMA ta' 32 bit f'OTP_CFG56 (il-password għandha tkun 0).

- Fuq STM32MP15xx password RMA 15 bit f'OTP_CFG56[14:0], password RMA_RELOCK f'OTP_CFG56[29:15].

Il-password għandha tkun differenti minn 0.

- Issettja l-OTP_CFG56 bħala "lock ta 'programmar permanenti" biex tevita l-ipprogrammar aktar tard f'0xFFFFFF u tippermetti li tidħol fl-istat RMA mingħajr ma tkun taf il-password inizjali.

- Ivverifika l-ipprogrammar korrett tal-OTP_CFG56 billi tiċċekkja r-reġistru BSEC_OTP_STATUS.

- Fl-aħħarnett, l-apparat jinbidel għal OTP_SECURED magħluq:

- Fuq STM32MP13xx billi tgħaqqad OTP_CFG0[3] = 1 u OTP_CFG0[5] = 1.

- Fuq STM32MP15xx billi tgħaqqad OTP_CFG0[6] = 1.

L-apparat jista' jerġa' jinfetaħ fl-istat RMA għal investigazzjoni minn STMicroelectronics

- Meta l-apparat ikun fi stat magħluq OTP_SECURED, "boot ta 'żvilupp" ma jkunx aktar possibbli.

Stat RMA li jdaħħal id-dettalji

Kif issemma qabel, l-istat RMA jintuża biex jerġa 'jinfetaħ b'mod sikur il-mod tat-test sħiħ mingħajr ebda espożizzjoni ta' sigrieti pprovduti mill-klijent. Dan isir grazzi għall-funzjonali JTAG inputs filwaqt li s-sigrieti kollha tal-klijenti jinżammu inaċċessibbli mill-hardware.

Fil-każ li jkun hemm rekwiżit għal analiżi fuq sample hemm il-ħtieġa li tmur għall-istat RMA (ara l-Figura 5. Qlib għal OTP_SECURED magħluqa ), li jiżgura s-sigrieti tal-klijenti u jerġa 'jiftaħ il-debug sigur u mhux sikur fid-DAP.

- Il-klijent jiċċaqlaq f'BSEC_JTAGIN irreġistra l-password RMA billi tuża JTAG (Valuri differenti minn 0 biss huma aċċettati).

- Il-klijent jerġa 'jissettja l-apparat (pin NRST).

Nota: Matul dan il-pass, il-password f'BSEC_JTAGIN reġistru m'għandux jitħassar. Għalhekk, l-NRST m'għandux jagħlaq il-VDD u lanqas il-provvisti tal-enerġija VDDCORE. M'għandux ukoll ikun imqabbad mal-pin NJTRST. F'każ li jintuża STPMIC1x, jista' jkun obbligatorju li l-provvisti tal-enerġija jiġu mgħottija waqt ir-reset. Dan isir billi tipprogramma r-reġistru tal-għażla tal-maskra STPMIC1x (BUCKS_MRST_CR) jew titneħħa r-reżistenza miżjuda għal RMA fuq il-bord bejn STPMICx RSTn u STM32MP1xxx NRST (ara l-Figura 3). - Il-boot ROM tiġi invokata u tiċċekkja l-password RMA mdaħħla f'BSEC_JTAGIN b'OTP_CFG56.RMA_PASSWORD:

• Jekk il-passwords jaqblu, l-sample isir RMA_LOCK sample (għal dejjem fuq STM32MP13xx).

• Jekk il-passwords ma jaqblux, l-sample tibqa 'fl-istat magħluq OTP_SECURED u counter RMA ta' "ftuħ mill-ġdid tal-provi" huwa inkrementat f'OTP.

Nota: Tliet provi tal-ftuħ mill-ġdid tal-RMA biss huma awtorizzati. Wara tliet provi falluti, il-ftuħ mill-ġdid tal-RMA m'għadux possibbli. L-apparat jibqa' fl-istat attwali taċ-ċiklu tal-ħajja tiegħu. - Il-klijent resets it-tieni darba l-sample permezz tal-pin NRST:

• l-LED fuq PA13 huwa mixgħul (jekk imqabbad)

• l-aċċess tad-debug DAP jerġa' jinfetaħ. - L-apparat jista' jintbagħat lil STMicroelectronics.

- Wara reset (pin NRST jew kwalunkwe reset tas-sistema), il-boot ROM jiġi invokat:

• Jiskopri li OTP8.RMA_LOCK = 1 (RMA msakkra sample).

• Tassigura l-STMicroelectronics u s-sigrieti tal-klijenti kollha.

• Terġa' tiftaħ l-aċċess tad-debug DAP b'mod sigur u mhux sigur.

Filwaqt li fl-istat RMA il-parti qed tinjora l-labar tal-Ibbutjar u mhix kapaċi tibbutja minn flash estern u lanqas USB/UART.

RMA nisfruttaw id-dettalji

Fuq STM32MP15xx huwa possibbli li jinfetaħ l-apparat minn RMA u jerġa 'lura għall-istat SECURE_CLOSED.

Fil-BSEC_JTAGFIR-reġistru, il-klijent ibiddel il-password tal-ftuħ tal-RMA billi juża JTAG (Valuri differenti minn 0 biss huma aċċettati)

- Il-klijent jerġa 'jissettja l-apparat (pin NRST).

Nota: Tliet provi RMA Unlock biss huma awtorizzati. Wara tliet provi falluti, RMA nisfruttaw m'għadux possibbli. L-apparat jibqa' fl-istat taċ-ċiklu tal-ħajja RMA tiegħu. - Il-klijent resets it-tieni darba l-sample permezz tal-pin NRST:

• l-LED fuq PA13 huwa mixgħul (jekk imqabbad),

• l-apparat huwa fi stat SECURE_CLOSED (aċċess tad-debug DAP huwa magħluq).

Stat RMA li jidħol JTAG skript examples

STM32MP13xx skript examples biex tidħol il-password u tidħol fl-istat RMA huma disponibbli f'zip separat file. Jistgħu jintużaw ma' Trace32, OpenOCD bl-użu ta' sonda STLINK, OpenOCD bl-użu ta' sonda kompatibbli CMSIS-DAP (eż.ample ULink2). L-informazzjoni tista' tinstab fuq www.st.com. Irreferi għall-prodott STM32MP13xx "Riżorsi CAD" fit-taqsima "speċifikazzjoni tal-manifattura tal-bord".

Simili examples jistgħu jiġu derivati għal apparati STM32MP15xx. Example biex tidħol fl-istat RMA u biex toħroġ mill-istat RMA għal Trace32 hija disponibbli f'zip separat file. L-informazzjoni tista' tinstab fuq www.st.com. Irreferi għall-prodott STM32MP15x "Riżorsi CAD" fit-taqsima "speċifikazzjoni tal-manifattura tal-bord".

Storja tar-reviżjoni

Tabella 4. Storja tar-reviżjoni tad-dokument

| Data | Verżjoni | Bidliet |

| 13-Frar-23 | 1 | Rilaxx inizjali. |

AVVIŻ IMPORTANTI AQRA B'attenzjoni

STMicroelectronics NV u s-sussidjarji tagħha (“ST”) jirriżervaw id-dritt li jagħmlu bidliet, korrezzjonijiet, titjib, modifiki, u titjib għall-prodotti ST u/jew għal dan id-dokument fi kwalunkwe ħin mingħajr avviż. Ix-xerrejja għandhom jiksbu l-aħħar informazzjoni rilevanti dwar il-prodotti ST qabel ma jagħmlu ordnijiet. Il-prodotti ST jinbiegħu skont it-termini u l-kundizzjonijiet tal-bejgħ ta' ST fis-seħħ fil-ħin tar-rikonoxximent tal-ordni.

Ix-xerrejja huma unikament responsabbli għall-għażla, l-għażla u l-użu tal-prodotti ST u ST ma jassumi l-ebda responsabbiltà għall-assistenza tal-applikazzjoni jew id-disinn tal-prodotti tax-xerrejja.

L-ebda liċenzja, espressa jew impliċita, għal xi dritt ta' proprjetà intellettwali ma tingħata minn ST hawnhekk.

Il-bejgħ mill-ġdid ta' prodotti ST b'dispożizzjonijiet differenti mill-informazzjoni stipulata hawnhekk għandu jħassar kwalunkwe garanzija mogħtija minn ST għal tali prodott.

ST u l-logo ST huma trademarks ta' ST. Għal informazzjoni addizzjonali dwar it-trademarks ST, irreferi għal www.st.com/trademarks. L-ismijiet l-oħra kollha tal-prodott jew tas-servizz huma proprjetà tas-sidien rispettivi tagħhom.

L-informazzjoni f'dan id-dokument tieħu post u tissostitwixxi l-informazzjoni pprovduta qabel fi kwalunkwe verżjoni preċedenti ta' dan id-dokument.

© 2023 STMicroelectronics Id-drittijiet kollha riżervati

AN5827 – Rev 1

AN5827 – Rev 1 – Frar 2023

Għal aktar informazzjoni ikkuntattja l-uffiċċju lokali tal-bejgħ STMicroelectronics tiegħek.

www.st.com

Dokumenti / Riżorsi

|

Mikroproċessuri Serje STMicroelectronics STM32MP1 [pdfGwida għall-Utent Mikroproċessuri Serje STM32MP1, Serje STM32MP1, Mikroproċessuri |