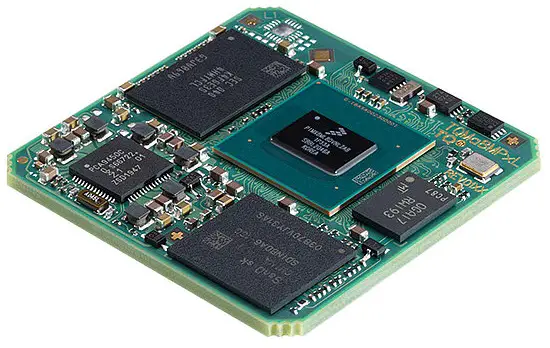

Computer a scheda singola incorporato TQMa8MPxL

Informazioni sul prodotto

Specifiche

- Modello: TQMa8MPxL

- Data: 06.05.2024

- Produttore: TQ-Systems GmbH

Istruzioni per l'uso del prodotto

Informazioni su questo manuale

Questo Manuale dell'utente fornisce informazioni importanti sul prodotto e sul suo corretto utilizzo. Include dettagli su copyright, spese di licenza, marchi registrati e dichiarazioni di non responsabilità.

Spese per diritti d'autore e licenze

Questo Manuale dell'utente è protetto da copyright e non può essere copiato, riprodotto, tradotto, modificato o distribuito senza il consenso scritto di TQ-Systems GmbH. I driver, le utilità, il BIOS e i componenti utilizzati sono soggetti ai diritti d'autore dei rispettivi produttori.

Marchi registrati

TQ-Systems GmbH rispetta i diritti d'autore e si propone di utilizzare grafica e testi originali o privi di licenza. Tutti i nomi di marchi e marchi commerciali menzionati in questo manuale sono protetti dalle attuali leggi sul copyright e sulla proprietà.

Disclaimer

TQ-Systems GmbH si riserva il diritto di modificare o aggiungere contenuti al presente Manuale dell'utente senza preavviso.

Domande frequenti

- D: Posso fare copie di questo Manuale dell'utente?

- A: No, questo manuale dell'utente non può essere copiato senza il consenso scritto di TQ-Systems GmbH.

- D: Le spese di licenza del sistema operativo sono incluse nel prezzo?

- A: No, le spese di licenza del sistema operativo e delle applicazioni non sono comprese nel prezzo e devono essere calcolate a parte.

Manuale dell'utente di TQMa8MPxL

TQMa8MPxL UM 0105 06.05.2024

CRONOLOGIA DELLE REVISIONI

Manuale dell'utente l TQMa8MPxL UM 0105 l © 2024, TQ-Systems GmbH

Pagina v

Rev. 0100 0101 0102 0103 0104 0105

Data

Nome

Posizione

23.03.2022 Kreuzer

22.11.2022 Kreuzer Tabella 3

30.05.2023 Kreuzer Capitolo 3.1.1.1

20.03.2024 Kreuzer Capitolo 3.2.5.20

11.04.2024 Kreuzer Tabella 3

06.05.2024 Kreuzer Tabella 27

Modifica Prima edizione V_SD2 corretto in Pout Numero di pad corretto a 366 Riferimenti ai capitoli corretti Assegnazioni delle sfere della CPU corrette Tabella ampliata

Manuale dell'utente l TQMa8MPxL UM 0105 l © 2024, TQ-Systems GmbH

Pagina 1

1.

INFORMAZIONI SU QUESTO MANUALE

1.1

Spese per diritti d'autore e licenze

Copyright protetto © 2024 da TQ-Systems GmbH.

Questo Manuale dell'utente non può essere copiato, riprodotto, tradotto, modificato o distribuito, completamente o parzialmente in formato elettronico, leggibile da una macchina o in qualsiasi altra forma senza il consenso scritto di TQ-Systems GmbH.

I driver e le utilità dei componenti utilizzati nonché il BIOS sono soggetti ai diritti d'autore dei rispettivi produttori. Devono essere rispettate le condizioni di licenza del rispettivo produttore.

Le spese di licenza del bootloader sono a carico di TQ-Systems GmbH e sono incluse nel prezzo.

Le spese di licenza del sistema operativo e degli applicativi non vengono prese in considerazione e devono essere calcolate/dichiarate separatamente.

1.2

Marchi registrati

TQ-Systems GmbH mira a rispettare i diritti d'autore di tutta la grafica e i testi utilizzati in tutte le pubblicazioni e si impegna a utilizzare grafica e testi originali o privi di licenza.

Tutti i marchi e i marchi citati nel presente Manuale dell'utente, compresi quelli protetti da terzi, se non diversamente specificato per iscritto, sono soggetti alle specifiche delle attuali leggi sul copyright e alle leggi sulla proprietà dell'attuale proprietario registrato senza alcuna limitazione. Si dovrebbe concludere che marchio e marchi sono giustamente protetti da terzi.

1.3

Disclaimer

TQ-Systems GmbH non garantisce che le informazioni contenute in questo Manuale dell'utente siano aggiornate, corrette, complete o di buona qualità. TQ-Systems GmbH non si assume nemmeno alcuna garanzia per l'ulteriore utilizzo delle informazioni. Le richieste di responsabilità nei confronti di TQ-Systems GmbH, in riferimento a danni materiali o immateriali causati dall'utilizzo o dal mancato utilizzo delle informazioni fornite nel presente Manuale dell'utente o dall'utilizzo di informazioni errate o incomplete, sono esenti a condizione che poiché non è stata dimostrata alcuna colpa intenzionale o negligente da parte di TQ-Systems GmbH.

TQ-Systems GmbH si riserva esplicitamente il diritto di modificare o integrare il contenuto del presente manuale dell'utente o parti di esso senza preavviso.

Avviso importante:

Prima di utilizzare lo Starterkit MBa8MPxL o parti degli schemi dell'MBa8MPxL, è necessario valutarlo e determinare se è adatto all'applicazione prevista. L'utente si assume tutti i rischi e le responsabilità associati a tale utilizzo. TQ-Systems GmbH non fornisce altre garanzie incluse, ma non limitate a, qualsiasi garanzia implicita di commerciabilità o idoneità per uno scopo particolare. Salvo laddove vietato dalla legge, TQ-Systems GmbH non sarà responsabile per eventuali perdite o danni indiretti, speciali, incidentali o consequenziali derivanti dall'utilizzo dello Starterkit MBa8MPxL o degli schemi utilizzati, indipendentemente dalla teoria legale affermata.

1.4

Impronta

TQ-Systems GmbH Gut Delling, Mühlstraße 2 D-82229 Seefeld

Tel: Fax: E-Mail: Web:

+49 8153 9308 +0 49 8153 Info@TQ-Group TQ-Group

Manuale dell'utente l TQMa8MPxL UM 0105 l © 2024, TQ-Systems GmbH

1.5

Consigli sulla sicurezza

Una manipolazione impropria o errata del prodotto può ridurne sostanzialmente la durata.

Pagina 2

1.6

Simboli e convenzioni tipografiche

Tabella 1: Termini e convenzioni

Simbolo

Senso

Questo simbolo rappresenta la manipolazione di moduli e/o componenti sensibili alle scariche elettrostatiche. Questi componenti vengono spesso danneggiati/distrutti dalla trasmissione di un voltage superiore a circa 50 V. Un corpo umano di solito sperimenta scariche elettrostatiche solo superiori a circa 3,000 V.

Questo simbolo indica il possibile utilizzo del voltages superiore a 24 V.

Si prega di osservare le norme di legge pertinenti al riguardo.

Il mancato rispetto di queste norme può provocare gravi danni alla salute e può danneggiare o distruggere il componente.

Questo simbolo indica una possibile fonte di pericolo. Ignorare le istruzioni descritte può causare danni alla salute o danneggiare l'hardware.

Questo simbolo rappresenta dettagli o aspetti importanti per lavorare con i prodotti TQ.

Comando

Un carattere a larghezza fissa viene utilizzato per denotare comandi, contenuti, file nomi o voci di menu.

1.7

Consigli per la manipolazione e ESD

Gestione generale dei vostri prodotti TQ

Il prodotto TQ può essere utilizzato e riparato solo da personale certificato che ha preso nota delle informazioni, delle norme di sicurezza contenute in questo documento e di tutte le norme e regolamenti correlati.

Una regola generale è non toccare il prodotto TQ durante il funzionamento. Ciò è particolarmente importante quando si accende, si modificano le impostazioni dei jumper o si collegano altri dispositivi senza assicurarsi prima che l'alimentazione del sistema sia stata disattivata.

La violazione di queste linee guida può causare danni/distruzione del TQMa8MPxL ed essere pericoloso per la salute.

Un utilizzo improprio del vostro prodotto TQ invaliderà la garanzia.

Gestione corretta delle scariche elettrostatiche

I componenti elettronici del prodotto TQ sono sensibili alle scariche elettrostatiche (ESD).

Indossare sempre indumenti antistatici, utilizzare strumenti, materiali di imballaggio ecc. sicuri per le scariche elettrostatiche e utilizzare il prodotto TQ in un ambiente sicuro per le scariche elettrostatiche. Soprattutto quando si accendono i moduli, si modificano le impostazioni dei jumper o si collegano altri dispositivi.

Manuale dell'utente l TQMa8MPxL UM 0105 l © 2024, TQ-Systems GmbH

Pagina 3

1.8

Denominazione dei segnali

Un cancelletto (#) alla fine del nome del segnale indica un segnale con attività bassa. Example: RESET#

Se un segnale può commutare tra due funzioni e se ciò è annotato nel nome del segnale, la funzione attiva bassa viene contrassegnata con un cancelletto e visualizzata alla fine.

Example: Do/Re#

Se un segnale ha più funzioni, le singole funzioni vengono separate da barre quando sono importanti per il cablaggio. L'identificazione delle singole funzioni segue le convenzioni sopra riportate. Example: WE2# / OE#

1.9

Ulteriori documenti applicabili/conoscenze presunte

· Specifiche e manuale dei moduli utilizzati: questi documenti descrivono il servizio, la funzionalità e le caratteristiche speciali del modulo utilizzato (incl. BIOS).

· Specifiche dei componenti utilizzati: le indicazioni del produttore dei componenti utilizzati, ad esample schede CompactFlash, è necessario tenerne conto. Contengono, se applicabili, informazioni aggiuntive di cui tenere conto per un funzionamento sicuro e affidabile. Questi documenti sono archiviati presso TQ-Systems GmbH.

· Errata chip: è responsabilità dell'utente assicurarsi che tutti gli errata pubblicati dal produttore di ciascun componente siano presi in considerazione. È necessario seguire i consigli del produttore.

· Comportamento del software: non viene fornita alcuna garanzia né si assume alcuna responsabilità per eventuali comportamenti imprevisti del software dovuti a componenti difettosi.

· Competenza generale: per l'installazione e l'utilizzo del dispositivo è richiesta competenza in ingegneria elettrica/informatica.

Per comprendere appieno i seguenti contenuti sono necessari i seguenti documenti:

· Schema elettrico MBa8MPxL · Manuale utente MBa8MPxL · Scheda tecnica i.MX 8M Plus · Manuale di riferimento i.MX 8M Plus · Documentazione U-Boot: · Documentazione PTXdist: · Documentazione Yocto: · Wiki TQ-Support:

www.denx.de/wiki/U-Boot/Documentation www.ptxdist.de www.yoctoproject.org/docs/ Support-Wiki TQMa8MPxL

Manuale dell'utente l TQMa8MPxL UM 0105 l © 2024, TQ-Systems GmbH

Pagina 4

2.

BREVE DESCRIZIONE

Questo manuale utente descrive l'hardware del TQMa8MPxL a partire dalla revisione 0100, in combinazione con l'MBa8MPxL a partire dalla revisione 0100 e fa riferimento ad alcune impostazioni del software. Un certo derivato TQMa8MPxL non fornisce necessariamente tutte le funzionalità descritte in questo Manuale dell'utente.

Il presente Manuale dell'utente non sostituisce il Manuale di riferimento di i.MX 8M Plus (1), né la Scheda tecnica di i.MX 8M Plus (2), né qualsiasi altro documento di NXP.

TQMa8MPxL è un minimodulo universale basato sulla famiglia di CPU i.MX 53M basata su NXP ARM® Cortex®-A8, vedere anche la Tabella 4.

2.1

Funzioni e caratteristiche principali

Il TQMa8MPxL amplia la gamma di prodotti TQ-Systems GmbH e offre prestazioni di calcolo eccezionali. Tutti i segnali essenziali di i.MX 8M Plus vengono instradati ai pad LGA TQMa8MPxL. Non ci sono quindi restrizioni per i clienti che utilizzano TQMa8MPxL rispetto a un design personalizzato integrato. Tutti i componenti essenziali come CPU, LPDDR4, eMMC e PMIC sono già integrati nel TQMa8MPxL. Le caratteristiche principali del TQMa8MPxL sono:

· CPU NXP i.MX 64M Plus a 8 bit, fino a 4 × ARM Cortex®-A53 e 1 × Cortex®-M7 o Plus Dual, Plus Quad 4 Lite, Plus Quad 6 Video, Plus Quad 8 ML/AI

· Fino a 4 Gbyte LPDDR32-4 a 4000 bit · Fino a 256 Gbyte eMMC NAND Flash, eMMC standard 5.1 · Fino a 256 Mbyte QSPI NOR Flash · EEPROM da 64 Kbit (opzionale) · Sensore di temperatura + EEPROM · RTC (opzionale) · Trust Secure Element (opzionale) · Circuito integrato di gestione dell'alimentazione NXP PCA9450 · Tutti i segnali i.MX 8M Plus essenziali vengono instradati ai pad LGA TQMa8MPxL · Vol alimentazione singolatage 5 V

2.2

Schema a blocchi della CPU

Figura 1:

Schema a blocchi i.MX 8M Plus (Fonte: NXP)

Manuale dell'utente l TQMa8MPxL UM 0105 l © 2024, TQ-Systems GmbH

3.

ELETTRONICA

Le informazioni fornite in questo Manuale dell'utente sono valide solo in connessione con il boot loader personalizzato, preinstallato sul TQMa8MPxL, e il BSP fornito da TQ-Systems GmbH, vedere anche il capitolo 4.

Pagina 5

PMIC NXP PCA9450C

Supervisore

i.MX 8M Plus

RAM LPDDR4

e-MMC 5.1 (opzionale)

1x QSPI-NORFlash (opzionale)

RTC (opzionale) TSE (opzionale) EEPROM (opzionale)

Sensore di temperatura/EEPROM

PCIe RGMII USB3.0 UART

I2C GPIO SPI HDMI CSI DSI

5 Volt

5 Volt

Pad LGA 366 Figura 2: diagramma a blocchi TQMa8MPxL (semplificato)

3.1

Interfacce con altri sistemi e dispositivi

3.1.1

Multiplexing dei pin

È necessario prendere nota delle molteplici configurazioni dei pin delle diverse unità funzionali interne di i.MX 8M Plus. L'assegnazione dei pin nella Tabella 3 si riferisce a un TQMa8MPxL con CPU i.MX 8M Plus Quad 8 ML/AI in combinazione con la scheda carrier MBa8MPxL. NXP fornisce uno strumento che mostra il multiplexing e semplifica la selezione e la configurazione (i.MX Pins Tool NXP Tool). Le caratteristiche elettriche e dei pin devono essere ricavate dalla documentazione di i.MX 8M Plus e PMIC, vedere Tabella 40.

Attenzione: distruzione o malfunzionamento, multiplexing dei pin

A seconda della configurazione, molti pin dell'i.MX 8M Plus possono fornire diverse funzioni. Si prega di prendere nota delle informazioni relative alla configurazione di questi pin nel Manuale di riferimento i.MX 8M Plus (1), prima dell'integrazione o dell'avvio della scheda carrier/Starterkit. Una programmazione impropria tramite il software operativo può causare malfunzionamenti, deterioramento o distruzione del TQMa8MPxL.

Si tenga conto delle descrizioni riportate nelle tabelle seguenti: – DNC: questi pin non devono mai essere collegati e devono essere lasciati aperti.

Si prega di contattare il supporto TQ per i dettagli.

Manuale dell'utente l TQMa8MPxL UM 0105 l © 2024, TQ-Systems GmbH

Pagina 6

3.1.1.1 Pinout TQMa8MPxL Il TQMa8MPxL ha un totale di 366 pad LGA. Il TQMa8MPxL è saldato e quindi collegato in modo permanente alla scheda portante. Non è banale e non è consigliabile rimuovere il TQMa8MPxL. La tabella seguente mostra il pad-out di TQMa8MPxL, in alto view tramite TQMa8MPxL.

Tabella 2: Pinout TQMa8MPxL, in alto view tramite TQMa8MPxL

Un 22

BCDEFGHJKLMNPRTUVWY AA AB

USB1_ USB1_ D_P D_N

Terra

DSI_ DSI_ D1_N D1_P

Terra

DSI_ DSI_ D3_N D3_P

Terra

CSI1_ CSI1_ CLK_N CLK_P

Terra

CSI2_ CSI2_ D0_N D0_P

Terra

CSI2_ CSI2_ D2_N D2_P

Terra

PCIE_RE PCIE_RE F_CLKN F_CLKP

22

21

USB1_TX_N

Terra

ISO_14 ISO_14 443_LB 443_LA

Terra

DSI_ DSI_ CLK_N CLK_P

Terra

CSI1_D0_N

CSI1_D0_P

Terra

CSI1_D2_N

CSI1_D2_P

Terra

CSI2_D1_N

CSI2_D1_P

Terra

CSI2_D3_N

CSI2_D3_P

Terra

PCIE_TXN

PCIE_TXP

21

20

USB1_TX_P

USB1_RX_N

Terra

DSI_D0_N

DSI_D0_P

Terra

DSI_ DSI_ D2_N D2_P

Terra

CSI1_ CSI1_ D1_N D1_P

Terra

CSI1_ CSI1_ D3_N D3_P

Terra

CSI2_ CSI2_ CLK_N CLK_P

Terra

PCIE_RXN

PCIE_RXP

LVDS1_D3_P

Terra

20

19GND

USB1_ USB2 RX_P _D_N

USB2 GPIO1 USB1 _DNU _IO11 _DNU

Terra

18

USB2_TX_N

Terra

USB2_ GPIO1 D_P _IO15

Terra

USB1_VBUS

USB1 _OTG _ID

USB1_OTG_OC

ISO_78_CLK

Terra

JTAG_ JTAG_ TDOTCK

Terra

BOOT_ BOOT_ BOOT_ TEMP_ MODE3 MODE2 MODE1 EVENT#

M7_NMI

USB1_OTG_PWR

ISO_78_IO16

ISO_78_IO16

ISO_78_RST

Terra

JTAG_ JTAG_TMS TDI

Terra

BOOT_ RTC_ MODE0 EVENTO#

Terra

Terra

V_SD1

LVDS1_D3_N

LVDS1_CLK_P

19

CLK1_IN

Terra

LVDS1_D2_P

LVDS1_CLK_N

18

17

USB2_TX_P

USB2_RX_N

Terra

GPIO1 USB2_ _IO14 VBUS

CLK2_USCITA

CLK1_ LVDS1 LVDS1 USCITA _D1_P _D2_N

Terra

17

16GND

USB2_ GPIO3 RX_P _IO14

Terra

GPIO1_IO00

15

V_SAI2_ SAI3_ SPDIF

V_SAI1_ SAI5

Terra

V_ GPIO1 LICELL _IO01

14GND

I2C4_ I2C1_ SCL SCL

Terra

GPIO1_IO03

Terra

CLK2_ LVDS1 IN _D1_N

Terra

LVDS1_D0_P

16

QSPI_A QSPI_A _SS0# _SCLK

Terra

LVDS0_D3_P

LVDS1_D0_N

15

QSPI_A_DATA0

Terra

LVDS0_ LVDS0_ CLK_P D3_N

Terra

14

13

SAI3_TXD0

I2C4_SDA

I2C2_SCL

I2C1_SDA

Terra

QSPI_A QSPI_A LVDS0_ _DATA1 _DATA2 CLK_N

Terra

LVDS0_D2_P

13

12

SAI3_RXD0

SAI3_TXC

I2C2_SDA

Terra

GPIO1_IO06

UART1 QSPI_A _RXD _DATA3

Terra

LVDS0_D1_P

LVDS0_D2_N

12

11GND

SAI3_TXFS

Terra

GPIO1 GPIO1 _IO09 _IO07

UART1_TXD

Terra

LVDS0 LVDS0 _D0_P _D1_N

TERRA 11

10

GPIO4_IO29

Terra

SAI3_MCLK

PWM3

Terra

I2C6_SCL

I2C6_SDA

LVDS0 _D0_N

ENET _QOS _TD3

V_ENET 10

9

GPIO4_IO28

ENET_Q OS_EVE NT2_IN

GPIO4_IO25

Terra

GPIO5 GPIO5 _IO27 _IO26

RFU

Terra

Terra

V_SD2

GPIO2_IO07

UART2 UART2 _TXD _RXD

ENET _QOS _TD2

Terra

ENET

_QOS9 _TXC

8

ENET_QO GND S_EVENTO GND

2_FUORI

GPT2_CLK

PMIC_ GND WDOG_ GND

FUORI#

RFU

RFU

Terra

GPIO2 UART3 _IO06 _RXD

ENET ENET GND _QOS_ _QOS

TX_CTL_TD0

ENET_QOS8_TD1

7

GPIO4_IO22

Terra

GPIO4_IO24

Terra

RESETTA _IN#

RESETTA _OUT#

AccesoSpento

Terra

Terra

SD2_WP

SD2_RST#

UART3 GPIO2 _TXD _IO11

ENET _QOS _RD3

Terra

ENET

_QOS7 _RXC

6

GPIO4_IO27

GPIO4_IO21

Terra

Terra

PMIC_RST#

PMIC_WDOG_

IN#

UART4_TXD

UART4_RXD

ECSPI3_MOSI

Terra

GPIO5 GPIO5 _IO05 _IO03

Terra

ECSPI2 SD2_ _SS0 CD#

Terra

SD2_CMD

GPIO2_IO10

Terra

ENET ENET _QOS_ _QOS MDIO _RD2

TERRA 6

5GND

Terra

Terra

Terra

Terra

Terra

V_3V3 ECSPI3 ECSPI3 ECSPI3 GPIO5 ECSPI2 ECSPI2 ECSPI2 _SD _SS0 _MISO _SCLK _IO04 _SCLK _MISO _MOSI

Terra

SD2_DATI3

SD2_DATI2

SD2_DATI1

SD2_DATI0

ENET_QOS_MDC

Terra

ENET

_QOS5 _RD1

4

V_5V_IN

V_5V V_5V _IN _IN

Terra

Terra

Terra

ENET0 ENET1 _INT# _INT#

Terra

ENET0 ENET1 _RST# _RST#

Terra

GPIO4 ENET_ ENET_ SD2_ _IO18 RX_CTL TX_CTL CLK

Terra

EARC_ HDMI_ AUX CEC

Terra

ENET_ ENET QOS_ _QOS RX_CTL _RD0

4

3

V_5V_IN

V_5V V_5V _IN _IN

Terra

Terra

Terra

Terra

ENET ENET _MDC _MDIO

Terra

ENET ENET _RD2 _RD3

Terra

ENET ENET _TD2 _TD3

Terra

HDMI_ HDMI_ TXC_N TXC_P

Terra

HDMI_HPD

Terra

HDMI_

DDC_3SCL

2

GPIO3_IO20

Terra

GPIO3 GPIO3 _IO21 _IO19

Terra

GPIO5 GPIO5 _IO09 _IO08

Terra

ENET_RD0

ENET_RD1

Terra

ENET _TD0

ENET _TD1

Terra

ENET_TXC

GPIO4_IO19

Terra

HDMI_TX0_N

HDMI_TX0_P

HDMI_TX2_N

HDMI_TX2_P

HDMI_ DDC_ SDA

2

1

CAN_F CAN_F CAN_F CAN_F D1_TX D1_RX D2_TX D2_RX

Terra

GPIO5 GPIO5 _IO07 _IO06

Terra

ENET_RXC

GPIO4_IO20

Terra

V_1V8 V_3V3

Terra

EARC_N EARC_P _HPD _UTIL

Terra

HDMI_ HDMI_ TX1_N TX1_P

Terra

1

ABCDEFGHJKLMNPRTUVWY AA AB

Manuale dell'utente l TQMa8MPxL UM 0105 l © 2024, TQ-Systems GmbH

Pagina 7

3.1.1.2 Segnali TQMa8MPxL

I dettagli sulle caratteristiche elettriche dei singoli pin e delle interfacce devono essere presi dalla documentazione di i.MX 8M Plus (1), (2), (3), nonché dalla scheda tecnica PMIC (4).

Tabella 3:

CPU Ball

G10 F8 G8 G12 AF16 AD16 AF14 AE14 K28 K29 L28 L29 E22 D22 E18 D18 E20 D20 E24 D24 E26 D26 B23 A23 B25 A25 B24 A24 B22 A22 B21 A21 B18 A18 B16 A16 B17 A17 B19 A19 B20 A 20

TQMa8MPxL, segnali

Segnale

BOOT_MODE0 BOOT_MODE1 BOOT_MODE2 BOOT_MODE3 CAN_FD1_RX CAN_FD1_TX CAN_FD2_RX CAN_FD2_TX CLK1_IN CLK1_OUT CLK2_IN CLK2_OUT CSI1_CLK_N CSI1_CLK_P CSI1_D0_N CSI1_D0_P CSI1_D1_N CSI1_D1_P 1_N CSI2_D1_P CSI2_D1_N CSI3_D1_P CSI3_CLK_N CSI2_CLK_P CSI2_D2_N CSI0_D2_P CSI0_D2_N CSI1_D2_P CSI1_D2_N CSI2_D2_P CSI2_D2_N CSI3_D2_P DSI_CLK_N DSI_CLK_P D3_N DSI_D0_P DSI_D0_N DSI_D1_P DSI_D1_N DSI_D2_P DSI_D2_N DSI_D3_P

Gruppo

BOOT BOOT BOOT BOOT CAN CAN CAN CAN CLK CLK CLK CLK

CSI CSI CSI CSI CSI CSI CSI CSI CSI CSI CSI CSI CSI CSI CSI CSI CSI DSI DSI DSI DSI DSI DSI DSI DSI DSI

Direttore

Livello

TQMa8MPxL-Pad

I

3.3 Volt

T18

I

3.3 Volt

T19

I

3.3 Volt

R19

I

3.3 Volt

P19

I

V_SAI1_SAI5

C1

O

V_SAI1_SAI5

B1

I

V_SAI1_SAI5

E1

O

V_SAI1_SAI5

D1

I

1.8 Volt

W18

O

1.8 Volt

W17

I

1.8 Volt

W16

O

1.8 Volt

V17

I

1.8 Volt

L22

I

1.8 Volt

Numero di modello: M22

I

1.8 Volt

J21

I

1.8 Volt

K21

I

1.8 Volt

K20

I

1.8 Volt

L20

I

1.8 Volt

Numero di modello: M21

I

1.8 Volt

N21

I

1.8 Volt

N20

I

1.8 Volt

P20

I

1.8 Volt

T20

I

1.8 Volt

Minore 20

I

1.8 Volt

P22

I

1.8 Volt

R22

I

1.8 Volt

R21

I

1.8 Volt

T21

I

1.8 Volt

Minore 22

I

1.8 Volt

V22

I

1.8 Volt

V21

I

1.8 Volt

W21

O

1.8 Volt

F21

O

1.8 Volt

G21

O

1.8 Volt

D20

O

1.8 Volt

E20

O

1.8 Volt

E22

O

1.8 Volt

F22

O

1.8 Volt

G20

O

1.8 Volt

H20

O

1.8 Volt

H22

O

1.8 Volt

J22

Manuale dell'utente l TQMa8MPxL UM 0105 l © 2024, TQ-Systems GmbH

3.1.1.2 Segnali TQMa8MPxL (continua)

Tabella 3:

CPU AH20 AJ21 AH21 AJ22 AF6 AJ3 AD6 AH4 AJ9 AH8 AC10 AF10 AH9 AJ8 AH28 AH29 AG29 AG28 AF29 AF28 AE28 AE29 AC25 AE26 AF26 AD24 AF24 AE24 AJ14

AH16 AD10 AE10 AH10 AH12 AF12 AJ12 AJ11 AJ10 AH11 AD12 AE12 AH13 AH14

B4 –

TQMa8MPxL, segnali (continua)

Segnale ECSPI2_MISO ECSPI2_MOSI ECSPI2_SCLK ECSPI2_SS0 ECSPI3_MISO ECSPI3_MOSI ECSPI3_SCLK ECSPI3_SS0 ENET0_RST# ENET0_INT# ENET1_RST# ENET1_INT# ENET_MDC ENET_MDIO ENET_QOS_MDC ENET_QOS_MDIO ENET_QOS_RD0 ENET_Q OS_RD1 ENET_QOS_RD2 ENET_QOS_RD3 ENET_QOS_RX_CTL ENET_QOS_RXC ENET_QOS_TD0 ENET_QOS_TD1 ENET_QOS_TD2 ENET_QOS_TD3 ENET_QOS_TX_CTL ENET_QOS_TXC ENET_QOS_EVENT2_OUT

ENET_QOS_EVENT2_IN ENET_RD0 ENET_RD1 ENET_RD2 ENET_RD3 ENET_RX_CTL ENET_RXC ENET_TD0 ENET_TD1 ENET_TD2 ENET_TD3 ENET_TX_CLK ENET_TX_CTL ENET_TXC M7_NMI RTC_EVENT# TEMP_EVENT#

Gruppo

ECSPI ECSPI ECSPI ECSPI ECSPI ECSPI ECSPI ENET ENET ENET ENET ENET ENET ENET ENET ENET ENET ENET ENET ENET ENET ENET ENET ENET ENET ENET ENET

ENET

ENET ENET ENET ENET ENET ENET ENET ENET ENET ENET ENET ENET ENET Evento Evento Evento

Direttore

Livello

I

1.8 Volt

O

1.8 Volt

O

1.8 Volt

O

1.8 Volt

I

3.3 Volt

O

3.3 Volt

O

3.3 Volt

O

3.3 Volt

O

V_SAI1_SAI5

I

V_SAI1_SAI5

O

V_SAI1_SAI5

I

V_SAI1_SAI5

O

V_SAI1_SAI5

Entrata/uscita

V_SAI1_SAI5

O

V_ENET

Entrata/uscita

V_ENET

I

V_ENET

I

V_ENET

I

V_ENET

I

V_ENET

I

V_ENET

I

V_ENET

O

V_ENET

O

V_ENET

O

V_ENET

O

V_ENET

O

V_ENET

O

V_ENET

O

V_SAI2_SAI3_SPDIF

I

V_SAI2_SAI3_SPDIF

I

V_SAI1_SAI5

I

V_SAI1_SAI5

I

V_SAI1_SAI5

I

V_SAI1_SAI5

I

V_SAI1_SAI5

I

V_SAI1_SAI5

O

V_SAI1_SAI5

O

V_SAI1_SAI5

O

V_SAI1_SAI5

O

V_SAI1_SAI5

O

V_SAI1_SAI5

O

V_SAI1_SAI5

O

V_SAI1_SAI5

I

3.3 Volt

O

OD

O

OD

Pagina 8

TQMa8MPxL N5 P5 M5 P6 J5 J6 K5 H5 K4 G4 L4 H4 H3 J3 Y5 Y6 AB4 AB5 AA6 Y7 AA4 AB7 AA8 AB8 Y9

AA10 Y8 AB9 B8 B9 J2 K2 L3 M3 P4 K1 M2 N2 P3 R3 L1 R4 R2 V19 U18 U19

Manuale dell'utente l TQMa8MPxL UM 0105 l © 2024, TQ-Systems GmbH

3.1.1.2 Segnali TQMa8MPxL (continua)

Tabella 3:

CPU A7 E8 D6 A3 F6 B8 D8 A4 B5 U26

AA29

W25

W26 R26 AC14 AD14 AE16 AC12 AJ13 AH17

AJ16

AJ17

AH15

AJ15

AJ19

AJ18

AE18

AD18

AC18 AF20 AC20 AD20 AE20 AJ4 AE6 AJ7 AH23 AH22 AJ23 AD22 AC22 AF22 AE22 AJ25 AH25 AJ26

TQMa8MPxL, segnali (continua)

Segnale GPIO1_IO00 GPIO1_IO01 GPIO1_IO03 GPIO1_IO06 GPIO1_IO07 GPIO1_IO09 GPIO1_IO11 GPIO1_IO14 GPIO1_IO15 GPIO2_IO06

GPIO2_IO07

GPIO2_IO10

GPIO2_IO11 GPIO3_IO14 GPIO3_IO19 GPIO3_IO20 GPIO3_IO21 GPIO4_IO18 GPIO4_IO19 GPIO4_IO21

GPIO4_IO22

GPIO4_IO24

GPIO4_IO25

GPIO4_IO27

GPIO4_IO28

GPIO4_IO29

GPIO5_IO03

GPIO5_IO04

GPIO5_IO05 GPIO5_IO06 GPIO5_IO07 GPIO5_IO08 GPIO5_IO09 GPIO5_IO27 GPIO5_IO26 GPT2_CLK EARC_AUX EARC_N_HPD EARC_P_UTIL HDMI_CEC HDMI_DDC_SCL HDMI_DDC_SDA HDMI_HPD HDMI_TX0_N HDMI_TX0_P HDMI_TX1_N

Gruppo GPIO GPIO GPIO GPIO GPIO GPIO GPIO GPIO GPIO

GPIO

GPIO

GPIO GPIO GPIO GPIO GPIO GPIO GPIO GPIO

GPIO

GPIO

GPIO

GPIO

GPIO

GPIO

GPIO

GPIO

GPIO GPIO GPIO GPIO GPIO GPIO GPIO GPT HDMI HDMI HDMI HDMI HDMI HDMI HDMI HDMI HDMI

Direttore

Livello

Entrata/uscita

3.3 Volt

Entrata/uscita

3.3 Volt

Entrata/uscita

3.3 Volt

Entrata/uscita

3.3 Volt

Entrata/uscita

3.3 Volt

Entrata/uscita

3.3 Volt

Entrata/uscita

3.3 Volt

Entrata/uscita

3.3 Volt

Entrata/uscita

3.3 Volt

Entrata/uscita

V_SD1

Entrata/uscita

V_SD1

Entrata/uscita

V_SD1

Entrata/uscita

V_SD1

Entrata/uscita

1.8 Volt

Entrata/uscita

V_SAI1_SAI5

Entrata/uscita

V_SAI1_SAI5

Entrata/uscita

V_SAI1_SAI5

Entrata/uscita

V_SAI1_SAI5

Entrata/uscita

V_SAI1_SAI5

I/O V_SAI2_SAI3_SPDIF

I/O V_SAI2_SAI3_SPDIF

I/O V_SAI2_SAI3_SPDIF

I/O V_SAI2_SAI3_SPDIF

I/O V_SAI2_SAI3_SPDIF

I/O V_SAI2_SAI3_SPDIF

I/O V_SAI2_SAI3_SPDIF

I/O V_SAI2_SAI3_SPDIF

I/O V_SAI2_SAI3_SPDIF

I/O V_SAI2_SAI3_SPDIF

Entrata/uscita

1.8 Volt

Entrata/uscita

1.8 Volt

I

1.8 Volt

O

1.8 Volt

Entrata/uscita

3.3 Volt

Entrata/uscita

3.3 Volt

Entrata/uscita

3.3 Volt

O

1.8 Volt

I

1.8 Volt

O

1.8 Volt

O

1.8 Volt

O

1.8 Volt

Entrata/uscita

1.8 Volt

I

1.8 Volt

O

1.8 Volt

O

1.8 Volt

O

1.8 Volt

Pagina 9

TQMa8MPxL E16 E15 E14 E12 E11 D11 E19 D17 D18 U8 U9 V6 W7 C16 D2 A2 C2 N4 T2 B6 A7 C7 C9 A6 A9 A10 M6 L5 L6 H1 G1 G2 F2 E9 F9 D8 V4 T1 U1 W4 AB3 AB2 Y3 V2 W2 W1

Manuale dell'utente l TQMa8MPxL UM 0105 l © 2024, TQ-Systems GmbH

3.1.1.2 Segnali TQMa8MPxL (continua)

Tabella 3: TQMa8MPxL, segnali (continua)

processore

AH26 AJ27 AH27 AJ24 AH24 AC8 AH7 AH6 AE8 AF8 AD8 Y29 Y28

G18 G16 F14 G14 G28 F29 E28 D29 F28 E29 H28 G29 J28 H29 B28 A28 B26 A26 B27 A27 C28 B29 D28 C29

Segnale

HDMI_TX1_P HDMI_TX2_N HDMI_TX2_P HDMI_TXC_N HDMI_TXC_P I2C1_SCL I2C1_SDA I2C2_SCL I2C2_SDA I2C4_SCL I2C4_SDA I2C6_SCL I2C6_SDA ISO_7816_CLK ISO_7816_IO1 ISO_7816_IO2 ISO_7816_RST ISO _14443_LA ISO_14443_LB JTAG_TCK JTAG_TDIJTAG_TDO JTAG_TMS LVDS0_CLK_N LVDS0_CLK_P LVDS0_D0_N LVDS0_D0_P LVDS0_D1_N LVDS0_D1_P LVDS0_D2_N LVDS0_D2_P LVDS0_D3_N LVDS0_D3_P LVDS1_CLK_N LVDS1_CLK_P LVDS1_D0_N LVDS 1_D0_P LVDS1_D1_N LVDS1_D1_P LVDS1_D2_N LVDS1_D2_P LVDS1_D3_N LVDS1_D3_P

Gruppo

Direttore

Cavo HDMI

O

Cavo HDMI

O

Cavo HDMI

O

Cavo HDMI

O

Cavo HDMI

O

I2C

O

I2C

Entrata/uscita

I2C

O

I2C

Entrata/uscita

I2C

O

I2C

Entrata/uscita

I2C

O

I2C

Entrata/uscita

ISO_7816

I

ISO_7816

Entrata/uscita

ISO_7816

Entrata/uscita

ISO_7816

I

ISO_14443

Entrata/uscita

ISO_14443

Entrata/uscita

JTAG

I

JTAG

I

JTAG

O

JTAG

I

LVDS

O

LVDS

O

LVDS

O

LVDS

O

LVDS

O

LVDS

O

LVDS

O

LVDS

O

LVDS

O

LVDS

O

LVDS

O

LVDS

O

LVDS

O

LVDS

O

LVDS

O

LVDS

O

LVDS

O

LVDS

O

LVDS

O

LVDS

O

Livello

1.8 V 1.8 V 1.8 V 1.8 V 1.8 V 3.3 V 3.3 V 3.3 V 3.3 V 3.3 V 3.3 V V_SD1 V_SD1 3.3 V 3.3 V 3.3 V 3.3 V 3.3 V 3.3 V 3.3 V 3.3 V 3.3 V 3.3 V 1.8 V 1.8 V 1.8 V 1.8 V 1.8 V 1.8 V 1.8 V 1.8 V 1.8 V 1.8 V 1.8 V 1.8 V 1.8 V 1.8 V 1.8 V 1.8 V 1.8 V 1.8 V 1.8 V 1.8 V

Pagina 10

TQMa8MPxL Y1 Y2 AA2 U3 V3 C14 D13 C13 C12 B14 B13 V10 W10 J19 K18 J18 L18 D21 C21 M19 P18 L19 N18 Y13 Y14 Y10 Y11

AA11 AA12 AB12 AB13 AA14 AA15 AB18 AB19 AB15 AB16 Y16 Y17 AA17 AA18 AA19 AA20

Manuale dell'utente l TQMa8MPxL UM 0105 l © 2024, TQ-Systems GmbH

3.1.1.2 Segnali TQMa8MPxL (continua)

Tabella 3:

CPU E16 D16 B14 A14 B15 A15 AJ6 R25 L25 L24 N24 N25 L26

B6 AJ20 AF18 AC16 AH19 AH18 AD29 AB29 AB28 AC28 AC29 AA26 AA25 AD28 AC26

TQMa8MPxL, segnali (continua)

Segnale PCIE_REF_CLKN PCIE_REF_CLKP PCIE_RXN PCIE_RXP PCIE_TXN PCIE_TXP PWM3 QSPI_A_DATA0 QSPI_A_DATA1 QSPI_A_DATA2 QSPI_A_DATA3 QSPI_A_SCLK QSPI_A_SS0# PMIC_RST# PMIC_WDOG_IN# PMIC_WDOG_OUT# RESET_ IN# RESET_OUT# SAI3_MCLK SAI3_RXD0 SAI3_TXFS SAI3_TXC SAI3_TXD0 SD2_CD# SD2_CLK SD2_CMD SD2_DATA0 SD2_DATA1 SD2_DATA2 SD2_DATA3 SD2_RST# SD2_WP

Gruppo PCIe PCIe PCIe PCIe PCIe PCIe PWM QSPI QSPI QSPI QSPI QSPI QSPI Reset Reset Reset Reset Reset SAI SAI SAI SAI SAI SD SD SD SD SD SD SD SD SD

Direttore

Livello

Entrata/uscita

1.8 Volt

Entrata/uscita

1.8 Volt

I

1.8 Volt

I

1.8 Volt

O

1.8 Volt

O

1.8 Volt

O

3.3 Volt

Entrata/uscita

1.8 Volt

Entrata/uscita

1.8 Volt

Entrata/uscita

1.8 Volt

Entrata/uscita

1.8 Volt

O

1.8 Volt

O

1.8 Volt

I

1.8 Volt

I

3.3 Volt

O

3.3 Volt

I

OD

O

OD

O

V_SAI2_SAI3_SPDIF

I

V_SAI2_SAI3_SPDIF

O

V_SAI2_SAI3_SPDIF

O

V_SAI2_SAI3_SPDIF

O

V_SAI2_SAI3_SPDIF

I

1.8/ 3.3 V

O

1.8/ 3.3 V

Entrata/uscita

1.8/ 3.3 V

Entrata/uscita

1.8/ 3.3 V

Entrata/uscita

1.8/ 3.3 V

Entrata/uscita

1.8/ 3.3 V

Entrata/uscita

1.8/ 3.3 V

O

1.8/ 3.3 V

I

1.8/ 3.3 V

Pagina 11

TQMa8MPxL Y22 AA22 W20 Y20 AA21 AB21 D10 V14 V13 W13 W12 W15 V15 E6 F6 F8 E7 F7 C10 A12 B11 B12 A13 R6 T4 U6 W5 V5 U5 T5 U7 T7

Manuale dell'utente l TQMa8MPxL UM 0105 l © 2024, TQ-Systems GmbH

Pagina 12

3.1.1.2 Segnali TQMa8MPxL (continua)

Tabella 3:

CPU G22 W29 W28 V28 V29 U25 AA28 AJ5 AH5 E10 D10 B11 B7 A6 A5 B9 A9 B10 A10 A11 E14 D14 E12 B12 A12 B13 A13 D12

AA24 Y11 AA11 U24 –

TQMa8MPxL, segnali (continua)

AccesoSpento

Segnale

Gruppo

Direttore

SNVS

I

Livello 1.8 V

TQMa8MPxL G7

UART1_RXD

UART

I

V_SD1

V12

UART1_TXD UART2_RXD UART2_TXD UART3_RXD UART3_TXD

UART

O

V_SD1

V11

UART

I

V_SD1

W9

UART

O

V_SD1

V9

UART

I

V_SD1

V8

UART

O

V_SD1

V7

UART4_RXD

UART

I

3.3 Volt

H6

UART4_TXD USB1_D_N USB1_D_P USB1_DNU USB1_OTG_ID USB1_OTG_OC USB1_OTG_PWR USB1_RX_N USB1_RX_P USB1_TX_N USB1_TX_P USB1_VBUS USB2_D_N USB2_D_P USB2_DNU USB2_RX_N USB2_RX_P USB2_TX_N USB2_TX_P USB2_V AUTOBUS

Terra

V_1V8 V_3V3 V_3V3_SD V_5V_IN V_ENET V_LICELL V_SAI1_SAI5 V_SAI2_SAI3_SPDIF V_SD1 V_SD2 RFU

UART

O

3.3 Volt

G6

USB

Entrata/uscita

3.3 Volt

C22

USB

Entrata/uscita

3.3 Volt

B22

USB

3.3 Volt

F19

USB

I

3.3 Volt

G18

USB

I

3.3 Volt

H19

USB

O

3.3 Volt

H18

USB

I

3.3 Volt

B20

USB

I

3.3 Volt

B19

USB

O

3.3 Volt

A21

USB

O

3.3 Volt

A20

USB

P

5 Volt

F18

USB

Entrata/uscita

3.3 Volt

C19

USB

Entrata/uscita

3.3 Volt

C18

USB

3.3 Volt

D19

USB

I

3.3 Volt

B17

USB

I

3.3 Volt

B16

USB

O

3.3 Volt

A18

USB

O

3.3 Volt

A17

USB

P

5 Volt

E17

A11, A14, A16, A19, A5, A8, AA1, AA13, AA16, AA3, AA5, AA7, AA9, AB11, AB14, AB17, AB20, AB6, B10, B18, B2, B21, B5, B7, C11, C15, C17, C20, C5, C6, C8, D12, D14, D16, D22, D3, D4, D5, D6, D7, D9, E10, E13, E18, E2, E21, E3, E4, E5, E8, F1, F20, F3, F4, F5, G19, G22, G3, G8, H2, H21, H7, H9, J1, J20, J4, K19, K22, K3, K6, L2, L21, M1, M18, M20, M4, N19, N22, N3, N6, P2, P21, R1, R18, R20, R5, R7, R9, T22, T3, T6, T8, U2, U21, U4, V1, V16, V18, V20, W11, W14, W19, W22, W3, W6, W8, Y12, Y15, Y18, Y21, Y4

Energia

Broncio

1.8V 1

Energia

Broncio

3.3V 1

Energia

Broncio

3.3V 2

Energia

Spillo

5 Volt

Energia

Spillo

1.8 / 3.3 V

Energia

Spillo

3 Volt

Energia

Spillo

1.8 / 3.3 V

Energia

Spillo

1.8 / 3.3 V

Energia

Spillo

1.8 / 3.3 V

Energia

Broncio

1.8 / 3.3 V

Riservato per uso futuro. Non connettersi.

N1 P1 G5 A3, A4, B3, B4, C3, C4 AB10 D15 B15 A15 Y19 T9 G9, H8, R8

1: Carico massimo di 500 mA. 2: Carico massimo di 400 mA.

Manuale dell'utente l TQMa8MPxL UM 0105 l © 2024, TQ-Systems GmbH

Pagina 13

3.2

Componenti del sistema

3.2.1

i.MX 8M Plus

3.2.1.1 Derivati i.MX 8M Plus

A seconda della versione TQMa8MPxL, viene assemblato uno dei seguenti derivati i.MX 8M Plus.

Tabella 4: derivati i.MX 8M Plus

Versione TQMa8MPxL TQMa8MPDL-XX TQMa8MPQLL-AA TQMa8MPQL-AA TQMa8MPQL-AB

Derivata i.MX 8M Plus i.MX 8M Plus Dual i.MX 8M Plus Quad 4 Lite i.MX 8M Plus Quad 6 Video i.MX 8M Plus Quad 8 ML/AI

Clock i.MX 8M Plus A53: 1.6 GHz, M7: 800 MHz A53: 1.6 GHz, M7: 800 MHz A53: 1.6 GHz, M7: 800 MHz A53: 1.6 GHz, M7: 800 MHz

Intervallo di temperatura 40 °C … +105 °C 40 °C … +105 °C 40 °C … +105 °C 40 °C … +105 °C

3.2.1.2 Errata i.MX 8M Plus Attenzione: Distruzione o malfunzionamento, errata i.MX 8M Plus

Si prega di prendere nota delle attuali errata di i.MX 8M Plus (5).

3.2.1.3 Modalità di avvio

L'i.MX 8M Plus ha una ROM con boot loader integrato. Dopo il rilascio di PMIC_POR#, il controller di sistema (SCU) si avvia dalla ROM interna e quindi carica l'immagine del programma dal dispositivo di avvio selezionato. Per esample, è possibile selezionare l'eMMC integrato o la QSPI NOR Flash opzionale come dispositivo di avvio predefinito. Le seguenti origini di avvio sono supportate da TQMa8MPxL:

· eMMC · QSPI NOR Flash · USB OTG · Scheda SD

In alternativa, un'immagine può essere caricata nella RAM interna utilizzando il downloader seriale. Maggiori informazioni sul flusso di avvio sono disponibili nel Manuale di riferimento (1) e nella Scheda tecnica (2) di i.MX 8M Plus.

3.2.1.4 Configurazione di avvio

L'i.MX 8M Plus utilizza quattro segnali BOOT_MODE disponibili sui pad LGA del TQMa8MPxL. Questi richiedono un cablaggio pull-up/pull-down a 3.3 V e terra. L'esatto comportamento di avvio dipende dal valore del registro BT_FUSE_SEL. L'avvio da USDHC1 è possibile solo su i.MX 8M Plus dopo aver masterizzato gli eFuse. La tabella seguente mostra il comportamento in dipendenza di BT_FUSE_SEL e della modalità di avvio selezionata:

Tabella 5: Configurazione di avvio i.MX 8M Plus

Origine di avvio

Avvio da eFuse USB Serial Downloader Avvio da USDHC3 (eMMC) Avvio da USDHC2 (scheda SD) Avvio da NAND (non supportato) Avvio da QSPI (lettura 3 byte) Avvio da QSPI (Hyperflash) (non supportato) Avvio da eCSPI (non supportato ) (Riservato)

BOOT_MODE3 0 0 0 0 0 0

0

1 1

BOOT_MODE2 0 0 0 0 1 1

1

0 0

BOOT_MODE1 0 0 1 1 0 1

1

0 0

BOOT_MODE0 0 1 0 1 x 0

1

0 1

Manuale dell'utente l TQMa8MPxL UM 0105 l © 2024, TQ-Systems GmbH

Pagina 14

3.2.2

Memoria

3.2.2.1 SDRAM LPDDR4

L'interfaccia di memoria dell'i.MX 8M Plus supporta la memoria DDR4 e LPDDR4 (bus a 32 bit) con un clock rate massimo di 2.0 GHz, che soddisfa lo standard JEDEC LPDDR4-4000. Il TQMa8MPxL utilizza esclusivamente LPDDR4. È supportato un massimo di 8 Gbyte di SDRAM LPDDR4.

3.2.2.2 eMMC

Sul TQMa8MPxL è fornito un eMMC per boot loader, sistema operativo e software applicativo. È collegato all'i.MX 8M Plus tramite USDHC3.

1,8 V 3,3 V

i.MX8M Plus NAND_WE# NAND_WP#

NAND_DATI[7;4] NAND_RE#

NAND_CE2# NAND_CE3#

NAND_CLE NAND_READY#

NAND_CE1#

e-MMC 5.1

VCC VCCQ

CLK CMD DATA[3:0] DATA4 DATA5 DATA6 DATA7 RST# STROBE

Figura 3: Diagramma a blocchi eMMC

L'i.MX 8M Plus supporta le modalità di trasferimento fino all'attuale standard eMMC v5.1 secondo JESD84-B51. Nella modalità DDR (HS400) è possibile raggiungere velocità di trasmissione dati fino a 400 Mbyte/s. La configurazione di avvio è descritta nel capitolo 3.2.1.3

3.2.2.3 QSPI NOR Flash

Il flash QSPI NOR può essere opzionalmente assemblato sul TQMa8MPxL. Se sul TQMa8MPxL non è popolato alcun QSPI NOR Flash, è possibile utilizzare i pad LGA dell'interfaccia. Poiché non è possibile separare i percorsi del segnale, questi pad LGA non devono essere cablati quando è equipaggiata la Flash NOR.

3.2.2.4 EEPROM24LC64T

Viene assemblata una EEPROM seriale, controllata dal bus I2C1. La protezione da scrittura (WP) non è supportata. Sul TQMa64MPxL è montata di default una EEPROM 24LC64T da 8 Kbit.

i.MX 8M Plus

I2C1_SCL I2C1_SDA

Memoria EEPROM

SCL SDA

Figura 4: Schema a blocchi EEPROM La EEPROM ha indirizzo I2C 0x57 / 101 0111b

Manuale dell'utente l TQMa8MPxL UM 0105 l © 2024, TQ-Systems GmbH

Pagina 15

3.2.2.5 EEPROM con sensore di temperatura SE97BTP

Sul TQMa97MPxL è montata una EEPROM seriale comprendente il sensore di temperatura tipo SE2BTP, controllato dal bus I1C8. I 128 byte inferiori (indirizzo da 00h a 7Fh) possono essere impostati sulla modalità protetta da scrittura permanente (PWP) o sulla modalità protetta da scrittura reversibile (RWP) tramite software. I 128 byte superiori (indirizzo da 80h a FFh) non possono essere protetti da scrittura e sono disponibili per la memorizzazione di dati generali. L'uscita di sovratemperatura dell'SE97BTP è collegata come drain aperto al pad LGA U8 TQMa19MPxL (TEMP_EVENT#). Ciò richiede un pull-up a 3.3 V (massimo 5.5 V) sulla scheda portante. Il dispositivo è assemblato sul lato superiore del TQMa8MPxL, vedere il componente D12, Figura 22.

Il dispositivo fornisce i seguenti indirizzi I2C:

o EEPROM (modalità normale): o EEPROM (modalità di protezione): o Sensore di temperatura:

0x53/101 0011b 0x33/011 0011b 0x1B/001 1011b

3.2.3

Affidati a Secure Element SE050

Un NXP Trust Secure Element SE050 è disponibile sul TQMa8MPxL come opzione di assemblaggio. Se equipaggiato, il chip fornisce due interfacce secondo ISO 7816 e ISO 14443. A queste è possibile collegare tra l'altro delle antenne.

i.MX 8M Plus

I2C1_SCL I2C1_SDA

SE050

I2C_SCL I2C_SDA

ISO_7816_IO1 ISO_7816_IO2 ISO_7816_CLK ISO_7816_RST

ISO_14443_LA ISO_14443_LB

Pastiglie LGA

V_3V3_IN

ISO_7816_IO1 ISO_7816_IO2 ISO_7816_CLK ISO_7816_RST

ISO_14443_LA ISO_14443_LB

L'SE050 è controllato dal bus I2C1. Maggiori dettagli possono essere trovati in (8). Il Trust Secure Element ha l'indirizzo I2C 0x48/100 1000b

3.2.4

RTC

TQMa8MPxL fornisce un RTC interno i.MX 8M Plus o un RTC discreto PCF85063A.

3.2.4.1 RTC interno i.MX 8M Plus

L'i.MX 8M Plus fornisce un RTC, che ha il proprio dominio di alimentazione (V_1V8_SNVS). Il dominio di alimentazione RTC SNVS di i.MX 8M Plus è fornito dal PMIC. Il PMIC è alimentato dall'ingresso TQMa8MPxL voltage di V_5V_IN. Il quarzo utilizzato per sincronizzare l'RTC ha una tolleranza di frequenza standard di ±20 ppm a +25 °C.

5 Volt

Pastiglie LGA

V_5V_IN

PMICPCA9450

INL1

LDO1

i.MX 8M Plus

VDD_SNVS_1P8

Figura 5: Schema a blocchi alimentazione RTC (TQMa8MPxL senza RTC discreto)

Manuale dell'utente l TQMa8MPxL UM 0105 l © 2024, TQ-Systems GmbH

Pagina 16

Nota: alimentazione RTC

L'RTC interno della CPU può essere utilizzato durante il normale funzionamento. Se l'alimentazione TQMa8MPxL (5 V) viene a mancare, non è più disponibile, poiché la guida SNVS dell'i.MX 8M Plus non è più alimentata.

3.2.4.2 RTC discreto PCF85063A

Oltre all'RTC interno i.MX 8M Plus, il TQMa8MPxL fornisce un RTC discreto PCF85063A come opzione di assemblaggio, controllato dal bus I2C1. Il quarzo utilizzato per sincronizzare l'RTC ha una tolleranza di frequenza standard di ±20 ppm a +25 °C. L'RTC discreto ha un'uscita di interruzione che fornisce il segnale di drain aperto RTC_EVENT# al pad LGA U18. Questo pin richiede un pull-up a 3.3 V (massimo 3.6 V) sulla scheda portante. L'RTC PCF85063A viene alimentato direttamente da V_LICELL solo quando l'alimentazione del PMIC o del TQMa8MPxL è disattivata. Durante il normale funzionamento del TQMa8MPxL, il PMIC fornisce 3.3 V.

Alimentazione elettrica

Protezione

Pastiglie LGA

V_5V_IN

PMIC

INL1 BUCK4

Batteria a bottone (tip. 3 V)

Protezione

V_LICELL

PCF85063A

VDD

Figura 6: Schema a blocchi alimentazione RTC (TQMa8MPxL con RTC discreto) L'RTC discreto ha indirizzo I2C 0x51 / 101 0001b

Nota: alimentazione RTC

Le funzioni SNVS dell'i.MX 8M Plus possono essere utilizzate solo se il TQMa8MPxL è alimentato con 5 V. Poiché la guida SNVS non viene alimentata quando il TQMa8MPxL non è acceso, si consiglia di utilizzare l'RTC PCF85063A opzionale.

3.2.5

Interfacce

3.2.5.1 Oltreview

Le seguenti interfacce o segnali non sono disponibili sui pad LGA TQMa8MPxL e vengono utilizzati su TQMa8MPxL. Tabella 6: Interfacce interne TQMa8MPxL

Interfaccia USDHC3 SDRAM GPIO1_IO04 / SD2_VSELECT GPIO1_IO08 / IRQ# POR# PMIC_ON_REQ PMIC_STBY_REQ RTC_XTALO

Capitolo 3.2.2.2 3.2.2.1 3.2.5.20

Nota eMMC, 8 bit LPDDR4, 32 bit 100 k PU su TQMa8MPxL 100 k PU su TQMa8MPxL, segnale da CPU a PMIC Segnale da CPU a PMIC Segnale da CPU a PMIC 100 k PU su TQMa8MPxL

Manuale dell'utente l TQMa8MPxL UM 0105 l © 2024, TQ-Systems GmbH

Pagina 17

3.2.5.2 PUÒ FD

L'i.MX 8M Plus fornisce due interfacce CAN FD, CAN FD1 e CAN FD2. Entrambi sono multiplexati sui pin SAI5 nella configurazione standard e specificati secondo il protocollo CAN 2.0B. La fornitura voltage viene impostato tramite il pad LGA TQMa8MPxL V_SAI1_SAI5.

Tabella 7: Segnali CAN FD

Segnale CAN_FD1_TX CAN_FD1_RX CAN_FD2_TX CAN_FD2_RX

i.MX 8M Plus AD16 AF16 AE14 AF14

TQMa8MPxL B1 C1 D1 E1

Gruppo di potenza V_SAI1_SAI5

3.2.5.3 PWM L'i.MX 8M Plus fornisce fino a quattro segnali PWM che possono essere multiplati tramite vari pin. Nella configurazione predefinita viene fornito un segnale PWM (PWM3) al pad LGA D8 TQMa10MPxL.

3.2.5.4 GPT i.MX 8M Plus fornisce fino a tre timer per uso generale (GPT). Questi utilizzano sempre una parte della risoluzione UART. Pin I2C della CPU. Pertanto solo l'interfaccia GPT2 (GPT2_CLK) è fornita dal pad TQMa8MPxL D8.

Manuale dell'utente l TQMa8MPxL UM 0105 l © 2024, TQ-Systems GmbH

Pagina 18

3.2.5.5 Ethernet

L'i.MX 8M Plus fornisce due interfacce Gigabit Ethernet, che supportano velocità di trasferimento di 10/100 e 1000 Mbps nonché full e half-duplex. Per impostazione predefinita l'interfaccia ENET è configurata come RGMII. La seconda interfaccia Ethernet è fornita sui pin SAI1. La fornitura voltage deve essere impostato esternamente a 1.8 V o 3.3 V, con pad LGA V_ENET e V_SAI1_SAI5, vedere anche capitolo 3.2.8.6. I segnali differenziali vengono adattati in lunghezza sul TQMa8MPxL e instradati con un'impedenza differenziale di 100 . Sulla carrier board devono essere collegati secondo le specifiche RGMII.

La tabella seguente mostra i segnali utilizzati in modalità RGMII.

Tabella 8: Segnali ENET in modalità RGMII

Segnale

ENET_QOS_RX_CTL ENET_QOS_RXC ENET_QOS_RD0 ENET_QOS_RD1 ENET_QOS_RD2 ENET_QOS_RD3 ENET_QOS_TX_CTL ENET_QOS_TXC ENET_QOS_TD0 ENET_QOS_TD1 ENET_QOS_TD2 ENET_QOS_TD3 ENET_QOS_MDC ENET_QOS_MDIO ENET_QOS _EVENT2_OUT ENET_QOS_EVENT2_IN ENET1_RST# ENET1_INT# ENET0_RST# ENET0_INT# ENET_MDC ENET_MDIO ENET_RD0 ENET_RD1 ENET_RD2 ENET_RD3 ENET_RXC ENET_TD0 ENET_TD1 ENET_TD2 ENET_TD3 ENET_TX_CTL ENET_TXC ENET_RX_CTL

Etereo

ENET1 ENET1 ENET1 ENET1 ENET1 ENET1 ENET1 ENET1 ENET1 ENET1 ENET1 ENET1 ENET1 ENET1 ENET1 ENET1 ENET1 ENET1 ENET0 ENET0 ENET0 ENET0 ENET0 ENET0 ENET0 ENET0 ENET0 ENET0 ENET0 ENET0 ENET0 ENET0 ENET0

Direzione

IIIIIIOOOOOOI/OOIOOOIOI/OIIIIIIOOOOOOI

i.MX 8M Plus

AE28 AE29 AG29 AG28 AF29 AF28 AF24 AE24 AC25 AE26 AF26 AD24 AH28 AH29 AJ14 AH16 AC10 AF10 AJ9 AH8 AH9 AJ8 AD10 AE10 AH10 AH12 AJ12 AJ11 AJ10 AH11 AD12 AH13 AH14 AF12

TQMa8MPxL

AA4 AB7 AB4 AB5 AA6 Y7 Y8 AB9 AA8 AB8 Y9 AA10 Y5 Y6 B8 B9 L4 H4 K4 G4 H3 J3 J2 K2 L3 M3 K1 M2 N2 P3 R3 R4 R2 P4

Gruppo di potenza V_ENET

V_SAI2_SAI3_SPDIF V_SAI1_SAI5

Manuale dell'utente l TQMa8MPxL UM 0105 l © 2024, TQ-Systems GmbH

3.2.5.6 I2C Quattro interfacce I2C fornite da i.MX 8M Plus vengono instradate ai pad LGA TQMa8MPxL. Tutti i dispositivi I2C sul TQMa8MPxL sono controllati dal bus I2C1.

La tabella seguente mostra i segnali utilizzati dalle interfacce I2C.

Pagina 19

I2C1

i.MX 8M Plus

PCA9450

Codice PCF85063

3.3 Volt

SE050

SE97BTP

I2C1

24LC64T

Pastiglie LGA

I2C2

I2C2

I2C4

I2C4

SD1_DATI[1:0]

I2C6

Figura 7: Schema a blocchi I2C

Tabella 9:

Segnale I2C1_SCL I2C1_SDA I2C2_SCL I2C2_SDA I2C4_SCL I2C4_SDA I2C6_SCL I2C6_SDA

Segnali I2C

Direzione OI/OOI/OOI/OOI/O

i.MX 8M Plus AC8 AH7 AH6 AE8 AF8 AD8 Y29 Y28

TQMa8MPxL C14 D13 C13 C12 B14 B13 V10 W10

Gruppo di alimentazione 3.3 V V_SD1

Nota 4.7 k PU a 3.3 V su TQMa8MPxL 4.7 k PU a 3.3 V su TQMa8MPxL No PU su TQMa8MPxL No PU su TQMa8MPxL No PU su TQMa8MPxL No PU su TQMa8MPxL No PU su TQMa8MPxL No PU su TQMa8MPxL

La tabella seguente mostra i dispositivi I2C controllati dal bus I2C1 sul TQMa8MPxL.

Tabella 10: assegnazione degli indirizzi bus I2C1

Componente

Funzione

PCA9450LC24T PCF64A

SE97BTP

SE050

PMIC EEPROM (opzionale) RTC (opzionale) EEPROM (modalità normale) EEPROM (modalità di protezione) Sensore di temperatura in EEPROM Trust Secure Element (opzionale)

Indirizzo a 7 bit 0x25 / 010 0101b 0x57 / 101 0111b 0x51 / 101 0001b 0x53 / 101 0011b 0x33 / 011 0011b 0x1B / 001 1011b 0x48 / 100 1000b

Se sulla carrier board sono collegati più dispositivi al bus I2C1, è necessario tenere conto del carico capacitivo massimo del bus secondo lo standard I2C. Se necessario, è necessario fornire pull-up aggiuntivi sul bus I2C sulla scheda portante.

Manuale dell'utente l TQMa8MPxL UM 0105 l © 2024, TQ-Systems GmbH

Pagina 20

3.2.5.7 ETAG

Il processore fornisce un JTAG interfaccia che può essere utilizzata per eseguire il debug dei programmi eseguiti sul processore. A questo scopo è necessario uno strumento hardware corrispondente. L'interfaccia può anche essere configurata per Boundary Scan.

i.MX 8M Plus

JTAG_TCK JTAG_TDIJTAG_TDO JTAG_TMSJTAG_MOD

Terra

Pastiglie LGA

JTAG_TCK JTAG_TDIJTAG_TDO JTAG_TMS

Figura 8: Schema a blocchi JTAG interfaccia

La tabella seguente mostra i segnali utilizzati dal JTAG interfaccia. Non è necessario prevedere un circuito esterno sulla scheda madre.

Tabella 11:

Segnale JTAG_TCK JTAG_TDIJTAG_TDO JTAG_TMSJTAG_MOD

JTAG segnali

Direzione IIOII

i.MX 8M Plus G18 G16 F14 G14 G20

TQMa8MPxL M19 P18 L19 N18

Nota 10 kPD su TQMa8MPxL

Gruppo di alimentazione 3.3 V

Manuale dell'utente l TQMa8MPxL UM 0105 l © 2024, TQ-Systems GmbH

Pagina 21

3.2.5.8 GPIO

Ad eccezione dei segnali differenziali dedicati, ad esempio MIPI DSI/CSI e USB, tutti i segnali della CPU instradati ai pad LGA TQMa8MPxL possono essere configurati come GPIO. Le caratteristiche elettriche dei GPIO sono da ricavare dal Data Sheet di i.MX 8M Plus (2). La tabella seguente mostra i segnali GPIO configurati principalmente come GPIO.

Tabella 12: segnali GPIO

Segnale GPIO1_IO00 GPIO1_IO01 GPIO1_IO03 GPIO1_IO06 GPIO1_IO07 GPIO1_IO09 GPIO3_IO14 GPIO2_IO06 GPIO2_IO07 GPIO2_IO10 GPIO2_IO11 GPIO3_IO19 GPIO3_IO20 GPIO3_IO21 GPIO4_IO18 GPIO4_IO19 GPIO4 _IO20 GPIO4_IO28 GPIO4_IO27 GPIO4_IO21 GPIO4_IO22 GPIO4_IO24 GPIO4_IO25 GPIO4_IO29 GPIO5_IO04 GPIO5_IO05 GPIO5_IO03 GPIO5_IO27 GPIO5_IO26 GPIO5_IO07 GPIO5_IO06 GPIO5_IO09

i.MX 8M Plus A7 E8 D6 A3 F6 B8 R26 U26

AA29 W25 W26 AC14 AD14 AE16 AC12 AJ13 AE12 AJ19 AJ15 AH17 AJ16 AJ17 AH15 AJ18 AD18 AC18 AE18 AJ4 AE6 AC20 AF20 AE20 AD20

TQMa8MPxL E16 E15 E14 E12 E11 D11 C16 U8 U9 V6 W7 D2 A2 C2 N4 T2 L1 A9 A6 B6 A7 C7 C9 A10 L5 L6 M6 E9 F9 G1 H1 F2 G2

Gruppo di potere

V_SD1

V_SAI1_SAI5

V_SAI2_SAI3_SPDIF

Manuale dell'utente l TQMa8MPxL UM 0105 l © 2024, TQ-Systems GmbH

Pagina 22

3.2.5.9 MIPI CSI

L'i.MX 8M Plus fornisce due interfacce per fotocamera MIPI-CSI con quattro coppie di dati ciascuna. Quando si utilizza un'interfaccia per fotocamera, il formato immagine massimo è 4K a 45 fps o 12 MP a 30 fps. Quando si utilizzano entrambe le interfacce della fotocamera, è supportato fino a 1080p a 80 fps. La velocità in bit massima è 1.5 Gbps. I segnali differenziali vengono adattati in lunghezza sul TQMa8MPxL e instradati con un'impedenza differenziale di 100 .

i.MX 8M Plus

MIPI_CSI[2:1]_CLK_N/P MIPI_CSI[2:1]_D[3:0]_N/P

Pastiglie LGA

MIPI_CSI[2:1]_CLKN/P MIPI_CSI[2:1]_DN/P[3:0]

Figura 9: Diagramma a blocchi MIPI CSI

La tabella seguente mostra i segnali utilizzati dall'interfaccia MIPI CSI. Tabella 13: segnali MIPI CSI

Segnale

i.MX 8M Plus

CSI1_D1_N

E20

CSI1_D1_P

D20

CSI1_D3_N

E26

CSI1_D3_P

D26

CSI1_CLK_N

E22

CSI1_CLK_P

D22

CSI1_D0_N

E18

CSI1_D0_P

D18

CSI1_D2_N

E24

CSI1_D2_P

D24

CSI2_D1_N

B24

CSI2_D1_P

A24

CSI2_D3_N

B21

CSI2_D3_P

A21

CSI2_CLK_N

B23

CSI2_CLK_P

A23

CSI2_D0_N

B25

CSI2_D0_P

A25

CSI2_D2_N

B22

CSI2_D2_P

A22

TQMa8MPxL K20 L20 N20 P20 L22 M22 J21 K21 M21 N21 R21 T21 V21 W21 T20 U20 P22 R22 U22 V22

Gruppo di alimentazione 1.8 V

3.2.5.10 MIPI DSI

L'i.MX 8M Plus fornisce un'interfaccia DSI con quattro coppie di dati per inviare dati di visualizzazione seriale fino a 1.5 Gbps. Il MIPI-DSI PHY supporta risoluzioni fino a 1920×1200 a 60 fps. I segnali differenziali vengono adattati in lunghezza sul TQMa8MPxL e instradati con un'impedenza differenziale di 100 .

i.MX 8M Plus

MIPI_DSI1_D[3:0]_P/N MIPI_DSI1_CLK_P/N

Pastiglie LGA

MIPI_DSI_DN/P[3:0] MIPI_DSI_CLKN/P

Figura 10: diagramma a blocchi MIPI DSI

Manuale dell'utente l TQMa8MPxL UM 0105 l © 2024, TQ-Systems GmbH

La tabella seguente mostra i segnali utilizzati dall'interfaccia MIPI DSI.

Tabella 14: segnali MIPI DSI

Segnale DSI_CLK_N DSI_CLK_P DSI_D0_N DSI_D0_P DSI_D1_N DSI_D1_P DSI_D2_N DSI_D2_P DSI_D3_N DSI_D3_P

i.MX 8M Plus B18 A18 B16 A16 B17 A17 B19 A19 B20 A20

TQMa8MPxL F21 G21 D20 E20 E22 F22 G20 H20 H22 J22

Pagina 23

Gruppo di alimentazione 1.8 V

3.2.5.11 HDMI

L'i.MX 8M Plus fornisce un'interfaccia HDMI secondo le specifiche del display "HDMI 2.0a" incl. eARC. Le risoluzioni massime sono 3840×2160 a 30 fps o 1920×1080 a 120 fps. L'interfaccia funziona con 1.8 V. I segnali differenziali vengono adattati in lunghezza sul TQMa8MPxL e instradati con un'impedenza differenziale di 100 .

Tabella 15: Segnali HDMI

Segnale EARC_AUX EARC_N_HPD EARC_P_UTIL HDMI_CEC HDMI_TXC_N HDMI_TXC_P HDMI_DDC_SCL HDMI_DDC_SDA HDMI_HPD HDMI_TX0_N HDMI_TX0_P HDMI_TX1_N HDMI_TX1_P HDMI_TX2_N HDMI_TX2_P

i.MX 8M Plus AH23 AH22 AJ23 AD22 AJ24 AH24 AC22 AF22 AE22 AJ25 AH25 AJ26 AH26 AJ27 AH27

TQMa8MPxL V4 T1 U1 W4 U3 V3 AB3 AB2 Y3 V2 W2 W1 Y1 Y2 AA2

Gruppo di alimentazione 1.8 V

Manuale dell'utente l TQMa8MPxL UM 0105 l © 2024, TQ-Systems GmbH

Pagina 24

3.2.5.12 LVDS

Oltre a MIPI-DSI e HDMI, la CPU fornisce un'interfaccia LVDS. La CPU offre solo un PHY, ma supporta fino a due canali con un massimo di quattro corsie dati ciascuno. La risoluzione massima è 1920 x 1200 a 60 fps. L'interfaccia funziona con 1.8 V. I segnali differenziali vengono adattati in lunghezza sul TQMa8MPxL e instradati con un'impedenza differenziale di 100 .

i.MX 8M Plus

LVDS[1:0]_D[3:0]_N/P LVDS[1:0]_CLK_N/P

Figura 11: Schema a blocchi LVDS

Tabella 16: Segnali LVDS

Segnale LVDS0_D0_N LVDS0_D0_P LVDS0_D1_N LVDS0_D1_P LVDS0_D2_N LVDS0_D2_P LVDS0_D3_N LVDS0_D3_P LVDS0_CLK_N LVDS0_CLK_P LVDS1_D0_N LVDS1_D0_P LVDS1_D1_N D1_P LVDS1_D1_N LVDS2_D1_P LVDS2_D1_N LVDS3_D1_P LVDS3_CLK_N LVDS1_CLK_P

i.MX 8M Plus E28 D29 F28 E29 H28 G29 J28 H29 G28 F29 B26 A26 B27 A27 C28 B29 D28 C29 B28 A28

Pastiglie LGA

LVDS[1:0]_D[3:0]_N/P LVDS[1:0]_CLK_N/P

TQMa8MPxL Y10 Y11 AA11 AA12 AB12 AB13 AA14 AA15 Y13 Y14 AB15 AB16 Y16 Y17 AA17 AA18 AA19 AA20 AB18 AB19

Gruppo di alimentazione 1.8 V

Manuale dell'utente l TQMa8MPxL UM 0105 l © 2024, TQ-Systems GmbH

Pagina 25

3.2.5.13 PCIe

L'i.MX 8M Plus fornisce un'interfaccia PCIe Gen3 con una corsia (x1). Il clock di riferimento da 100 MHz può essere generato su TQMa8MPxL e inviato a PCIE_REF_CLKN/P per la scheda PCIe. In alternativa, il clock di riferimento può essere fornito da una fonte esterna a PCIE_REF_CLKN/P. In generale, NXP consiglia l'uso di una fonte esterna per motivi di precisione. I condensatori in serie richiesti dallo standard PCIe devono essere forniti sulla scheda portante. I segnali differenziali vengono adattati in lunghezza sul TQMa8MPxL e instradati con un'impedenza differenziale di 85 . I segnali devono essere terminati sulla carrier board secondo la specifica PCIe.

i.MX 8M Plus PCIE_RESREF

PCIE_REF_PAD_CLK_P/N PCIE_RXN_P/N PCIE_TXN_P/N

Figura 12: diagramma a blocchi PCIe

Pastiglie LGA

Terra

PCIE_REF_CLKP/N PCIE_RXP/N PCIE_TXP/N

Tabella 17: segnali PCIe

Segnale PCIE_REF_CLKN PCIE_REF_CLKP PCIE_RXN PCIE_RXP PCIE_TXN PCIE_TXP PCIE_RESREF

Direzione I/OIOI

i.MX 8M Plus E16 D16 B14 A14 B15 A15 F16

TQMa8MPxL Y22 AA22 W20 Y20 AA21 AB21

Gruppo di alimentazione 1.8 V

8.2 kPD su TQMa8MPxL

Attenzione: invecchiamento accelerato di PCI Express PHY

A causa di un errore dell'i.MX 8M Plus, il PCI Express PHY è soggetto ad un invecchiamento accelerato in stati di basso consumo. Nell'errata i.MX 8M Plus (5), NXP descrive una soluzione alternativa da seguire per evitare l'impatto dell'invecchiamento sul PHY PCI Express.

Manuale dell'utente l TQMa8MPxL UM 0105 l © 2024, TQ-Systems GmbH

Pagina 26

3.2.5.14 Istruzione di ispezione

L'i.MX 8M Plus fornisce diverse interfacce SAI con diverse larghezze di bus. Il SAI8 a 1 bit non è disponibile poiché è multiplexato come interfaccia Ethernet. I moduli dalla Rev.02xx utilizzano solo l'interfaccia SAI3. La fornitura voltage deve essere impostato su 1.8 V o 3.3 V sulla scheda portante con pad LGA V_SAI2_SAI3_SPDIF. I pin dell'orologio possono essere utilizzati come ingresso o uscita.

i.MX 8M Plus

SAI3_MCLK SAI3_TXFS

SAI3_TXC SAI3_TXD SAI3_RXD

Pastiglie LGA

SAI3_MCLK SAI3_TXFS SAI3_TXC SAI3_TXD0 SAI3_RXD0

Figura 13: Schema a blocchi SAI1

La tabella seguente elenca tutti i segnali SAI forniti dal TQMa8MPxL:

Tabella 18:

Segnale SAI3_TXFS SAI4_RXD SAI3_TXc SAI3_TXD SAI3_MCLK

Segnali SAI

Direzione OIOOO

i.MX 8M Plus AC16 AF18 AH19 AH18 AJ20

TQMa8MPxL B11 A12 B12 A13 C10

Gruppo di potenza V_SAI2_SAI3_SPDIF

3.2.5.15 Ingresso SPDIF

L'i.MX 8M Plus ha un'interfaccia SPDIF che non viene utilizzata nativamente. Invece, i pin vengono multiplexati come GPIO per impostazione predefinita. Questa configurazione può essere modificata se necessario, ad esample utilizzando i pad LGA mostrati nella figura seguente:

i.MX 8M Plus

SPDIF_RX SPDIF_TX SPDIF_EXT_CLK

Pastiglie LGA

GPIO5_IO04 GPIO5_IO03 GPIO5_IO05

Figura 14: Schema a blocchi SPDIF

Manuale dell'utente l TQMa8MPxL UM 0105 l © 2024, TQ-Systems GmbH

Pagina 27

3.2.5.16 QSPI/NAND

I segnali flash NOR vengono instradati ai pad LGA TQMa8MPxL. I segnali flash NOR utilizzano una parte dei pin NAND dell'i.MX 8M Plus. Tutti gli altri pin NAND dell'i.MX 8M Plus vengono utilizzati TQMa8MPxL internamente per l'eMMC come sorgente di avvio uSDHC3. Questi pad LGA non possono essere utilizzati se è equipaggiato il flash QSPI NOR! Per ulteriori informazioni su QSPI vedere il capitolo 3.2.2.3.

Tabella 19: Segnali QSPI

Segnale

Direzione

QSPI_A_DATA3

Entrata/uscita

QSPI_A_DATA2

Entrata/uscita

QSPI_A_DATA1

Entrata/uscita

QSPI_A_DATA0

Entrata/uscita

QSPI_A_SS0#

O

QSPI_A_SCLK

O

i.MX 8M Plus N24 L24 L25 R25 L26 N25

TQMa8MPxL W12 W13 V13 V14 V15 W15

Gruppo di alimentazione 1.8 V

3.2.5.17 ECSPI

Le interfacce SPI full-duplex dell'i.MX 8M Plus supportano sia la modalità master che quella slave con velocità dati fino a 52 Mbit/s. Tutte le interfacce SPI forniscono una selezione di chip ciascuna e vengono instradate direttamente ai pad LGA TQMa8MPxL. ECSPI2 è alimentato con 1.8 V. ECSPI3, che è multiplexato con i segnali UART, è alimentato con 3.3 V.

i.MX 8M Plus ECSPI2_SS0

ECSPI2_MOSI ECSPI2_MISO ECSPI2_SCLK

UART2_TXD UART1_TXD UART2_RXD UART1_RXD

Figura 15: Schema a blocchi ECSPI

Pastiglie LGA

ECSPI2_CS0 ECSPI2_SDO ECSPI2_SDI ECSPI2_SCK

ECSPI3_CS0 ECSPI3_SDO ECSPI3_SDI ECSPI3_SCK

La tabella seguente mostra i segnali utilizzati dall'interfaccia ECSPI.

Tabella 20:

Segnale ECSPI2_MOSI ECSPI2_MISO ECSPI2_SCLK ECSPI2_SS0 ECSPI3_MOSI ECSPI3_MISO ECSPI3_SCLK ECSPI3_SS0

Segnali ECSPI

Direzione OIOOOIOO

i.MX 8M Plus

AJ21 AH20 AH21 AJ22 AJ3 AF6 AD6 AH4

TQMa8MPxL

P5 N5 M5 P6 J6 J5 K5 H5

Gruppo di alimentazione 1.8 V

3.3 Volt

Manuale dell'utente l TQMa8MPxL UM 0105 l © 2024, TQ-Systems GmbH

3.2.5.18UART

L'i.MX 8M Plus fornisce quattro interfacce UART, tutte instradate ai pad LGA TQMa8MPxL. Il voltagL'alimentazione per UART1, UART2 e UART3 deve essere impostata esternamente su 1.8 V o 3.3 V tramite il pad LGA Y19, V_SD1. UART4 è fisso e alimentato a 3.3 V.

i.MX 8M Plus

SD1_CLK SD1_CMD SD1_DATA6 SD1_DATA7 UART4_TX UART4_RX SD1_DATA2 SD1_DATA3

Pastiglie LGA

UART1_TX UART1_RX UART3_TX UART3_RX UART4_TX UART4_RX UART2_TX UART2_RX

Pagina 28

Figura 16: diagramma a blocchi interfacce UART

La tabella seguente mostra i segnali utilizzati dalle interfacce UART.

Tabella 21:

Segnale UART1_TXD UART1_RXD UART2_TXD UART2_RXD UART3_TXD UART3_RXD UART4_TXD UART4_RXD

Segnali UART

Direzione OIOIOIOI

i.MX 8M Plus W28 W29 V29 V28 AA28 U25 AH5 AJ5

TQMa8MPxL V11 V12 V9 W9 V7 V8 G6 H6

Gruppo di potenza V_SD1 3.3 V

Manuale dell'utente l TQMa8MPxL UM 0105 l © 2024, TQ-Systems GmbH

Pagina 29

3.2.5.19 Interfaccia USB

L'i.MX 8M Plus fornisce due interfacce USB 3.0 con PHY integrati tramite USB1 e USB2. Questi supportano Super-Speed (5 Gbit/s), High-Speed (480 Mbit/s), Full-Speed (12 Mbit/s) e Low-Speed (1.5 Mbit/s) e offrono host, dispositivo e Funzionalità OTG 2.0. I segnali OTG sono forniti tramite pin GPIO1. Tutti i segnali hanno un livello di 3.3 V. È possibile applicare fino a 5 V ai pin VBUS. Le resistenze da 30k richieste da NXP sono già fornite sul modulo. I segnali differenziali vengono adattati in lunghezza sul TQMa8MPxL e instradati con un'impedenza differenziale di 90 .

i.MX 8M Plus

USB1_VBUS USB1_DN/DP USB1_RX_N/RX_P USB1_TX_N/TX_P

GPIO1_IO13 GPIO1_IO12 GPIO1_IO10 USB1_DNU

USB2_VBUS USB2_DN/DP USB2_RX_N/RX_P USB2_TX_N/TX_P

GPIO1_IO15 GPIO1_IO14 GPIO1_IO11 USB2_DNU

Pastiglie LGA

USB1_VBUS USB1_DN/DP USB1_RXN/RXP USB1_TXN/TXP USB1_OTG_OC USB1_OTG_PWR USB1_OTG_ID USB1_ID

USB2_VBUS USB2_DN/DP USB2_RXN/RXP USB2_TXN/TXP GPIO1_IO15 (USB2_OTG_OC) GPIO1_IO14 (USB2_OTG_PWR) GPIO1_IO11 (USB2_OTG_ID) USB2_ID

Figura 17: Schema a blocchi interfacce USB

Tabella 22: Segnali USB

Segnale

USB1_VBUS USB1_OTG_OC USB1_OTG_PWR USB1_OTG_ID USB1_ID USB1_DN USB1_DP USB1_RXN USB1_RXP USB1_TXN USB1_TXP

USB2_VBUS USB2_OTG_OC USB2_OTG_PWR USB2_OTG_ID USB2_ID USB2_DN USB2_DP USB2_RXN USB2_RXP USB2_TXN USB2_TXP

Direzione

PIOIII/OI/OIIOO

PIOIII/OI/OIIOO

i.MX 8M Plus

A11 A6 A5 B7 B11 E10 D10 B9 A9 B10 A10

D12 B5 A4 D8 E12 E14 D14 B12 A12 B13 A13

TQMa8MPxL

F18 H19 H18 G18 F19 C22 B22 B20 B19 A21 A20

E17 D18 D17 E19 D19 C19 C18 B17 B16 A18 A17

Gruppo di alimentazione tollerante a 5 V

3.3 Volt

Tollerante a 5 V

3.3 Volt

Nota

NXP: non utilizzare

Multiplexato come GPIO1_IO15 Multiplexato come GPIO1_IO14 Multiplexato come GPIO1_IO11

NXP: non utilizzare

Manuale dell'utente l TQMa8MPxL UM 0105 l © 2024, TQ-Systems GmbH

Pagina 30

3.2.5.20 uSDHC L'i.MX 8M Plus fornisce tre interfacce uSDHC: uSDHC1, uSDHC2 e uSDHC3. uSDHC1 è configurato come UART e I2C, vedere capitoli 3.2.5.18 e 3.2.5.6. Tutte e tre le interfacce supportano lo standard SD fino alla versione 3.0, lo standard MMC fino alla versione 5.1 e il funzionamento a 1.8 V e 3.3 V. uSDHC1 e uSDHC3 forniscono interfacce a 8 bit, uSDHC2 fornisce un'interfaccia a 4 bit.

uSDHC1 Il voltagIl livello di uSDHC1 può essere impostato su 1.8 V o 3.3 V dal pad LGA TQMa8MPxL V_SD1, Y19. Poiché tutti i segnali essenziali dell'i.MX 8M Plus vengono instradati ai pad LGA TQMa8MPxL, è possibile collegare un eMMC sulla scheda portante. In questo caso la fornitura voltage deve essere impostato su 1.8 V. L'avvio da uSDHC1 è possibile solo dopo aver bruciato i fusibili di avvio e quindi non è supportato per impostazione predefinita.

uSDHC2

È possibile collegare una scheda SD all'interfaccia uSDHC2. Tutti i segnali i.MX 8M Plus richiesti vengono instradati ai pad LGA TQMa8MPxL. SD2_VSELECT (GPIO1_IO04) viene utilizzato per controllare l'alimentazione della scheda SD voltage e non viene instradato a un pad LGA TQMa8MPxL. Il segnale SD2_RESET_B può essere ignorato se la scheda SD è alimentata dal TQMa8MPxL. Il voltage V_SD2 è previsto per i pull-up esterni.

i.MX 8M Plus

SD2_CLK SD2_CMD SD2_DATA[3:0] SD2_CD_B

SD2_WP SD2_RESET_B SD2_VSELECT

NVCC_SD2

Pastiglie LGA

SD2_CLK SD2_CMD SD2_DATA[3:0] SD2_CD_B SD2_WP SD2_RESET_B V_3V3_SD V_SD2

PMICPCA9450

LDO5 SD_VSEL

SW_EN SWOUT

Figura 18: Schema a blocchi dell'interfaccia della scheda SD

Tabella 23:

Segnale SD2_DATA3 SD2_DATA2 SD2_DATA1 SD2_DATA0 SD2_CLK SD2_CD# SD2_CMD SD2_WP SD2_RST# 3

Segnali USDHC2

Direzione I/OI/OI/OI/OOII/OIO

i.MX 8M Plus AA25 AA26 AC29 AC28 AB29 AD29 AB28 AC26 AD28

TQMa8MPxL T5 U5 V5 W5 T4 R6 U6 T7 U7

uSDHC3 L'interfaccia uSDHC3 utilizza una parte dei pin NAND, sul TQMa8MPxL è collegata l'eMMC.

3: PU da 4.7 k su TQMa8MPxL.

Gruppo di potenza SD2_VSELECT

Manuale dell'utente l TQMa8MPxL UM 0105 l © 2024, TQ-Systems GmbH

3.2.5.21 Sorgenti di clock esterne

L'i.MX 8M Plus ha la possibilità di utilizzare due oscillatori esterni come sorgenti di clock. Tutti e quattro i segnali i.MX 8M Plus forniti a questo scopo vengono instradati ai pad LGA TQMa8MPxL. La tabella seguente mostra questi segnali di clock.

Tabella 24: Segnali CLK

Segnale CLK1_IN CLK2_IN CLK1_OUT CLK2_OUT

i.MX 8M Plus K28 L28 K29 L29

TQMa8MPxL W18 W16 W17 V17

Pagina 31

Gruppo di alimentazione 1.8 V

3.2.6

Segnali non specifici

La tabella seguente elenca tutti i segnali che non sono assegnati a un gruppo specifico. I segnali ISO_7816 e ISO_14443 sono disponibili solo con Trust Secure Element assemblato, vedere capitolo 3.2.3.

Tabella 25: Segnali non specifici

Segnale PMIC_WDOG_OUT# PMIC_WDOG_IN# M7_NMI TEMP_EVENT# RTC_EVENT# ISO_7816_CLK ISO_7816_RST ISO_7816_IO1 ISO_7816_IO2 ISO_14443_LA ISO_14443_LB

Direzione OII OOD OOD III/OI/OI/OI/O

i.MX 8M Plus B6 B4

TQMa8MPxL F8 F6 V19 U19 U18 J19 L18 K18 J18 D21 C21

Nota 3.3 V 3.3 V, 100 k PU su TQMa8MPxL 3.3 V attivo alto da 0.9 V a 3.6 V da 0.7 V a 5.5 V

Utilizzare con Trust Secure Element popolato

Manuale dell'utente l TQMa8MPxL UM 0105 l © 2024, TQ-Systems GmbH

3.2.7

Reset

Gli ingressi o le uscite di ripristino sono disponibili sui pad LGA TQMa8MPxL. Il seguente schema a blocchi mostra il cablaggio dei segnali di reset.

Pagina 32

Pastiglie LGA

RESET_IN# ONOFF

PMIC_RST# RESET_OUT#

Figura 19: Schema a blocchi Reset

1.8 V SIST_RST#

i.MX 8M Plus

ONOFF POR_B

PCA9450

PMIC_RST# POR_B

La tabella seguente descrive i segnali di reset disponibili sui pad LGA TQMa8MPxL:

Tabella 26: Segnali di reset

Segnale

Direzione TQMa8MPxL

RESET_IN#

I

E7

RESET_OUT#

O

F7

Gruppo di alimentazione 3.3 V

Osservazione

· Attiva il RESET (POR_B) dell'i.MX 8M Plus; poco attivo. · È necessario il pull-up esterno a 3.3 V. · Tirare verso GND per attivare.

· Uscita a scarico aperto; poco attivo. · Attiva il RESET dei componenti della scheda portante. · È necessario un pull-up esterno (max. 5.5 V).

PMIC_RST#

I

E6

1.8 Volt

· Non è richiesto alcun pull-up sul pannello portante; poco attivo. · Risposta PMIC programmabile (ripristino a caldo, ripristino a freddo).

AccesoSpento

· Funzione ON/OFF dell'i.MX 8M Plus (vedi scheda tecnica CPU (2)).

I

G7

1.8 Volt

· Non è richiesto alcun pull-up sul pannello portante; poco attivo.

· Tirare verso GND per 5 s per attivare.

Manuale dell'utente l TQMa8MPxL UM 0105 l © 2024, TQ-Systems GmbH

Pagina 33

3.2.8

Energia

3.2.8.1 Alimentazione

Il TQMa8MPxL richiede una fornitura voltage di 5 V ±5 %. Le caratteristiche e le funzioni di un determinato pin o segnale devono essere ricavate dalla scheda tecnica PMIC (4) e dalla scheda tecnica i.MX 8M Plus (2).

3.2.8.2 Consumo energetico

Il consumo energetico indicato deve essere considerato come un valore approssimativo. Il consumo energetico del TQMa8MPxL dipende fortemente dall'applicazione, dalla modalità operativa e dal sistema operativo. Per ulteriori informazioni sul consumo energetico e sulle opzioni di risparmio, consultare la nota applicativa NXP AN12410 (6).

La seguente tabella mostra i parametri di alimentazione (V_8V_IN) e consumo energetico di TQMa8MPxL (con i.MX 5M Plus Quad):

Tabella 27: Consumo energetico

Modalità di funzionamento Picco teorico calcolato (caso peggiore) Prompt U-Boot Linux-Idle Linux con carico della CPU al 100% Reset Suspend in modalità RAM

Corrente a 5 V 3.625 A 0.36 A

341.7mA 716.1mA 0.140mA 25.60mA

Consumo energetico a 5 V 18.1 W 1.8 W 1.7 W 3.6 W 0.7 mW

128mW

3.2.8.3 volumitage monitoraggio Il TQMa8MPxL è dotato di un supervisore che monitora il volume in ingressotage(VIN). Se l'input voltage scende al di sotto di 4.38 V, viene attivato un Reset e il TQMa8MPxL viene mantenuto in reset fino all'ingresso voltage rientra nuovamente nell'intervallo consentito.

Attenzione: Distruzione o malfunzionamento, fornitura voltage superamento

il volumetagIl monitoraggio non rileva un superamento del volume di ingresso consentitotage. Un superamento del volume di ingresso consentitotagCiò potrebbe causare malfunzionamento, distruzione o invecchiamento accelerato del TQMa8MPxL.

3.2.8.4 Altre forniture voltages USBx_VBUS: Il voltagGli ingressi USB1_VBUS e USB2_VBUS vengono utilizzati per rilevare l'USB-VBUS voltage e sono solitamente collegati al VBUS voltage commutato tramite USB[2:1]_PWR. Il circuito di protezione sul TQMa8MPxL consente di applicare fino a 5 V a questi pad LGA. Si consiglia di fornire un condensatore da 220 nF (10 V) ciascuno tra USBx_VBUS e terra sulla scheda portante.

V_LICELL: una cella a bottone può essere collegata al pad LGA D8 TQMa15MPxL, V_LICELL, per alimentare l'RTC discreto opzionale. Vedere il capitolo 3.2.4.2 per informazioni sulle opzioni LICELL o RTC.

Nota: alimentazione RTC

Se un RTC discreto viene alimentato da una cella a bottone, l'RTC interno alla CPU non viene ripristinato in caso di interruzione del volume di alimentazionetage fallimento.

Manuale dell'utente l TQMa8MPxL UM 0105 l © 2024, TQ-Systems GmbH

Pagina 34

3.2.8.5 Uscite di alimentazione Il TQMa8MPxL fornisce tre voltages che possono essere utilizzati sulla scheda portante.

Tabella 28:

Voltage V_1V8 V_3V3 V_3V3_SD

Voltage forniti da TQMa8MPxL

TQMa8MPxL N1 P1 G5

Utilizzo Utilizzo generale sulla scheda carrier Utilizzo generale sulla scheda carrier Alimentazione scheda SD

Massimo. carico 500 mA 500 mA 400 mA

il volumetage V_3V3 può essere utilizzato come segnale Power-Good per l'alimentazione dei circuiti sulla scheda portante.

Attenzione: Distruzione o malfunzionamento, superamento della corrente

Un carico fino a 500 mA su V_1V8 o V_3V3, così come fino a 400 mA su V_3V3_SD provoca un maggiore consumo energetico del TQMa8MPxL e quindi un maggiore autoriscaldamento. Questi tre voltage sono uscite e non devono mai essere alimentate da fonti esterne! Inoltre le uscite non sono a prova di cortocircuito. Sovraccaricare il voltagLe uscite possono danneggiare il TQMa8MPxL.

3.2.8.6 Vol. configurabiletages

Il TQMa8MPxL fornisce quattro pad LGA che definiscono il volume I/Otages per binari specifici della CPU. Questi sono elencati nella tabella seguente e devono essere definiti sulla scheda portante. Se non definito, i corrispondenti segnali I/O non vengono forniti con voltage. A questo scopo il voltagÈ possibile utilizzare V_1V8 o V_3V3.

Tabella 29: Vol. configurabiletages

Segnale

TQMa8MPxL

V_ENET

Numero di modello: AB10

V_SAI1_SAI5

B15

Vol. consentitotages 1.8 V o 3.3 V 1.8 V o 3.3 V

Nota RGMII: 1.8 V RMII: 1.8 V o 3.3 V

V_SAI2_SAI3_SPDIF

A15

1.8 V o 3.3 V

V_SD1

Y19

1.8 V o 3.3 V

Manuale dell'utente l TQMa8MPxL UM 0105 l © 2024, TQ-Systems GmbH

Pagina 35

3.2.8.7 Sequenza di accensione TQMa8MPxL / scheda portante

Poiché il TQMa8MPxL funziona con 5 V e l'I/O voltages dei segnali CPU vengono generati sul TQMa8MPxL, esistono requisiti di temporizzazione per la progettazione della scheda portante rispetto al volumetage generati sulla scheda portante: dopo l'accensione dell'alimentazione a 5 V per il TQMa8MPxL, inizia la sequenza di accensione del PMIC. Gli ingressi TQMa8MPxL esterni pilotati dalla scheda carrier possono essere attivati solo dopo l'accensione di V_3V3. Il pad LGA P1 (V_3V3) può essere utilizzato come feedback.

Numero di telaio

TQMa8MPxL

5 Volt

V_5V_IN

V_3V3

Tavola portante

Numero di telaio

VOUT 3.3 V / 1.8 V / …

Avvio CC/CC 3 V3 < 4 ms

ABILITARE

Figura 20: Schema a blocchi della scheda portante dell'alimentatore

Attenzione: distruzione o malfunzionamento, sequenza di accensione

Per evitare alimentazioni incrociate ed errori nella sequenza di accensione, nessun pin I/O può essere pilotato da componenti esterni finché la sequenza di accensione non è stata completata. La fine della sequenza di accensione è indicata da un livello alto del segnale V_3V3, pad LGA P1.

3.2.8.8 Standby e SNVS

In modalità standby, diversi voltagI controller sul TQMa8MPxL sono spenti. I binari V_1V8_SNVS e V_0V8_SNVS rimangono attivi, il che garantisce il corretto funzionamento dell'RTC.

Manuale dell'utente l TQMa8MPxL UM 0105 l © 2024, TQ-Systems GmbH

3.2.8.9 PMIC Le caratteristiche e le funzioni di tutti i pin e segnali devono essere prese dal Manuale di riferimento i.MX 8M Plus (1) e dalla Scheda tecnica PMIC (4). Il PMIC è controllato dal bus I2C1.

Il PMIC ha l'indirizzo I2C 0x25/010 0101b

Pagina 36

I seguenti segnali PMIC e di gestione dell'alimentazione sono disponibili sui pad LGA TQMa8MPxL

Tabella 30: Segnale

Direzione dei segnali PMIC

PMIC_WDOG_IN#

Unità di produzione individuale

PMIC_RST#

I

RESET_OUT#

BUONO

TQMa8MPxL F6 E6 F7

Gruppo di potenza V_3V3

V_1V8_SNVS 1.8 V

Nota · Ingresso di ripristino PMIC a bassa attività · Attiva il ripristino a freddo · Disattivato per impostazione predefinita

· Ingresso di riposo PMIC a bassa attività con PU interna · Attiva il ripristino a freddo per impostazione predefinita

· Uscita attiva bassa · Connessa a PMIC POR# · Può segnalare un ripristino TQMa8MPxL

SD_VSEL

· Vedi capitolo 3.2.5.20

Attenzione: Distruzione o malfunzionamento, programmazione PMIC

Una programmazione impropria del PMIC può comportare il funzionamento dell'i.MX 8M Plus o della periferica al di fuori delle sue specifiche. Ciò potrebbe causare malfunzionamenti, invecchiamento accelerato o distruzione del TQMa8MPxL.

3.2.9

Impedenze

Per impostazione predefinita, tutti i segnali single-ended hanno un'impedenza nominale del 50 ±10%. Tuttavia, alcune interfacce sul TQMa8MPxL vengono instradate con impedenze diverse, a seconda dei requisiti del segnale.

La seguente tabella è tratta dalla Guida per sviluppatori hardware (3) e mostra le rispettive interfacce:

Tabella 31: Impedenze

Segnale/Interfaccia DDR DQS/CLK; Coppie dati PCIe CLK, TX/RX Segnali USB differenziali Segnali MIPI differenziali (CSI, DSI), HDMI, EARC, LVDS Segnali RGMII differenziali

Impedenza su TQMa8MPxL 85, differenziale 90, differenziale

100, differenziale 100, differenziale

Raccomandazione per scheda portante 85 ±10 %, differenziale 90 ±10 %, differenziale

100 ±10 %, differenziale 100 ±10 %, differenziale

Manuale dell'utente l TQMa8MPxL UM 0105 l © 2024, TQ-Systems GmbH

4.

SOFTWARE

Il TQMa8MPxL viene fornito con un boot loader U-Boot preinstallato. Il BSP fornito da TQ-Systems GmbH è configurato per la combinazione di TQMa8MPxL e MBa8MPxL. Il boot loader U-Boot fornisce impostazioni specifiche per TQMa8MPxL e per la scheda, ad esempio:

· Configurazione i.MX 8M Plus · Configurazione PMIC · Configurazione SDRAM · Configurazione eMMC · Multiplexing · Orologi · Configurazione pin · Punti di forza del driver

Ulteriori informazioni sono disponibili su https://support.tq-group.com/TQMa8MPxL. Se viene utilizzato un altro Bootloader, questi dati devono essere adattati. Contattare il supporto TQ per informazioni dettagliate.

Pagina 37

5.

MECCANICA

5.1

Dimensioni

Manuale dell'utente l TQMa8MPxL UM 0105 l © 2024, TQ-Systems GmbH

Pagina 38

Figura 21: dimensioni TQMa8MPxL, lato view

Tabella 32: Altezze TQMa8MPxL

Scuro.

Valore

A