UG0596

UG0596

Ke alakaʻi hoʻohana

RTG4 FPGA Mana Mana Mana

UG0596 RTG4 FPGA Mea Mana Mana Mana

ʻAʻole hana ʻo Microsemi i kahi palapala hōʻoia, hōʻike, a i ʻole e hōʻoiaʻiʻo e pili ana i ka ʻike i loko a i ʻole ke kūpono o kāna mau huahana a me kāna mau lawelawe no kekahi kumu, ʻaʻole hoʻi e manaʻo ʻo Microsemi i kekahi kuleana i loaʻa mai ka noi a i ʻole ka hoʻohana ʻana i kekahi huahana a kaapuni paha. ʻO nā huahana i kūʻai ʻia ma lalo nei a me nā huahana ʻē aʻe i kūʻai ʻia e Microsemi ua kau ʻia i ka hoʻāʻo liʻiliʻi a ʻaʻole pono e hoʻohana pū ʻia me nā mea hana koʻikoʻi a me nā noi. Manaʻo ʻia nā ʻōlelo kikoʻī a pau e hilinaʻi ʻia akā ʻaʻole i hōʻoia ʻia, a pono ka mea kūʻai aku e alakaʻi a hoʻopau i nā hana āpau a me nā hoʻāʻo ʻē aʻe o nā huahana, hoʻokahi a hui pū me, a i hoʻokomo ʻia i loko o nā huahana hopena. ʻAʻole e hilinaʻi ka mea kūʻai aku i nā ʻikepili a me nā kikoʻī hana a i ʻole nā ʻāpana i hāʻawi ʻia e Microsemi. ʻO ia ke kuleana o ka mea kūʻai aku

hoʻoholo kūʻokoʻa i ke kūpono o nā huahana a e hoʻāʻo a hōʻoia i ka like. ʻO ka ʻike i hāʻawi ʻia e Microsemi ma lalo nei ua hāʻawi ʻia "e like me ia, ma hea" a me nā hewa āpau, a ʻo ka pilikia āpau e pili ana i ia ʻike me ka mea kūʻai aku. ʻAʻole hāʻawi ʻo Microsemi i nā kuleana patent, nā laikini, a i ʻole nā kuleana IP ʻē aʻe, inā e pili ana i ia ʻike ponoʻī a i ʻole kekahi mea i wehewehe ʻia e ia ʻike. ʻO ka ʻike i hāʻawi ʻia ma kēia palapala he kuleana ia iā Microsemi, a mālama ʻo Microsemi i nā hoʻololi i ka ʻike ma kēia palapala a i ʻole nā huahana a me nā lawelawe i kēlā me kēia manawa me ka ʻole o ka hoʻolaha.

E pili ana iā Microsemi

ʻO Microsemi, he lālā paʻa loa o Microchip Technology Inc. (Nasdaq: MCHP), hāʻawi i kahi kōpili piha o nā semiconductor a me nā ʻōnaehana ʻōnaehana no ka aerospace & pale, kamaʻilio, kikowaena data a me nā mākeke ʻoihana.

Loaʻa i nā huahana nā hana kiʻekiʻe a me ka radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs a me ASICs; nā huahana hoʻokele mana; ka manawa a me nā mea hoʻonohonoho hoʻonohonoho a me nā hoʻonā manawa kūpono, e hoʻonohonoho ana i ka pae honua no ka manawa; nā mea hana leo; Nā hoʻonā RF; ʻāpana ʻokoʻa; ka mālama ʻana i nā ʻoihana a me nā hoʻonā kamaʻilio, nā ʻenehana palekana a me nā anti-t scalableampnā huahana; Nā hoʻonā Ethernet; Nā IC Power-over-Ethernet a me nā midspans; a me nā mana hoʻolālā maʻamau a me nā lawelawe. E aʻo hou ma www.microsemi.com.

Moolelo Hooponopono

Hōʻike ka mōʻaukala hoʻoponopono i nā loli i hoʻokō ʻia ma ka palapala. Ua helu ʻia nā hoʻololi e ka loiloi, e hoʻomaka ana me ka paʻi hou loa.

1.1 Hoʻoponopono 2.0

Hoʻouka hou ʻia no ka RTG4 Power Estimator v6a.

1.2 Hoʻoponopono 1.0

ʻO kēia ka puka mua o kēia palapala.

RTG4 FPGA Mana Mana Mana

2.1 Hoolauna

Hōʻike kēia alakaʻi mea hoʻohana i ka RTG4™ Power Estimator no nā ʻohana hāmeʻa RTG4 Field Programmable Gate Array (FPGA). ʻO ka manaʻo manaʻo mua e kōkua i nā mea hoʻolālā e wehewehe i ka hoʻolālā i loko o ka waihona mana ma o ka hoʻohana ʻana i nā hoʻolālā mālama mana. He kōkua pū i nā mea hoʻolālā papa e hoʻolālā a koho i nā lako mana a me ka wela. Hoʻohana ʻia ka puke hana Power Estimator e koho i ka hoʻohana mana mai ka manaʻo hoʻolālā mua a hiki i ka hoʻokō hoʻolālā. Hāʻawi pū ia i nā kikoʻī e pili ana i ka nānā ʻana i ka wela a me nā mea e kōkua ai i ka hoʻohana ʻana i ka mana. Hoʻokomo ʻia nā kumu waiwai, ka alapine hana, nā kumuwaiwai uaki, ka helu hoʻololi, a me nā ʻāpana ʻē aʻe he nui i loko o ka puke hana Power Estimator.

Hoʻohui ʻia kēia mau ʻāpana me nā kumu hoʻohālike mana e koho i ka mana. Hoʻokumu ʻia nā hiʻohiʻona mana ma ka simulation a i ʻole ka ʻikepili o ka mea hana.

ʻO ka pololei o ka manaʻo manaʻo e pili ana i ka ʻikepili i hoʻokomo ʻia i loko o ka puke hana. No laila, e hōʻoia i ka hoʻokomo ʻana i ka ʻikepili maoli i loko o ka hoʻolālā. ʻO ka mana maoli e hilinaʻi nui i ka hoʻolālā RTL maoli, kahi-a-alanui, a me nā kūlana hana. ʻO ka hopena Power Estimator kahi koho mua o ka hoʻohana mana ma mua o ke ana ʻana. E hoʻohana i ka hāmeʻa SmartPower ma ka polokalamu Libero® System-on-Chip (SoC) no ka helu mana pololei a kikoʻī no nā hoʻolālā ma hope o kahi-a-alanui. Pono e ana i ka mana i ka wā e hana ai ka mea hana.

2.1.1 Nā hiʻohiʻona

Loaʻa i ka RTG4 Power Estimator nā hiʻohiʻona aʻe:

- ʻO ka manaʻo o ka hoʻohana mana mai ka pae manaʻo hoʻolālā a hiki i ka hoʻokō.

- Integrated Graphical User Interface (GUI) i loko o ka pepa haʻawina e hoʻomaka i ka Power Estimator a no I/O Bank voltage hoʻonohonoho.

- Manaʻo manaʻo o nā ʻano mana Active a Standby.

- Ka helu mana me ka hoʻohana ʻana i nā hiʻohiʻona.

- E hoʻokaʻawale i ka pepa haʻawina no nā hiʻohiʻona hāmeʻa a me kahi pūʻulu pūʻulu o ka mana i pau i kēlā me kēia hiʻohiʻona.

- Ka helu ʻana i ka mahana Junction a me ke kākoʻo hoʻokomo wela.

2.2 Palapala Hou

- RTG4 FPGA Hua pōkole

- RTG4 FPGA Pin Wehewehe

- RTG4 FPGA Palapala Hoʻohana

- RTG4 FPGA High Speed DDR Interfaces Ke alakaʻi hoʻohana

- RTG4 FPGA High Speed Serial Interfaces Guide

- RTG4 FPGA Mea Hoʻohana Mea Hoʻohana Punawai

- Ke alakaʻi hoʻohana ʻo Libero SoC

2.3 Hoʻomaka ʻana i ka Mana Mana Mana

Aia kēia ʻāpana i nā ʻāpana lalo:

- Pono Pūnaewele, ʻaoʻao 3

- Hoʻoiho i ka Power Estimator a me ka Enabling Macros, ʻaoʻao 3

- ʻO nā koi hoʻokomo liʻiliʻi, ʻaoʻao 5

2.3.1 Pono Pūnaewele

- Pono ka puke hana Power Estimator iā Microsoft Excel. Hōʻike ka Papa 1 i ka polokalamu i kākoʻo ʻia.

- ʻōnaehana hana Windows.

Papa 1 • Kākoʻo lako polokalamu

Kākoʻo lako polokalamu

Microsoft Excel 2003

Microsoft Excel 2007

Microsoft Excel 2010

Microsoft Excel 2013

Nānā: ʻAʻole kākoʻo ʻia nā mea hoʻoponopono palahalaha OpenOffice a me Google Docs.

2.3.2 Hoʻoiho ʻana i ka Mana Mana Mana a me ka Hoʻonā ʻana i nā Macros

Hiki ke hoʻoiho ʻia ka puke hana Power Estimator no nā polokalamu RTG4 hou mai:

https://www.microsemi.com/document-portal/doc_download/1244030-rtg4-power-calculator

He mau macros i kūkulu ʻia i loko o ka puke hana Power Estimator. Ma ka paʻamau, ua hoʻonohonoho ʻia ka pae palekana macro ma Microsoft Excel i High. Hoʻopau ʻia nā macros inā hoʻonohonoho ʻia ka pae palekana macro i Kiʻekiʻe. E hōʻoia i ka ʻae ʻana o nā hoʻonohonoho Microsoft Excel i nā hoʻokō macro no ka puke haʻawina Power Estimator e hana pono.

Hōʻike nā ʻāpana aʻe i ka hoʻololi ʻana i nā hoʻonohonoho palekana macro ma nā mana like ʻole o ka polokalamu Microsoft Excel:

- Microsoft Excel 2003, ʻaoʻao 3

- Microsoft Excel 2007, ʻaoʻao 3

- Microsoft Excel 2010 a me 2013, ʻaoʻao 5

2.3.2.1 Microsoft Excel 2003

- E wehe i ka Power Estimator Excel file a koho i nā mea hana > Macro > Security mai ka papa kuhikuhi nui.

Kiʻi 1 • Nā hoʻonohonoho pae palekana Macro ma Microsoft Excel 2003

- Mai ka pahu kūkākūkā Macro Security, kaomi i ka ʻaoʻao Security Level, a koho i ka Medium. Kaomi OK.

- Pani i ka Mana Mana file a wehe hou.

- Kaomi iā Enable Macros ke koi ʻia e hiki i nā macros.

2.3.2.2 Microsoft Excel 2007

- E wehe i ka Power Estimator Excel file a kaomi i ke pihi Office ma ka ʻaoʻao hema hema.

- Kaomi iā Excel Options.

Kiʻi 2 • Nā hoʻonohonoho pae palekana Macro ma Microsoft Excel 2007

- Kaomi i ka Trust Center mai ka ʻaoʻao hema.

- Kaomi i ka Trust Center Settings….

- Mai ka pukaaniani Trust Center, e kaomi i ka Macro Settings mai ka ʻaoʻao hema. E koho Hoʻopau i nā macros āpau me ka hoʻolaha a kaomi iā OK.

- Pani i ka Mana Mana file a wehe hou.

- Hōʻike ʻia kahi leka hoʻomaopopo palekana ma lalo o ka lipine Office. Kaomi i nā koho.

- Koho i ka Enable this content in the Microsoft Office Security Options window.

2.3.2.3 Microsoft Excel 2010 a me 2013

- E wehe i ka Power Estimator Excel file.

- Kaomi i ka File ʻaoʻao a kaomi i nā koho.

Kiʻi 3 • Nā hoʻonohonoho pae palekana Macro ma Microsoft Excel 2010 a me 2013

- Kaomi i ka Trust Center mai ka ʻaoʻao hema.

- Kaomi i ka Trust Center Settings….

- Mai ka pukaaniani Trust Center, e kaomi i ka Macro Settings mai ka ʻaoʻao hema. E koho Hoʻopau i nā macros āpau me ka hoʻolaha a kaomi iā OK.

- Pani i ka Mana Mana file a wehe hou.

- Hōʻike ʻia kahi leka hoʻomaopopo palekana ma lalo o ka lipine Office. Kaomi i nā koho.

- Koho i ka Enable this content in the Microsoft Office Security Options window.

2.3.3 Nā Koina Hoʻokomo Haʻahaʻa

ʻO ka manaʻo manaʻo no nā mea RTG4 e hilinaʻi nui ʻia i ka nui o nā loina i loaʻa i ka FPGA Fabric.

Eia nā koi hoʻokomo haʻahaʻa loa no ka manaʻo mana kūpono kūpono:

- E koho i kahi mea hana kūpono me nā kūlana hana kūpono.

- Ka helu kūpono o nā kumuwaiwai FPGA Fabric (no ka example, flip-flops, LUTs, LSRAM, uSRAM, MACC, a me I/O).

- ʻO ka manaʻo kūpono o nā kikowaena serial a me DDR.

- Pūnaehana uaki a me ka uaki domain.

- E hoʻololi i ka nui o ka loiloi a me I/Os.

- E ho'ā, kākau, a heluhelu i nā helu no nā RAM.

2.4 Puke Hana Excel no ka mea helu mana

Hōʻike kēia ʻāpana i kēlā me kēia pepa hana o ka puke haʻawina RTG4 Power Estimator Excel. Loaʻa nā pepa haʻawina kaʻawale no nā hiʻohiʻona o ka mea hana. Eia kekahi, loaʻa kahi subtotal o ka mana i pau i kēlā me kēia hiʻohiʻona. Hiki ke hoʻokomo ʻia nā kikoʻī hoʻohana a me nā hana o nā kumuwaiwai like ʻole i loaʻa i ka hāmeʻa RTG4 i manaʻo ʻia (no ka example, flip-flops, LUTs, LSRAM, uSRAM, MACC, I/O, high speed serial and DDR interfaces, system clock and clock domain, toggle rate of logic, and I/Os). Hāʻawi ka ʻāpana Power Summary i ka pepa haʻawina Summary i ka nui o ka mana a me ka haki ʻana o ka mana ma ke kaʻaahi a me ke ʻano kumu waiwai.

Aia kēia ʻāpana i nā ʻāpana lalo:

- Hoʻopili kala kala, ʻaoʻao 6

- Manaʻo ʻia ke kahe, ʻaoʻao 6

2.4.1 Hoʻopili kala kala

He mau pepa hana ka RTG4 Power Estimator Excel. Hoʻopili kala ʻia nā keena o kēlā me kēia pepa haʻawina no ka maʻalahi o ka hoʻokomo ʻana i ka ʻikepili a me ka review.

Papa 2 i na waihooluu a me ka wehewehe.

Papa 2 • Hoʻopili kala kelepona

| kala kelepona | Hana Mea hoʻohana | wehewehe |

| Hiki ke hoʻoponopono | Hiki i ka mea hoʻohana ke hoʻokomo i ka ʻikepili | |

| Hiki ole ke hooponopono | ʻAʻole hiki i ka mea hoʻohana ke hoʻokomo i ka ʻikepili | |

| Heluhelu-wale | Helu helu | |

| Heluhelu-wale | Nā waiwai hōʻuluʻulu | |

| Heluhelu-wale | Kuhihewa |

2.4.2 Manaʻo Kahe

2.4.2.1 Kaʻina – 1: Nā hoʻonohonoho

E koho i ka mea hana, pūʻolo, ka pae wela, ke kūlana hana, a me nā hoʻonohonoho hoʻokomo wela.

2.4.2.2 KaʻAnuʻu – 2: Hoʻonohonoho ʻano hana

E hoʻonohonoho i ka ʻike kikoʻī hoʻolālā i hoʻohana ʻia no ka helu ʻana i ka mana ikaika.

- Nā ʻāpana lole FPGA:

- Hoʻonohonoho i nā ʻāpana FPGA Fabric a me kā lākou mau alapine hana.

- I/Os:

- Hoʻonohonoho i ka ʻenehana I/O a me kā lākou mau alapine hana.

- Nā poloka i kūkulu ʻia (SERDES a me FDDR):

- E hoʻonohonoho i nā subsystem SERDES a me DDR me nā hoʻonohonoho kūpono.

2.4.2.3 KaʻAnuʻu – 3: Nā hiʻohiʻona

Koho: Hoʻohou i ka pākēnekatagʻO ka manawa e pono ai ka hāmeʻa ma ke ʻano i hāʻawi ʻia i kona manawa hana (no ka laʻana, 50% o ka manawa Active a me 50% i Standby).

2.4.2.4 KaʻAnuʻu – 4: Hōʻuluʻulu Mana Mana

Hāʻawi ka ʻāpana hōʻuluʻulu mana ma ka pepa haʻawina Summary i ka nui o ka mana a me kona haki ʻana ma muli o nā kumu mana a me nā alahao. Hōʻike ʻia ka nui o ka mana no ka hiʻohiʻona ma ka Step – 3: Scenarios, ʻaoʻao 22.

Hōʻike kikoʻī kēia mau ʻāpana i kēia mau ʻanuʻu:

- KaʻAnuʻu - 1: Nā hoʻonohonoho, ʻaoʻao 7

- KaʻAnuʻu - 2: Active Mode Configuration, ʻaoʻao 10

- KaʻAnuʻu – 3: Nā hiʻohiʻona, ʻaoʻao 22

- KaʻAnuʻu - 4: Hōʻuluʻulu Manaʻo Manaʻo, ʻaoʻao 23

2.5 Kaʻina – 1: Nā hoʻonohonoho

Hōʻike ka Figure 4 i ka ʻāpana Settings ma ka Summary worksheet.

Kiʻi 4 • Māhele Hoʻonohonoho i ka Pepa Haʻawina Hōʻuluʻulu

Hōʻike ka papa 3 i nā hoʻonohonoho General and Thermal Inputs ma ka ʻāpana Settings o ka Summary worksheet. E hōʻoia e koho ʻoe i ka hāmeʻa me nā kūlana hana kūpono.

| Nā ʻāpana | wehewehe |

| Nā hoʻonohonoho maʻamau | |

| ʻOhana | RTG4 |

| Mea lako | E koho i ka mea hana. Kākoʻo ʻia nā mea hana penei: • RT4G150L |

| Pūʻolo | E koho i ka pūʻolo. |

| Kaulana | E koho i ka papa huahana. Loaʻa nā māka ma lalo nei. • E Koa Papa wela no nā pae like ʻole: • Koa E (-55°C a 125°C) |

| Koko Voltage | lako kumu voltage (1.2 V) |

| Kaʻina hana | E koho i ke kaʻina hana. Loaʻa kēia mau kūlana: • maʻamau Nā moʻokāki kaʻina hana no nā ʻano like ʻole o ke kaʻina hana e pili ana i ka pau ʻana o ka mana. Hoʻohana maʻamau nā kumu hoʻoheheʻe mana no kāu hoʻolālā. Voltage a me ka Mahana i hoomaluia kaawale mai ke kaʻina hana. |

| Mokuʻāina ʻikepili | Kiʻekiʻe: ʻO ka ʻike i manaʻo mua ʻia e pili ana i ka simulation, nā huahana ʻē aʻe, nā mea hana, a i ʻole nā māka wikiwiki. Hiki ke hoʻohana ʻia kēia ʻike ma ke ʻano he koho, akā ʻaʻole no ka hana. mua: ʻIke pili i ka simulation a/a i ʻole ka hōʻike mua. Manaʻo ʻia he pololei ka ʻike, akā hiki ke loli. Hana ʻia: ʻO ka ʻike i manaʻo ʻia he hope loa. |

| Nā mea hoʻokomo wela | |

| Ka Mahana Huina Tj (°C) Nānā: ʻAʻole loaʻa ka ʻikepili wela. Kākoʻo wale ʻia ke koho TJ i komo. |

E komo i ka Junction Temperature o ka mea hana. Loaʻa kēia kahua inā koho ʻia ka mea hoʻohana i komo i ke koho TJ. I kēia hihia, pio nā kahua hoʻokomo wela ʻē aʻe. Ke koho ʻia ka koho TJ i koho ʻia, helu ʻia ka mahana o ka hui ma muli o nā hoʻokomo wela i hoʻokomo ʻia. |

| Ka Mahana Kaiapuni Ta (°C) | E hoʻokomo i ka mahana o ka ea e hoʻopuni ana i ka mea hana. Loaʻa kēia kahua inā koho ʻia ke koho TJ i koho ʻia. ʻO nā pae wela kūpono: • E Koa: -55°C a hiki i 125°C Ke koho ʻia ʻo Estimated Theta JA koho, hoʻohana ʻia kēia kahua no ka helu ʻana i ka mahana o ka hui ma muli o ke kūpaʻa wela a me ka dissipation mana. Ke koho ʻia ʻo Custom Theta JA koho, hoʻohana ʻia kēia kahua e helu i ka mahana o ka hui e pili ana i ka qJA Effective a me ka dissipation mana. |

| qJA pono | Kūleʻa wela kūpono. Hoʻohana ʻia ka mea hoʻohana i koho ʻia, ka pūʻolo, ka ea, ka wela a me ke ʻano o ka papa me ka ʻike kikoʻī a me ka simulation e helu ai i ke kūpaʻa wela kūpono. No ke komo ʻana i kahi Theta JA kūpono maʻamau, koho ʻo Custom Theta JA a hoʻokomo i kahi waiwai, no ka helu ʻana i nā kūlana i uhi ʻole ʻia e nā koho i loaʻa a i ʻole kahi i hana ʻia ai ka hoʻohālike wela. Hoʻopau ʻia nā kahua ma lalo ke koho ʻia ʻo Custom Theta JA a hiki ke koho ʻia ʻo Estimated Theta JA i koho ʻia: • E Pumi Wela • Ke Kahe Ea • QSA maʻamau E (°C/W) • E Papa Hoʻohālike Thermal |

| Pahu wela | E koho i kekahi o kēia mau koho: •ʻAʻohe • Kuʻuna • 10 mm-Low Profile • 15 mm-Medium Profile • 20 mm-Kiʻekiʻe Profile Hoʻohana ʻia kēia kahua inā koho ʻia nā koho Estimated TJ a me Theta JA i koho ʻia. |

| Kaʻea ea | E koho i kahi kahe ea ambient i mika no kekona (m/s): • 1.0 m/s • 2.5 m/s Hoʻohana ʻia kēia kahua inā koho ʻia nā koho Estimated TJ a me Theta JA i koho ʻia. Hoʻemi ʻia ka mahana o ka hui inā hoʻonui ʻia ka ea ambient. |

| qSA maʻamau (°C/W) | Inā koho ʻia kahi puʻu wela maʻamau, e hoʻokomo i ka pale wela wela-a-ambient mai ka ʻikepili wela. Hoʻohana ʻia kēia kahua inā koho ʻia nā koho Estimated TJ a me Theta JA i koho ʻia. |

| Ke Ana Hoʻohālike Papa | E koho i kekahi o kēia mau koho: • ʻAʻohe (Conservative) • JEDEC (2s2p) Hoʻohana ʻia kēia kahua inā koho ʻia nā koho Estimated TJ a me Theta JA i koho ʻia. Inā koho ʻia ʻAʻohe (Conservative), manaʻo ke kumu hoʻohālike wela ʻaʻohe wela i hoʻopau ʻia ma ka papa. Inā koho ʻia ke koho JEDEC (2s2p), manaʻo ke kumu hoʻohālike wela nā hiʻohiʻona o ka papa hoʻāʻo JEDEC 2s2p i kuhikuhi ʻia i ka maʻamau JESD51-9. |

2.6 KaʻAnuʻu – 2: Hoʻonohonoho ʻano hana

Ma kēia ʻāpana, e hoʻokomo i ka ʻike kikoʻī i hiki ke hoʻohana ʻia e helu i ka mana ikaika.

Loaʻa iā ia nā ʻāpana lalo:

- E hoʻomaka i ka Wizard Estimator Power, ʻaoʻao 10

- Nā Mea Hana lole FPGA, ʻaoʻao 11

- I/O, aoao 17

- Nā poloka i kūkulu ʻia, ʻaoʻao 19

2.6.1 Hoʻomaka i ka Wizard Mea Manaʻo Mana

Loaʻa i ka Pepa Haʻawina Summary kahi wizard hoʻohālikelike mana. Kaomi i ka Initialize Power Estimator ma ka ʻaoʻao hema o ka pepa haʻawina no ke kāhea ʻana i ka wizard Initialize Power Estimator. Hiki i kēia wizard ke koho i ka ʻike kikoʻī kikoʻī. Ma ka holo ʻana i ka wizard, hoʻopiha ʻo ia i ka pālahalaha Power Estimator me ka ʻike kikoʻī hoʻolālā a koho i ka mana no ka hoʻolālā. E hoʻololi i nā mea hoʻokomo wizard e hāʻawi i nā mea hoʻokomo pololei i ka Power Estimator.

Hōʻike ka Figure 5 i ka wizard Initialize Power Estimator.

Kiʻi 5 • Wizard Nānā Mana Mana

Hāʻawi ka wizard Power Estimator i nā kahua ma muli o ka ʻohana huahana i koho ʻia:

- FDDR

E koho i ke ʻano hoʻomanaʻo, laula, ECC, ODT, a me FDDR_CLK.

ʻO 333 MHz ka alapine kiʻekiʻe o FDDR_CLK. - SERDES_IF

E koho i ka sub-system PCIE (PCIESS), non-PCIE sub-system (NPSS), Protocol, Number of Lanes, AXI/AHB_CLK (PCIe) clock, a me Ref Clk Freq. - Ka lole FPGA

- Uaki Pūnaehana

E wehewehe i ke alapine uaki o ka lole. Ma ka maʻamau, ua hoʻonohonoho ʻia i 100 MHz. Aia nā helu kūpono ma waena o 0 a 300 MHz. - Hoʻohana Hoʻolālā

E hoʻohana i ka papa kuhikuhi hāʻule iho e kūʻē i ka Set all FPGA Fabric Resources e hoʻonoho i kahi pākēnekatage waiwai no nā kumuwaiwai a pau i ka manawa hoʻokahi. He pākēnekatagHiki ke hoʻonohonoho ʻia ka waiwai no kēlā me kēia kumuwaiwai e hoʻohana ʻia me ka hoʻohana ʻana i ka pahu paheʻe i nā kumuwaiwai.

Eia nā kumuwaiwai i loaʻa:

* Nā Paʻi-Flops

* LUTs

* uSRAM

* LSRAM

* MACC - I/O

E koho i ka ʻenehana I/O a hoʻokomo i ka helu o nā hoʻokomo a me nā mea hoʻopuka. - Ka helu hoʻololi paʻamau

E hoʻokomo i ka helu hoʻololi i ka pākēnekatage. E pili ana kēia helu hoʻololi i nā module logic a me I/Os. - Ka helu hoʻāno RAM paʻamau

E hoʻokomo i ka helu hiki i ka pākēnekatage. Hoʻopili kēia helu hiki iā uSRAM a me LSRAM.

Nānā: Ke neʻe ka manamana lima paheʻe ma waena o nā helu hope o ke ala paheʻe, e hōʻano hou ʻia ka waiwai ma ke kahua kikokikona e pili ana.

No ka hoʻopiha ʻana i ka pāpalapala Power Estimator me nā waiwai i hoʻokomo ʻia, kaomi iā OK.

2.6.2 Nā ʻāpana lole FPGA

Hōʻike kēia ʻāpana i ka hoʻolālā ʻana o ka ʻike kikoʻī no nā ʻāpana FPGA Fabric i hoʻohana ʻia e helu i ka mana ikaika. Hāʻawi ka RTG4 Power Estimator i nā pepa hana ʻokoʻa no kēlā me kēia ʻāpana FPGA Fabric. Ua wehewehe ʻia kēia mau pepa hana ma nā ʻāpana:

- Uaki, aoao 11

- Logic, aoao 12

- LSRAM, aoao 13

- uSRAM, aoao 14

- Palena Math, aoao 15

- CCC, aoao 16

2.6.2.1 Uaki

Kākoʻo nā mea ʻenehana RTG4 i nā pūnaewele uaki honua wale nō. Hōʻike kēlā me kēia lālani i ka pepa haʻawina Clock i kahi kikowaena uaki ʻokoʻa.

E hoʻokomo i kēia mau ʻāpana no kēlā me kēia kikowaena uaki:

- inoa

- Ka pinepine o ka uaki (MHz)

- Fanout

- Ka Laki Hoʻonā honua

Hōʻike ke kiʻi 6 i ka pepa hana Uaki.

Kiʻi 6 • Pepa Haʻawina Uaki

Hōʻike ka papa 4 i nā ʻāpana e hoʻokomo ʻia i ka pepa haʻawina Clock.

Papa 4 • Nā ʻāpana o ka pepa hana uaki

| Nā ʻāpana | wehewehe |

| inoa | E hoʻokomo i ka inoa no kēlā me kēia kikowaena uaki (koe). |

| Ka pinepine o ka uaki (MHz) | E hoʻokomo i ke alapine o ka uaki o ka waihona. ʻO ka alapine kiʻekiʻe o ka lole FPGA he 300 MHz. |

| Fanout | E hoʻokomo i ka helu o nā mea hoʻopaʻa inoa a me nā mea like ʻole (LSRAM, uSRAM, Math Block, a me I/O). |

| Ka Laki Hoʻonā honua | E hoʻokomo i ka pākēneka maʻamautagʻO ka manawa e hiki ai ka uaki ke kiʻekiʻe no kēlā me kēia kikowaena uaki. |

No ka ʻike hou aku e pili ana i nā pūnaewele uaki o nā ʻohana mea i kākoʻo ʻia, e nānā iā RTG4 FPGA Alakaʻi Hoʻohana Mea Hoʻohana ʻo Clocking Resources.

2.6.2.2 Loko

Hōʻike ʻia kēlā me kēia lālani i ka pepa haʻawina Logic i kahi kikowaena uaki ʻokoʻa.

E hoʻokomo i kēia mau ʻāpana no kēlā me kēia kikowaena uaki:

- inoa

- Ka pinepine o ka uaki (MHz)

- Ka helu o na kakau inoa

- Ka helu o na LUT

- Fanout

- Hoʻololi i ka helu

Hōʻike ka Figure 7 i ka pepa hana Logic.

Kiʻi 7 • Pepa Haʻawina Logic

Hōʻike ka papa 5 i nā ʻāpana e hoʻokomo ʻia i ka pepa hana Logic.

Papa 5 • Nā Kūlana Pepa Haʻawina Logic

| Nā ʻāpana | wehewehe |

| inoa | E hoʻokomo i ka inoa no kēlā me kēia kikowaena uaki (koe). |

| Ka pinepine o ka uaki (MHz) | E hoʻokomo i ke alapine o ka uaki o ka waihona. ʻO ka alapine kiʻekiʻe o ka lole FPGA he 300 MHz. |

| Ka helu o na kakau inoa | E hoʻokomo i ka helu o nā papa inoa no kēlā me kēia kikowaena uaki. |

| Ka helu o na LUT | E hoʻokomo i ka helu o nā modula LUT maʻamau (combinatorial). |

| Fanout maʻamau | E hoʻokomo i ka fanout maʻamau o nā ʻupena i alakaʻi ʻia e nā papa inoa a me nā LUT. |

| Hoʻololi i ka helu | E hoʻokomo i ka helu toggle o ka hoʻopaʻa inoa a me nā huahana LUT. |

No ka ʻike hou aku e pili ana i ka Logic Element o nā ʻohana mea i kākoʻo ʻia, e nānā iā RTG4 FPGAFabric User Guide.

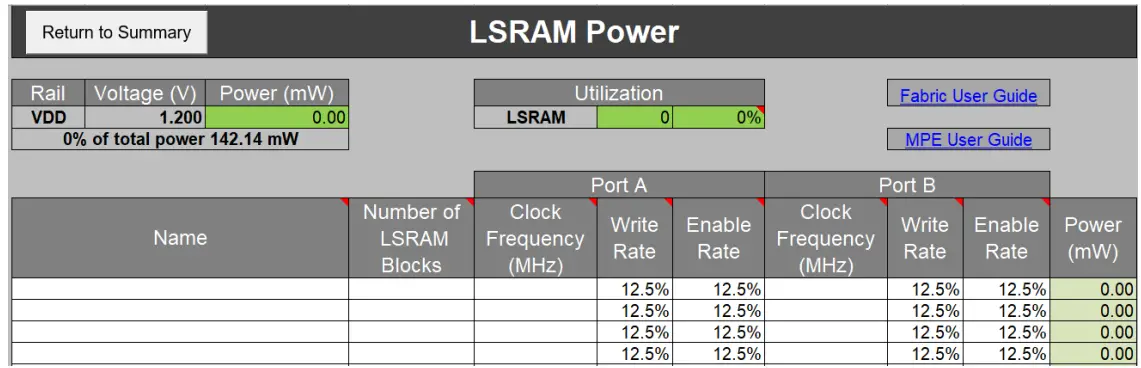

2.6.2.3 LSRAM

Hōʻike kēlā me kēia lālani i ka pepa haʻawina LSRAM i kahi kikowaena uaki ʻokoʻa.

E hoʻokomo i kēia mau ʻāpana no kēlā me kēia kikowaena uaki:

- inoa

- Ka helu o nā poloka LSRAM

- Awa A – Ka pinepine Uki (MHz)

- Awa A – Kakau Kākau

- Awa A – E ho'ā i ka uku

- Awa B – Ka pinepine Uki (MHz)

- Awa B – Kakau Kākau

- Awa B – E ho'ā i ka uku

Hōʻike ka helu 8 i ka pepa hana LSRAM.

Kiʻi 8 • LSRAM Pepa Haʻawina

Hōʻike ka papa 6 i nā ʻāpana e hoʻokomo ʻia i ka pepa haʻawina LSRAM.

Papa 6 • Nā Kūlana Pepa Hana LSRAM

| Nā ʻāpana | wehewehe |

| inoa | E hoʻokomo i ka inoa o ka module a i ʻole ka waihona uaki me ka LSRAM. |

| Ka helu o nā poloka LSRAM | E hoʻokomo i ka helu o nā poloka LSRAM. |

| Awa A – Ka pinepine Uki (MHz) | E hoʻokomo i ke alapine o ka uaki no Port A o nā poloka LSRAM. Kākoʻo ia i ka alapine kiʻekiʻe a hiki i 300 MHz. |

| Awa A – Kakau Kākau | E komo i ka pākēnekatagʻo ka manawa i hoʻohana ʻia ai ʻo Port A no nā hana kākau. Hoʻohana ʻia ka manawa i koe no nā hana heluhelu. |

| Awa A – E ho'ā i ka uku | E komo i ka pākēnekatage o ka manawa i hiki ai ke Port A. |

| Awa B – Ka pinepine Uki (MHz) | E hoʻokomo i ke alapine o ka uaki no Port B o nā poloka LSRAM. Kākoʻo ia i ka alapine kiʻekiʻe a hiki i 300 MHz. |

| Awa B – Kakau Kākau | E komo i ka pākēnekatagʻO ka manawa e hoʻohana ʻia ai ʻo Port B no nā hana kākau. Hoʻohana ʻia ka manawa i koe no nā hana heluhelu. |

| Awa B – E ho'ā i ka uku | E komo i ka pākēnekatage o ka manawa i hiki ai ke Port B. |

No ka ʻike hou aku e pili ana i ka LSRAM o nā ʻohana mea i kākoʻo ʻia, e nānā iā RTG4 FPGA Fabric User Guide.

2.6.2.4 uSRAM

Hōʻike kēlā me kēia lālani i ka pepa haʻawina uSRAM i kahi kikowaena uaki ʻokoʻa.

E hoʻokomo i kēia mau ʻāpana no kēlā me kēia kikowaena uaki:

- inoa

- Ka helu o nā poloka uSRAM

- ʻAwa A – Heluhelu i ke alapine (MHz)

- Awa A – E ho'ā i ka uku

- ʻAwa B – Heluhelu i ke alapine (MHz)

- Awa B – E ho'ā i ka uku

- Awa C – Kākau i ka pinepine Uki (MHz)

- Awa C – Enable Rate

Hōʻike ka helu 9 i ka pepa hana uSRAM.

Kiʻi 9 • uSRAM Pepa Haʻawina

Hōʻike ka papa 7 i nā ʻāpana e hoʻokomo ʻia i ka pepa haʻawina uSRAM.

Papa 7 • uSRAM Pepa Haʻawina

| Nā ʻāpana | wehewehe |

| inoa | E hoʻokomo i ka inoa o ka module a i ʻole ka uSRAM. |

| Ka helu o nā poloka uSRAM | E hoʻokomo i ka helu o nā poloka uSRAM. |

| ʻAwa A – Heluhelu i ke alapine (MHz) | E hoʻokomo i ke alapine o ka uaki heluhelu no Port A o nā poloka uSRAM. Kākoʻo ia i ka alapine kiʻekiʻe a hiki i 300 MHz. |

| Awa A – E ho'ā i ka uku | E komo i ka pākēnekatage o ka manawa i hiki ai ke Port A. |

| ʻAwa B – Heluhelu i ke alapine (MHz) | E hoʻokomo i ke alapine uaki heluhelu no Port B o nā poloka uSRAM. Kākoʻo ia i ka alapine kiʻekiʻe a hiki i 300 MHz. |

| Awa B – E ho'ā i ka uku | E komo i ka pākēnekatage o ka manawa ua hiki ke Port B. |

| Awa C – Kākau i ka pinepine Uki (MHz) | E hoʻokomo i ke alapine o ka uaki kākau no Port C o nā poloka uSRAM. Kākoʻo ia i ka alapine kiʻekiʻe a hiki i 300 MHz. |

| Awa C – Enable Rate | E komo i ka pākēnekatage o ka manawa i hiki ai ke Port C. |

No ka ʻike hou aku e pili ana i ka uSRAM o nā ʻohana hāmeʻa i kākoʻo ʻia, e nānā iā RTG4 FPGA Fabric User Guide.

2.6.2.5 Pāka Makemakika

Hōʻike kēlā me kēia lālani i ka pepa haʻawina Math Block i kahi kāʻei uaki ʻokoʻa.

E hoʻokomo i kēia mau ʻāpana no kēlā me kēia kikowaena uaki:

- inoa

- Ka pinepine o ka uaki (MHz)

- Ka helu o nā poloka Matematika

- Ka helu hoʻololi ʻikepili

Hōʻike ka Helu 10 i ka pepa haʻawina Math Block.

Kiʻi 10 • Pepa Haʻawina Pākīpika

Hōʻike ka papa 8 i nā ʻāpana e hoʻokomo ʻia i ka pepa haʻawina Math Block.

Papa 8 • Nā ʻāpana o ka Pepa Haʻawina Pākīpika

| Nā ʻāpana | wehewehe |

| inoa | E hoʻokomo i ka inoa o ka module a i ʻole ka pūnaewele uaki i loaʻa iā Math Block. |

| Ka pinepine o ka uaki (MHz) | E hoʻokomo i ka pinepine uaki o ka waihona. ʻO 300 MHz ka alapine kiʻekiʻe o ka Math Block. |

| Ka helu o nā poloka Matematika | E hoʻokomo i ka helu o nā poloka makemakika no kēlā me kēia kāʻei kuaki. |

| Ka helu hoʻololi ʻikepili | E hoʻokomo i ka awelika ʻikepili kaʻa kaʻa. |

No ka ʻike hou aku e pili ana i ka Math Block o nā ʻohana mea i kākoʻo ʻia, e nānā iā RTG4 FPGA Fabric User Guide.

2.6.2.6 CCC

Loaʻa i nā polokalamu RTG4 ʻewalu CCC. Hiki i kēlā me kēia CCC ke hoʻohana i nā papa hana uʻi maʻalahi no ka loiloi i hoʻokō ʻia ma ka FPGA Fabric a hiki ke hāʻawi i ka uaki kumu no nā poloka IP paʻakikī ma-chip e like me FDDR a me SERDESIF.

E hoʻokomo i kēia mau ʻāpana no kēlā me kēia CCC:

- inoa

- Hōʻike ʻana i ke alapine (MHz)

- PLL Puke alapine (MHz)

- Puke 1 alapine (MHz)

- Puke 2 alapine (MHz)

- Puke 3 alapine (MHz)

- Puke 4 alapine (MHz)

Hōʻike ka Kiʻi 11 i ka ʻāpana CCC Power ma ka pepa hana CCC.

Helu 11 • Pauku Mana CCC

Hōʻike ka Papa 9 i nā ʻāpana e hoʻokomo ʻia ma ka ʻāpana CCC Power o ka pepa hana CCC.

Papa 9 • Nā ʻāpana ʻāpana CCC

| Nā ʻāpana | wehewehe |

| inoa | E hoʻokomo i ka inoa o ka module CCC. |

| Hōʻike ʻana i ke alapine (MHz) | E hookomo i ke alapine o ka uaki kuhikuhi. |

| PLL Puke alapine (MHz) | E hoʻokomo i ke alapine puka PLL. |

| Puke 1 alapine (MHz) | E hoʻokomo i ke alapine output1 (GL0/Y0). |

| Puke 2 alapine (MHz) | E hoʻokomo i ke alapine output2 (GL1/Y1). |

| Puke 3 alapine (MHz) | E hoʻokomo i ke alapine output3 (GL2/Y2). |

| Puke 4 alapine (MHz) | E hoʻokomo i ke alapine output4 (GL3/Y3). |

No ka ʻike hou aku e pili ana i ka CCC o nā ʻohana hāmeʻa i kākoʻo ʻia, e nānā iā RTG4 FPGA Clocking Resources User Guide.

2.6.3 I/O

Hoʻokomo ʻia ka ʻike kikoʻī hoʻolālā i ka pepa hana I/O no nā I/O i hoʻohana ʻia no ka helu ʻana i ka mana ikaika.

Hōʻike kēlā me kēia lālani i ke alapine o ka uaki a me kahi kikowaena I/O.

E hoʻokomo i kēia mau ʻāpana no kēlā me kēia lālani:

- inoa

- ʻAno Panakō

- I/O maʻamau

- I/P Pin

- O/P Pin

- Bidir Pins

- ODT

- Puka Puka (mA)

- Haawe Huhua (pF)

- Uaki (MHz)

- Ka helu ʻikepili

- Hoʻololi i ka helu

- Hiki ke hoʻopuka

- Hiki iā ODT

Hōʻike ka helu 12 i ka pepa hana I/O.

Kiʻi 12 • Pepa Haʻawina I/O

Hōʻike ka papa 10 i nā ʻāpana e hoʻokomo ʻia i ka pepa hana I/O. ʻAʻole ʻike ʻia nā hoʻonohonoho I/O kiʻekiʻe, Schmitt trigger, Pre-emphasis, a me Slew ma ka paʻamau. E koho Show Advanced I/O Settings e wehe i kēia mau kolamu.

Papa 10 • I/O Nā Palena Pepa Hana

| Nā ʻāpana | wehewehe | |

| inoa | E hoʻokomo i inoa no kēlā me kēia I/O, kaʻa a i ʻole module. | |

| Nā hoʻonohonoho I/O | ʻAno Panakō | E koho i ke ʻano panakō. Kākoʻo i nā ʻano panakō penei: •MSIO •MSIOD •DDRIO |

| I/O maʻamau | E koho i ke kūlana I/O kūpono. | |

| UP Pins | E hoʻokomo i ka helu o nā pine hoʻokomo a i ʻole nā pālua ʻokoʻa i hoʻohana ʻia no kēlā me kēia I/O, kaʻa a i ʻole module. Pono e noʻonoʻo ʻia ka hui ʻokoʻa ma ke ʻano he pine hoʻokahi. | |

| 0/P Pin | E hoʻokomo i ka helu o nā pine puka a i ʻole nā pālua ʻokoʻa i hoʻohana ʻia no kēlā me kēia I/O, kaʻa a i ʻole module. Pono e noʻonoʻo ʻia ka hui ʻokoʻa ma ke ʻano he pine hoʻokahi. | |

| Bidir Pins | E hoʻokomo i ka helu o nā pine bidirectional a i ʻole nā pālua ʻokoʻa i hoʻohana ʻia no kēlā me kēia I/O, kaʻa a i ʻole module. Pono e noʻonoʻo ʻia ka paʻa ʻokoʻa he pine hoʻokahi. | |

| ODT | E koho i ka Input On-die termination impedance. | |

| Puka Puka (mA) | E koho i ka hoʻokuke puka i kēia manawa. | |

| Haawe Huhua (pF) | E komo i ka papa a me nā capacitance waho ʻē aʻe. | |

Papa 10 • Nā ʻāpana pepa hana I/O (hoʻomau ʻia)

| Nā ʻāpana | wehewehe | |

| Hana I/O | Uaki (MHz) | E hoʻokomo i ka pinepine uaki o ka waihona. Kākoʻo ia i ka alapine kiʻekiʻe a hiki i 300 MHz. |

| Ka helu ʻikepili | No nā I/0s i hoʻohana ʻia ma ke ʻano he wati, koho i ka uaki e like me ka helu ʻikepili. No nā mea ʻē aʻe, koho i ka ʻikepili. | |

| Hoʻololi i ka helu | E hoʻokomo i ka pākēneka maʻamautage o ka hookomo, ka puka, a me na pine bidirectional e huli ana. | |

| Hiki ke hoʻopuka | E komo i ka pākēnekatage o ka manawa hoʻopuka pin i hiki. No ka I/Os bidirectional nā pine hoʻokomo i ka wā e pio ai nā pine puka. |

|

| Hiki iā ODT | Pili wale ka ODT Enable: • No nā hoʻokomo DDRIO a me nā pine Bidirectional (inā pili lākou no FDDR a i ʻole MDDR) •No nā kūlana: LPDDR, SSTL18, a me SSTL15 •Inā hiki iā ODT |

|

No ka ʻike hou aku e pili ana i nā I/O o nā ʻohana mea i kākoʻo ʻia, e nānā iā RTG4 FPGA Fabric User Guide.

2.6.4 Nā poloka i kūkulu ʻia

Hoʻolālā i ka ʻike kikoʻī no nā poloka i kūkulu ʻia (SERDES a me FDDR) i hoʻokomo ʻia e helu i ka mana ikaika. Aia ma keia pauku keia mau pauku:

- SERDES, aoao 19

- FDDR, aoao 21

2.6.4.1 SERDES

Loaʻa nā mea RTG4 a hiki i 6 SERDES poloka (2 PCIESS a me 4 NPSS). Pili ia i ka mea i koho ʻia. Hōʻike kēlā me kēia lālani i ka pepa haʻawina SERDES i hoʻokahi ala (X1) a i ʻole nui (X2/X4) SERDES.

E hoʻokomo i kēia mau ʻāpana no kēlā me kēia poloka SERDES:

- inoa

- Wahi

- Kūkākūkā

- Ka helu o na Alanui

- Ka māmā holo (Gbps)

- PCIe F AXI/AHB (MHz)

- Laki ʻikepili (Mbps)

Hōʻike ka helu 13 i ka pepa hana SERDES.

Kiʻi 13 • SERDES Pepa Haʻawina

Hōʻike ka papa 11 i nā ʻāpana e hoʻokomo ʻia i ka pepa haʻawina SERDES.

Papa 11 • SERDES Pepa Ha'awina

| Nā ʻāpana | wehewehe |

| inoa | E hoʻokomo i kahi inoa no kēlā me kēia poloka SERDES. He koho ka inoa. Hiki ke hoʻonohonoho ʻia kēlā me kēia poloka SERDES e like me nā ala X1, X2, a i ʻole X4. Hiki ke hoʻonohonoho ʻia: •Eha X1 •ʻelua X2, a i ʻole •hookahi X4 Ma muli o ka hoʻonohonoho ʻana o nā alahele ma SERDES block, ʻokoʻa ka helu o nā lālani. |

| Wahi | E koho i ka wahi SERDES. Hiki i kēlā me kēia SERDES ke hoʻohana i nā alahele 4 a pili ia i ka mea i koho ʻia. Ke koho ʻia ʻo NPSS, loaʻa nā protocols ʻole PCIe (XAUI a me EPCS) i ke kolamu protocol. Ke koho ʻia ʻo PCIESS, loaʻa nā protocol āpau (PCIe, XAUI, a me EPCS). |

| Kūkākūkā | E koho i ka protocol. Kākoʻo ia i nā protocols PCIe, XAUI, a me EPCS. Hōʻike ka helu 14 i ka papa inoa wikiwiki i kākoʻo ʻia ke koho ʻia ka protocol EPCS. Hiki ke koho ʻia ka wikiwiki maʻamau a me ka laula o ka ʻikepili mai ka papa inoa hāʻule iho i ka Rate Rate (Mbps). Hoʻopili ʻia ka helu VCO a me ka FPGA Interface Frequencies ma muli o ka helu ʻikepili i koho ʻia. |

| Ka helu o na Alanui | E koho i ka helu o nā alahele. Kākoʻo ia iā X1, X2, a me X4. |

| Ka māmā holo (Gbps) | E koho i ka helu ʻikepili no ka protocol i koho ʻia. |

| PCIe F AXI/AHB (MHz) | E hoʻokomo i ke alapine o ka uaki o ke kikowaena AXI/AHB. Kākoʻo ia i ka alapine kiʻekiʻe a hiki i 200 MHz. |

| Laki ʻikepili (Mbps) | E koho i ka wikiwiki maʻamau a me ka laula ʻikepili. Hoʻohana ʻia kēia kahua inā koho ʻia ka protocol EPCS. |

| Hōʻike ʻana i ke alapine (MHz) | He waiwai paʻa kēia no nā protocols a pau koe ka wikiwiki maʻamau EPCS. I kēia hihia, e hoʻokomo i kekahi waiwai ma waena o 100 MHz a me 160 MHz. |

| Laki VCO (MHz) | Heluhelu-wale ka waiwai pa'a no nā ku'ina a pau koe wale nō ka wikiwiki ma'amau o EPCS. Hoʻopili ʻia nā waiwai i hōʻike ʻia ma muli o ka Reference Clock Frequency and Data Rate. |

Kiʻi 14 • ʻO ka wikiwiki EPCS maʻamau

No ka ʻike hou aku e pili ana i nā SERDES o nā ʻohana hāmeʻa i kākoʻo ʻia, e nānā iā RTG4 FPGA High Speed Serial Interfaces User Guide.

2.6.4.2 FDDR

Hōʻike ka Kiʻi 15 i ka ʻāpana FDDR Power ma ka pepa haʻawina FDDR. E komo i kēia mau ʻāpana no FDDR:

- inoa

- F AXI/AHB (MHz)

- ʻO ka hoʻonui ʻana i ka uaki DDR

Kiʻi 15 • Māhele Mana FDDR

Hōʻike ka papa 12 i nā ʻāpana e hoʻokomo ʻia ma ka ʻāpana FDDR Power o ka pepa haʻawina FDDR.

Papa 12 • FDDR Power Section Parameters

| Nā ʻāpana | wehewehe |

| inoa | E hoʻokomo i ka inoa o ka module i loaʻa iā FDDR. |

| F AXI/AHB (MHz) | E hoʻokomo i ke alapine o ka uaki o AXI/AHB interface. Kākoʻo ia i ka alapine kiʻekiʻe a hiki i 200 MHz. |

| ʻO ka hoʻonui ʻana i ka uaki DDR | E koho i ka helu hoʻonui pinepine o DDR. ʻO ka pinepine o ka uaki DDR (FDDR_CLK) ma lalo o 334 MHz (no ka exampe, inā he 167 ka F AXI/AHB, ʻaʻole pono e ʻoi aku ka nui o ka uaki DDR ma mua o F AXI/AHB*2). |

No ka 'ike hou aku e pili ana i FDDR, e nānā iā RTG4 FPGA High Speed DDR Interfaces User Guide.

2.7 KaʻAnuʻu – 3: Nā hiʻohiʻona

Ma kēia ʻāpana, e hoʻokomo i nā ʻano hana hoʻohana i kona manawa hana, no ka laʻana, 50% o ka manawa Active a me 50% i Standby. E komo i ka pākēnekatagʻO ka manawa e manaʻo ʻia ai ka hāmeʻa ma ke ʻano Active a Standby. Aia kēia ʻāpana ma ka pepa haʻawina Summary. He koho ke hāʻawi i kēia mau kikoʻī.

Hōʻike ka Figure 16 i ka ʻāpana Modes and Scenarios ma ka pepa haʻawina Summary.

Kiʻi 16 • Māhele ʻano a me nā hiʻohiʻona

2.8 KaʻAnuʻu – 4: Hōʻuluʻulu Mana Mana

Hāʻawi ka ʻāpana Power Summary i ka nui o ka mana a me ka haki ʻana o ka mana ma muli o nā kumu mana a me nā alahao. Hāʻawi pū ia i ka hōʻuluʻulu manaʻo Thermal Margin (Maximum Ta and Maximum Power).

Hōʻike ka Figure 17 i nā ʻāpana o kēia manawa, Hōʻuluʻulu Mana, a me nā ʻano a me nā Scenarios ma ka pepa haʻawina Summary.

Kiʻi 17 • Hōʻuluʻulu Pepa Haʻawina

Nānā: Hōʻike ka papa 13 i ka vol rail i ʻae ʻiatage laulā.

Papa 13 • 'Apono 'ia Rail Voltage Laulā

| Inoa Kaaahi | Voltage laulā (V) | |

| Min | Max | |

| VDD | 1.14 | 1.26 |

| VDDI 1.2 | 1.14 | 1.26 |

| VDDI 1.5 | 1.425 | 1.575 |

| VDDI 1.8 | 1.71 | 1.89 |

| VDDI 2.5 | 2.375 | 2.625 |

| VDDI 3.3 | 3.15 | 3.45 |

| SERDES J011_L[0123LVDDA10 | 1.14 | 1.26 |

| SERDES JOILL[0123]_VDDAPLL | 2.375 | 2.625 |

| PLL_VDDA (3.3 V)1 | 3.135 | 3.465 |

| SERDES VDDI | 1.14 | 3.45 |

| VPP | 3.135 | 3.465 |

1. Aia ka PLL Analog Supply SERDES_x_PLL_VDDA (x: 0 a 6), FDDR_x_PLL_VDDA (x: 0 a 2) a me CCC_x_PLL_VDDA (x = NE0, NE1, NW0, NW1, SW0, SW1, SE0, SE1).

ʻO ka SERDES_REFCLK (Bank Type) a me nā koho maʻamau IO ma ka ʻaoʻao IO e pili ana i ka SERDES_VDDI rail Voltage ma ka ʻaoʻao Hōʻuluʻulu.

Nānā: Hiki iā ʻoe ke hoʻololi i ka SERDES_VDDI rail voltage mai ka papa Rail Breakdown ma ka ʻaoʻao Summary. ʻO kēia nā lālā kūpono:

- [1.14, 1.26] no ka 1.2 V

- [1.425, 1.575] no ka 1.5 V

- [1.710, 1890] no ka 1.8 V

- [2.375, 2.625] no ka 2.5 V

- [3.15, 3.45] no 3.3. V

Kiʻi 18 • Hōʻuluʻulu Tab

Nānā: E kikokiko i kekahi o ka SERDES_VDDI rail voltage like me ka mea i hōʻike ʻia ma ka ʻaoʻao o ka hāmeʻa ma ke kelepona (Voltage kolamu).

Kii 19 • IO Tab

Nānā: Mai ka SERDES_VDDI rail voltagUa koho ʻia ʻo e 1.5v (Figure 18), hiki ke koho ʻia nā kūlana I/O no SERDES_REFCLK mai ka hāʻule iho e pili ana i ka vol railtage.

Hōʻike ka Figure 20 i ka ʻāpana Hoʻohana Mea Hana i hōʻike ʻia ma lalo o ka pepa haʻawina Summary.

Kiʻi 20 • Māhele Hoʻohana Mea Hana

Hōʻike ka Figure 21 i ka ʻāpana Hapa ma ka pepa haʻawina Summary.

Kii 21 • Pauku Hapa

Microsemi Headquarters

Microsemi Headquarters

Hoʻokahi ʻoihana, Aliso Viejo,

CA 92656 USA

I loko o ʻAmelika: +1 800-713-4113

Ma waho o ʻAmelika: +1 949-380-6100

Kūʻai: +1 949-380-6136

Fax: +1 949-215-4996

leka uila: sales.support@microsemi.com

www.microsemi.com

©2020 Microsemi, he lālā nona piha o Microchip Technology Inc. Ua mālama ʻia nā kuleana āpau. ʻO Microsemi a me ka Microsemi logo nā inoa inoa inoa o

Hui Microsemi. ʻO nā hōʻailona ʻē aʻe a pau a me nā hōʻailona lawelawe ʻo ia ka waiwai o ko lākou mau mea nona.

ʻO Microsemi Proprietary and Confidential UG0596 Mea hoʻohana Hoʻoponopono Hoʻoponopono 2.0

Palapala / Punawai

|

ʻO Microsemi UG0596 RTG4 FPGA Mea Mana Mana Mana [pdf] Ke alakaʻi hoʻohana UG0596, UG0596 RTG4 FPGA Mea Mana Mana Mana, RTG4 FPGA Mana Mana Mana Mana, FPGA Mana Mana Mana, Mana Mana Mana, Mana Mana Mana |