AN5827

Nota de aplicación

Directrices para entrar en estado RMA en MPU da serie STM32MP1

Introdución

Os microprocesadores da serie STM32MP1 inclúen dispositivos STM32MP15xx e STM32MP13xx. Esta nota da aplicación ofrece información para apoiar o proceso de entrada do estado de análise do material de devolución, denominado RMA neste documento.

Información xeral

Este documento aplícase aos microprocesadores da serie STM32MP1 baseados en núcleos Arm® Cortex®

Nota: Arm é unha marca rexistrada de Arm Limited (ou das súas filiais) nos EUA e/ou noutros lugares.

Documentos de referencia

| Referencia | Título do documento |

| STM32MP13xx | |

| AN5474 | Comezando co desenvolvemento de hardware de liñas STM32MP13x |

| DS13878 | Arm® Cortex®-A7 ata 1 GI-ft, 1xETH, 1 xADC, 24 temporizadores, audio |

| DS13877 | Arm® Cortex®-A7 ata 1 GHz, 1xETH, 1 xADC, 24 temporizadores, audio, criptografía e adv. seguridade |

| DS13876 | Arm® Cortex®-A7 ata 1 GI-ft, 2xETH, 2xCAN FD, 2xADC. 24 temporizadores, audio |

| DS13875 | Arm® Cortex®-A7 ata 1 GHz, 2xETH, 2xCAN FD, 2xADC, 24 temporizadores, audio, criptografía e adv. seguridade |

| DS13874 | Arm® Cortex®-A7 ata 1 GHz, LCD-TFT, interfaz de cámara, 2xETH, 2xCAN FD, 2xADC, 24 temporizadores, audio |

| DS13483 | Arm® Cortex®-A7 ata 1 GHz, LCD-TFT, interface de cámara, 2xETH, 2xCAN FD, 2xADC, 24 temporizadores, audio, criptografía e adv. seguridade |

| RM 0475 | STM32MP13xx MPU avanzadas de 0 bits baseadas en Arm32 |

| STM32MP15xx | |

| AN5031 | Comezando co desenvolvemento de hardware das liñas STM32MP151, STM32MP153 e STM32MP157 |

| DS12500 | Arm® Cortex®-A7 800 MHz + Cortex®-M4 MPU, TFT, 35 com. interfaces, 25 temporizadores, adv. analóxico |

| DS12501 | Arm® Cortex®-A7 800 MHz + Cortex®-M4 MPU, TFT, 35 com. interfaces, 25 temporizadores, adv. analóxico, cripto |

| DS12502 | Arm® dual Cortex®-A7 800 MHz + Cortex®-M4 MPU, TFT, 37 com. interfaces, 29 temporizadores, adv. analóxico |

| DS12503 | Arm® dual Cortex®-A7 800 MHz + Cortex®-M4 MPU, TFT, 37 com. interfaces, 29 temporizadores, adv. analóxico, cripto |

| DS12504 | Arm® dual Cortex®-A7 800 MHz + Cortex®-M4 MPU, GPU 3D, TFT/DSI, 37 com. interfaces, 29 temporizadores, adv. analóxico |

| DS12505 | Arm® dual Cortex®-A7 800 MHz + Cortex®-M4 MPU, GPU 3D, TFT/DSI, 37 com. interfaces, 29 temporizadores, adv. analóxico, cripto |

| RM 0441 | MPU avanzadas de 32 bits baseadas en Arm® STM151MP32 |

| RM 0442 | STM32MP153 MPU avanzadas de 32 bits baseadas en Arnie |

| RM 0436 | STM32MP157 MPU avanzadas de 0 bits baseadas en Arm32 |

Termos e acrónimos

Táboa 2. Definición de acrónimos

| Prazo | Definición |

| LONXE | Solicitude de análise de fallos: fluxo utilizado para devolver o dispositivo sospeitoso para a súa análise a STMicroelectronics. Para mellorar o pleno probabilidade do dispositivo durante esa análise, o dispositivo debe estar en estado RMA. |

| JTAG | Grupo de acción de proba conxunto (interface de depuración) |

| PMIC | Circuíto externo de xestión de enerxía que proporciona varias fontes de alimentación da plataforma, cunha gran capacidade de control sinais e interface serie. |

| RMA | Análise do material de retorno: estado específico do dispositivo no ciclo de vida que permite a activación do modo de proba completa segundo o necesite STMicroelectronics para a análise de fallos. |

1. Neste documento, o acrónimo RMA non se refire en ningún lugar a "aceptación de material de devolución", que é o fluxo utilizado para devolver pezas non usadas (stock do cliente por exemploample).

Estado RMA dentro do fluxo FAR

O fluxo FAR consiste en devolver un dispositivo a STMicroelectronics para unha análise máis profunda dos fallos en caso de sospeita dun problema de calidade. A peza debe devolverse comprobable a ST para que se poida realizar a análise.

- A peza debe estar en estado RMA

- A peza debe ser fisicamente compatible co dispositivo orixinal (tamaño da pelota, campo, etc.)

Ciclo de vida do produto STM32MP13xx

Nos dispositivos STM32MP13xx, antes de devolver o dispositivo, o cliente debe entrar no estado RMA cun contrasinal de 32 bits predefinido do cliente introducido a través do JTAG (ver Sección 3). Unha vez introducido no estado RMA, o dispositivo xa non se pode utilizar para a produción (consulte a Figura 1) e actívase o modo de proba completa para que STMicroelectronics continúe a investigación mentres se manteñen inaccesibles todos os segredos do cliente (OTP superior como se describe no manual de referencia) polo hardware.

A seguinte figura mostra o ciclo de vida do produto dos dispositivos STM32MP13xx. Mostra que unha vez que se ingresa o estado RMA o dispositivo non pode volver a outros modos.

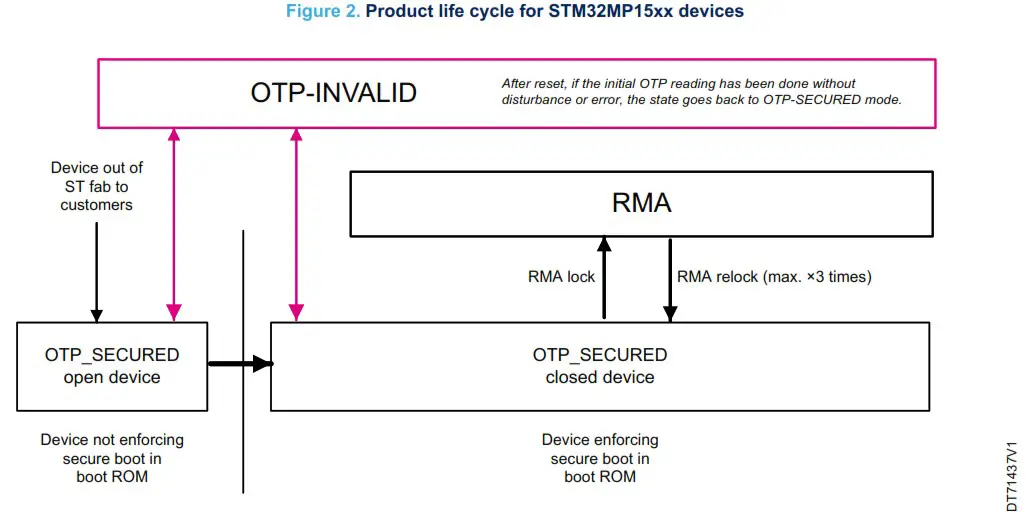

Ciclo de vida do produto STM32MP15xx

Nos dispositivos STM32MP15xx, antes de devolver o dispositivo, o cliente debe entrar no estado RMA cun contrasinal de 15 bits predefinido do cliente introducido a través do JTAG (ver Sección 3). Unha vez introducido no estado RMA, o dispositivo pode volver ao estado SECURE_CLOSED introducindo un contrasinal "RMA_RELOCK" predefinido polo cliente. Só se permiten 3 probas de estado de transición RMA a RMA_RELOCKED (consulta a Figura 2). No estado RMA, o modo de proba completa está activado para que STMicroelectronics continúe a investigación mentres todos os segredos do cliente (OTP superior como se describe no manual de referencia) están inaccesibles polo hardware.

A seguinte figura mostra o ciclo de vida do produto dos dispositivos STM32MP15x.

Restricións do consello estatal de RMA

Para activar o estado RMA, son necesarias as seguintes restricións.

O JTAG o acceso debe estar dispoñible

Os sinais NJTRST e JTDI, JTCK, JTMS, JTDO (pin PH4, PH5, PF14, PF15 en dispositivos STM32MP13xx) deben ser accesibles. Nalgunhas ferramentas, o JTDO non é necesario (por exemploample, Trace32) noutros, como OpenOCD, a ferramenta comproba o dispositivo JTAG ID mediante JTDO antes de executar JTAG secuencia.

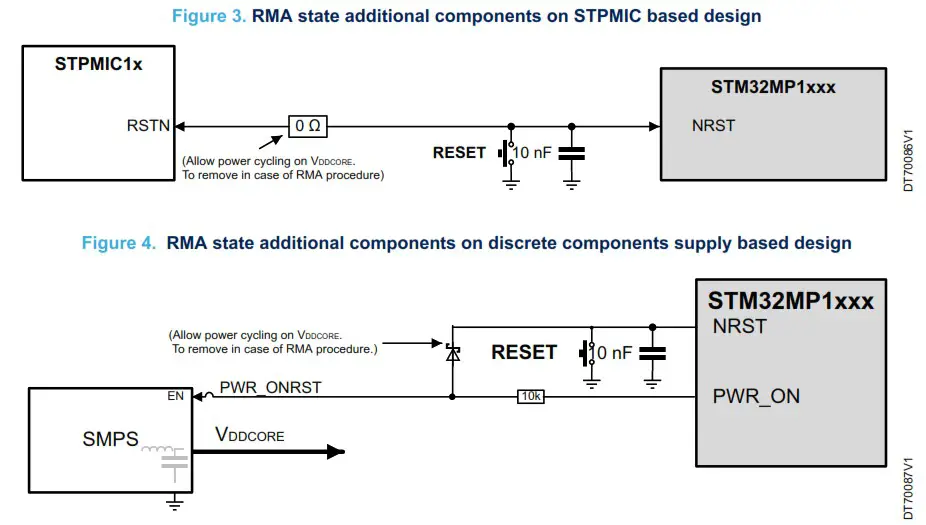

As fontes de alimentación VDDCORE e VDD non se deben apagar cando se activa o pin NRST

No deseño de referencia ST, o NRST activa un ciclo de encendido do STPMIC1x ou dos reguladores de potencia de compoñentes discretos externos. Unha posible implementación móstrase no deseño de referencia examplieiro proporcionado na nota da aplicación Iniciación ao desenvolvemento de hardware de liñas STM32MP13x (AN5474). A Figura 3 e a Figura 4 son versións simplificadas que só mostran os compoñentes relacionados co estado RMA. O mesmo aplícase aos dispositivos STM32MP15xx.

Un taboleiro sinxelo con só o JTAG o pin e o zócalo axeitado só se poden usar para propósitos de contrasinal RMA (no caso de que non sexa posible acceder a JTAG no taboleiro de produción). Neste caso, o cliente debe primeiro dessoldar o dispositivo da placa de produción e repoboar as bolas do paquete.

A placa debe ter os pinos STM32MP1xxx indicados na Táboa 3 conectados como se indica. Outros pinos pódense deixar flotando.

Táboa 3. Conexión de pin para placa simple utilizada para introducir o contrasinal RMA

| Nome do pin (sinal) | Conectado a | Comenta | |

| STM32MP13xx | STM32MP15xx | ||

| JTAG e reiniciar | |||

| NJTRST | NJRST | JTAG conector | |

| PH4 (JTDI) | JTDI | ||

| PH5 (JTDO) | JTDO | Non é necesario nalgunha ferramenta de depuración como Trace32 | |

| PF14 (JTCK) | JTCK | ||

| PF15 (JTMS) | JTMS | ||

| NRST | NRST | Botón de reinicio | Con capacitor de 10 nF a VSS |

| Fontes de alimentación | |||

| VDDCORE. VDDCPU | VDDCORE | Subministración externa | Consulte a folla de datos do produto para o típico valor |

| VDD. VDDSD1. VDDSD2. VDD_PLL. VDD_PLL2. VBAT. VDD_ANA. PDR_ON |

VDD. VDD_PLL. VDD_PLL2. VBAT. VDD_ANA. PDR_ON. PDR_ON_CORE |

3.3 V externo subministración |

Debería estar dispoñible primeiro e eliminado último (pode estar xunto con outros suministros) |

| VDDA, VREF+, VDD3V3_USBHS. VDDO_DDR |

VDDA. VREF+. VDD3V3_USBHS. VDDO_DDR. VDD_DSI. VDD1V2_DSI_REG. VDD3V3_USBFS |

0 | ADC. VREFBUF, USB, DDR non utilizados |

| VSS. VSS_PLL. VSS_PLL2. VSSA. VSS_ANA. VREF-. VSS_US131-IS |

VSS. VSS_PLL, VSS_PLL2. VSSA. VSS_ANA. VREF-. VSS_USBHS. VSS_DSI |

0 | |

| VDDA1V8_REG. VDDA1V1_REG |

VDDA1V8_REG. VDDA1V1_REG |

flotando | |

| Outros | |||

| BYPASS_REG1V8 | BYPASS_REG1V8 | 0 | Regulador 1V8 activado por defecto (REG 18E = 1) |

| PC15- OSC32_OUT | PC15- OSC32_OUT | flotando | |

| PC14- OSC32_IN | PC14- OSC32_IN | Osciladores externos non utilizados (ROM de arranque utilizar oscilador interno HSI) |

|

| PHO-OSC_IN | PHO-OSC_IN | ||

| PH1-0SC_OUT | PH1-0SC_OUT | ||

| USB_RREF | USB_RREF | flotando | USB non usado |

| P16 (BOOT2) | BOTE 2 | X | Entrar no estado RMA funciona calquera que sexa o valor de arranque (2:0). |

| PI5 (BOOT1) | 60011 | X | |

| PI4 (BOOTO) | BOOTO | X | |

| NRST_CORE | 10 nF para VSS | Extracción interna en NRST_CORE | |

| PA13 (BOOTFAILN) | PA13 (BOOTFAILN) | LED | Opcional |

Requisitos previos para permitir a entrada no futuro estado RMA

A posibilidade de entrar no estado RMA debe ser configurada polo cliente introducindo un contrasinal durante a produción do cliente despois do aprovisionamento secreto

- O dispositivo cando se envía desde STMicroelectronics está en estado aberto OTP_SECURED.

- O dispositivo contén segredos ST que están protexidos pola ROM de arranque e ningún segredo do cliente.

- Ao restablecer ou despois da execución da ROM de arranque, o acceso DAP pódese reabrir mediante Linux ou mediante o modo de "inicio de desenvolvemento" da ROM de arranque (OTP_SECURED aberto + pins de arranque BOOT[2:0]=1b100 + restablecemento).

- Mentres está aberto OTP_SECURED, o cliente debe proporcionar os seus segredos en OTP:

- directamente polo cliente por conta propia ou risco

- de forma segura a través da canle cifrada usando a "función SSP" da ROM de inicio xunto coas ferramentas STM32.

- Ao final do aprovisionamento de segredos, o cliente pode fusionar:

- En STM32MP13xx un contrasinal RMA de 32 bits en OTP_CFG56 (o contrasinal debe ser 0).

- No STM32MP15xx un contrasinal RMA de 15 bits en OTP_CFG56[14:0], un contrasinal RMA_RELOCK en OTP_CFG56[29:15].

O contrasinal debe ser diferente de 0.

- Establece o OTP_CFG56 como "bloqueo de programación permanente" para evitar a programación posterior en 0xFFFFFF e permitir entrar no estado RMA sen coñecer o contrasinal inicial.

- Verifique a programación correcta do OTP_CFG56 comprobando o rexistro BSEC_OTP_STATUS.

- Finalmente, o dispositivo cámbiase a OTP_SECURED pechado:

- En STM32MP13xx fusionando OTP_CFG0[3] = 1 e OTP_CFG0[5] = 1.

- En STM32MP15xx fusionando OTP_CFG0[6] = 1.

O dispositivo pódese reabrir no estado RMA para a investigación por parte de STMicroelectronics

- Cando o dispositivo está en estado pechado OTP_SECURED, xa non é posible o "inicio de desenvolvemento".

RMA introducindo detalles

Como se mencionou anteriormente, o estado RMA utilízase para reabrir de forma segura o modo de proba completo sen exposición dos segredos proporcionados polo cliente. Isto faise grazas ao funcional JTAG entradas mentres que o hardware mantén inaccesibles todos os segredos do cliente.

No caso de que exista un requisito de análise sobre un sample hai a necesidade de ir ao estado RMA (ver Figura 5. Cambiando a OTP_SECURED pechado ), que protexe os segredos dos clientes e reabre a depuración segura e non segura en DAP.

- O cliente cambia en BSEC_JTAGIN rexistre o contrasinal RMA usando JTAG (só se aceptan valores diferentes de 0).

- O cliente restablece o dispositivo (pin NRST).

Nota: Durante este paso, o contrasinal en BSEC_JTAGO rexistro IN non debe borrarse. Así, o NRST non debe apagar o VDD nin as fontes de alimentación VDDCORE. Tampouco debería estar conectado ao pin NJTRST. No caso de que se use STPMIC1x, pode ser obrigatorio enmascarar as fontes de alimentación durante o reinicio. Isto faise programando o rexistro de opcións de máscara STPMIC1x (BUCKS_MRST_CR) ou eliminando a resistencia engadida para RMA na placa entre STPMICx RSTn e STM32MP1xxx NRST (consulte a Figura 3). - Invócase a ROM de inicio e comproba o contrasinal RMA introducido en BSEC_JTAGIN con OTP_CFG56.RMA_PASSWORD:

• Se os contrasinais coinciden, o sample convértese nun RMA_LOCK sample (para sempre en STM32MP13xx).

• Se os contrasinais non coinciden, o sampli permanece no estado pechado OTP_SECURED e un contador de "probas de reapertura" de RMA increméntase en OTP.

Nota: Só se autorizan tres probas de reapertura de RMA. Despois de tres ensaios fallidos, a reapertura de RMA xa non é posible. O dispositivo permanece no seu estado de ciclo de vida real. - O cliente restablece unha segunda vez o sample a través do pin NRST:

• o LED do PA13 está acendido (se está conectado)

• reabre o acceso de depuración DAP. - O dispositivo pódese enviar a STMicroelectronics.

- Despois do reinicio (pin NRST ou calquera reinicio do sistema), invócase a ROM de inicio:

• Detecta que OTP8.RMA_LOCK = 1 (RMA bloqueado sample).

• Protexe todos os segredos dos clientes e de STMicroelectronics.

• Reabre o acceso de depuración DAP de forma segura e non segura.

Mentres está en estado RMA, a parte ignora os pinos de arranque e non é capaz de iniciar desde un flash externo nin USB/UART.

Detalles de desbloqueo de RMA

No STM32MP15xx é posible desbloquear o dispositivo de RMA e volver ao estado SECURE_CLOSED.

En BSEC_JTAGNO rexistro, o cliente cambia o contrasinal de desbloqueo de RMA usando JTAG (só se aceptan valores diferentes de 0)

- O cliente restablece o dispositivo (pin NRST).

Nota: Só se autorizan tres probas de desbloqueo de RMA. Despois de tres probas fallidas, o desbloqueo de RMA xa non é posible. O dispositivo permanece no seu estado de ciclo de vida RMA. - O cliente restablece unha segunda vez o sample a través do pin NRST:

• o LED do PA13 está acendido (se está conectado),

• o dispositivo está en estado SECURE_CLOSED (o acceso á depuración de DAP está pechado).

Estado RMA ingresando JTAG guión examples

script STM32MP13xx exampOs ficheiros para introducir o contrasinal e introducir o estado RMA están dispoñibles nun zip separado file. Pódense usar con Trace32, OpenOCD usando sonda STLINK, OpenOCD usando sonda compatible con CMSIS-DAP (por exemploample ULink2). A información pódese atopar en www.st.com. Consulte "Recursos CAD" do produto STM32MP13xx na sección "Especificación de fabricación de placas".

Semellante exampOs ficheiros pódense derivar para dispositivos STM32MP15xx. Un example para entrar no estado RMA e saír do estado RMA para Trace32 está dispoñible nun zip separado file. A información pódese atopar en www.st.com. Consulte "Recursos CAD" do produto STM32MP15x na sección "Especificación de fabricación de placas".

Historial de revisións

Táboa 4. Historial de revisións de documentos

| Data | Versión | Cambios |

| 13-Feb-23 | 1 | Lanzamento inicial. |

AVISO IMPORTANTE LER ATENTAMENTE

STMicroelectronics NV e as súas subsidiarias (“ST”) resérvanse o dereito de realizar cambios, correccións, melloras, modificacións e melloras nos produtos ST e/ou neste documento en calquera momento sen previo aviso. Os compradores deben obter a información relevante máis recente sobre produtos ST antes de facer pedidos. Os produtos ST véndense de acordo cos termos e condicións de venda de ST existentes no momento do recoñecemento da orde.

Os compradores son os únicos responsables da elección, selección e uso dos produtos ST e ST non asume ningunha responsabilidade pola asistencia á aplicación ou o deseño dos produtos dos compradores.

ST non concede ningunha licenza, expresa ou implícita, a ningún dereito de propiedade intelectual.

A revenda de produtos ST con disposicións diferentes da información aquí establecida anulará calquera garantía concedida por ST para tal produto.

ST e o logotipo de ST son marcas comerciais de ST. Para obter información adicional sobre as marcas rexistradas ST, consulte www.st.com/trademarks. Todos os outros nomes de produtos ou servizos son propiedade dos seus respectivos propietarios.

A información deste documento substitúe e substitúe a información proporcionada anteriormente en calquera versión anterior deste documento.

© 2023 STMicroelectronics Todos os dereitos reservados

AN5827 - Rev 1

AN5827 - Rev 1 - febreiro de 2023

Para obter máis información, póñase en contacto coa oficina local de vendas de STMicroelectronics.

www.st.com

Documentos/Recursos

|

Microprocesadores da serie STMicroelectronics STM32MP1 [pdfGuía do usuario Microprocesadores da serie STM32MP1, serie STM32MP1, microprocesadores |