Raspberry Pi SC1631 Raspberry Microcontroller

Manylebau Cynnyrch

- Model: RP2350

- Pecyn: QFN-60

- Storio Flash Mewnol: Na

- Cyftage Rheoleiddiwr: Rheoleiddiwr newid sglodion

- Pinnau Rheoleiddiwr: 5 (mewnbwn 3.3V, allbwn 1.1V, VREG_AVDD, VREG_LX, VREG_PGND)

Cyfarwyddiadau Defnydd Cynnyrch

- Pennod 1: Cyflwyniad

- Mae'r gyfres RP2350 yn cynnig opsiynau pecyn gwahanol o'i gymharu â'r gyfres RP2040. Daw'r RP2350A a RP2354A mewn pecyn QFN-60 heb a gyda storfa fflach fewnol yn y drefn honno, tra bod y RP2354B a RP2350B yn dod mewn pecyn QFN-80 gyda a heb storfa fflach.

- Pennod 2: Grym

Mae'r gyfres RP2350 yn cynnwys cyfrol newid ar-sglodion newyddtage rheolydd gyda phum pin. Mae'r rheolydd hwn angen cydrannau allanol ar gyfer gweithredu ond mae'n cynnig effeithlonrwydd pŵer uwch ar gerrynt llwyth uwch o'i gymharu â'r rheolydd llinellol yn y gyfres RP2040. Rhowch sylw i sensitifrwydd sŵn yn y pin VREG_AVDD sy'n cyflenwi'r cylchedwaith analog.

Cwestiynau Cyffredin (FAQ)

- C: Beth yw'r prif wahaniaeth rhwng RP2350A a RP2350B?

A: Mae'r prif wahaniaeth ym mhresenoldeb storio fflach fewnol. Nid oes gan RP2350A storfa fflach fewnol tra bod gan RP2350B. - C: Sawl pin mae'r cyftage rheolydd yn y gyfres RP2350 wedi?

A: Mae'r cyftagMae gan y rheolydd yn y gyfres RP2350 bum pin.

Dyluniad caledwedd gyda RP2350 Defnyddio microreolyddion RP2350 i adeiladu byrddau a chynhyrchion

Colophon

- © 2023-2024 Raspberry Pi Cyf

- Mae'r ddogfennaeth hon wedi'i thrwyddedu o dan Creative Commons Attribution-NoDerivatives 4.0 International (CC BY-ND). dyddiad adeiladu: 2024-08-08 adeiladu-fersiwn: c0acc5b-glân

- Hysbysiad ymwadiad cyfreithiol

- DDARPERIR DATA TECHNEGOL A DIBYNADWYEDD AR GYFER CYNHYRCHION RASPBERRY PI (GAN GYNNWYS TAFLENNI DATA) FEL Y'U ADDASWYD O AMSER I AMSER ("ADNODDAU") GAN RASPBERRY PI LTD (“RPL”) “FEL Y MAE” AC UNRHYW WARANTAU MYNEGOL NEU WEDI EU HYNNY, GAN GYNNWYS, NID OND AT, GWAHODDIR GWARANTIAETHAU GOBLYGEDIG O FYDDHADEDD A FFITRWYDD AT DDIBEN NODEDIG. I'R MATERION UCHAF A GANIATEIR GAN GYFRAITH BERTHNASOL MEWN DIGWYDDIAD NAD OEDD RPL YN ATEBOL AM UNRHYW DDIFROD UNIONGYRCHOL, ANUNIONGYRCHOL, ARBENNIG, ENGHREIFFTIOL NEU GANLYNIADOL (GAN GYNNWYS, OND NID YN GYFYNGEDIG I, SICRHAU DEFNYDD O DDWYFOLIADAU, WEDI'U COLLI); , NEU ELW; NEU YMYRIAD I FUSNES) FODD WEDI ACHOSI AC AR UNRHYW Damcaniaeth O ATEBOLRWYDD, P'un ai WRTH GYTUNDEB, ATEBOLRWYDD DYNOL, NEU GAFF (GAN GYNNWYS Esgeulustod NEU FEL ARALL) SY'N CODI MEWN UNRHYW FFORDD ALLAN O'R DEFNYDD O ' R ADNODDAU, HYD YN OED. O'R FATH DDIFROD.

- Mae RPL yn cadw'r hawl i wneud unrhyw welliannau, gwelliannau, cywiriadau neu unrhyw addasiadau eraill i'r ADNODDAU neu unrhyw gynhyrchion a ddisgrifir ynddynt ar unrhyw adeg a heb rybudd pellach.

Mae'r ADNODDAU wedi'u bwriadu ar gyfer defnyddwyr medrus sydd â lefelau addas o wybodaeth ddylunio. Defnyddwyr yn unig sy'n gyfrifol am eu dewis a'u defnydd o'r ADNODDAU ac unrhyw gymhwysiad o'r cynhyrchion a ddisgrifir ynddynt. Defnyddiwr yn cytuno i indemnio a dal RPL yn ddiniwed yn erbyn yr holl rwymedigaethau, costau, iawndal neu golledion eraill sy'n deillio o'u defnydd o'r ADNODDAU. - Mae RPL yn rhoi caniatâd i ddefnyddwyr ddefnyddio'r ADNODDAU ar y cyd â'r cynhyrchion Raspberry Pi yn unig. Gwaherddir pob defnydd arall o'r ADNODDAU. Ni roddir trwydded i unrhyw RPL arall nac unrhyw hawl eiddo deallusol trydydd parti arall.

- GWEITHGAREDDAU RISG UCHEL. Nid yw cynhyrchion Raspberry Pi wedi'u dylunio, eu gweithgynhyrchu na'u bwriadu i'w defnyddio mewn amgylcheddau peryglus sy'n gofyn am berfformiad methu diogel, megis wrth weithredu cyfleusterau niwclear, systemau llywio neu gyfathrebu awyrennau, rheoli traffig awyr, systemau arfau neu gymwysiadau sy'n hanfodol i ddiogelwch (gan gynnwys cynnal bywyd systemau a dyfeisiau meddygol eraill), lle gallai methiant y cynhyrchion arwain yn uniongyrchol at farwolaeth, anaf personol neu ddifrod corfforol neu amgylcheddol difrifol (“Gweithgareddau Risg Uchel”). Mae RPL yn gwadu'n benodol unrhyw warant benodol neu oblygedig o addasrwydd ar gyfer Gweithgareddau Risg Uchel ac nid yw'n derbyn unrhyw atebolrwydd am ddefnyddio neu gynnwys cynhyrchion Raspberry Pi mewn Gweithgareddau Risg Uchel.

- Darperir cynhyrchion Raspberry Pi yn amodol ar Delerau Safonol RPL. Nid yw darpariaeth RPL o'r ADNODDAU yn ehangu nac yn addasu fel arall Delerau Safonol RPL gan gynnwys ond heb fod yn gyfyngedig i'r ymwadiadau a'r gwarantau a fynegir ynddynt.

Pennod 1. Rhagymadrodd

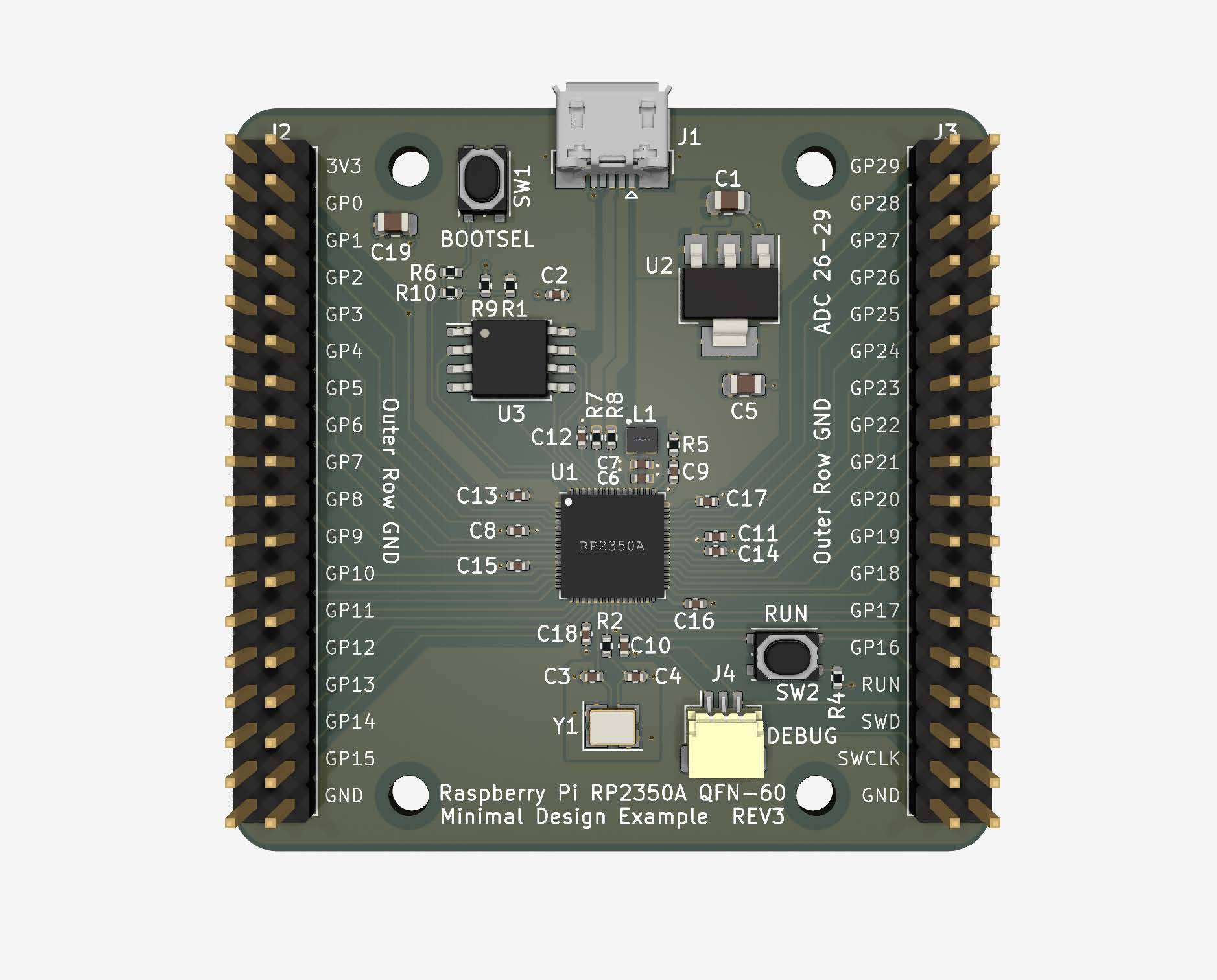

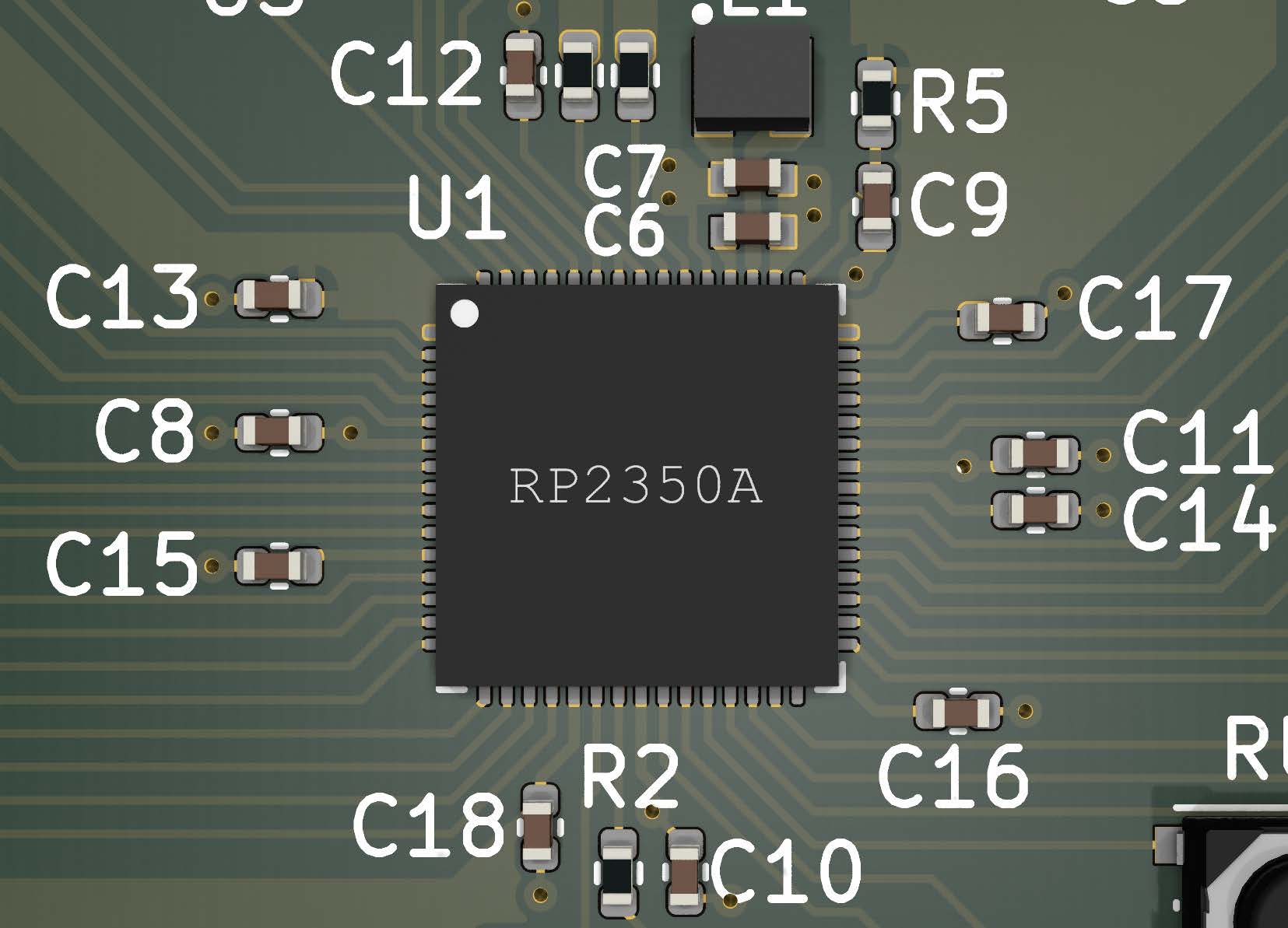

Ffigur 1. Rendro KiCad 3D o'r dyluniad Lleiaf RP2350A example

Pan wnaethom gyflwyno'r Raspberry Pi RP2040 gyntaf, fe wnaethom hefyd ryddhau dyluniad 'Lleiaf' cynample a'r canllaw cysylltiedig Dyluniad caledwedd gyda RP2040 a oedd, gobeithio, yn esbonio sut y gellid defnyddio'r RP2040 mewn bwrdd cylched syml, a pham y gwnaed y dewisiadau cydran amrywiol. Gyda dyfodiad y gyfres RP235x, mae'n bryd ailedrych ar y dyluniad RP2040 Minimal gwreiddiol, a'i ddiweddaru i gyfrif am y nodweddion newydd, a hefyd ar gyfer pob un o'r amrywiadau pecyn; yr RP2350A gyda'i becyn QFN-60, a'r RP2350B sy'n QFN-80. Unwaith eto, mae'r dyluniadau hyn ar fformat Kicad (7.0), ac ar gael i'w lawrlwytho (https://datasheets.raspberrypi.com/rp2350/Minimal-KiCAD.zip).

Y Bwrdd Lleiaf

Roedd y bwrdd Lleiaf gwreiddiol yn ymgais i ddarparu dyluniad cyfeirio syml, gan ddefnyddio'r lleiafswm o gydrannau allanol sydd eu hangen i redeg yr RP2040 a dal i gael yr holl IO yn agored ac yn hygyrch. Roedd hyn yn ei hanfod yn cynnwys ffynhonnell pŵer (rheoleiddiwr llinellol 5V i 3.3V), osgiliadur grisial, cof fflach, a chysylltiadau IO (soced micro USB a phenawdau GPIO). Mae'r byrddau Minimal cyfres RP235x newydd i raddau helaeth yr un fath, ond gyda rhai newidiadau yn angenrheidiol oherwydd y caledwedd newydd. Yn ogystal â hyn, ac er gwaethaf mynd yn groes i natur fach iawn y dyluniad, rwyf wedi ychwanegu cwpl o fotymau ar gyfer bŵt a rhedeg, ynghyd â phennawd SWD ar wahân, a ddylai olygu profiad dadfygio cwbl llai rhwystredig y tro hwn. A siarad yn fanwl gywir, nid oes angen y botymau hyn ar ddyluniadau, mae'r signalau ar gael o hyd ar y penawdau, a gellir eu hepgor os ydych yn arbennig o ymwybodol o gost neu ofod, neu os oes gennych dueddiadau masochistaidd.

Cyfres RP2040 vs RP235x

Mae'r newid mwyaf amlwg yn y pecynnau. Tra bod yr RP2040 yn QFN-7 7x56mm, mae gan y gyfres RP235x bedwar aelod gwahanol ar hyn o bryd. Mae dwy ddyfais sy'n rhannu'r un pecyn QFN-60; yr RP2350A nad yw'n cynnwys storfa fflach fewnol, a'r RP2354A sy'n gwneud hynny. Yn yr un modd, mae'r QFN-80 hefyd yn dod mewn dau flas; y RP2354B gyda fflach, a RP2350B heb. Mae'r dyfeisiau QFN-60 a'r RP2040 gwreiddiol yn rhannu heri gyffredintage.

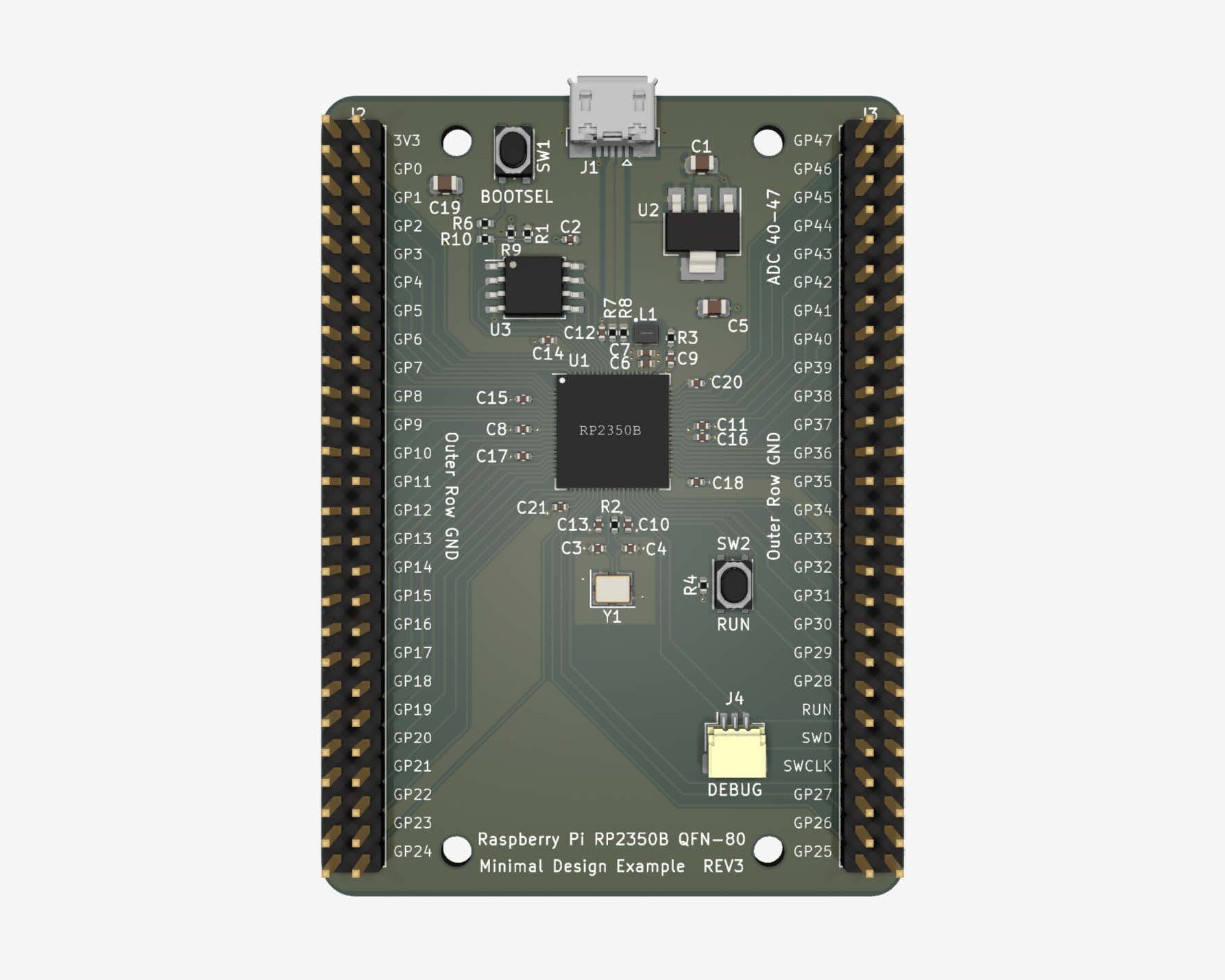

Mae gan bob un ohonynt 30 GPIO, y mae pedwar ohonynt hefyd wedi'u cysylltu â'r ADC, ac maent yn 7x7mm o faint. Er gwaethaf hyn, nid yw'r RP2350A yn disodli'r RP2040 galw heibio, gan fod nifer y pinnau ar bob un yn wahanol. Mewn cyferbyniad, mae gan y sglodion QFN-80 bellach 48 GPIO, ac mae wyth o'r rhain bellach yn gallu ADC. Oherwydd hyn, mae gennym bellach ddau fwrdd Lleiaf; un ar gyfer y dyfeisiau 60 pin, ac un ar gyfer yr 80. Mae'r byrddau Minimal hyn wedi'u cynllunio'n bennaf ar gyfer y rhannau heb fflach fewnol (RP2350), fodd bynnag, mae'n hawdd defnyddio'r dyluniadau gyda'r dyfeisiau fflach mewnol (RP2354) trwy hepgor y fflach ar fwrdd yn unig cof, neu hyd yn oed ei ddefnyddio fel dyfais fflach eilaidd (mwy ar hyn yn nes ymlaen). Nid oes llawer o wahaniaeth rhwng y ddau fwrdd, heblaw am y ffaith bod gan y fersiwn QFN-80 resi hirach o benawdau i ddarparu ar gyfer y GPIO ychwanegol, ac felly mae'r bwrdd yn fwy.

Ar wahân i'r pecyn, y gwahaniaeth lefel bwrdd mwyaf rhwng y gyfres RP235x a RP2040 yw'r cyflenwadau pŵer. Mae gan y gyfres RP235x rai pinnau pŵer newydd, a rheolydd mewnol gwahanol. Mae rheolydd llinol 100mA yr RP2040 wedi'i ddisodli gan reoleiddiwr newid 200mA, ac o'r herwydd, mae angen rhywfaint o gylchedau penodol iawn, ac ni chymerir fawr o ofal gyda'r gosodiad. Argymhellir yn gryf eich bod yn dilyn ein cynllun a'n dewis o gydrannau yn agos; rydym eisoes wedi mynd trwy'r boen o orfod gwneud sawl fersiwn o'r dyluniad, felly gobeithio nad oes rhaid i chi.

Ffigur 2. Rendro KiCad 3D o'r dyluniad Lleiaf RP2350B cynample

Y Dyluniad

Bwriad y dyluniad Lleiaf examples yw creu pâr o fyrddau syml gan ddefnyddio'r gyfres RP235x, a ddylai fod yn rhad ac yn hawdd eu gweithgynhyrchu, heb ddefnyddio technolegau PCB egsotig yn ddiangen. Mae'r byrddau Lleiaf felly yn ddyluniadau 2 haen, gan ddefnyddio cydrannau a ddylai fod ar gael yn gyffredin, ac i gyd wedi'u gosod ar ochr uchaf y bwrdd. Er y byddai'n braf defnyddio cydrannau mawr, hawdd eu sodro â llaw, mae traw bach y sglodion QFN (0.4mm) yn golygu bod defnyddio rhai cydrannau goddefol 0402 (metrig 1005) yn anochel os yw'r holl GPIOs i'w defnyddio. Er nad yw sodro cydrannau 0402 â llaw yn rhy heriol gyda haearn sodro gweddus, mae bron yn amhosibl sodro'r QFNs heb offer arbenigol.

Dros yr ychydig adrannau nesaf, rydw i'n mynd i geisio esbonio beth yw pwrpas y cylchedwaith ychwanegol, a gobeithio sut y daethom i wneud y dewisiadau a wnaethom. Gan fy mod yn mynd i fod yn siarad am ddau ddyluniad ar wahân, un ar gyfer pob maint pecyn, rwyf wedi ceisio cadw pethau mor syml ag y gallaf. Cyn belled ag y bo modd, mae'r holl gyfeiriadau cydran ar gyfer y ddau fwrdd yn union yr un fath, felly os cyfeiriaf at U1, R1, ac ati, yna mae'r un mor berthnasol i'r ddau fwrdd. Yr eithriad amlwg yw pan fydd y gydran ar un o'r byrddau yn unig (ym mhob achos, bydd hyn ar yr amrywiad 80 pin mwy), yna dim ond ar y dyluniad QFN-80 y bydd y gydran dan sylw; ar gyfer cynample, dim ond ar y bwrdd hwn y mae R13 yn ymddangos.

Pennod 2. Pŵer

Mae cyflenwadau pŵer y gyfres RP235x a'r RP2040 ychydig yn wahanol y tro hwn, er yn ei ffurfweddiad symlaf, mae angen dau gyflenwad, 3.3V ac 1.1V o hyd. Mae'r gyfres RP235x ar yr un pryd yn fwy newynog pŵer, gan ei fod yn berfformiad uwch, a hefyd yn fwy cynnil (pan mewn cyflwr pŵer isel) na'i ragflaenydd, ac felly mae'r rheolydd llinellol ar y RP2040 wedi'i uwchraddio gyda rheolydd newid. Mae hyn yn caniatáu mwy o effeithlonrwydd pŵer i ni ar gerrynt uwch (hyd at 200mA o'i gymharu â'r 100mA yn flaenorol).

Cyfrol newydd ar sglodiontage rheoleiddiwr

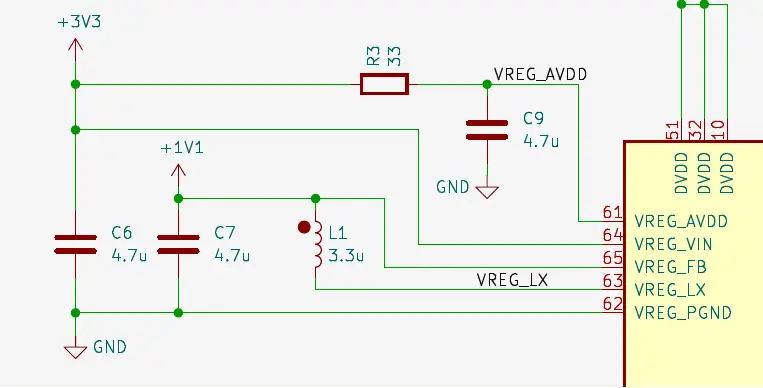

Ffigur 3. Adran sgematig yn dangos y gylched rheolydd mewnol

Roedd gan reoleiddiwr llinellol yr RP2040 ddau bin, mewnbwn 3.3V, ac allbwn 1.1V i gyflenwi'r DVDD ar y sglodion. Y tro hwn, mae gan reoleiddiwr y gyfres RP235x bum pin, ac mae angen rhywfaint o gydrannau allanol i wneud iddo weithio. Er bod hyn yn ymddangos yn gam yn ôl o ran defnyddioldeb, mae gan y rheolydd newid y fantaistage bod yn fwy ynni-effeithlon ar gerrynt llwyth uwch.

Fel y mae'r enw'n awgrymu, mae'r rheolydd yn troi ymlaen ac i ffwrdd yn gyflym transistor mewnol sy'n cysylltu'r mewnbwn 3.3V cyftage (VREG_VIN) i'r pin VREG_LX, a gyda chymorth anwythydd (L1) a chynhwysydd allbwn (C7), gall gynhyrchu cyfaint allbwn DCtagd sydd wedi'i gamu i lawr o'r mewnbwn. Mae'r pin VREG_FB yn monitro'r cyfaint allbwntage, ac yn addasu cymhareb ymlaen/diffodd y cylch newid, i sicrhau bod y cyftage yn cael ei gynnal. Wrth i gerrynt mawr gael eu newid o VREG_VIN i VREG_LX, mae angen cynhwysydd mawr (C6) yn agos at y mewnbwn, felly nid ydym yn cynhyrfu'r cyflenwad 3.3V yn ormodol. Wrth siarad am y cerrynt newid mawr hyn, mae'r rheolydd hefyd yn dod â'i gysylltiad dychwelyd daear ei hun, VREG_PGND. Yn yr un modd gyda VREG_VIN a VREG_LX, mae cynllun y cysylltiad hwn yn hollbwysig, ac er bod yn rhaid i VREG_PGND gysylltu â'r prif GND, rhaid ei wneud yn y fath fodd fel bod yr holl gerrynt switsio mawr yn dychwelyd yn uniongyrchol i'r pin PGND, heb darfu ar weddill y y GND gormod.

Y pin olaf yw VREG_AVDD, sy'n cyflenwi'r cylchedwaith analog o fewn y rheolydd, ac mae hyn yn sensitif iawn i sŵn.

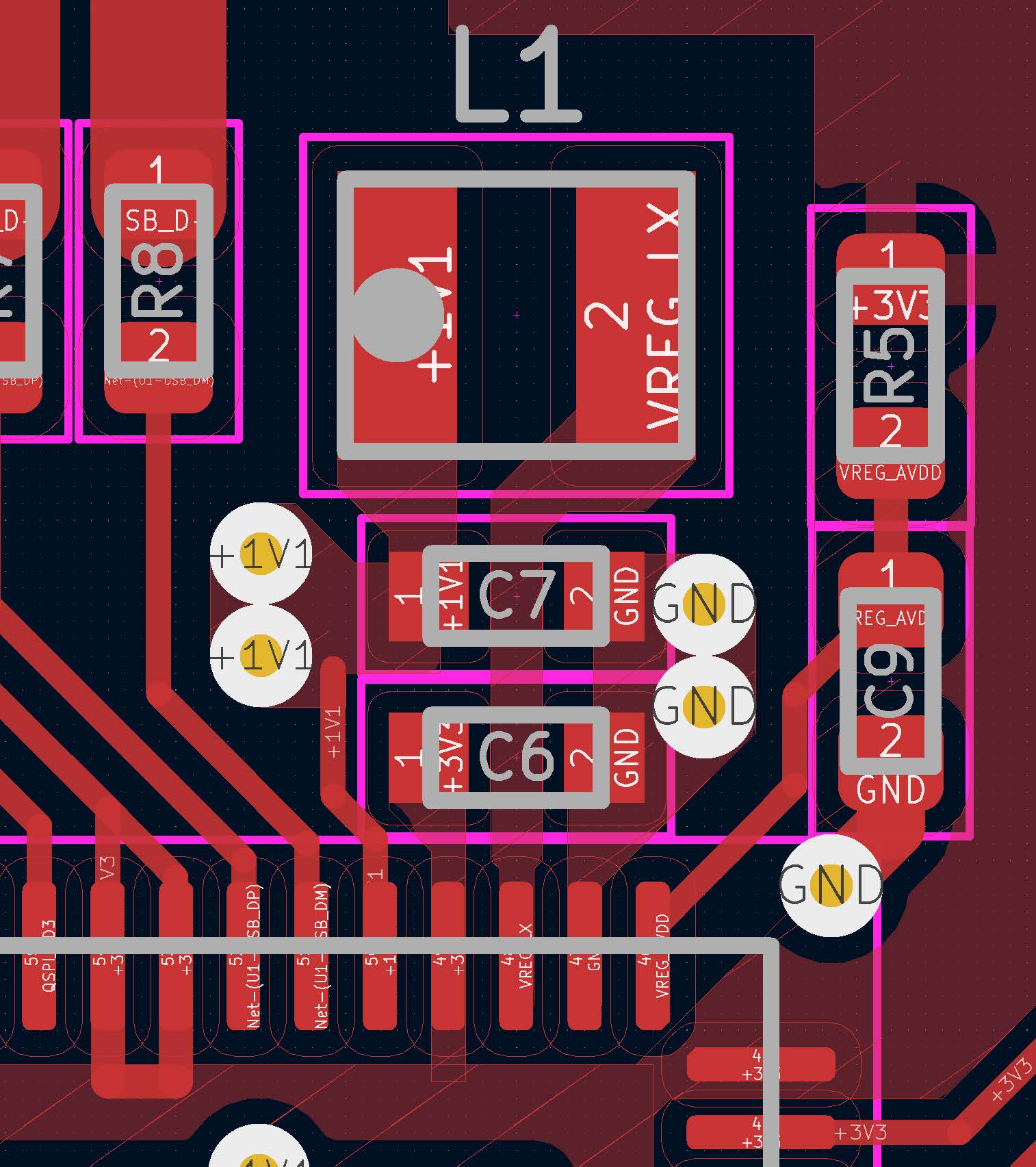

Ffigur 4. Adran sgematig yn dangos gosodiad PCB y rheolydd

- Mae cynllun y rheolydd ar y byrddau lleiaf yn adlewyrchu'n agos yr un y Raspberry Pi Pico 2. Mae llawer iawn o waith wedi'i wneud i ddyluniad y gylched hon, ac mae angen llawer o iteriadau o'r PCB er mwyn ei gwneud cystal ag y gallwn. can. Er y gallech osod y cydrannau hyn mewn amrywiaeth o wahanol ffyrdd a dal i gael y rheolydd i 'weithio' (hy, cynhyrchu cyfaint allbwntage ar y lefel gywir yn fras, yn ddigon da i'w gael yn rhedeg cod), rydym wedi canfod bod angen i'n rheolydd gael ei drin yn union y ffordd gywir i'w gadw'n hapus, a thrwy fod yn hapus, rwy'n golygu cynhyrchu'r allbwn cywir cyfainttage o dan ystod o amodau cerrynt llwyth.

- Wrth berfformio ein harbrofion ar hyn, cawsom ein siomi braidd i gael ein hatgoffa na ellir bob amser anwybyddu byd anghyfleus ffiseg. Rydym ni, fel peirianwyr, i raddau helaeth yn ceisio gwneud hyn yn union; symleiddio cydrannau, anwybyddu (yn aml) nodweddion ffisegol di-nod, a chanolbwyntio yn lle hynny ar yr eiddo y mae gennym ddiddordeb ynddo.ampLe, nid yn unig mae gan wrthydd syml wrthwynebiad, ond hefyd anwythiad, ac ati. yn cael ei glwyfo, a chyfeiriad llif y cerrynt. Cawsom ein hatgoffa hefyd nad yw anwythydd 'cyflawn' wedi'i warchod yn golygu'r hyn y credwch y gallai. Mae'r maes magnetig yn cael ei wanhau i raddau helaeth, ond mae rhai yn dal i ddianc. Canfuom y gellid gwella perfformiad y rheolydd yn aruthrol os mai'r anwythydd yw'r 'ffordd gywir'.

- Mae'n ymddangos bod y maes magnetig sy'n allyrru o anwythydd 'ffordd anghywir' yn ymyrryd â chynhwysydd allbwn y rheolydd (C7), sydd yn ei dro yn cynhyrfu'r cylchedwaith rheoli o fewn RP2350. Gyda'r anwythydd yn y cyfeiriadedd cywir, a'r union gynllun a'r dewis o gydrannau a ddefnyddir yma, yna mae'r broblem hon yn diflannu. Yn ddiamau, bydd cynlluniau, cydrannau, ac ati eraill, a allai weithio gydag anwythydd mewn unrhyw gyfeiriadedd, ond maent yn fwyaf tebygol o ddefnyddio llawer mwy o le PCB i wneud hynny. Rydym wedi darparu'r cynllun argymelledig hwn i arbed yr oriau peirianneg niferus yr ydym wedi'u treulio i ddatblygu a mireinio'r datrysiad cryno hwn sy'n ymddwyn yn dda.

- Yn fwy at y pwynt, rydym yn mynd mor bell â dweud, os dewiswch beidio â defnyddio ein cynample, yna rydych yn gwneud hynny ar eich menter eich hun. Yn debyg iawn i ni eisoes gyda RP2040 a'r gylched grisial, lle rydyn ni'n mynnu (wel, yn awgrymu'n gryf) eich bod chi'n defnyddio rhan benodol (byddwn yn gwneud hynny eto yn adran grisial y ddogfen hon).

- Mae cyfeiriadedd yr anwythyddion bach hyn yn cael ei anwybyddu bron yn gyffredinol, gyda chyfeiriadedd dirwyn y coil yn amhosibl ei ddiddwytho, a hefyd wedi'i ddosbarthu ar hap ar hyd rîl o gydrannau. Yn aml gellir canfod bod meintiau cas anwythydd mwy â marciau polaredd arnynt, ond ni allem ddod o hyd i rai addas ym maint yr achos 0806 (metrig 2016) a ddewiswyd gennym. I'r perwyl hwn, rydym wedi gweithio gydag Abracon i gynhyrchu rhan 3.3μH gyda dot i ddangos polaredd, ac yn bwysig, dod ar rîl gyda nhw i gyd wedi'u halinio yn yr un ffordd. Mae'r TBD (neu bydd yn fuan iawn) ar gael i'r cyhoedd gan ddosbarthwyr. Fel y soniwyd yn gynharach, mae'r cyflenwad VREG_AVDD yn sensitif iawn i sŵn, ac felly mae angen ei hidlo. Gan fod y VREG_AVDD yn tynnu tua 200μA yn unig, canfuom fod hidlydd RC o 33Ω a 4.7μF yn ddigonol.

- Felly, i grynhoi, y cydrannau a ddefnyddir fydd…

- C6, C7 & C9 – 4.7μF (0402, 1005 metrig)

- L1 – Abracon TBD (0806, metrig 2016)

- R3 – 33Ω (0402, 1005 metrig)

- Mae taflen ddata RP2350 yn cynnwys trafodaeth fanylach ar argymhellion cynllun y rheolydd, gweler Cydrannau Allanol a gofynion gosodiad PCB.

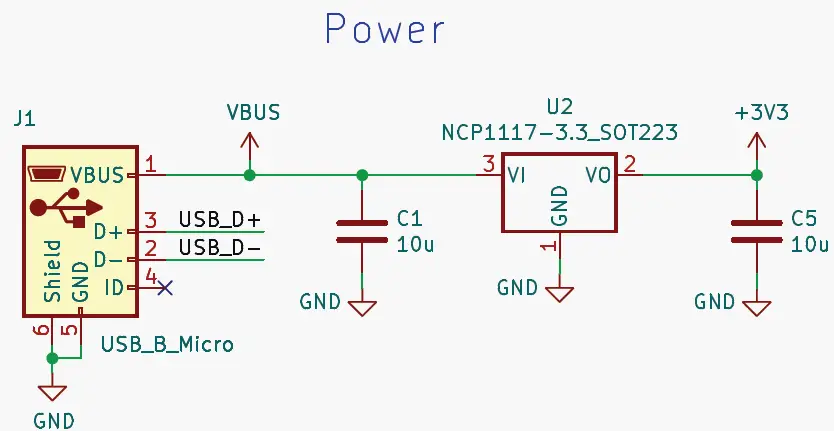

Cyflenwad mewnbwn

Mae'r cysylltiad pŵer mewnbwn ar gyfer y dyluniad hwn trwy'r pin 5V VBUS o gysylltydd Micro-USB (wedi'i labelu J1 yn Ffigur 5). Mae hwn yn ddull cyffredin o bweru dyfeisiau electronig, ac mae'n gwneud synnwyr yma, gan fod gan RP2350 ymarferoldeb USB, y byddwn yn ei weirio i binnau data'r cysylltydd hwn. Gan mai dim ond 3.3V sydd ei angen arnom ar gyfer y dyluniad hwn (daw'r cyflenwad 1.1V o'r mewnol), mae angen i ni ostwng y cyflenwad USB 5V sy'n dod i mewn, yn yr achos hwn, gan ddefnyddio cyfrol allanol arall.tage rheolydd, yn yr achos hwn rheolydd llinol (aka rheolydd Gollwng Isel, neu LDO). Ar ôl canmol rhinweddau defnyddio rheolydd newid effeithlon yn flaenorol, gallai hefyd fod yn ddewis doeth defnyddio un yma hefyd, ond rwyf wedi dewis symlrwydd. Yn gyntaf, mae defnyddio Gorchymyn Datblygu Lleol bron bob amser yn haws. Nid oes angen unrhyw gyfrifiadau i ddarganfod pa inductor maint y dylech ei ddefnyddio, na pha mor fawr yw'r cynwysyddion allbwn, ac mae'r gosodiad fel arfer yn llawer symlach hefyd. Yn ail, nid arbed pob diferyn olaf o bŵer yw'r nod yma; os oedd, byddwn yn ystyried o ddifrif defnyddio rheolydd newid, a gallwch ddod o hyd i gynample o wneud hynny ar y Raspberry Pi Pico 2. Ac yn drydydd, gallaf 'fenthyg' y gylched a ddefnyddiais yn flaenorol ar fersiwn RP2040 o'r bwrdd Minimal. Mae gan yr NCP1117 (U2) a ddewisir yma allbwn sefydlog o 3.3V, mae ar gael yn eang, a gall ddarparu hyd at 1A o gerrynt, a fydd yn ddigon ar gyfer y rhan fwyaf o ddyluniadau. Mae edrych ar y daflen ddata ar gyfer yr NCP1117 yn dweud wrthym fod y ddyfais hon yn gofyn am gynhwysydd 10μF ar y mewnbwn, ac un arall ar yr allbwn (C1 a C5).

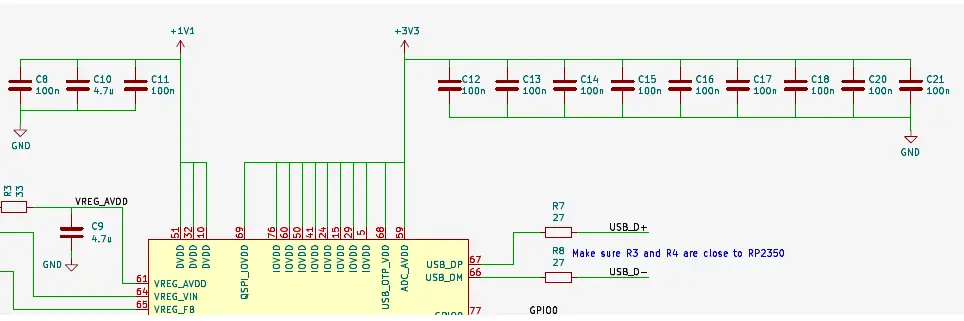

Datgysylltu cynwysorau

Ffigur 6. Adran sgematig yn dangos y mewnbynnau cyflenwad pŵer RP2350, cyftage rheolydd a chynwysorau datgysylltu

Agwedd arall ar ddyluniad y cyflenwad pŵer yw'r cynwysyddion datgysylltu sydd eu hangen ar gyfer RP2350. Mae'r rhain yn darparu dwy swyddogaeth sylfaenol. Yn gyntaf, maen nhw'n hidlo sŵn cyflenwad pŵer, ac yn ail, yn darparu cyflenwad tâl lleol y gall y cylchedau y tu mewn i RP2350 ei ddefnyddio ar fyr rybudd. Mae hyn yn atal y cyftagBydd y lefel yn yr ardal gyfagos yn gostwng yn ormodol pan fydd y galw presennol yn cynyddu'n sydyn. Oherwydd, o hyn, mae'n bwysig gosod datgysylltu yn agos at y pinnau pŵer. Fel arfer, rydym yn argymell defnyddio cynhwysydd 100nF fesul pin pŵer, fodd bynnag, rydym yn gwyro oddi wrth y rheol hon mewn cwpl o achosion.

Ffigur 7. Rhan o'r cynllun yn dangos llwybro a datgysylltu RP2350

- Yn gyntaf, er mwyn gallu cael digon o le i bob un o'r pinnau sglodion allu cael eu cyfeirio allan, i ffwrdd o'r ddyfais, mae'n rhaid i ni gyfaddawdu gyda faint o gynwysorau datgysylltu y gallwn eu defnyddio. Yn y dyluniad hwn, mae pinnau 53 a 54 o RP2350A (pinnau 68 a 69 o RP2350B) yn rhannu cynhwysydd sengl (C12 yn Ffigur 7 a Ffigur 6), gan nad oes llawer o le ar yr ochr honno i'r ddyfais, a'r cydrannau a chynllun y rheolydd sy'n cael blaenoriaeth.

- Gellid goresgyn y diffyg lle hwn i raddau pe baem yn defnyddio technoleg fwy cymhleth/drud, megis cydrannau llai, neu PCB pedair haen gyda chydrannau ar yr ochr uchaf a'r ochr isaf. Mae hwn yn gyfaddawd dylunio; rydym wedi lleihau'r cymhlethdod a'r gost, ar draul cael llai o gynhwysedd datgysylltu, a chynwysorau sydd ychydig ymhellach i ffwrdd o'r sglodyn nag sy'n optimaidd (mae hyn yn cynyddu'r anwythiad). Gallai hyn gael yr effaith o gyfyngu ar y cyflymder uchaf y gallai'r dyluniad weithredu arno, gan fod y cyftaggallai e gyflenwad fynd yn rhy swnllyd a disgyn yn is na'r isafswm a ganiateir cyftage; ond ar gyfer y rhan fwyaf o geisiadau, dylai'r cyfaddawd hwn fod yn dderbyniol.

- Y gwyriad arall o'r rheol 100nF yw er mwyn i ni allu gwella'r cyftage perfformiad rheolyddion; rydym yn argymell defnyddio 4.7μF ar gyfer C10, sef y gosod ar ochr arall y sglodion gan y rheolydd.

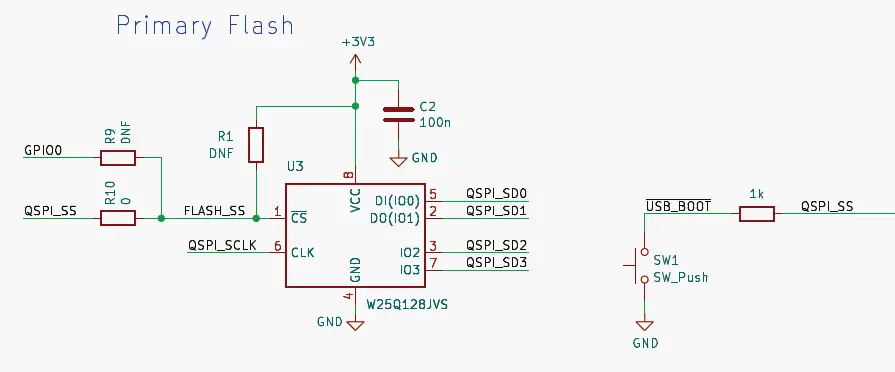

Pennod 3. Cof Fflach

Fflach cynradd

Ffigur 8. Adran sgematig yn dangos y prif gof fflach a chylchedwaith USB_BOOT

- Er mwyn gallu storio cod rhaglen y gall RP2350 gychwyn a rhedeg ohono, mae angen i ni ddefnyddio cof fflach, yn benodol, cof fflach quad SPI. Y ddyfais a ddewisir yma yw dyfais W25Q128JVS (U3 yn Ffigur 8), sef sglodyn 128Mbit (16MB). Dyma'r maint cof mwyaf y gall RP2350 ei gefnogi. Os nad oes angen cymaint o le storio ar eich cais penodol, yna gellid defnyddio cof llai a rhatach yn lle hynny.

- Gan y gall y bws data hwn fod yn eithaf uchel ac yn cael ei ddefnyddio'n rheolaidd, dylai pinnau QSPI RP2350 gael eu gwifrau'n uniongyrchol i'r fflach, gan ddefnyddio cysylltiadau byr i gynnal cywirdeb y signal, a hefyd i leihau crosstalk mewn cylchedau cyfagos. Crosstalk yw lle mae signalau ar un rhwyd cylched yn gallu achosi cyftagau ar gylched gyfagos, a allai achosi gwallau.

- Mae'r signal QSPI_SS yn achos arbennig. Mae wedi'i gysylltu â'r fflach yn uniongyrchol, ond mae ganddo hefyd ddau wrthydd (wel, pedwar, ond dof ymlaen at hynny yn ddiweddarach) sy'n gysylltiedig ag ef. Mae'r cyntaf (R1) yn tynnu i fyny at y cyflenwad 3.3V. Mae'r cof fflach yn ei gwneud yn ofynnol i'r mewnbwn sglodyn-ddewis fod ar yr un cyftage fel ei bin cyflenwad 3.3V ei hun gan fod y ddyfais yn cael ei bweru, fel arall, nid yw'n gweithio'n gywir. Pan fydd y RP2350 wedi'i bweru, bydd ei bin QSPI_SS yn tynnu i fyny yn awtomatig, ond mae cyfnod byr o amser yn ystod y broses o droi ymlaen lle na ellir gwarantu cyflwr y pin QSPI_SS. Mae ychwanegu gwrthydd tynnu i fyny yn sicrhau y bodlonir y gofyniad hwn bob amser. Mae R1 wedi'i farcio fel DNF (Peidiwch â Ffitio) ar y sgematig, gan ein bod wedi canfod, gyda'r ddyfais fflach benodol hon, nad oes angen tynnu i fyny allanol. Fodd bynnag, os defnyddir fflach wahanol, efallai y bydd yn bwysig gallu gosod gwrthydd 10kΩ yma, felly mae wedi'i gynnwys rhag ofn.

- Mae'r ail wrthydd (R6) yn wrthydd 1kΩ, wedi'i gysylltu â botwm gwthio (SW1) wedi'i labelu 'USB_BOOT'. Mae hyn oherwydd bod y pin QSPI_SS yn cael ei ddefnyddio fel 'strap cist'; Mae RP2350 yn gwirio gwerth yr I/O hwn yn ystod y dilyniant cychwyn, ac os canfyddir ei fod yn rhesymeg 0, yna mae RP2350 yn dychwelyd i'r modd BOOTSEL, lle mae RP2350 yn cyflwyno ei hun fel dyfais storio màs USB, a gellir copïo'r cod yn uniongyrchol iddo. Os byddwn yn pwyso'r botwm yn unig, byddwn yn tynnu QSPI_SS pin i'r llawr, ac os caiff y ddyfais ei ailosod wedyn (ee trwy doglo'r pin RUN), bydd RP2350 yn ailgychwyn yn y modd BOOTSEL yn lle ceisio rhedeg cynnwys y fflach. Dylid gosod y gwrthyddion hyn, R2 a R6 (R9 a R10 hefyd), yn agos at y sglodion fflach, felly rydym yn osgoi darnau ychwanegol o draciau copr a allai effeithio ar y signal.

- Mae'r uchod i gyd yn benodol berthnasol i'r RP2350, nad oes ganddo fflach fewnol. Wrth gwrs, mae gan y dyfeisiau RP2354 atgofion fflach 2MB mewnol, felly nid oes angen y cof U3 allanol, felly gellir tynnu U3 yn ddiogel o'r sgematig, neu ei adael heb ei boblogi. Yn y naill neu'r llall o'r achosion hyn, byddem yn dal i fod eisiau cadw'r switsh USB_BOOT wedi'i gysylltu â QSPI_SS, fel y gallwn fynd i mewn i fodd cychwyn USB o hyd.

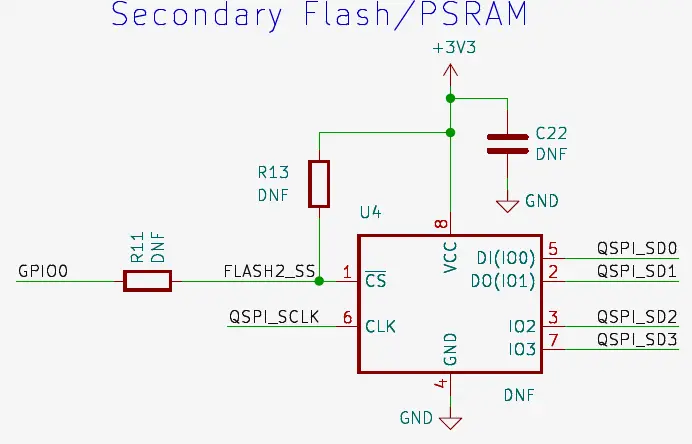

Fflach eilaidd neu PSRAM

- Mae'r gyfres RP235x bellach yn cefnogi ail ddyfais cof gan ddefnyddio'r un pinnau QSPI, gyda GPIO yn darparu'r dewis sglodion ychwanegol. Felly, os ydym yn defnyddio RP2354 (sydd â fflach fewnol), yna gallem ddefnyddio U3 fel fflach eilaidd, neu hyd yn oed gosod dyfais PSRAM yn ei le. Er mwyn gwneud hyn, mae angen i ni ddatgysylltu QSPI_SS o U3, a'i gysylltu â GPIO addas yn lle hynny. Y GPIO agosaf sy'n gallu bod yn ddewis sglodion (XIP_CS1n) yw GPIO0, felly trwy dynnu'r 0Ω o R10, a'i osod ar R9, gallwn nawr gael mynediad i U3 yn ogystal â'r fflach ar sglodion. Er mwyn cymryd advan yn llawntage o'r nodwedd hon, lle mae gennym ddau ddyfais cof allanol fel y gall y rhannau RP2350 di-fflach elwa, mae'r mwyaf o'r ddau fwrdd Lleiaf, ar gyfer y RP2350B, yn cynnwys ôl troed dewisol (U4) ar gyfer sglodyn cof ychwanegol.

Ffigur 9. Adran sgematig yn dangos y ddyfais cof eilaidd ddewisol

Er mwyn gallu defnyddio'r ddyfais hon, mae'n amlwg y bydd yn rhaid ei phoblogi , yn ogystal ag R11 (0Ω), ac R13 (10KΩ). Mae ychwanegu R11 yn cysylltu GPIO0 (y signal XIP_CS1n) â dewis sglodion yr ail gof. Yn bendant, mae angen tynnu'r pin dethol sglodion i fyny y tro hwn, gan fod cyflwr rhagosodedig GPIO0 i'w dynnu'n isel ar bŵer i fyny, a fyddai'n achosi i'n dyfais fflach fethu. Byddai angen C22 hefyd i ddarparu datgysylltu cyflenwad pŵer lleol ar gyfer U4.

Sglodion fflach â chymorth

Dilyniant chwiliedydd fflach cychwynnol, a ddefnyddir gan y gwaelod i echdynnu'r ail stage o fflach, yn defnyddio gorchymyn darllen cyfresol 03h, gyda chyfeiriadau 24-did, a chloc cyfresol o tua 1MHz. Mae'n beicio dro ar ôl tro trwy'r pedwar cyfuniad o bolaredd cloc a chyfnod cloc, gan chwilio am eiliad dilystage gwiriad CRC32.

Fel yr ail stagMae e wedyn yn rhydd i ffurfweddu gweithredu yn ei le gan ddefnyddio'r un gorchymyn darllen cyfresol 03h, gall RP2350 berfformio gweithredu fflach wedi'i storio yn ei le gydag unrhyw sglodyn yn cefnogi darlleniad cyfresol 03h gyda chyfeiriadau 24-bit, sy'n cynnwys y rhan fwyaf o ddyfeisiau fflach 25-cyfres . Mae'r SDK yn darparu example eiliad stage ar gyfer CPOL=0 CPHA=0, yn https://github.com/raspberrypi/pico-sdk/blob/master/src/rp2350/boot_stage2/boot2_generic_03h.S. Er mwyn cefnogi rhaglennu fflach gan ddefnyddio'r arferion yn y gwaelod, rhaid i'r ddyfais hefyd ymateb i'r gorchmynion canlynol:

- Rhaglen tudalen 02h 256-beit

- Darllen cofrestr statws 05h

- 06h set ysgrifennu galluogi clicied

- Dileu sector 20h 4kB

Mae RP2350 hefyd yn cefnogi amrywiaeth eang o ddulliau mynediad deuol-SPI a QSPI. Am gynample, https://github.com/raspberrypi/pico-sdk/blob/master/src/rp2350/boot_stage2/boot2_w25q080.S yn ffurfweddu dyfais Winbond W25Q-cyfres ar gyfer modd darllen parhaus quad-IO, lle mae RP2350 yn anfon cyfeiriadau quad-IO (heb ragddodiad gorchymyn) ac mae'r fflach yn ymateb gyda data quad-IO.

Mae angen peth gofal gyda moddau fflach XIP lle mae'r ddyfais fflach yn stopio ymateb i orchmynion cyfresol safonol, fel y modd darllen parhaus Winbond a grybwyllir uchod. Gall hyn achosi problemau pan fydd RP2350 yn cael ei ailosod, ond nid yw'r ddyfais fflach yn gylchrediad pŵer, oherwydd ni fydd y fflach wedyn yn ymateb i ddilyniant chwiliedydd fflach y bootrom. Cyn cyhoeddi darlleniad cyfresol 03h, mae'r bootrom bob amser yn cyhoeddi'r dilyniant sefydlog canlynol, sy'n ddilyniant ymdrech orau i ddod â XIP i ben ar ystod o ddyfeisiau fflach:

- CSn=1, IO[3:0]=4'b0000 (trwy dynnu lawr i osgoi cynnen), cyhoeddi ×32 cloc

- CSn=0, IO[3:0]=4'b1111 (trwy dynnu i fyny i osgoi cynnen), cyhoeddi ×32 cloc

- CSn=1

- CSn=0, MOSI=1'b1 (gyrru isel-Z, pob I/Os Hi-Z arall), cyhoeddi ×16 cloc

Os nad yw'r ddyfais a ddewiswyd gennych yn ymateb i'r dilyniant hwn pan yn ei modd darllen parhaus, yna mae'n rhaid ei gadw mewn cyflwr lle mae gorchymyn cyfresol yn rhagddodi pob trosglwyddiad, fel arall ni fydd RP2350 yn gallu adfer ar ôl ailosodiad mewnol.

I gael rhagor o fanylion am y QSPI , gweler Rhyngwyneb Cof QSPI (QMI) yn y daflen ddata RP2350.

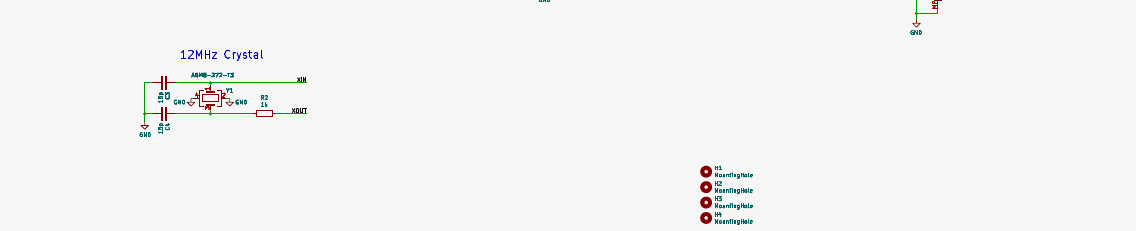

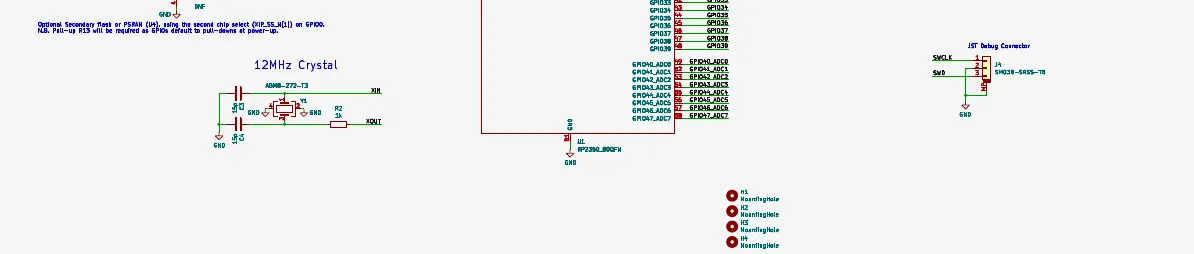

Pennod 4. Oscillator Grisial

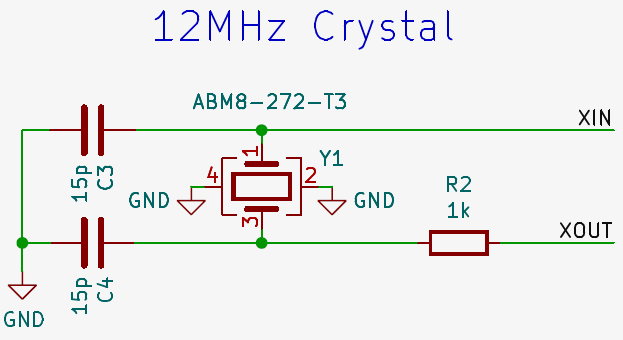

Ffigur 10. Adran sgematig yn dangos yr osgiliadur grisial a'r cynwysorau llwyth

- A siarad yn fanwl gywir, nid oes angen ffynhonnell cloc allanol ar RP2350 mewn gwirionedd, gan fod ganddo ei osgiliadur mewnol ei hun. Fodd bynnag, gan nad yw amlder yr oscillator mewnol hwn wedi'i ddiffinio na'i reoli'n dda, yn amrywio o sglodyn i sglodion, yn ogystal â chyfaint cyflenwad gwahanol.tages a thymheredd, argymhellir defnyddio ffynhonnell amledd allanol sefydlog. Nid yw cymwysiadau sy'n dibynnu ar union amleddau yn bosibl heb ffynhonnell amledd allanol, gyda USB yn gyn-brif gysefinample.

- Gellir darparu ffynhonnell amledd allanol mewn un o ddwy ffordd: naill ai trwy ddarparu ffynhonnell cloc gydag allbwn CMOS (ton sgwâr o IOVDD cyftage) i mewn i'r pin XIN, neu drwy ddefnyddio grisial 12MHz wedi'i gysylltu rhwng

- XIN a XOUT. Defnyddio grisial yw'r opsiwn a ffefrir yma, gan eu bod ill dau yn gymharol rhad ac yn gywir iawn.

- Y grisial a ddewiswyd ar gyfer y dyluniad hwn yw ABM8-272-T3 (Y1 yn Ffigur 10). Dyma'r un grisial 12MHz a ddefnyddir ar y Raspberry Pi Pico a Raspberry Pi Pico 2. Rydym yn argymell yn fawr defnyddio'r grisial hwn ynghyd â'r cylchedwaith cysylltiedig i sicrhau bod y cloc yn cychwyn yn gyflym o dan yr holl amodau heb niweidio'r grisial ei hun. Mae gan y grisial oddefgarwch amlder o 30ppm, a ddylai fod yn ddigon da ar gyfer y rhan fwyaf o geisiadau. Ynghyd â goddefgarwch amledd o +/- 30ppm, mae ganddo uchafswm ESR o 50Ω, a chynhwysedd llwyth o 10pF, ac roedd y ddau ohonynt yn effeithio ar y dewis o gydrannau cysylltiedig.

- Er mwyn i grisial osgiliadu ar yr amlder a ddymunir, mae'r gwneuthurwr yn pennu'r cynhwysedd llwyth sydd ei angen arno i wneud hynny, ac yn yr achos hwn, mae'n 10pF. Cyflawnir y cynhwysedd llwyth hwn trwy osod dau gynhwysydd o werth cyfartal, un ar bob ochr i'r grisial i'r llawr (C3 a C4). O bwynt y grisial o view, mae'r cynwysyddion hyn wedi'u cysylltu mewn cyfres rhwng ei ddwy derfynell. Mae theori cylched sylfaenol yn dweud wrthym eu bod yn cyfuno i roi cynhwysedd o (C3*C4)/(C3+C4), ac fel C3=C4, yna yn syml C3/2 ydyw. Yn y cynampLe, rydym wedi defnyddio cynwysyddion 15pF, felly cyfuniad y gyfres yw 7.5pF. Yn ogystal â'r cynhwysedd llwyth bwriadol hwn, rhaid inni hefyd ychwanegu gwerth am y cynhwysedd ychwanegol anfwriadol, neu'r cynhwysedd parasitig, a gawn o'r traciau PCB a'r pinnau XIN a XOUT o RP2350. Byddwn yn tybio gwerth o 3pF ar gyfer hyn, a chan fod y cynhwysedd hwn yn gyfochrog â C3 a C4, rydym yn syml yn ychwanegu hwn i roi cyfanswm cynhwysedd llwyth i ni o 10.5pF, sy'n ddigon agos at y targed o 10pF. Fel y gallwch weld, mae cynhwysedd parasitig yr olion PCB yn ffactor, ac felly mae angen i ni eu cadw'n fach fel nad ydym yn cynhyrfu'r grisial a'i atal rhag pendilio yn ôl y bwriad. Ceisiwch gadw'r cynllun mor fyr â phosibl.

- Yr ail ystyriaeth yw uchafswm ESR (ymwrthedd cyfres cyfatebol) y grisial. Rydym wedi dewis dyfais gydag uchafswm o 50Ω, gan ein bod wedi canfod bod hwn, ynghyd â gwrthydd cyfres 1kΩ (R2), yn werth da i atal y grisial rhag cael ei or-yrru a chael ei niweidio wrth ddefnyddio IOVDD lefel o 3.3V. Fodd bynnag, os yw IOVDD yn llai na 3.3V, yna mae cerrynt gyriant y pinnau XIN/XOUT yn cael ei leihau, a byddwch yn gweld bod y ampmae goleuad y grisial yn is, neu efallai na fydd hyd yn oed yn osgiliad o gwbl. Yn yr achos hwn, bydd angen defnyddio gwerth llai o'r gwrthydd cyfres. Bydd unrhyw wyriad o'r gylched grisial a ddangosir yma, neu gyda lefel IOVDD heblaw 3.3V, yn gofyn am brofion helaeth i sicrhau bod y grisial yn pendilio o dan yr holl amodau, ac yn cychwyn yn ddigon cyflym i beidio ag achosi problemau gyda'ch cais.

Grisial a argymhellir

- Ar gyfer dyluniadau gwreiddiol gan ddefnyddio RP2350 rydym yn argymell defnyddio'r Abracon ABM8-272-T3. Am gynample, yn ychwanegol at y dyluniad lleiaf cynample, gweler sgematig bwrdd Pico 2 yn Atodiad B o Daflen Data Raspberry Pi Pico 2 a dyluniad Pico 2 files.

- I gael y perfformiad a'r sefydlogrwydd gorau ar draws ystodau tymheredd gweithredu nodweddiadol, defnyddiwch yr Abracon ABM8-272-T3. Gallwch ddod o hyd i'r ABM8-272-T3 yn uniongyrchol gan Abracon neu gan ailwerthwr awdurdodedig. Mae Pico 2 wedi'i diwnio'n benodol ar gyfer yr ABM8-272-T3, sydd â'r manylebau canlynol:

- Hyd yn oed os ydych chi'n defnyddio grisial gyda manylebau tebyg, bydd angen i chi brofi'r gylched dros ystod o dymheredd i sicrhau sefydlogrwydd.

- Mae'r osgiliadur grisial yn cael ei bweru o'r IOVDD cyftage. O ganlyniad, bu'r grisial Abracon a'r arbennig hwnnw dampgwrthydd ing yn cael eu tiwnio ar gyfer gweithrediad 3.3V. Os ydych yn defnyddio IO cyftage, bydd angen i chi ail-diwnio.

- Mae unrhyw newidiadau i baramedrau grisial yn peryglu ansefydlogrwydd ar draws unrhyw gydrannau sy'n gysylltiedig â'r gylched grisial.

- Os na allwch ddod o hyd i'r grisial a argymhellir yn uniongyrchol gan Abracon neu ailwerthwr, cysylltwch ceisiadau@raspberrypi.com.

Pennod 5. IOs

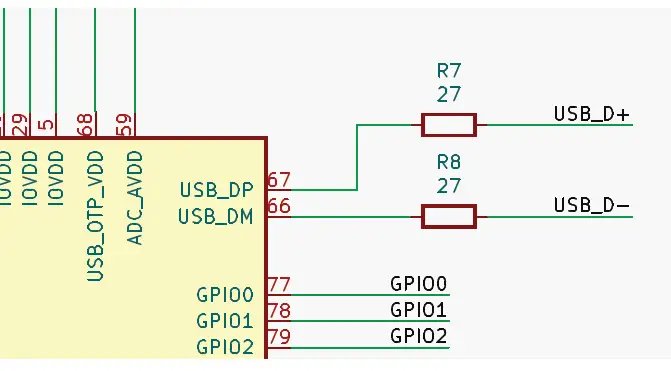

USB

Ffigur 11. Adran sgematig yn dangos pinnau USB RP2350 a therfyniad cyfres

- Mae'r RP2350 yn darparu dau binnau i'w defnyddio ar gyfer USB cyflymder llawn (FS) neu gyflymder isel (LS), naill ai fel gwesteiwr neu ddyfais, yn dibynnu ar y feddalwedd a ddefnyddir. Fel y trafodwyd eisoes, gall RP2350 hefyd gychwyn fel dyfais storio màs USB, felly mae gwifrau'r pinnau hyn i'r cysylltydd USB (J1 yn Ffigur 5) yn gwneud synnwyr. Nid yw'r pinnau USB_DP a USB_DM ar RP2350 yn gofyn am unrhyw dynnu i fyny neu dynnu i lawr ychwanegol (sy'n ofynnol i nodi cyflymder, FS neu LS, neu a yw'n westeiwr neu ddyfais), gan fod y rhain wedi'u cynnwys yn yr I/Os. Fodd bynnag, mae angen gwrthyddion terfynu cyfres 27Ω ar yr I/Os hyn (R7 a R8 yn Ffigur 11), wedi'u gosod yn agos at y sglodyn, er mwyn bodloni'r fanyleb rhwystriant USB.

- Er bod RP2350 wedi'i gyfyngu i gyfradd data cyflymder llawn (12Mbps), dylem geisio sicrhau bod rhwystriant nodweddiadol y llinellau trawsyrru (y traciau copr sy'n cysylltu'r sglodion â'r cysylltydd) yn agos at y

- Manyleb USB o 90Ω (wedi'i fesur yn wahaniaethol). Ar fwrdd 1mm o drwch fel hwn, os ydym yn defnyddio traciau 0.8mm o led ar USB_DP a USB_DM, gyda bwlch o 0.15mm rhyngddynt, dylem gael rhwystriant nodweddiadol gwahaniaethol o tua 90Ω. Mae hyn er mwyn sicrhau bod y signalau'n gallu teithio ar hyd y llinellau trawsyrru hyn mor lân â phosibl, gan leihau cyfaint yr offertage adlewyrchiadau a all leihau cyfanrwydd y signal. Er mwyn i'r llinellau trawsyrru hyn weithio'n iawn, mae angen i ni sicrhau bod tir yn union o dan y llinellau hyn. Ardal solet, di-dor o gopr daear, yn ymestyn hyd cyfan y trac. Ar y dyluniad hwn, mae bron y cyfan o'r haen gopr waelod wedi'i neilltuo i ddaear, a chymerwyd gofal arbennig i sicrhau bod y traciau USB yn mynd dros ddim byd ond y ddaear. Os dewisir PCB mwy trwchus nag 1mm ar gyfer eich adeiladwaith, yna mae gennym ddau opsiwn. Gallem ail-beiriannu'r llinellau trawsyrru USB i wneud iawn am y pellter mwy rhwng y trac a'r ddaear oddi tano (a allai fod yn amhosibl corfforol), neu gallem ei anwybyddu, a gobeithio am y gorau. Gall USB FS fod yn eithaf maddau, ond gall eich milltiroedd amrywio. Mae'n debygol o weithio mewn llawer o gymwysiadau, ond mae'n debyg na fydd yn cydymffurfio â'r safon USB.

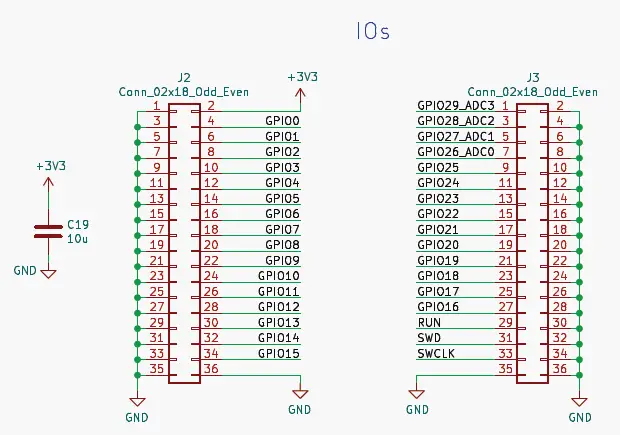

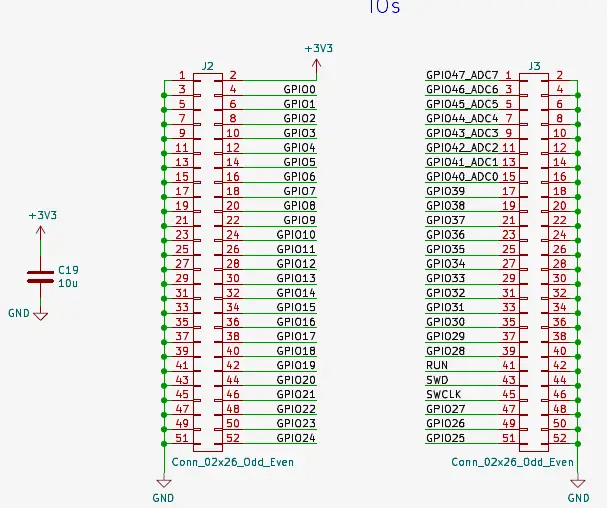

penawdau I/O

Ffigur 12. Adran sgematig yn dangos penawdau 2.54mm I/O y fersiwn QFN60

- Yn ogystal â'r cysylltydd USB a grybwyllwyd eisoes, mae yna bâr o benawdau rhes ddeuol 2.54mm (J2 a J3 yn Ffigur 12), un ar bob ochr i'r bwrdd, y mae gweddill yr I / O wedi'i gysylltu ag ef. Mae 30 GPIO ar yr RP2350A, tra bod 48 GPIO ar y RP2350B, felly mae'r penawdau ar y fersiwn hon o'r bwrdd Minimal yn fwy i ganiatáu ar gyfer y pinnau ychwanegol (gweler Ffigur 13).

- Gan mai dyluniad pwrpas cyffredinol yw hwn, heb unrhyw gymhwysiad penodol mewn golwg, mae'r I/O ar gael i'w gysylltu fel y mae'r defnyddiwr yn dymuno. Y rhes fewnol o binnau ar bob pennyn yw'r I/Os, ac mae'r rhes allanol i gyd wedi'u cysylltu â'r ddaear. Mae'n arfer da cynnwys llawer o seiliau ar gysylltwyr I/O. Mae hyn yn helpu i gynnal tir rhwystriant isel, a hefyd i ddarparu digon o lwybrau dychwelyd posibl ar gyfer cerhyntau sy'n teithio i'r safle ac oddi yno.

- Cysylltiadau I/O. Mae hyn yn bwysig er mwyn lleihau ymyrraeth electromagnetig a all gael ei achosi gan fod ceryntau dychwelyd signalau sy'n newid yn gyflym yn cymryd llwybrau hir, dolennog i gwblhau'r gylched.

- Mae'r ddau bennawd ar yr un grid 2.54mm, sy'n ei gwneud hi'n haws cysylltu'r bwrdd hwn â phethau eraill, fel byrddau bara. Efallai y byddwch am ystyried gosod pennawd un rhes yn unig yn lle'r pennawd rhes ddeuol, gan hepgor y rhes allanol o gysylltiadau daear, i'w gwneud yn fwy cyfleus i ffitio i fwrdd bara.

Ffigur 13. Adran sgematig yn dangos penawdau 2.54mm I/O y fersiwn QFN80

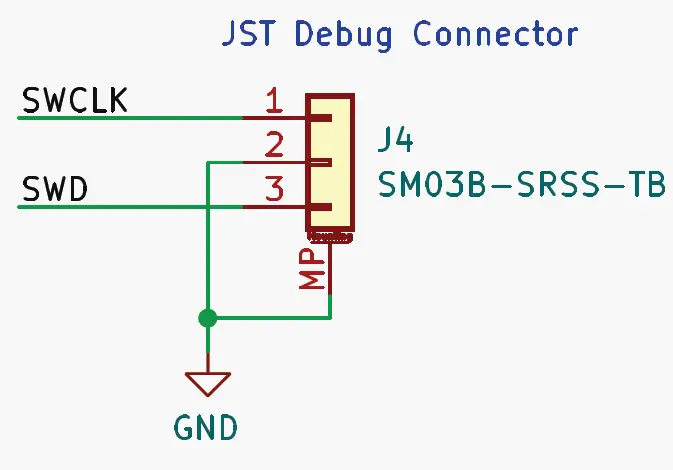

Cysylltydd dadfygio

Ffigur 14. Adran sgematig yn dangos y cysylltydd JST dewisol ar gyfer dadfygio SWD

Ar gyfer dadfygio ar sglodion, efallai yr hoffech chi gysylltu â rhyngwyneb SWD yr RP2350. Mae'r ddau bin, SWD a SWCLK, ar gael ar y pennawd 2.54mm, J3, i ganiatáu i'r stiliwr dadfygio o'ch dewis chi gael ei gysylltu'n hawdd. Yn ogystal â hyn, rwyf wedi cynnwys pennawd JST dewisol, sy'n caniatáu cysylltiad hawdd â Raspberry Pi Debug Probe. Nid oes angen i chi ddefnyddio hwn, bydd y penawdau 2.54mm yn ddigon os ydych yn bwriadu dadfygio meddalwedd, ond mae'n fwy cyfleus i mi wneud hynny. Rwyf wedi dewis cysylltydd llorweddol, yn bennaf oherwydd fy mod yn hoffi ei olwg, hyd yn oed os nad yw ar ymyl y bwrdd, ond mae rhai fertigol ar gael, er bod ganddynt ôl troed ychydig yn wahanol.

Botymau

Mae'r dyluniad Lleiaf bellach yn cynnwys nid un, ond dau fotwm, lle nad oedd gan y fersiwn RP240 ddim. Mae un ar gyfer dewis cist USB fel yr ydym wedi'i drafod yn flaenorol, ond mae'r ail yn botwm 'ailosod', wedi'i gysylltu â'r pin RUN. Nid yw'r un o'r rhain yn gwbl angenrheidiol (er y byddai'n rhaid disodli'r botwm BOOTSEL â phennawd neu debyg pe bai angen modd cychwyn USB), a gellir ei ddileu os yw gofod neu gost yn bryder, ond maent yn sicr yn gwneud defnyddio'r RP2350 ymhell. profiad mwy dymunol.

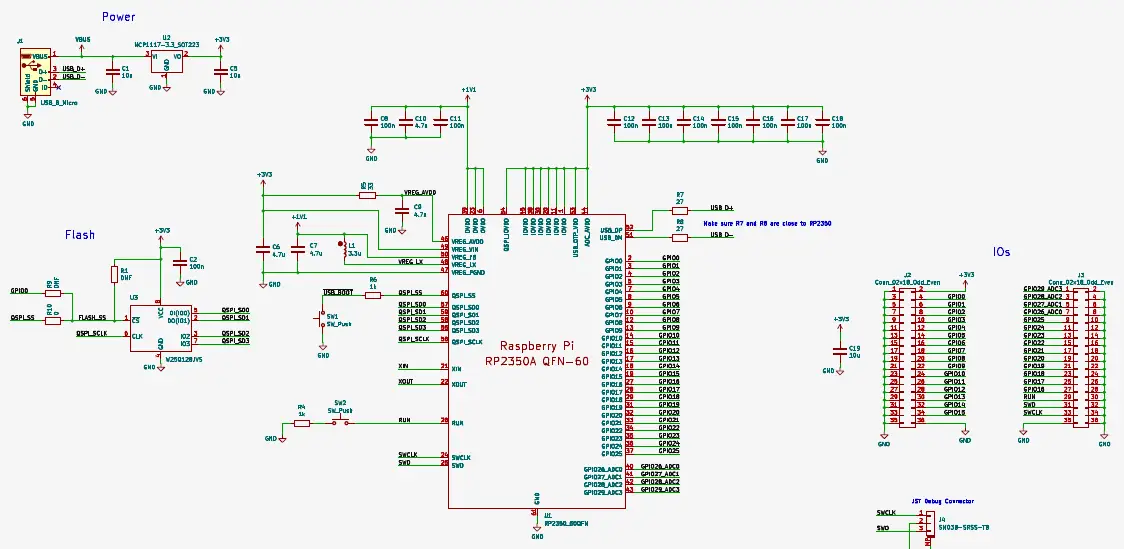

Atodiad A: Fersiwn sgematig gyflawn -RP2350A

Ffigur 15. Sgematig llawn o'r Dyluniad Lleiaf ar gyfer RP2350A

Atodiad B: Fersiwn sgematig gyflawn -RP2350B

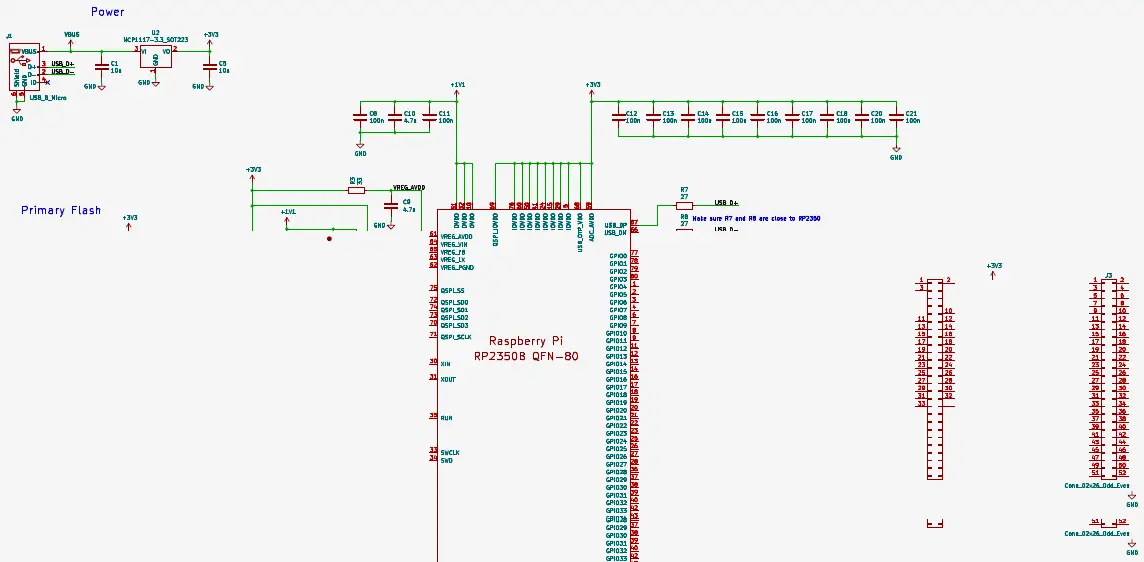

Ffigur 16. Sgematig llawn o'r Dyluniad Lleiaf ar gyfer RP2350B

Atodiad H: Hanes Rhyddhau Dogfennau

Awst 8 2024

Rhyddhad cychwynnol.

i Raspberry Pi

Mae Raspberry Pi yn nod masnach Raspberry Pi Ltd

Raspberry Pi Cyf

Dogfennau / Adnoddau

|

Raspberry Pi SC1631 Raspberry Microcontroller [pdfLlawlyfr Cyfarwyddiadau Microreolydd Mafon SC1631, SC1631, Microreolydd Mafon, Microreolydd |