Intel Blociau Array Logic Agilex a Modiwlau Rhesymeg Addasol

Intel® Agilex™ LAB ac ALM Overview

Mae'r bloc arae rhesymeg (LAB) yn cynnwys blociau adeiladu sylfaenol a elwir yn fodiwlau rhesymeg addasol (ALMs). Gallwch chi ffurfweddu'r LABs i weithredu swyddogaethau rhesymeg, swyddogaethau rhifyddeg, a swyddogaethau cofrestru.

Gallwch ddefnyddio hanner y LABs sydd ar gael yn y dyfeisiau Intel® Agilex™ fel LABs cof (MLABs). Efallai y bydd gan rai dyfeisiau gymhareb MLAB uwch.

Mae meddalwedd Intel Quartus® Prime ac offer synthesis trydydd parti eraill a gefnogir yn awtomatig yn dewis y modd priodol ar gyfer swyddogaethau cyffredin fel cownteri, gwiberod, tynnuwyr, a swyddogaethau rhifyddeg.

Pensaernïaeth Graidd Intel Hyperflex™, Dyfais Intel Agilex Drosoddview

Yn darparu mwy o wybodaeth am Hyper-Registers a phensaernïaeth graidd Intel Hyperflex™. Mae Hyper-Gofrestrau yn gofrestrau ychwanegol sydd ar gael ym mhob segment llwybro rhyng-gysylltu ledled y ffabrig craidd, gan gynnwys y segmentau llwybro sy'n gysylltiedig â mewnbynnau ac allbynnau LAB.

Cofrestr Intel Hyperflex™

Mae teulu dyfeisiau Intel Agilex yn seiliedig ar bensaernïaeth graidd Intel Hyperflex™.

Mae LAB Intel Agilex yn cynnwys cofrestrau Intel Hyperflex a nodweddion eraill a gynlluniwyd i hwyluso ail-amseru. Mae cofrestrau Intel Hyperflex ar gael mewn ALMs ac yn cario cadwyni. Fel y dangosir yn ffigwr Manylion Cysylltiad Intel Agilex ALM, mae'r cofrestrau Intel Hyperflex wedi'u lleoli ar y clir cydamserol ac mae cloc yn galluogi mewnbynnau i gynyddu neu leihau oedi llwybr. Gellir galluogi holl gofrestrau Intel Hyperflex a chânt eu rheoli gan feddalwedd Intel Quartus Prime yn ystod ail-amseru.

Pensaernïaeth a Nodweddion Intel Agilex LAB ac ALM

Mae'r adrannau canlynol yn disgrifio'r LAB a'r ALM ar gyfer dyfeisiau Intel Agilex.

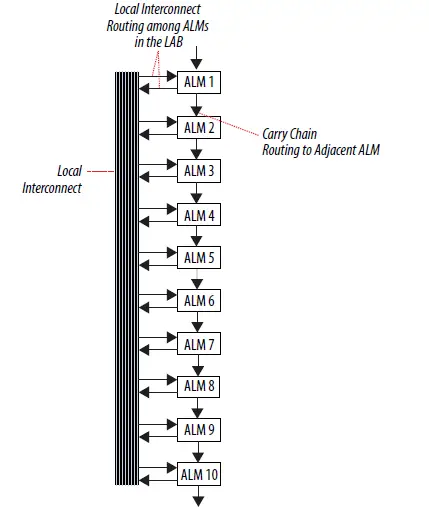

LAB

Mae'r LABs yn flociau rhesymeg ffurfweddadwy sy'n cynnwys grŵp o adnoddau rhesymeg. Mae pob LAB yn cynnwys rhesymeg bwrpasol ar gyfer gyrru signalau rheoli i'w ALMs. Mae'r MLAB yn uwch-set o'r LAB ac mae'n cynnwys yr holl nodweddion LAB. Mae cyfanswm o 10 ALM ym mhob LAB, fel y dangosir yn ffigwr Intel Agilex LAB a MLAB Strwythur.

Ffigur 1.

Strwythur LAB Intel Agilex ac yn Cydgysylltu Drosoddview

Mae'r ffigur hwn yn dangos gorview o strwythur Intel Agilex LAB a MLAB gyda'r LAB yn cydgysylltu.

Gwybodaeth Gysylltiedig

Gwybodaeth Gysylltiedig

MLAB ar dudalen 6

MLAB

Mae pob MLAB yn cefnogi uchafswm o 640 did o SRAM porthladd deuol syml. Gallwch chi ffurfweddu pob ALM mewn MLAB fel bloc cof 32 (dyfnder) x 2 (lled), gan arwain at gyfluniad o 32 (dyfnder) x 20 (lled) bloc SRAM porthladd deuol syml.

Ffigur 2.

Intel Agilex LAB a Strwythur MLAB Rhyng-gysylltiadau Cyswllt Lleol a Uniongyrchol

Rhyng-gysylltiadau Cyswllt Lleol a Uniongyrchol

Gall pob LAB yrru 60 o allbynnau ALM allan. Gall is-set o'r rhain yrru mewnbynnau LAB yn uniongyrchol, ond rhaid i unrhyw gysylltiad â rhes neu golofn wahanol ddefnyddio o leiaf un wifren llwybro pwrpas cyffredinol.

Mae'r rhyng-gysylltiad lleol yn gyrru'r mewnbynnau ALM. Mae allbynnau ALM, yn ogystal â rhyng-gysylltiadau colofn a rhes yn gyrru'r rhyng-gysylltiad lleol.

Ffigur 3. Rhyng-gysylltiad Cyswllt Lleol a Uniongyrchol Intel Agilex LAB  Cludo Chain Interconnects

Cludo Chain Interconnects

Mae llwybr cadwyn cario pwrpasol rhwng yr ALMs. Mae dyfeisiau Intel Agilex yn cynnwys strwythur rhyng-gysylltu gwell mewn LABs ar gyfer llwybro cadwyni cario ar gyfer swyddogaethau rhifyddeg effeithlon. Mae'r cysylltiadau ALM-i-ALM hyn yn osgoi'r rhyng-gysylltiad lleol.

Mae cofrestrau Intel Hyperflex yn cael eu hychwanegu at y gadwyn gario i alluogi ail-amseru hyblyg ar draws cadwyn o LABs ac mae Intel Quartus Prime Compiler yn cymryd advan yn awtomatig.tagd o'r adnoddau hyn i wella defnydd a pherfformiad.

Ffigur 4. Cludo Chain Interconnects Arwyddion Rheoli LAB

Arwyddion Rheoli LAB

Mae dwy ffynhonnell gloc ym mhob bloc rheoli LAB, sy'n cynhyrchu dau gloc LAB (LABCLK[1:0]) a dau gloc LAB oedi (LABCLK_Phi1[1:0]) i yrru'r cofrestrau ALM a Hyper-Registers yn y LAB. Mae'r LAB yn cefnogi dau signal galluogi cloc unigryw, yn ogystal â signalau clir ychwanegol, ar gyfer y cofrestrau ALM.

Mae'r clociau rhes LAB [5..0] a rhyng-gysylltiadau lleol LAB yn cynhyrchu'r signalau rheoli LAB-eang. Mae rhwydwaith cloc sgiw isel yn dosbarthu signalau byd-eang i'r clociau rhes [5..0]. Mae'r rhyng-gysylltiad MultiTrack yn cynnwys llinellau llwybro parhaus, wedi'u hoptimeiddio o ran perfformiad, o wahanol hyd a chyflymder a ddefnyddir ar gyfer effeithlonrwydd llwybro. Mae Intel Quartus Prime Compiler yn llwybro llwybrau dylunio hanfodol yn awtomatig ar ryng-gysylltiadau cyflymach i wella perfformiad dylunio a gwneud y gorau o adnoddau'r ddyfais.

Rheolaeth Rhesymeg Clir

Mae signalau ar draws LAB yn rheoli'r rhesymeg ar gyfer signal clir y gofrestr ALM. Mae'r gofrestr ALM yn cefnogi clir cydamserol ac asyncronaidd yn uniongyrchol. Mae pob LAB yn cynnal un signal clir cydamserol a dau signal clir asyncronaidd.

Mae dyfeisiau Intel Agilex yn darparu pin ailosod dyfais gyfan (DEV_CLRn) sy'n ailosod yr holl gofrestrau yn y ddyfais. Gallwch chi alluogi'r pin DEV_CLRn yn y meddalwedd Intel Quartus Prime cyn ei lunio. Mae'r signal ailosod dyfais gyfan yn diystyru'r holl signalau rheoli eraill.

Ffigur 5. Arwyddion Rheoli LAB-Eang Intel Agilex

ALM

Mae'r adrannau canlynol yn ymdrin ag adnoddau ALM, allbwn ALM, a dulliau gweithredu ALM.

Adnoddau ALM

Mae pob ALM yn cynnwys amrywiaeth o adnoddau sy'n seiliedig ar LUT y gellir eu rhannu rhwng dwy LUT addasol cyfun (ALUTs), gwiber lawn dau-did, a phedair cofrestr.

Gyda hyd at wyth mewnbwn ar gyfer y ddau ALUT cyfun, gall un ALM weithredu cyfuniadau amrywiol o ddwy swyddogaeth. Mae'r hyblygrwydd hwn yn caniatáu i ALM fod yn gwbl gydnaws yn ôl â phedair pensaernïaeth LUT mewnbwn. Gall un ALM hefyd weithredu is-set o wyth swyddogaeth fewnbwn.

Mae un ALM yn cynnwys pedair cofrestr rhaglenadwy. Mae gan bob cofrestr y porthladdoedd canlynol:

- Data yn

- Data allan

- Cloc LAB arferol

- Cloc LAB wedi'i ohirio

- Galluogi cloc

- Synchronous clir

- Asynchronous clir

Gall signalau byd-eang, pinnau I/O (GPIO) cyffredinol-bwrpas, neu unrhyw resymeg fewnol yrru'r cloc i alluogi signal, cloc, a signalau rheoli clir asyncronig neu gydamserol o gofrestr ALM. Mae gan y signal galluogi cloc flaenoriaeth dros y signal ailosod cydamserol.

Ar gyfer swyddogaethau cyfunol, mae'r cofrestrau'n cael eu hosgoi ac mae allbwn y tabl edrych (LUT) a'r gwiberod yn gyrru'n uniongyrchol at allbynnau ALM. Mae dau allbwn cyflym ar gael ar gyfer 6 allbwn LUT ac allbynnau 5 LUT gwaelod i osgoi'r mux allbwn a chysylltu â LAB arall ar gyfer addasiad llwybr critigol.

Ffigur 6. Diagram Bloc Lefel Uchel Intel Agilex ALM

Allbwn ALM

Allbwn ALM

Mae'r allbynnau llwybro cyffredinol ym mhob ALM yn gyrru'r adnoddau llwybro lleol, rhes a cholofn. Gall chwe allbwn ALM, gan gynnwys dau lwybr allbwn cyflym, yrru cysylltiadau llwybro colofn, rhes, neu gyswllt uniongyrchol.

Gall allbwn LUT, gwiber neu gofrestr yrru'r allbynnau ALM. Gall y LUT neu'r wiber a'r gofrestr ALM yrru allan o'r ALM ar yr un pryd.

Mae pacio cofrestr yn gwella'r defnydd o ddyfeisiau trwy ganiatáu i gofrestr anghysylltiedig a rhesymeg gyfunol gael eu pacio mewn un ALM. Gall yr ALM hefyd ddileu fersiynau cofrestredig ac anghofrestredig o allbwn LUT neu wiber.

Mae'r ffigur canlynol yn dangos cysylltedd Intel Agilex ALM. Yn y Intel Quartus Prime Resource Property Editor, mae'r cysylltiad ALM cyfan yn cael ei symleiddio. Bydd rhai llwybrau yn cael eu cyfeirio'n fewnol gan feddalwedd Intel Quartus Prime.

Ffigur 7. Manylion Cysylltiad Intel Agilex ALM Dulliau Gweithredu ALM

Dulliau Gweithredu ALM

Mae'r Intel Agilex ALM yn gweithredu mewn unrhyw un o'r dulliau canlynol:

- Modd arferol

- Modd LUT estynedig

- Modd rhifyddol

Modd Arferol

Mae modd arferol yn caniatáu gweithredu dwy swyddogaeth mewn un Intel Agilex ALM, neu un swyddogaeth o hyd at chwe mewnbwn.

Mae hyd at wyth mewnbwn data o'r rhyng-gysylltiad lleol LAB yn fewnbynnau i'r rhesymeg gyfuniadol.

Gall yr ALM gefnogi rhai cyfuniadau o swyddogaethau cwbl annibynnol a chyfuniadau amrywiol o swyddogaethau sydd â mewnbynnau cyffredin.

Mae Intel Quartus Prime Compiler yn dewis y mewnbynnau i'r LUT yn awtomatig. Mae ALMs yn y modd arferol yn cefnogi pacio'r gofrestr.

Mae'r ffigur canlynol yn dangos cyfuniad o wahanol gysylltiadau mewnbwn ar gyfer y modd LUT. Yn eich dyluniad, efallai y bydd meddalwedd Intel Quartus Prime yn aseinio gwahanol enwau mewnbwn wrth lunio.

Ffigur 8. ALM yn y Modd Arferol

Mae cyfuniadau o swyddogaethau gyda llai o fewnbynnau na'r rhai a ddangosir hefyd yn cael eu cefnogi. Am gynample, cyfuniadau o swyddogaethau gyda'r nifer canlynol o fewnbynnau yn cael eu cefnogi.

- 4 a 3

- 3 a 3

- 3 a 2

- 5 a 2

Ar gyfer pacio dwy swyddogaeth 5-mewnbwn i un ALM, rhaid i'r swyddogaethau gael o leiaf ddau fewnbwn cyffredin. Y mewnbynnau cyffredin yw dataa a datab. Mae angen un mewnbwn cyffredin (naill ai dataa neu datab) i gyfuno swyddogaeth 4-mewnbwn gyda swyddogaeth 5-mewnbwn.

Mewn dyfais na ddefnyddir yn aml, gall meddalwedd Intel Quartus Prime weithredu swyddogaethau y gellid eu gosod mewn un ALM mewn ALM ar wahân gan feddalwedd Intel Quartus Prime i gyflawni'r perfformiad gorau posibl. Wrth i ddyfais ddechrau llenwi, mae meddalwedd Intel Quartus Prime yn defnyddio potensial llawn yr Intel Agilex ALM yn awtomatig. Mae Intel Quartus Prime Compiler yn chwilio'n awtomatig am swyddogaethau gan ddefnyddio mewnbynnau cyffredin neu swyddogaethau cwbl annibynnol i'w gosod mewn un ALM i wneud defnydd effeithlon o adnoddau dyfais. Yn ogystal, gallwch reoli'r defnydd o adnoddau â llaw trwy osod aseiniadau lleoliad.

Ffigur 9. Swyddogaeth Modd LUT 6-Mewnbwn yn y Modd Normal

Ffigur 10. Swyddogaeth Modd LUT 3-Mewnbwn yn y Modd Normal

Ffigur 10. Swyddogaeth Modd LUT 3-Mewnbwn yn y Modd Normal

data a data b ar gael ar gyfer pacio cofrestr.  Gallwch chi weithredu unrhyw swyddogaeth mewnbwn tri i chwe gan ddefnyddio'r mewnbynnau canlynol:

Gallwch chi weithredu unrhyw swyddogaeth mewnbwn tri i chwe gan ddefnyddio'r mewnbynnau canlynol:

- datae

- datad0

- datac0

- datac1

- datad1

- dataf

- dataa a datab - lle mae dataa a datab yn cael eu rhannu ar draws y ddau LUT i ddarparu hyblygrwydd i weithredu swyddogaeth wahanol ym mhob LUT.

Mae mewnbynnau dataa a datab yn cefnogi nodwedd pacio'r gofrestr. Os ydych chi'n galluogi nodwedd pacio'r gofrestr, mae mewnbynnau dataa a datab neu naill ai un o'r mewnbynnau yn osgoi'r LUT ac yn bwydo'n uniongyrchol i'r gofrestr, yn dibynnu ar y modd cofrestr llawn a ddefnyddir. Ar gyfer dyfeisiau Intel Agilex, cefnogir y mathau canlynol o foddau cofrestr llawn:

- LUT 5 mewnbwn gydag 1 llwybr cofrestr llawn

- LUT 5 mewnbwn gyda 2 lwybr cofrestr llawn dop

- Dau LUT 3 mewnbwn gyda 2 lwybr cofrestr llawn dop

Mae'r LUT 3-mewnbwn gyda 2 lwybr cofrestr llawn wedi'i ddangos yn y ffigwr Swyddogaeth Modd LUT 3-Mewnbwn yn y Modd Normal. Ar gyfer dyfeisiau Intel Agilex, nid yw'r modd LUT 6-mewnbwn yn cefnogi nodwedd pacio'r gofrestr.

Modd LUT Estynedig

Ffigur 11. Swyddogaethau 8-Mewnbwn a Gefnogir yn y Modd LUT Estynedig

Gellir gweithredu rhai swyddogaethau 8-mewnbwn mewn un ALM gan ddefnyddio'r holl fewnbynnau LUT:

- datae

- datad0

- datac0

- dataa

- datab

- datac1

- datad1

- dataf

Yn y modd LUT estynedig 8-mewnbwn, cefnogir y modd cofrestr wedi'i bacio, ar yr amod bod y gofrestr lawn yn rhannu mewnbwn dataa neu ddatab gyda'r LUT 8-mewnbwn.

Modd Rhifyddol

Mae'r ALM mewn modd rhifyddol yn defnyddio dwy set o ddwy LUT 4 mewnbwn ynghyd â dwy wiber lawn bwrpasol. Mae'r gwiberod pwrpasol yn caniatáu i'r LUTs berfformio rhesymeg cyn-gwiber. Felly, gall pob gwiber ychwanegu allbwn dwy swyddogaeth 4-mewnbwn.

Mae modd rhifyddol hefyd yn cynnig galluogi cloc, galluogi cownter, rheolaeth gydamserol i fyny ac i lawr, rheolaeth adio a thynnu, a chlir cydamserol.

Mae'r opsiynau galluogi clir a chloc yn signalau LAB gyfan sy'n effeithio ar bob cofrestr yn y LAB. Gallwch analluogi neu alluogi'r signalau hyn yn unigol ar gyfer pob pâr o gofrestrau mewn LUT addasol (ALUT). Mae meddalwedd Intel Quartus Prime yn gosod unrhyw gofrestrau nad ydynt yn cael eu defnyddio gan y cownter mewn LABs eraill yn awtomatig.

Ffigur 12. Intel Agilex ALM mewn Modd Rhifyddol

Cadwyn Cario

Cadwyn Cario

Mae'r gadwyn gario yn darparu swyddogaeth cario cyflym rhwng y gwiberod pwrpasol yn y modd rhifyddol.

Mae'r nodwedd cario 2-did dethol mewn dyfeisiau Intel Agilex yn hollti oedi lluosogi cadwyni cario gyda'r ALM. Gall cadwyni cario ddechrau naill ai yn yr ALM cyntaf neu'r chweched ALM mewn LAB. Mae'r signal cario terfynol yn cael ei gyfeirio at ALM, lle caiff ei fwydo i ryng-gysylltiadau lleol, rhes, neu golofn.

Hanes Adolygu Dogfennau ar gyfer Canllaw Defnyddiwr Blociau Array Logic Intel Agilex a Modiwlau Rhesymeg Addasol

| Fersiwn y Ddogfen | Newidiadau |

| 2022.05.24 | Ffigur wedi'i Ddiweddaru: Diagram Bloc Lefel Uchel Intel Agilex ALM. |

| 2019.11.14 | Wedi diweddaru'r disgrifiad yn yr adran Arwyddion Rheoli LAB. |

| 2019.10.01 |

|

| 2019.04.02 | Rhyddhad cychwynnol. |

Intel Gorfforaeth.

Cedwir pob hawl. Mae Intel, logo Intel, a nodau Intel eraill yn nodau masnach Intel Corporation neu ei is-gwmnïau. Mae Intel yn gwarantu perfformiad ei gynhyrchion FPGA a lled-ddargludyddion i fanylebau cyfredol yn unol â gwarant safonol Intel, ond mae'n cadw'r hawl i wneud newidiadau i unrhyw gynhyrchion a gwasanaethau ar unrhyw adeg heb rybudd. Nid yw Intel yn cymryd unrhyw gyfrifoldeb nac atebolrwydd sy'n deillio o gymhwyso neu ddefnyddio unrhyw wybodaeth, cynnyrch neu wasanaeth a ddisgrifir yma ac eithrio fel y cytunwyd yn benodol yn ysgrifenedig gan Intel. Cynghorir cwsmeriaid Intel i gael y fersiwn ddiweddaraf o fanylebau dyfeisiau cyn dibynnu ar unrhyw wybodaeth gyhoeddedig a chyn archebu cynhyrchion neu wasanaethau.

*Gellir hawlio enwau a brandiau eraill fel eiddo eraill.

ISO

9001:2015

Wedi cofrestru

Dogfennau / Adnoddau

|

Intel Blociau Array Logic Agilex a Modiwlau Rhesymeg Addasol [pdfCanllaw Defnyddiwr Blociau Arae Rhesymeg Agilex a Modiwlau Rhesymeg Addasol, Agilex, Blociau Arae Rhesymeg a Modiwlau Rhesymeg Addasol, Blociau Arae a Modiwlau Rhesymeg Addasol, Modiwlau Rhesymeg Addasol, Modiwlau Rhesymeg |