樹莓派 SC1631 樹莓派微控制器

產品規格

- 型號:RP2350

- 封裝:QFN-60

- 內部快閃記憶體:無

- 卷tage 穩壓器:片上開關穩壓器

- 穩壓器接腳:5 個(3.3V 輸入、1.1V 輸出、VREG_AVDD、VREG_LX、VREG_PGND)

產品使用說明

- 第一章:簡介

- 與 RP2350 系列相比,RP2040 系列提供不同的封裝選項。 RP2350A 和 RP2354A 分別採用不含和不帶內部快閃記憶體的 QFN-60 封裝,而 RP2354B 和 RP2350B 則採用有和沒有快閃記憶體的 QFN-80 封裝。

- 第2章:力量

RP2350系列具有新的片上開關卷tag有五個引腳的調節器。此穩壓器需要外部組件才能運行,但與 RP2040 系列中的線性穩壓器相比,可在較高負載電流下提供更高的電源效率。請注意為類比電路供電的 VREG_AVDD 接腳中的雜訊敏感度。

常見問題 (FAQ)

- Q:RP2350A 和 RP2350B 的主要差異是什麼?

答:主要差異在於內部快閃記憶體的存在。 RP2350A 沒有內部閃存,而 RP2350B 有。 - Q:vol有多少針tagRP2350系列中的e穩壓器有哪些?

答:卷tagRP2350 系列中的調節器有五個引腳。

使用 RP2350 進行硬體設計 使用 RP2350 微控制器建構電路板和產品

版畫

- © 2023-2024 樹莓派股份有限公司

- 本文檔根據 Creative Commons Attribution-NoDerivatives 4.0 International (CC BY-ND) 授權。建置日期:2024-08-08 建置版本:c0acc5b-clean

- 法律免責聲明

- 不時修改的 RASPBERRY PI 產品(包括資料表)的技術和可靠性資料(「資源」)由 RASPBERRY PI LTD(「RPL」)「按原樣」提供,並提供任何明示或暗示的保證,包括但不限於TO,適銷性和特定用途適用性的默示保證不予承擔。在適用法律允許的最大範圍內,在任何情況下,RPL 均不對任何直接、間接、附帶、特殊、懲戒性或後果性損害(包括但不限於購買替代商品或服務;使用、資料遺失)承擔責任。這種可能性此類損害。

- RPL 保留隨時對資源或其中所述的任何產品進行任何增強、改進、更正或任何其他修改的權利,恕不另行通知。

這些資源適用於具有適當設計知識水準的熟練使用者。使用者對資源的選擇和使用以及其中描述的產品的任何應用承擔全部責任。使用者同意賠償並確保 RPL 免受因使用資源而產生的所有責任、費用、損害或其他損失。 - RPL 授予使用者僅將資源與 Raspberry Pi 產品結合使用的權限。禁止將資源用於任何其他用途。未授予任何其他 RPL 或其他第三方智慧財產權任何授權。

- 高風險活動。 Raspberry Pi 產品並非設計、製造或設計用於需要故障安全性能的危險環境,例如核設施、飛機導航或通訊系統、空中交通管制、武器系統或安全關鍵應用(包括生命維持)的運作系統和其他醫療設備),其中產品故障可能直接導致死亡、人身傷害或嚴重的身體或環境損害(「高風險活動」)。 RPL 特別聲明不對高風險活動的適用性做出任何明示或暗示的保證,也不承擔在高風險活動中使用或包含 Raspberry Pi 產品的任何責任。

- Raspberry Pi 產品是依照 RPL 的標準條款提供。 RPL 提供的資源不會擴展或以其他方式修改 RPL 的標準條款,包括但不限於其中表達的免責聲明和保證。

第一章簡介

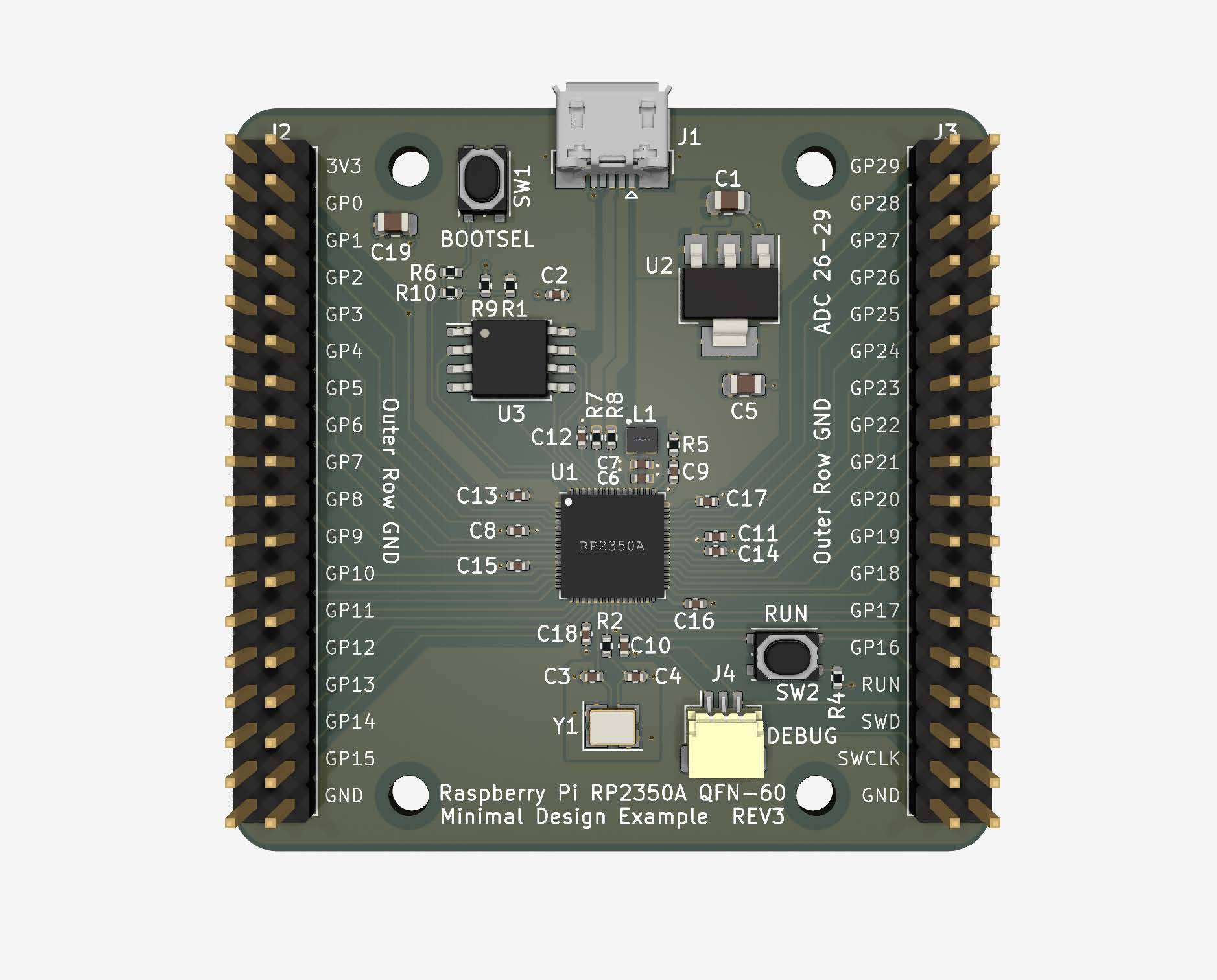

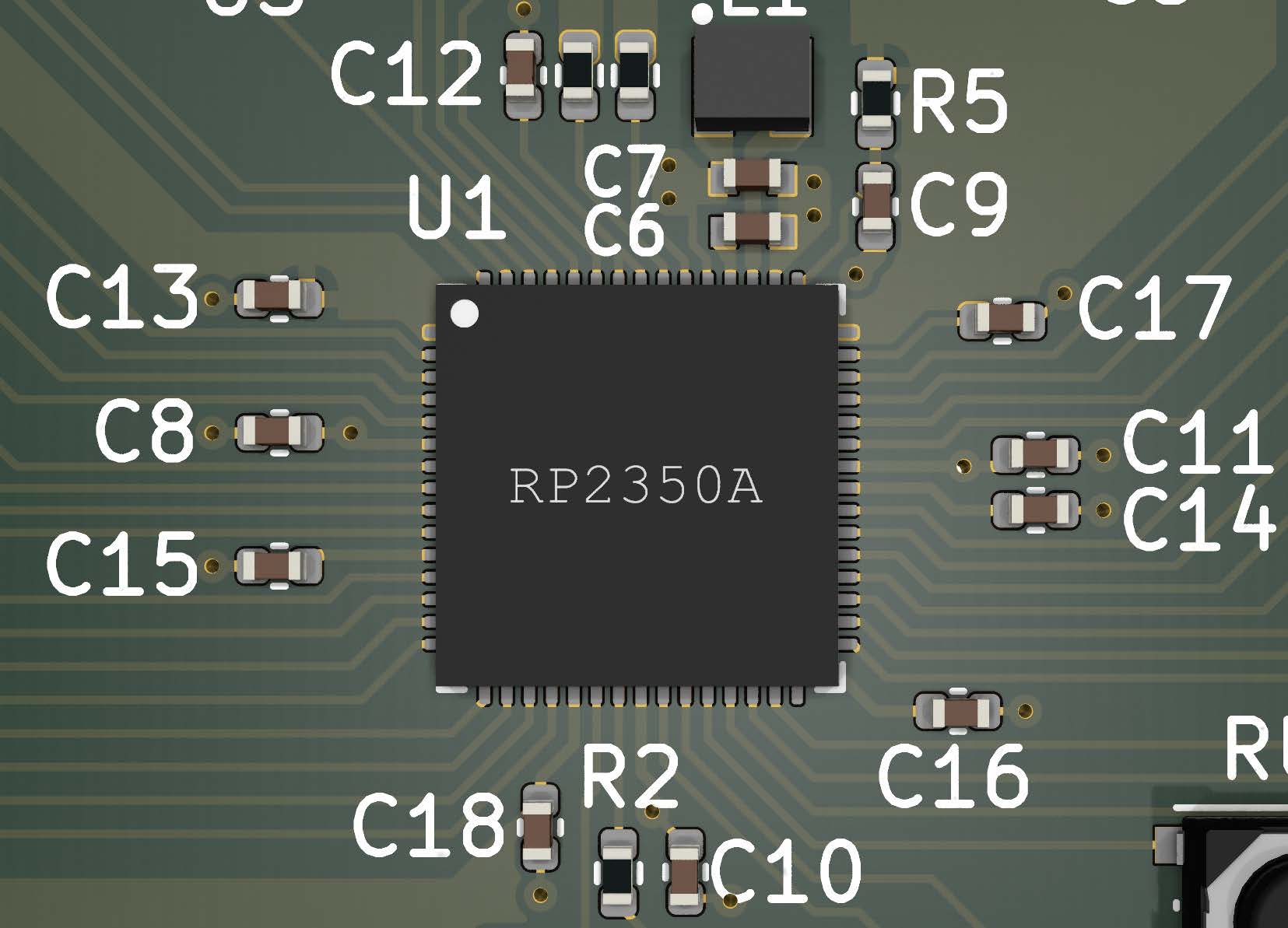

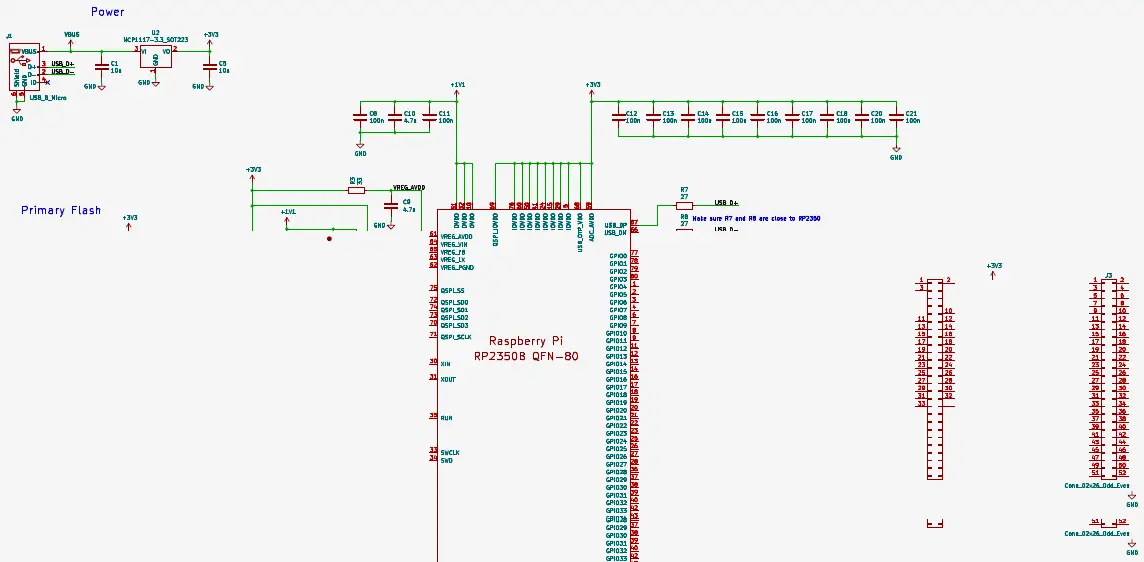

圖 1. RP3A Minimal 設計前的 KiCad 2350D 渲染ample

當我們第一次推出 Raspberry Pi RP2040 時,我們也發布了「Minimal」設計 examp文件和隨附的指南《使用 RP2040 進行硬體設計》有望解釋如何在簡單的電路板中使用 RP2040,以及為什麼選擇各種組件。隨著 RP235x 系列的到來,是時候重新審視最初的 RP2040 Minimal 設計,並對其進行更新以適應新功能以及每個封裝變體; RP2350A 採用 QFN-60 封裝,RP2350B 採用 QFN-80 封裝。同樣,這些設計採用 Kicad (7.0) 格式,並且可以下載 (https://datasheets.raspberrypi.com/rp2350/Minimal-KiCAD.zip).

最小董事會

最初的 Minimal 板試圖提供一個簡單的參考設計,使用運行 RP2040 所需的最少外部組件,並且仍然暴露和可存取所有 IO。它主要由電源(5V 至 3.3V 線性穩壓器)、晶體振盪器、快閃記憶體和 IO 連接(微型 USB 插座和 GPIO 接頭)組成。新的 RP235x 系列 Minimal 板基本上相同,但由於新硬體而需要進行一些更改。除此之外,儘管有點違背設計的簡約本質,我還是添加了幾個用於bootsel 和run 的按鈕,以及一個單獨的SWD 標頭,這應該意味著這次的調試體驗徹底不那麼令人沮喪。嚴格來說,設計並不需要這些按鈕,訊號在標頭上仍然可用,如果您特別注重成本或空間,或者有受虐傾向,則可以省略它們。

RP2040 與 RP235x 系列

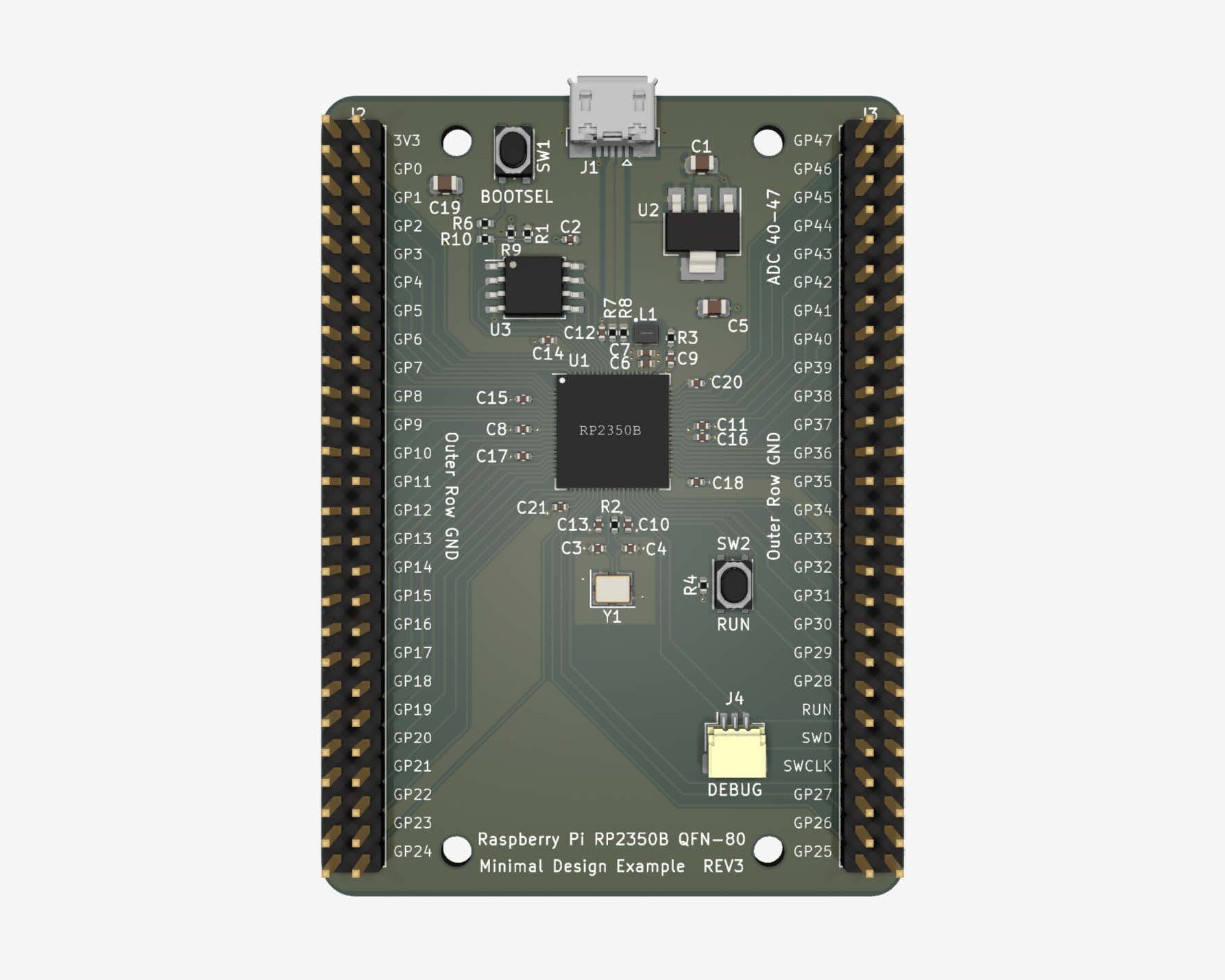

最明顯的變化是在包裝上。 RP2040 是 7x7mm QFN-56,而 RP235x 系列目前有四個不同的成員。有兩個裝置共用相同的 QFN-60 封裝; RP2350A 不包含內部快閃記憶體,RP2354A 包含內部快閃記憶體。同樣,QFN-80 也有兩種: RP2354B 附閃光燈,RP2350B 不含閃光燈。 QFN-60 裝置和原始 RP2040 具有共同的特點tage.

它們每個都有 30 個 GPIO,其中四個也連接到 ADC,尺寸為 7x7mm。儘管如此,RP2350A 並不是 RP2040 的直接替代品,因為兩者的引腳數量不同。相比之下,QFN-80 晶片現在有 48 個 GPIO,其中 60 個現在具有 ADC 功能。因此,我們現在有兩個 Minimal 板;一種用於80 引腳裝置,一種用於2350 引腳。閃存裝置(RP2354) 一起使用內存,甚至將其用作輔助閃存設備(稍後會詳細介紹)。這兩個板之間幾乎沒有什麼區別,除了 QFN-80 版本具有更長的排針以容納額外的 GPIO,因此板更大。

除了封裝之外,RP235x系列和RP2040之間最大的板級差異是電源。 RP235x 系列具有一些新的電源引腳和不同的內部穩壓器。 RP100 的 2040mA 線性穩壓器已被 200mA 開關穩壓器取代,因此,它需要一些非常特殊的電路,並且在佈局上也需要非常小心。強烈建議您密切注意我們的佈局和組件選擇;我們已經經歷了必須對設計進行多次迭代的痛苦,所以希望您不必這樣做。

圖 2. RP3B Minimal 設計前的 KiCad 2350D 渲染ample

設計

Minimal設計的意圖amp我們的目標是使用 RP235x 系列創建一對簡單的板,該板應該成本低廉且易於製造,而無需使用不必要的外來 PCB 技術。因此,Minimal 板採用 2 層設計,使用常見的組件,並且全部安裝在板的頂部。雖然使用大型、易於手工焊接的元件固然很好,但 QFN 晶片的小間距 (0.4mm) 意味著,如果要使用所有 GPIO,則不可避免地要使用一些 0402(1005 公制)被動元件。雖然使用像樣的烙鐵手工焊接 0402 元件並不太具有挑戰性,但在沒有專業設備的情況下幾乎不可能焊接 QFN。

在接下來的幾節中,我將嘗試解釋附加電路的用途,並希望解釋我們如何做出我們所做的選擇。由於我實際上要討論兩種獨立的設計,每種設計對應一種封裝尺寸,因此我盡力保持事情簡單。盡可能地,兩個板的所有組件參考都是相同的,因此如果我引用 U1、R1 等,那麼它與兩個板同樣相關。明顯的例外是,當組件僅位於其中一塊板上時(在所有情況下,這將位於較大的 80 引腳型號上),則相關組件將僅位於 QFN-80 設計上;對於前任ample,R13只出現在該板上。

第 2 章 權力

這次 RP235x 系列和 RP2040 的電源有所不同,儘管在最簡單的配置中,它仍然需要兩個電源:3.3V 和 1.1V。 RP235x 系列同時更耗電,因為它具有更高的性能,並且比其前身更節儉(處於低功耗狀態時),因此 RP2040 上的線性穩壓器已升級為開關穩壓器。這使我們能夠在更高電流下實現更高的電源效率(與先前的 200mA 相比,高達 100mA)。

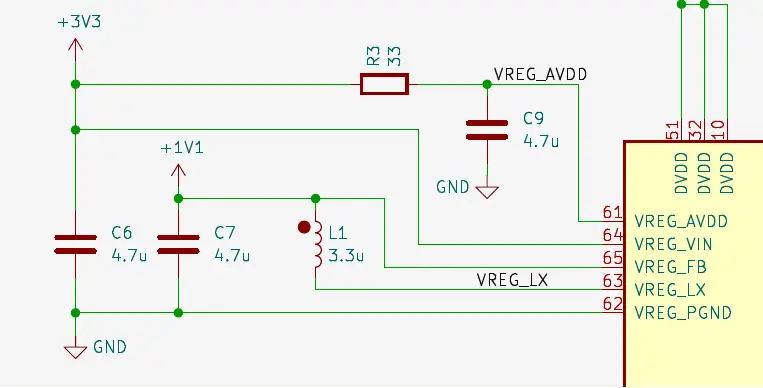

新片上卷tag調節器

圖 3. 顯示內部穩壓器電路的原理圖部分

RP2040 的線性穩壓器有兩個引腳,一個 3.3V 輸入,一個 1.1V 輸出,為晶片上的 DVDD 供電。這次,RP235x系列的穩壓器有五個引腳,需要一些外部元件才能運作。雖然這在可用性方面似乎有點倒退,但開關穩壓器具有優勢tage 在較高負載電流下具有更高的功率效率。

顧名思義,穩壓器快速開啟和關閉連接 3.3V 輸入電壓的內部電晶體tage (VREG_VIN) 連接到 VREG_LX 引腳,並在電感 (L1) 和輸出電容 (C7) 的幫助下,可以產生直流輸出電壓tage 已從輸入降壓。 VREG_FB 接腳監控輸出電壓tage、調整開關週期的開/關比,以確保所需的電壓tage 被維持。由於大電流從 VREG_VIN 切換到 VREG_LX,因此需要一個靠近輸入的大電容器 (C6),因此我們不會過度幹擾 3.3V 電源。說到這些大開關電流,穩壓器也帶著自己的接地迴路連接 VREG_PGND。與 VREG_VIN 和 VREG_LX 類似,此連接的佈局至關重要,雖然 VREG_PGND 必須連接到主 GND,但必須以所有大開關電流直接返回到 PGND 引腳的方式完成,而不會幹擾其餘的GND 太多。

最後一個引腳是 VREG_AVDD,它為穩壓器內的類比電路供電,並且對雜訊非常敏感。

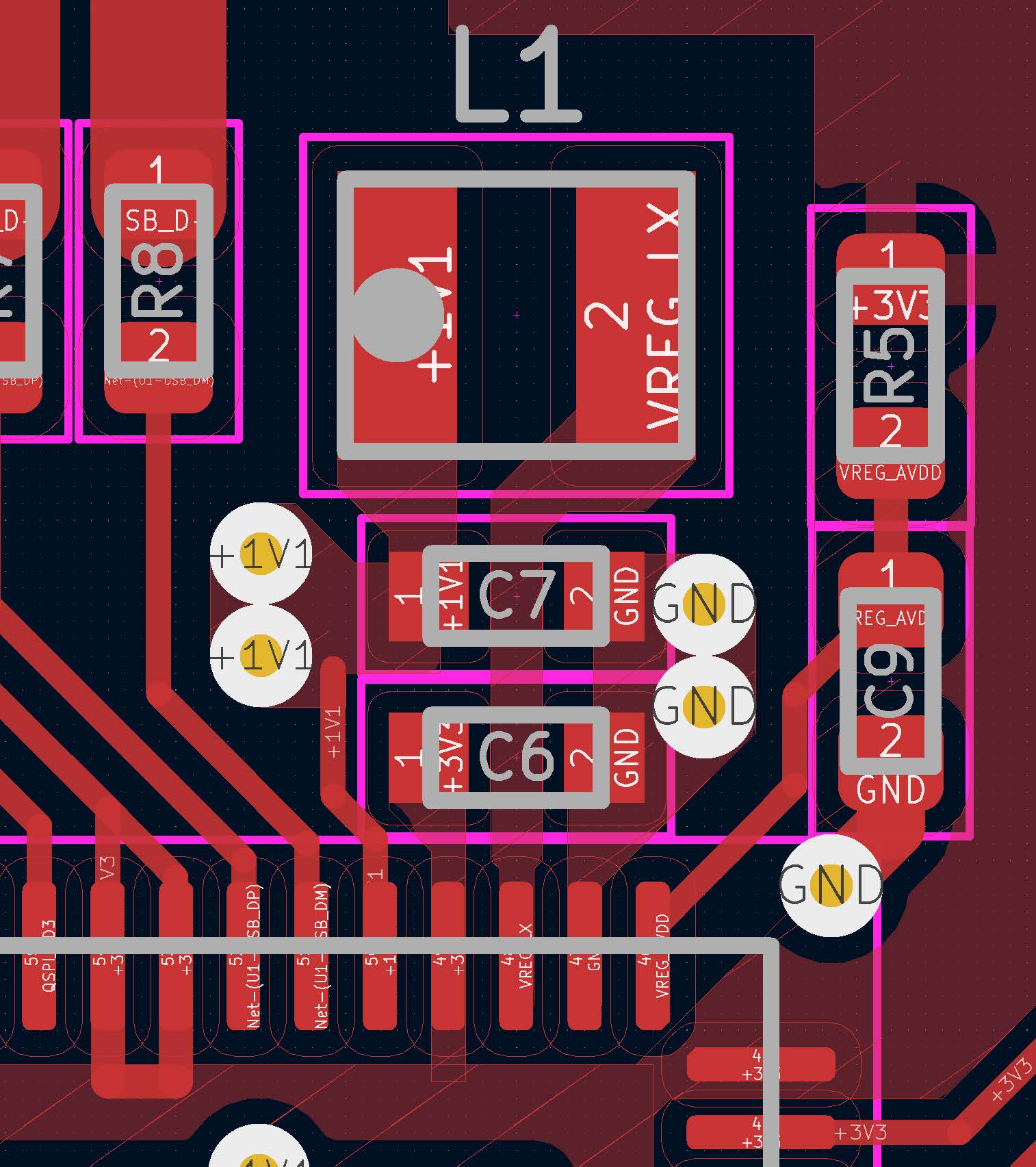

圖 4. 顯示穩壓器 PCB 佈局的示意圖

- 最小電路板上的調節器佈局與 Raspberry Pi Pico 2 的佈局非常相似。雖然您可以以各種不同的方式放置這些組件,但仍然可以讓調節器「工作」(即產生輸出量)tage 大致在正確的水平,足以讓它運行程式碼),我們發現我們的調節器需要以完全正確的方式對待以使其保持快樂,而快樂,我的意思是產生正確的輸出量tage 在一系列負載電流條件下。

- 在對此進行實驗時,我們有些失望地被提醒,不方便的物理世界不能總是被忽視。作為工程師,我們很大程度上嘗試並做到了這一點;簡化元件,忽略(通常)無關緊要的物理屬性,而是專注於我們感興趣的屬性。amp例如,一個簡單的電阻器不僅具有電阻,還具有電感等。的,以及電流的流動方向。我們也被提醒,「完全」屏蔽電感器並不意味著您所認為的那樣。磁場大幅衰減,但仍有部分逃逸。我們發現,如果電感器是“正確的方式”,則調節器的性能可以大大提高。

- 事實證明,從「錯誤方向」電感器發出的磁場會幹擾穩壓器輸出電容器 (C7),擾亂 RP2350 內的控制電路。如果電感器處於正確的方向,並且此處使用了精確的佈局和元件選擇,那麼這個問題就會消失。毫無疑問,還會有其他佈局、組件等可以與任何方向的電感器配合使用,但它們很可能會為此使用更多的 PCB 空間。我們提供了這個建議的佈局,以節省人們開發和完善這個緊湊且性能良好的解決方案所花費的大量工程時間。

- 更重要的是,我們甚至要說,如果您選擇不使用我們的前任ample,那麼您需要自行承擔風險。就像我們已經對 RP2040 和晶體電路所做的那樣,我們堅持(好吧,強烈建議)您使用特定的部件(我們將在本文檔的晶體部分再次這樣做)。

- 這些小型電感器的方向性幾乎普遍被忽略,線圈繞組的方向無法推斷,也沿著組件卷隨機分佈。通常可以發現較大的電感器外殼尺寸上有極性標記,但是我們在我們選擇的 0806(2016 公制)外殼尺寸中找不到合適的極性標記。為此,我們與 Abracon 合作生產了一個 3.3μH 零件,帶有一個點來指示極性,重要的是,它們都以相同的方式排列在捲軸上。發行商將(或很快)向公眾提供 TBD。如前所述,VREG_AVDD 電源對雜訊非常敏感,因此需要進行濾波。我們發現,由於 VREG_AVDD 僅消耗 200μA 左右的電流,因此 33Ω 和 4.7μF 的 RC 濾波器就足夠了。

- 因此,回顧一下,所使用的組件將是…

- C6、C7 和 C9 – 4.7μF(0402、1005 公制)

- L1 – Abracon 待定(0806、2016 公制)

- R3 – 33Ω(0402、1005 公制)

- RP2350 資料表對穩壓器佈局建議進行了更詳細的討論,請參閱外部元件和 PCB 佈局要求。

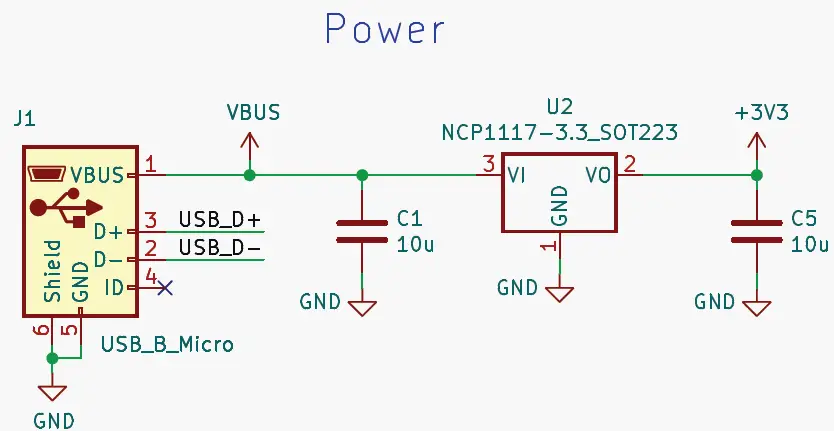

輸入電源

此設計的輸入電源連接是透過 Micro-USB 連接器(圖 5 中標記為 J1)的 5V VBUS 引腳進行的。這是為電子設備供電的常見方法,在這裡很有意義,因為 RP2350 具有 USB 功能,我們將其連接到該連接器的資料引腳。由於此設計僅需要 3.3V(1.1V 電源來自內部),因此我們需要降低傳入的 5V USB 電源,在本例中,使用另一個外部電壓tage 穩壓器,在本例中為線性穩壓器(又稱低壓差穩壓器,或 LDO)。之前曾讚揚過使用高效能開關穩壓器的優點,在這裡使用它也可能是明智的選擇,但我選擇了簡單性。首先,使用 LDO 幾乎總是更容易。無需計算即可確定應使用多大尺寸的電感器或輸出電容器有多大,而且佈局通常也更加簡單。其次,節省每一滴電量並不是這裡的目標;如果是的話,我會認真考慮使用開關穩壓器,你可以找到一個前任amp我在 Raspberry Pi Pico 2 上這樣做了。這裡選擇的 NCP2040 (U1117) 具有 2V 的固定輸出,用途廣泛,並且可以提供高達 3.3A 的電流,這對於大多數設計來說足夠了。在查看 NCP1 的資料表後,我們發現該元件的輸入端需要一個 1117μF 電容器,輸出端需要一個 10μF 電容器(C1 和 C5)。

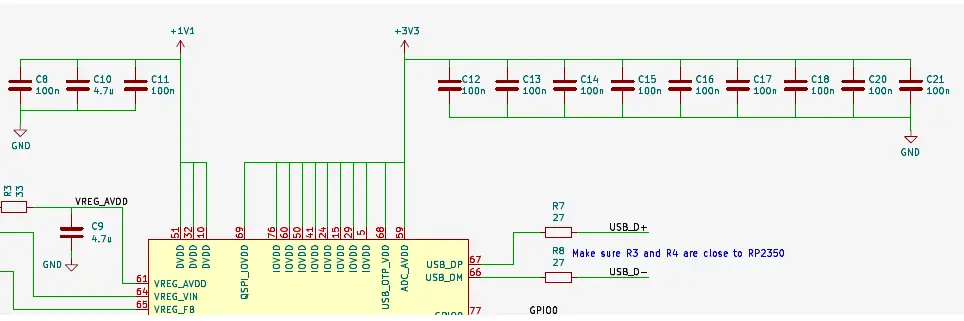

去耦電容

圖 6. 顯示 RP2350 電源輸入、電壓的原理圖部分tage 調節器和去耦電容器

電源設計的另一個方面是 RP2350 所需的去耦電容器。它們提供了兩個基本功能。首先,它們濾除電源噪聲,其次,提供本地電荷供應,供 RP2350 內部電路在短時間內使用。這可以防止卷tag當當前需求突然增加時,附近的水位不會下降太多。因此,將去耦裝置靠近電源引腳非常重要。通常,我們建議每個電源引腳使用 100nF 電容器,但是,在某些情況下我們會偏離此規則。

圖 7. 顯示 RP2350 佈線和去耦的佈局部分

- 首先,為了能夠有足夠的空間讓所有晶片引腳能夠從裝置中引出,我們必須在可以使用的去耦電容器的數量上做出妥協。在此設計中,RP53A 的引腳 54 和 2350(RP68B 的引腳 69 和 2350)共享一個電容器(圖 12 和圖 7 中的 C6),因為裝置那一側沒有太多空間,且組件調節器的佈局優先。

- 如果我們使用更複雜/昂貴的技術,例如更小的元件,或者在頂部和底部都有元件的四層 PCB,這種空間不足的問題可以在一定程度上得到解決。這是一種設計權衡;我們降低了複雜性和成本,但代價是去耦電容較小,而且電容器距離晶片的距離比最佳值稍遠(這會增加電感)。這可能會限制設計運行的最大速度,因為體積tag電源可能會變得太吵並且低於允許的最小音量tage;但對於大多數應用程式來說,這種權衡應該是可以接受的。

- 與 100nF 規則的另一個偏差是我們可以進一步提高音量tage 調節器性能;我們建議 C4.7 使用 10μF,它放置在晶片的另一側,遠離穩壓器。

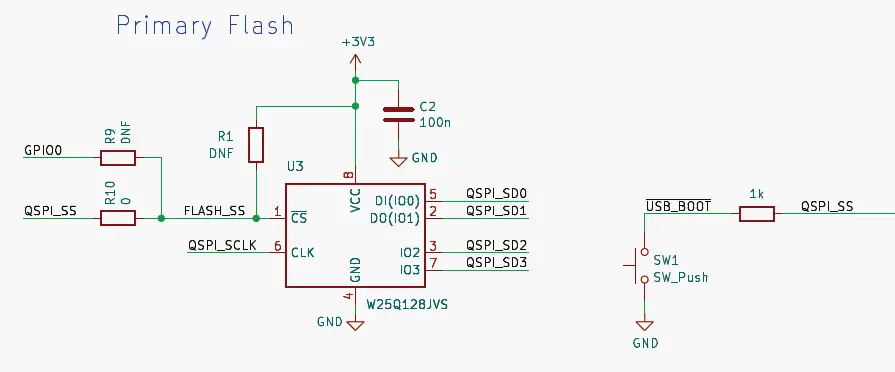

第 3 章快閃記憶體

主閃光燈

圖 8. 顯示主快閃記憶體和 USB_BOOT 電路的原理圖部分

- 為了能夠儲存RP2350可以啟動和運行的程式碼,我們需要使用閃存,特別是quad SPI快閃記憶體。這裡選擇的裝置是 W25Q128JVS 裝置(圖 3 中的 U8),它是 128Mbit 晶片 (16MB)。這是RP2350可以支援的最大記憶體大小。如果您的特定應用程式不需要那麼多儲存空間,則可以使用更小、更便宜的記憶體。

- 由於此資料匯流排的頻率相當高且經常使用,因此 RP2350 的 QSPI 引腳應直接連接到快閃記憶體,使用短連接來保持訊號完整性,並減少周圍電路中的串擾。串擾是指一個電路網路上的訊號可能造成不必要的電壓的情況tages 在相鄰電路上,可能會導致錯誤發生。

- QSPI_SS 訊號是一種特殊情況。它直接連接到閃光燈,但它還有兩個電阻器(好吧,四個,但我稍後會談到)連接到它。第一個 (R1) 是 3.3V 電源的上拉電阻。快閃記憶體要求片選輸入具有相同的容量tag當裝置上電時,e 作為其自己的 3.3V 電源引腳,否則,它無法正常工作。當 RP2350 上電時,其 QSPI_SS 引腳將自動預設為上拉,但在開啟期間有一小段時間無法保證 QSPI_SS 引腳的狀態。增加上拉電阻可確保始終滿足此要求。 R1 在原理圖上被標記為 DNF(不適合),因為我們發現對於這個特定的閃存裝置,外部上拉是不必要的。然而,如果使用不同的閃光燈,能夠在此處插入 10kΩ 電阻可能會變得非常重要,因此將其納入以防萬一。

- 第二個電阻器 (R6) 是 1kΩ 電阻器,連接到標示「USB_BOOT」的按鈕 (SW1)。這是因為 QSPI_SS 引腳被用作「引導帶」; RP2350 在啟動序列期間檢查此 I/O 的值,如果發現為邏輯 0,則 RP2350 恢復到 BOOTSEL 模式,其中 RP2350 將自身呈現為 USB 大容量存儲設備,並且可以直接複製代碼到它。如果我們簡單地按下按鈕,將 QSPI_SS 引腳拉至地,並且如果裝置隨後被重置(例如切換 RUN 引腳),RP2350 將在 BOOTSEL 模式下重新啟動,而不是嘗試執行快閃記憶體的內容。這些電阻器 R2 和 R6(還有 R9 和 R10)應放置在靠近快閃記憶體晶片的位置,這樣我們就可以避免可能影響訊號的額外銅軌長度。

- 以上所有內容都特別適用於沒有內部快閃記憶體的 RP2350。當然,RP2354 裝置具有內部 2MB 閃存,因此不需要外部 U3 記憶體,因此可以安全地從原理圖中刪除 U3,或者乾脆不填充。在這兩種情況下,我們仍然希望將 USB_BOOT 開關保持連接到 QSPI_SS,以便我們仍然可以進入 USB 引導模式。

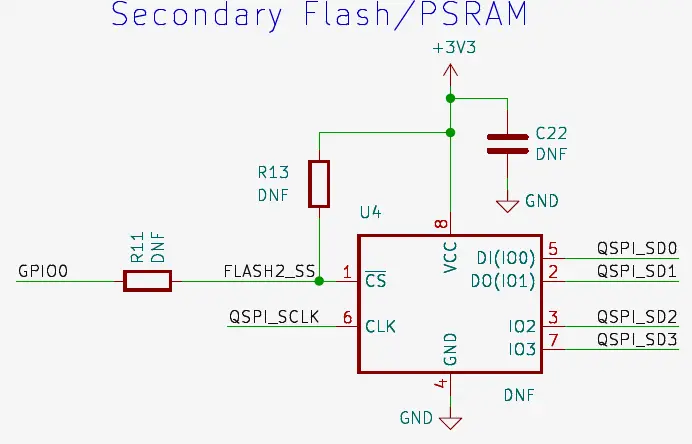

輔助快閃記憶體或 PSRAM

- RP235x 系列現在支援使用相同 QSPI 引腳的第二個記憶體元件,並透過 GPIO 提供額外的晶片選擇。因此,如果我們使用 RP2354(具有內部快閃記憶體),那麼我們可以使用 U3 作為輔助閃存,甚至用 PSRAM 裝置取代它。為此,我們需要斷開 QSPI_SS 與 U3 的連接,並將其連接到適當的 GPIO。最近的能夠作為片選 (XIP_CS1n) 的 GPIO 是 GPIO0,因此透過從 R0 中移除 10Ω,並將其安裝到 R9,我們現在除了可以存取片上快閃記憶體之外,還可以存取 U3。為了充分發揮優勢tag在這項功能中,我們有兩個外部儲存設備,以便無快閃 RP2350 元件可以受益,兩個 Minimal 板中較大的一個(對於 RP2350B)包括用於附加記憶體晶片的可選佔用空間 (U4)。

圖 9. 顯示選購輔助儲存設備的示意圖

為了能夠使用該設備,顯然必須填充它,以及 R11 (0Ω) 和 R13 (10KΩ)。新增 R11 將 GPIO0(XIP_CS1n 訊號)連接到第二個記憶體的片選。這次肯定需要片選引腳上的上拉,因為 GPIO0 的預設狀態是在上電時拉低,這會導致我們的快閃記憶體裝置發生故障。還需要 C22 為 U4 提供本地電源去耦。

支援的快閃記憶體晶片

初始閃存探針序列,由底部用來提取第二個 stage 來自閃存,使用 03h 串行讀取命令,具有 24 位元尋址和大約 1MHz 的串行時脈。它反覆循環遍歷時脈極性和時鐘相位的四種組合,尋找有效的秒數tage CRC32 校驗和。

作為第二個tag然後,可以使用相同的 03h 串行讀取命令自由配置就地執行,RP2350 可以使用任何支援 03 位元尋址的 24h 串行讀取的晶片執行緩存閃存就地執行,其中包括大多數 25 系列閃存裝置。該SDK提供了一個examp勒秒tage 對於 CPOL=0 CPHA=0,在 https://github.com/raspberrypi/pico-sdk/blob/master/src/rp2350/boot_stage2/boot2_generic_03h.S。為了支援使用底部例程進行快閃記憶體編程,元件還必須回應以下命令:

- 02h 256位元組頁程序

- 05h 狀態暫存器讀取

- 06h 設定寫入使能鎖存器

- 20h 4kB 磁區擦除

RP2350也支援多種雙SPI和QSPI存取模式。對於前amp樂, https://github.com/raspberrypi/pico-sdk/blob/master/src/rp2350/boot_stage2/boot2_w25q080.S 將 Winbond W25Q 系列裝置配置為四 IO 連續讀取模式,其中 RP2350 傳送四 IO 位址(無指令前綴),快閃記憶體以四 IO 資料回應。

對於快閃記憶體 XIP 模式需要注意一些,在這種模式下,快閃記憶體裝置會停止回應標準串列指令,例如上面提到的 Winbond 連續讀取模式。當 RP2350 重置但快閃記憶體裝置未重新啟動時,這可能會導致問題,因為快閃記憶體將不會回應 bootrom 的快閃記憶體探測序列。在發出 03h 串列讀取之前,bootrom 始終發出以下固定序列,這是在一系列快閃記憶體裝置上停止 XIP 的盡力而為的序列:

- CSn=1,IO[3:0]=4'b0000(透過下拉以避免爭用),發出×32時鐘

- CSn=0,IO[3:0]=4'b1111(透過上拉避免爭用),發出×32時鐘

- CSn=1

- CSn=0,MOSI=1'b1(驅動為低阻態,所有其他 I/O 為高阻態),發出 ×16 個時鐘

如果您選擇的裝置在連續讀取模式下未回應此序列,則必須將其保持在每次傳輸以序列指令為前綴的狀態,否則 RP2350 將無法在內部重設後復原。

有關 QSPI 的更多詳細信息,請參閱 RP2350 資料表中的 QSPI 記憶體介面 (QMI)。

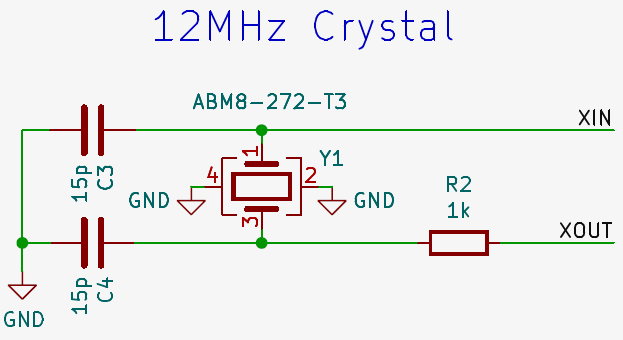

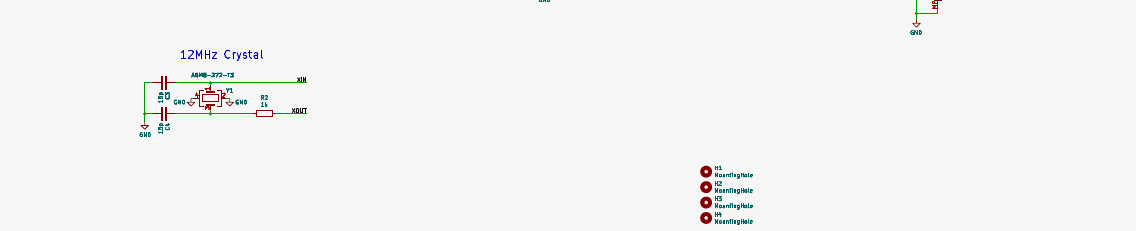

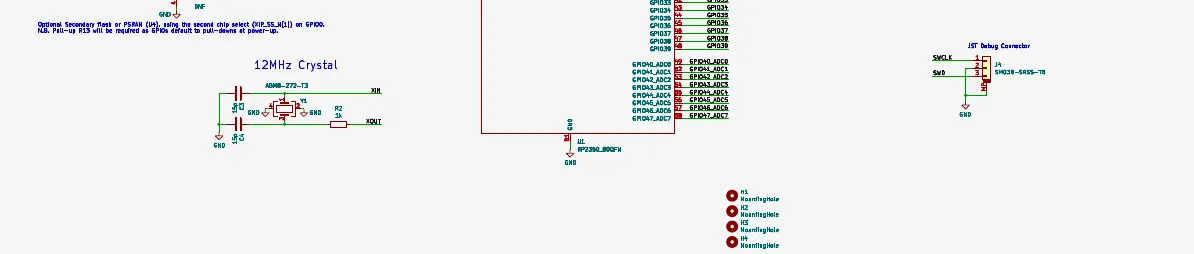

第 4 章晶體振盪器

圖 10. 顯示晶體振盪器和負載電容器的原理圖部分

- 嚴格來說,RP2350實際上不需要外部時鐘來源,因為它有自己的內部振盪器。然而,由於此內部振盪器的頻率沒有很好地定義或控制,晶片與晶片之間以及電源電壓不同,頻率也不同。tages 和溫度,建議使用穩定的外部頻率源。如果沒有外部頻率源,依賴精確頻率的應用是不可能的,USB 是主要的選擇amp勒。

- 提供外部頻率來源可以透過以下兩種方式之一完成:透過提供具有 CMOS 輸出的時脈源(IOVDD vol 的方波)tage) 插入 XIN 接腳,或使用連接在 XIN 接腳之間的 12MHz 晶振

- XIN 和 XOUT。使用晶體是這裡的首選,因為它們相對便宜且非常準確。

- 本設計選擇的晶體是 ABM8-272-T3(圖 1 中的 Y10)。這與 Raspberry Pi Pico 和 Raspberry Pi Pico 12 上使用的相同 2MHz 晶體。該晶體具有 30ppm 的頻率容差,對於大多數應用來說應該足夠了。除了+/-30ppm 的頻率容差之外,它還具有 50Ω 的最大 ESR 和 10pF 的負載電容,這兩者都與隨附組件的選擇有關。

- 為了使晶體以所需頻率振盪,製造商指定了所需的負載電容,在本例中為 10pF。此負載電容是透過放置兩個等值的電容器來實現的,每個電容器位於晶體接地的每一側(C3 和 C4)。從水晶的角度來說 view,這些電容器串聯在其兩個端子之間。基本電路理論告訴我們,它們組合起來得到的電容為(C3*C4)/(C3+C4),而當C3=C4時,它就是C3/2。在這個前ample,我們使用了 15pF 電容器,因此串聯組合為 7.5pF。除了這種有意的負載電容之外,我們還必須為無意的額外電容或寄生電容添加一個值,這些電容是從 RP2350 的 PCB 走線以及 XIN 和 XOUT 引腳獲得的。我們假設其值為 3pF,並且由於該電容與 C3 和 C4 並聯,因此我們只需將其相加即可得到 10.5pF 的總負載電容,這足夠接近 10pF 的目標。正如您所看到的,PCB 走線的寄生電容是一個因素,因此我們需要將它們保持在較小的水平,這樣我們就不會擾亂晶體並阻止其按預期振盪。嘗試使佈局盡可能短。

- 第二個考慮因素是晶體的最大 ESR(等效串聯電阻)。我們選擇了最大 50Ω 的裝置,因為我們發現該裝置與 1kΩ 串聯電阻 (R2) 一起使用時可以很好地防止晶體過度驅動和損壞電平為3.3V。但是,如果 IOVDD 小於 3.3V,則 XIN/XOUT 接腳的驅動電流會減小,您會發現 amp晶體的振幅較低,甚至可能根本不振盪。在這種情況下,需要使用較小值的串聯電阻。與此處顯示的晶體電路的任何偏差,或者IOVDD 電平不是3.3V,都需要進行大量測試,以確保晶體在所有條件下都能振盪,並足夠快地啟動,以免給您的應用帶來問題。

推薦水晶

- 對於使用 RP2350 的原始設計,我們建議使用 Abracon ABM8-272-T3。對於前ample,除了最小的設計example,請參閱 Raspberry Pi Pico 2 資料表附錄 B 中的 Pico 2 板原理圖和 Pico 2 設計 files.

- 為了在典型工作溫度範圍內獲得最佳性能和穩定性,請使用 Abracon ABM8-272-T3。您可以直接從 Abracon 或授權經銷商購買 ABM8-272-T3。 Pico 2 專門針對 ABM8-272-T3 進行了調整,其規格如下:

- 即使您使用具有相似規格的晶體,您也需要在一定溫度範圍內測試電路以確保穩定性。

- 晶體振盪器由 IOVDD 電壓供電tage.因此,Abracon 晶體和那個特殊的 damp荷蘭國際集團電阻器被調整為3.3V操作。如果您使用不同的 IO 卷tage,您將需要重新調整。

- 晶體參數的任何變化都會導致連接到晶體電路的任何組件不穩定。

- 如果您無法直接從 Abracon 或經銷商處購買建議的晶體,請聯絡 applications@raspberrypi.com.

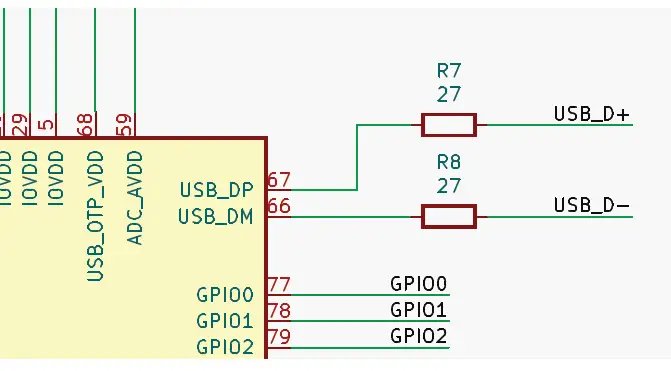

第 5 章 IO

USB

圖 11. 顯示 RP2350 的 USB 接腳和串聯終端的原理圖部分

- RP2350 提供兩個引腳用於全速 (FS) 或低速 (LS) USB,可作為主機或設備,具體取決於所使用的軟體。正如我們已經討論過的,RP2350 也可以作為 USB 海量儲存裝置啟動,因此將這些引腳連接到 USB 連接器(圖 1 中的 J5)是有意義的。 RP2350 上的 USB_DP 和 USB_DM 引腳不需要任何額外的上拉或下拉(需要指示速度、FS 或 LS,或者是主機還是裝置),因為它們內建在 I/O 中。然而,這些 I/O 確實需要靠近晶片放置的 27Ω 串聯終端電阻(圖 7 中的 R8 和 R11),以符合 USB 阻抗規範。

- 儘管 RP2350 僅限於全速資料速率 (12Mbps),但我們應該嘗試並確保傳輸線(將晶片連接到連接器的銅走線)的特性阻抗接近

- USB 規格為 90Ω(差分測量)。在像這樣的 1mm 厚的電路板上,如果我們在 USB_DP 和 USB_DM 上使用 0.8mm 寬的走線,它們之間的間隙為 0.15mm,我們應該得到大約 90Ω 的差分特性阻抗。這是為了確保訊號可以盡可能乾淨地沿著這些傳輸線傳輸,從而最大限度地減少音量tag反射會降低訊號的完整性。為了使這些傳輸線正常運作,我們需要確保這些線的正下方是接地的。堅固、不間斷的接地銅區域,延伸到軌道的整個長度。在此設計中,幾乎整個底部銅層都專用於接地,並且特別注意確保 USB 走線只透過接地。如果您的建造選擇厚度超過 1 毫米的 PCB,那麼我們有兩個選擇。我們可以重新設計 USB 傳輸線,以補償軌道和下方地面之間的更大距離(這在物理上可能是不可能的),或者我們可以忽略它,並希望得到最好的結果。 USB FS 的寬容度可能相當高,但您的情況可能會有所不同。它可能適用於許多應用程序,但可能不符合 USB 標準。

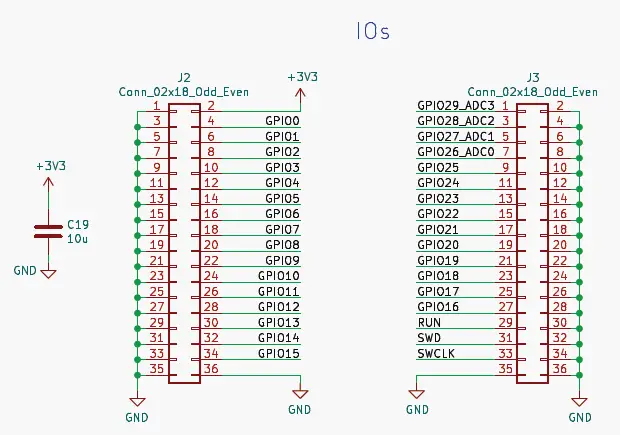

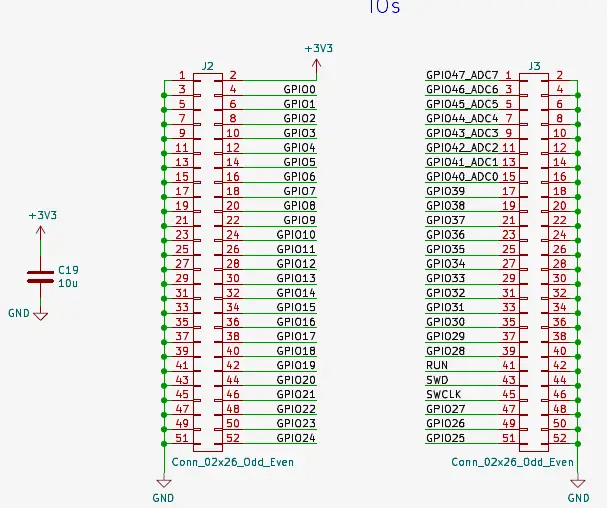

I/O 標頭

圖 12. 顯示 QFN2.54 版本的 60mm I/O 接頭連接器的原理圖部分

- 除了已經提到的USB 連接器之外,還有一對雙排2.54mm 接頭連接器(圖2 中的J3 和J12),電路板的每一側都有一個,其餘的I/O 已連接到該連接器。 RP30A 上有 2350 個 GPIO,而 RP48B 上有 2350 個 GPIO,因此此版本 Minimal 板上的接頭較大,可以容納額外的引腳(參見圖 13)。

- 由於這是通用設計,沒有考慮特定應用,因此 I/O 可以根據使用者的意願進行連接。每個接頭座上的內排腳位是 I/O,外排接腳全部接地。在 I/O 連接器上包含多個接地是一種很好的做法。這有助於保持低阻抗接地,並且還為流入和流出的電流提供充足的潛在返迴路徑。

- I/O 連接。這對於最大限度地減少電磁幹擾非常重要,電磁幹擾可能是由快速切換訊號的返回電流引起的,需要較長的循環路徑才能完成電路。

- 兩個接頭連接器位於相同的 2.54mm 網格上,這使得將該板連接到其他東西(例如麵包板)變得更容易。您可能需要考慮僅安裝單排接頭而不是雙排接頭,從而省去外排接地連接,以便更方便地安裝到麵包板上。

圖 13. 顯示 QFN2.54 版本的 80mm I/O 接頭連接器的原理圖部分

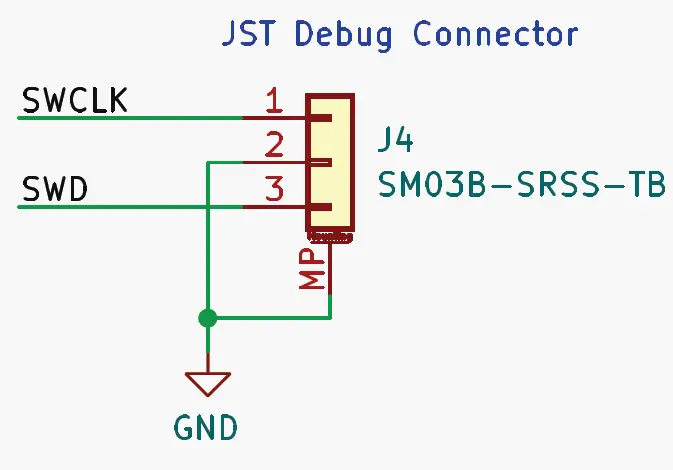

偵錯連接器

圖 14. 顯示用於 SWD 調試的可選 JST 連接器的示意圖

對於片上調試,您可能想要連接到 RP2350 的 SWD 介面。 2.54mm 接頭 J3 上提供了兩個引腳 SWD 和 SWCLK,以便輕鬆連接您選擇的調試探針。除此之外,我還包括一個可選的 JST 標頭,它允許輕鬆連接到 Raspberry Pi 偵錯探針。你不需要使用這個,如果你確實打算調試軟體,2.54mm 接頭就足夠了,但我發現這樣做更方便。我選擇了水平連接器,主要是因為我喜歡它的外觀,即使它不在板的邊緣,但也可以使用垂直連接器,儘管佔地面積略有不同。

按鈕

Minimal 設計現在不再包含一個按鈕,而是包含兩個按鈕,而 RP240 版本則沒有。正如我們之前討論的,一個用於 USB 啟動選擇,但第二個是「重置」按鈕,連接到 RUN 引腳。這些都不是絕對必要的(儘管如果需要USB 啟動模式,則BOOTSEL 按鈕必須替換為接頭或類似的按鈕),並且如果考慮空間或成本,則可以將其刪除,但它們確實使RP2350 的使用變得更加困難。

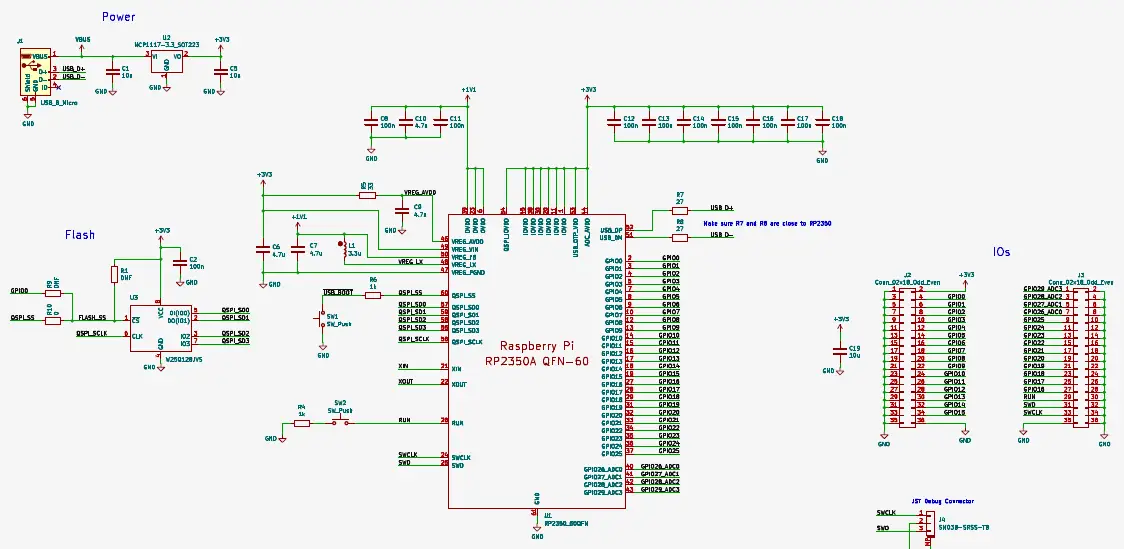

附錄 A:完整原理圖 - RP2350A 版本

圖 15. RP2350A 最小設計的完整原理圖

附錄 B:完整原理圖 - RP2350B 版本

圖 16. RP2350B 最小設計的完整原理圖

附錄 H:文件發布歷史記錄

8 年 2024 月 XNUMX 日

初次發布。

我的樹莓派

Raspberry Pi 是 Raspberry Pi Ltd 的商標

樹莓派有限公司

文件/資源

|

樹莓派 SC1631 樹莓派微控制器 [pdf] 使用說明書 SC1631 樹莓派微控制器,SC1631,樹莓派微控制器,微控制器 |