ינטעל Agilex Logic Array בלאַקס און אַדאַפּטיוו לאָגיק מאָדולעס

Intel® Agilex™ LAB און ALM Overview

די לאָגיק מענגע בלאָק (LAB) איז קאַמפּאָוזד פון יקערדיק בנין בלאַקס באקאנט ווי אַדאַפּטיוו לאָגיק מאַדזשולז (ALMs). איר קענען קאַנפיגיער די לאַבס צו ינסטרומענט לאָגיק פאַנגקשאַנז, אַריטמעטיק פאַנגקשאַנז און רעגיסטרירן פאַנגקשאַנז.

איר קענען נוצן האַלב פון די בנימצא לאַבס אין די Intel® Agilex ™ דעוויסעס ווי זכּרון לאַבס (MLABs). עטלעכע דעוויסעס קען האָבן אַ העכער MLAB פאַרהעלטעניש.

די Intel Quartus® Prime ווייכווארג און אנדערע געשטיצט דריט-פּאַרטיי סינטעז מכשירים אויטאָמאַטיש קלייַבן די צונעמען מאָדע פֿאַר פּראָסט פאַנגקשאַנז אַזאַ ווי קאָונטערס, אַדדערס, סאַבטראַקטערז און אַריטמעטיק פאַנגקשאַנז.

Intel Hyperflex ™ Core Architecture, Intel Agilex Device Overview

גיט מער אינפֿאָרמאַציע וועגן היפּער-רעגיסטרערס און די Intel Hyperflex ™ האַרץ אַרקאַטעקטשער. היפּער-רעגיסטרערס זענען נאָך רעדזשיסטערז בנימצא אין יעדער ינטערקאַנעקט רוטינג אָפּשניט איבער די האַרץ שטאָף, אַרייַנגערעכנט די רוטינג סעגמאַנץ פארבונדן צו די לאַב ינפּוץ און אַוטפּוץ.

Intel Hyperflex ™ רעגיסטרירן

די Intel Agilex מיטל משפּחה איז באזירט אויף די Intel Hyperflex ™ האַרץ אַרקאַטעקטשער.

די ינטעל אַגילעקס לאַב כּולל ינטעל היפּערפלעקס רעדזשיסטערז און אנדערע פֿעיִקייטן דיזיינד צו פאַסילאַטייט רעטימינג. ינטעל היפּערפלעקס רעדזשיסטערז זענען בנימצא אין ALMs און פירן קייטן. ווי געוויזן אין די Intel Agilex ALM קאַנעקשאַן דעטאַילס פיגור, די Intel Hyperflex רעדזשיסטערז זענען ליגן אויף די סינטשראָנאָוס קלאָר און זייגער געבן ינפּוץ צו פאַרגרעסערן אָדער רעדוצירן וועג פאַרהאַלטן. כל די Intel Hyperflex רעדזשיסטערז קענען זיין ענייבאַלד און זענען קאַנטראָולד דורך די Intel Quartus Prime ווייכווארג בעשאַס רעטימינג.

Intel Agilex LAB און ALM אַרטשיטעקטורע און פֿעיִקייטן

די פאלגענדע סעקשאַנז באַשרייַבן די LAB און ALM פֿאַר Intel Agilex דעוויסעס.

לאַב

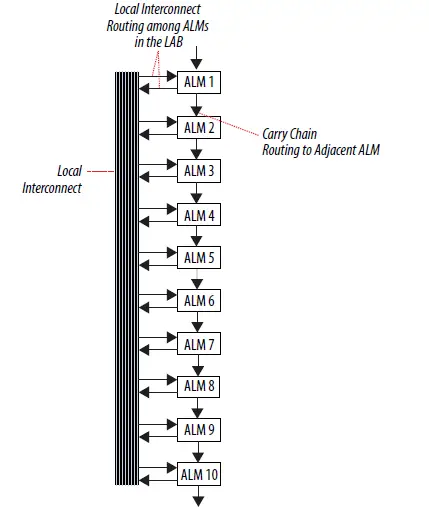

די לאַבס זענען קאָנפיגוראַבלע לאָגיק בלאַקס וואָס צונויפשטעלנ זיך פון אַ גרופּע פון לאָגיק רעסורסן. יעדער לאַב כּולל דעדאַקייטאַד לאָגיק פֿאַר דרייווינג קאָנטראָל סיגנאַלז צו זיין ALMs. די MLAB איז אַ סופּערסעט פון די לאַב און כולל אַלע די לאַב פֿעיִקייטן. עס זענען אַ גאַנץ פון 10 ALMs אין יעדער לאַב, ווי געוויזן אין די Intel Agilex LAB און MLAB סטרוקטור פיגור.

פיגורע 1.

Intel Agilex לאַב סטרוקטור און ינטערקאַנעקץ איבערview

די פיגור ווייזט אַן איבערview פון די Intel Agilex LAB און MLAB סטרוקטור מיט די לאַב ינטערקאַנעקץ.

פֿאַרבונדענע אינפֿאָרמאַציע

פֿאַרבונדענע אינפֿאָרמאַציע

MLAB אויף בלאַט 6

MLAB

יעדער MLAB שטיצט מאַקסימום 640 ביץ פון פּשוט צווייענדיק-פּאָרט SRAM. איר קענען קאַנפיגיער יעדער ALM אין אַ MLAB ווי אַ 32 (טיפקייַט) רענטגענ 2 (ברייט) זכּרון בלאָק, ריזאַלטינג אין אַ קאַנפיגיעריישאַן פון 32 (טיפקייַט) רענטגענ 20 (ברייט) פּשוט צווייענדיק-פּאָרט SRAM בלאָק.

פיגורע 2.

Intel Agilex LAB און MLAB סטרוקטור לאקאלע און דירעקט לינק ינטערקאַנעקץ

לאקאלע און דירעקט לינק ינטערקאַנעקץ

יעדער לאַב קענען פירן אויס 60 ALM אַוטפּוץ. א סובסעט פון די קענען גלייך פאָר לאַב ינפּוץ, אָבער קיין קשר צו אַ אַנדערש רודערן אָדער זייַל מוזן נוצן לפּחות איין גענעראַל-ציל רוטינג דראָט.

די היגע ינטערקאַנעקט דרייווז די ALM ינפּוץ. ALM אַוטפּוץ, ווי געזונט ווי זייַל און רודערן ינטערקאַנעקץ פירן די היגע ינטערקאַנעקט.

פיגורע 3. Intel Agilex LAB לאקאלע און דירעקט לינק ינטערקאַנעקט  פירן קייט ינטערקאַנעקץ

פירן קייט ינטערקאַנעקץ

עס איז אַ דעדאַקייטאַד פירן קייט וועג צווישן די ALMs. ינטעל אַגילעקס דעוויסעס אַרייַננעמען אַן ימפּרוווד ינטערקאַנעקט סטרוקטור אין לאַבס פֿאַר רוטינג פירן קייטן פֿאַר עפעקטיוו אַריטמעטיק פאַנגקשאַנז. די ALM-צו-ALM קאַנעקשאַנז בייפּאַס די היגע ינטערקאַנעקט.

די ינטעל היפּערפלעקס רעדזשיסטערז זענען מוסיף צו די קעריינג קייט צו געבן פלעקסאַבאַל רעטימינג אַריבער אַ קייט פון לאַבס און די Intel Quartus Prime Compiler נעמט אויטאָמאַטיש אַדוואַנט.tagפון די רעסורסן צו פֿאַרבעסערן יוטאַלאַזיישאַן און פאָרשטעלונג.

פיגורע 4. פירן קייט ינטערקאַנעקץ לאַב קאָנטראָל סיגנאַלז

לאַב קאָנטראָל סיגנאַלז

עס זענען צוויי זייגער קוואלן אין יעדער לאַב קאָנטראָל בלאָק, וואָס דזשענערייט צוויי לאַב קלאַקס (LABCLK[1:0]) און צוויי דילייד לאַב קלאַקס (LABCLK_Phi1[1:0]) צו פירן די ALM רעדזשיסטערז און היפּער-רעגיסטרערס אין די לאַב. די לאַב שטיצט צוויי יינציק זייגער געבן סיגנאַלז, ווי געזונט ווי נאָך קלאָר סיגנאַלז, פֿאַר די ALM רעדזשיסטערז.

די לאַב רודערן קלאַקס [5..0] און לאַב היגע ינטערקאַנעקץ דזשענערייט די לאַב-ברייט קאָנטראָל סיגנאַלז. א נידעריק סקיו זייגער נעץ דיסטריביוץ גלאבאלע סיגנאַלז צו די רודערן קלאַקס [5..0]. די MultiTrack ינטערקאַנעקט באשטייט פון קעסיידערדיק, פאָרשטעלונג-אָפּטימיזעד רוטינג שורות פון פאַרשידענע לענגקטס און ספּידז געניצט פֿאַר רוטינג עפעקטיווקייַט. די Intel Quartus Prime Compiler אויטאָמאַטיש רוץ קריטיש פּלאַן פּאַטס אויף פאַסטער ינטערקאַנעקץ צו פֿאַרבעסערן פּלאַן פאָרשטעלונג און אָפּטימיזעס די מיטל רעסורסן.

קלאָר לאָגיק קאָנטראָל

לאַב-ברייט סיגנאַלז קאָנטראָלירן די לאָגיק פֿאַר די קלאָר סיגנאַל פון די ALM רעגיסטרירן. די ALM רעגיסטרירן גלייך שטיצט ביידע אַ סינטשראָנאָוס און אַ ייסינגקראַנאַס קלאָר. יעדער לאַב שטיצט איין סינטשראָנאָוס קלאָר סיגנאַל און צוויי ייסינגקראַנאַס קלאָר סיגנאַלז.

ינטעל אַגילעקס דעוויסעס צושטעלן אַ מיטל-ברייט באַשטעטיק שטיפט (DEV_CLRn) וואָס ריסעץ אַלע די רעדזשיסטערז אין די מיטל. איר קענען געבן די DEV_CLRn שטיפט אין די Intel Quartus Prime ווייכווארג איידער זאַמלונג. דער מיטל-ברייט באַשטעטיק סיגנאַל אָווועררייד אַלע אנדערע קאָנטראָל סיגנאַלז.

פיגורע 5. ינטעל אַגילעקס לאַב-ברייט קאָנטראָל סיגנאַלז

ALM

די פאלגענדע סעקשאַנז דעקן די ALM רעסורסן, ALM רעזולטאַט און ALM אַפּערייטינג מאָדעס.

ALM רעסאָורסעס

יעדער ALM כּולל אַ פאַרשיידנקייַט פון LUT-באזירט רעסורסן וואָס קענען זיין צעטיילט צווישן צוויי קאַמבאַנשאַנאַל אַדאַפּטיוו LUTs (ALUTs), אַ צוויי-ביט פול אַדער און פיר רעדזשיסטערז.

מיט אַרויף צו אַכט ינפּוץ פֿאַר די צוויי קאַמבאַנשאַנאַל ALUTs, איין ALM קענען ינסטרומענט פאַרשידן קאַמבאַניישאַנז פון צוויי פאַנגקשאַנז. די אַדאַפּטאַבילאַטי אַלאַוז אַן ALM צו זיין גאָר צוריק-קאַמפּאַטאַבאַל מיט פיר אַרייַנשרייַב LUT אַרקאַטעקטשערז. איין ALM קענען אויך ינסטרומענט אַ סאַבסעט פון אַכט אַרייַנשרייַב פאַנגקשאַנז.

איין ALM כּולל פיר פּראָוגראַמאַבאַל רעדזשיסטערז. יעדער רעגיסטרירן האט די פאלגענדע פּאָרץ:

- דאַטן אין

- דאַטע אויס

- נאָרמאַל לאַב זייגער

- דילייד לאַב זייגער

- זייגער געבן

- סינטשראָנאָוס קלאָר

- ייסינגקראַנאַס קלאָר

גלאבאלע סיגנאַלז, גענעראַל-צוועק I/O (GPIO) פּינס, אָדער קיין ינערלעך לאָגיק קענען פירן די זייגער געבן סיגנאַל, זייגער און ייסינגקראַנאַס אָדער סינטשראָנאָוס קלאָר קאָנטראָל סיגנאַלז פון אַן ALM רעגיסטרירן. דער זייגער געבן סיגנאַל האט בילכערקייַט איבער סינטשראָנאָוס באַשטעטיק סיגנאַל.

פֿאַר קאַמבאַנשאַנאַל פאַנגקשאַנז, די רעדזשיסטערז זענען בייפּאַסט און די רעזולטאַט פון די קוק-אַרויף טיש (LUT) און אַדדערס דרייווז גלייַך צו די אַוטפּוץ פון אַ ALM. צוויי שנעל אַוטפּוץ זענען בנימצא פֿאַר 6 LUT אַוטפּוץ און דנאָ 5 LUT אַוטפּוץ צו בייפּאַס די רעזולטאַט מוקס און פאַרבינדן צו אן אנדער לאַב פֿאַר קריטיש וועג אַדזשאַסטמאַנט.

פיגורע 6. Intel Agilex ALM הויך-לעוועל בלאַק דיאַגראַמע

ALM רעזולטאַט

ALM רעזולטאַט

די אַלגעמיינע רוטינג אַוטפּוץ אין יעדער ALM פאָר די היגע, רודערן און זייַל רוטינג רעסורסן. זעקס ALM אַוטפּוץ, אַרייַנגערעכנט צוויי שנעל רעזולטאַט פּאַטס, קענען פירן זייַל, רודערן אָדער דירעקט לינק רוטינג קאַנעקשאַנז.

די LUT, אַדער אָדער רעגיסטרירן רעזולטאַט קענען פירן די ALM אַוטפּוץ. ביידע די LUT אָדער אַדער און די ALM רעגיסטרירן קענען פאָרן סיימאַלטייניאַסלי פון די ALM.

רעגיסטרירן פּאַקינג ימפּרוווז מיטל יוטאַלאַזיישאַן דורך אַלאַוינג אַנרילייטיד רעגיסטרירן און קאַמבאַנשאַנאַל לאָגיק צו זיין פּאַקט אין אַ איין ALM. די ALM קענען אויך אַרויספירן רעגיסטרירט און אַנרעדזשיסטערד ווערסיעס פון די LUT אָדער אַדער רעזולטאַט.

די פאלגענדע פיגור ווייזט די Intel Agilex ALM קאַנעקטיוויטי. אין די Intel Quartus Prime Resource Property Editor, די גאנצע ALM פֿאַרבינדונג איז סימפּלאַפייד. עטלעכע ראָוטינגז וועט זיין ראַוטיד ינעווייניק דורך די Intel Quartus Prime ווייכווארג.

פיגורע 7. Intel Agilex ALM קאַנעקשאַן דעטאַילס ALM אַפּערייטינג מאָדעס

ALM אַפּערייטינג מאָדעס

די Intel Agilex ALM אַפּערייץ אין קיין פון די פאלגענדע מאָדעס:

- נאָרמאַל מאָדע

- עקסטענדעד LUT מאָדע

- אַריטמעטיק מאָדע

נאָרמאַל מאָדע

נאָרמאַל מאָדע אַלאַוז צוויי פאַנגקשאַנז צו זיין ימפּלאַמענאַד אין איין Intel Agilex ALM, אָדער אַ איין פונקציע פון אַרויף צו זעקס ינפּוץ.

אַרויף צו אַכט דאַטן ינפּוץ פון די לאַב היגע ינטערקאַנעקט זענען ינפּוץ צו די קאַמבאַנשאַנאַל לאָגיק.

די ALM קענען שטיצן זיכער קאַמבאַניישאַנז פון גאָר פרייַ פאַנגקשאַנז און פאַרשידן קאַמבאַניישאַנז פון פאַנגקשאַנז וואָס האָבן פּראָסט ינפּוץ.

די Intel Quartus Prime Compiler סאַלעקץ אויטאָמאַטיש די ינפּוץ צו די LUT. ALMs אין נאָרמאַל מאָדע שטיצן רעגיסטרירן פּאַקינג.

די פאלגענדע פיגור ווייזט אַ קאָמבינאַציע פון פאַרשידענע אַרייַנשרייַב קאַנעקשאַנז פֿאַר די LUT מאָדע. אין דיין פּלאַן, די Intel Quartus Prime ווייכווארג קען באַשטימען פאַרשידענע אַרייַנשרייַב נאַמינג בעשאַס זאַמלונג.

פיגורע 8. ALM אין נאָרמאַל מאָדע

קאַמבאַניישאַנז פון פאַנגקשאַנז מיט ווייניקערע ינפּוץ ווי די געוויזן זענען אויך געשטיצט. פֿאַר עקסample, קאַמבאַניישאַנז פון פאַנגקשאַנז מיט די פאלגענדע נומער פון ינפּוץ זענען געשטיצט.

- 4 און 3

- 3 און 3

- 3 און 2

- 5 און 2

פֿאַר די פּאַקינג פון צוויי 5-אַרייַנפיל פאַנגקשאַנז אין איין ALM, די פאַנגקשאַנז מוזן האָבן בייַ מינדסטער צוויי פּראָסט ינפּוץ. די פּראָסט ינפּוץ זענען דאַטאַאַ און דאַטאַב. די קאָמבינאַציע פון אַ 4 אַרייַנשרייַב פֿונקציע מיט אַ 5 אַרייַנשרייַב פֿונקציע ריקווייערז איין פּראָסט אַרייַנשרייַב (אָדער דאַטן אָדער דאַטן).

אין אַ ספּאַרסלי געוויינט מיטל, פאַנגקשאַנז וואָס קען זיין געשטעלט אין איין ALM קענען זיין ימפּלאַמענאַד אין באַזונדער ALMs דורך די Intel Quartus Prime ווייכווארג צו דערגרייכן די בעסטער פאָרשטעלונג. ווען אַ מיטל הייבט צו פּלאָמבירן, די Intel Quartus Prime ווייכווארג ניצט אויטאָמאַטיש די פול פּאָטענציעל פון די Intel Agilex ALM. די Intel Quartus Prime Compiler זוכט אויטאָמאַטיש פֿאַר פאַנגקשאַנז ניצן פּראָסט ינפּוץ אָדער גאָר פרייַ פאַנגקשאַנז צו זיין שטעלן אין איין ALM צו מאַכן עפעקטיוו נוצן פון מיטל רעסורסן. אין אַדישאַן, איר קענען מאַניואַלי קאָנטראָלירן מיטל נוצן דורך באַשטעטיקן אָרט אַסיינמאַנץ.

פיגורע 9. 6 ינפּוט LUT מאָדע פֿונקציע אין נאָרמאַל מאָדע

פיגורע 10. 3 ינפּוט LUT מאָדע פֿונקציע אין נאָרמאַל מאָדע

פיגורע 10. 3 ינפּוט LUT מאָדע פֿונקציע אין נאָרמאַל מאָדע

דאַטן און דאַטן ב זענען בארעכטיגט פֿאַר פאַרשרייַבן פּאַקינג.  איר קענען ינסטרומענט קיין 3-6 אַרייַנשרייַב פאַנגקשאַנז ניצן די פאלגענדע ינפּוץ:

איר קענען ינסטרומענט קיין 3-6 אַרייַנשרייַב פאַנגקשאַנז ניצן די פאלגענדע ינפּוץ:

- דאַטע

- datad0

- datac0

- datac1

- datad1

- dataf

- דאַטאַאַ און דאַטאַב - וואָס דאַטאַ און דאַטאַב זענען שערד איבער ביידע LUTs צו צושטעלן בייגיקייַט צו ינסטרומענט אַ אַנדערש פֿונקציע אין יעדער LUT.

ביידע דאַטאַאַ און דאַטאַב ינפּוץ שטיצן די רעגיסטרירן פּאַקינג שטריך. אויב איר געבן די רעגיסטרירן פּאַקינג שטריך, ביידע דאַטן און דאַטאַב ינפּוץ אָדער איינער פון די ינפּוץ בייפּאַס די LUT און גלייך קאָרמען אין די רעגיסטרירן, דיפּענדינג אויף די פּאַקט רעגיסטרי מאָדע. פֿאַר Intel Agilex דעוויסעס, די פאלגענדע טייפּס פון פּאַקט רעגיסטרירן מאָדעס זענען געשטיצט:

- 5 אַרייַנשרייַב LUT מיט 1 פּאַקט רעגיסטרירן דרך

- 5 אַרייַנשרייַב LUT מיט 2 פּאַקט רעגיסטרירן פּאַטס

- צוויי 3 ינפּוט LUTs מיט 2 פּאַקט רעגיסטרירן פּאַטס

די LUT מיט 3 אַרייַנשרייַב מיט 2 פּאַקט רעגיסטרירט פּאַטס איז ילאַסטרייטיד אין די 3-אינופּ לוט מאָדע פֿונקציע אין נאָרמאַל מאָדע. פֿאַר Intel Agilex דעוויסעס, די LUT מאָדע מיט 6 אַרייַנשרייַב שטיצט נישט די רעגיסטרירן פּאַקינג שטריך.

עקסטענדעד LUT מאָדע

פיגורע 11. שטיצט 8-ינפּוט פאַנגקשאַנז אין די עקסטענדעד לוט מאָדע

זיכער פאַנגקשאַנז פון 8 אַרייַנשרייַב קענען זיין ימפּלאַמענאַד אין אַ איין ALM ניצן אַלע די LUT ינפּוץ:

- דאַטע

- datad0

- datac0

- dataa

- דאַטאַב

- datac1

- datad1

- dataf

אין די 8-אַרייַן עקסטענדעד LUT מאָדע, די פּאַקט רעגיסטרי מאָדע איז געשטיצט, צוגעשטעלט אַז די פּאַקט רעגיסטרירן שאַרעס אַ דאַטן אָדער דאַטאַב אַרייַנשרייַב מיט די 8-אַרייַנשרייַב LUT.

אַריטמעטיק מאָדע

די ALM אין אַריטמעטיק מאָדע ניצט צוויי סעט פון צוויי 4-אַרייַנופּן LUTs צוזאמען מיט צוויי דעדאַקייטאַד פול אַדדערס. די דעדאַקייטאַד אַדדערס לאָזן די LUTs צו דורכפירן פאַר-אַדדער לאָגיק. דעריבער, יעדער אַדער קענען לייגן די רעזולטאַט פון צוויי 4 אַרייַנשרייַב פאַנגקשאַנז.

אַריטמעטיק מאָדע אויך אָפפערס זייגער געבן, טאָמבאַנק געבן, סינטשראָנאָוס אַרויף און אַראָפּ קאָנטראָל, לייגן און אַראָפּרעכענען קאָנטראָל און סינטשראָנאָוס קלאָר.

די קלאָר און זייגער געבן אָפּציעס זענען לאַב-ברייט סיגנאַלז וואָס ווירקן אַלע רעדזשיסטערז אין די לאַב. איר קענען ינדיווידזשואַלי דיסייבאַל אָדער געבן די סיגנאַלז פֿאַר יעדער פּאָר פון רעדזשיסטערז אין אַ אַדאַפּטיוו LUT (ALUT). די Intel Quartus Prime ווייכווארג לייגט אויטאָמאַטיש רעגיסטערס וואָס זענען נישט געניצט דורך די טאָמבאַנק אין אנדערע לאַבס.

פיגורע 12. Intel Agilex ALM אין אַריטמעטיק מאָדע

פירן קייט

פירן קייט

די פירן קייט גיט אַ שנעל פירן פונקציע צווישן די דעדאַקייטאַד אַדדערס אין די אַריטמעטיק מאָדע.

די 2-ביסל קעריינג סעלעקט שטריך אין Intel Agilex דעוויסעס ספּליץ די פּראַפּאַגיישאַן פאַרהאַלטן פון פירן קייטן מיט די ALM. פירן קייטן קענען אָנהייבן אין דער ערשטער אַלם אָדער די זעקסט אַלם אין אַ לאַב. די לעצט פירן-אויס סיגנאַל איז ראַוטיד צו אַ ALM, ווו עס איז פאסטעכער צו היגע, רודערן אָדער זייַל ינטערקאַנעקץ.

דאָקומענט רעוויזיע געשיכטע פֿאַר די Intel Agilex Logic Array Blocks און Adaptive Logic Modules User Guide

| דאָקומענט ווערסיע | ענדערונגען |

| 2022.05.24 | דערהייַנטיקט פיגור: Intel Agilex ALM High-Level Block Diagram. |

| 2019.11.14 | דערהייַנטיקט די באַשרייַבונג אין די לאַב קאָנטראָל סיגנאַלז אָפּטיילונג. |

| 2019.10.01 |

|

| 2019.04.02 | ערשט מעלדונג. |

Intel Corporation.

אלע רעכטן רעזערווירט. ינטעל, די ינטעל לאָגאָ און אנדערע ינטעל מאַרקס זענען טריידמאַרקס פון ינטעל קאָרפּאָראַטיאָן אָדער זייַן סאַבסידיעריז. ינטעל וואָראַנטיז פאָרשטעלונג פון זייַן FPGA און סעמיקאַנדאַקטער פּראָדוקטן צו קראַנט ספּעסאַפאַקיישאַנז אין לויט מיט ינטעל ס נאָרמאַל וואָראַנטי, אָבער ריזערווז די רעכט צו מאַכן ענדערונגען צו קיין פּראָדוקטן און באַדינונגס אין קיין צייט אָן באַמערקן. ינטעל אַסומז קיין פֿאַראַנטוואָרטלעכקייט אָדער אַכרייַעס וואָס איז שטייענדיק פֿון די אַפּלאַקיישאַן אָדער נוצן פון קיין אינפֿאָרמאַציע, פּראָדוקט אָדער דינסט דיסקרייבד דאָ, אַחוץ ווי ינטעל איז עקספּרעסלי מסכים צו שרייבן. ינטעל קאַסטאַמערז זענען אַדווייזד צו קריגן די לעצטע ווערסיע פון די מיטל ספּעסאַפאַקיישאַנז איידער זיי פאַרלאָזנ אויף קיין ארויס אינפֿאָרמאַציע און איידער פּלייסינג אָרדערס פֿאַר פּראָדוקטן אָדער באַדינונגס.

* אנדערע נעמען און בראַנדז קען זיין קליימד ווי די פאַרמאָג פון אנדערע.

יסאָ

9001:2015

רעגיסטרירט

דאָקומענטן / רעסאָורסעס

|

ינטעל Agilex Logic Array בלאַקס און אַדאַפּטיוו לאָגיק מאָדולעס [pdfבאַניצער גייד Agilex Logic Array Blocks און Adaptive Logic Modules, Agilex, Logic Array Blocks and Adaptive Logic Modules, Array Blocks and Adaptive Logic Modules, Adaptive Logic Modules, Logic Modules |