Bộ vi điều khiển Raspberry Pi SC1631 Raspberry

Thông số kỹ thuật sản phẩm

- Mẫu: RP2350

- Gói: QFN-60

- Bộ nhớ Flash bên trong: Không

- Tậptage Bộ điều chỉnh: Bộ điều chỉnh chuyển mạch trên chip

- Chân điều chỉnh: 5 (đầu vào 3.3V, đầu ra 1.1V, VREG_AVDD, VREG_LX, VREG_PGND)

Hướng dẫn sử dụng sản phẩm

- Chương 1: Giới thiệu

- Dòng RP2350 cung cấp các tùy chọn gói khác nhau so với dòng RP2040. RP2350A và RP2354A có gói QFN-60 không có và có bộ nhớ flash bên trong, trong khi RP2354B và RP2350B có gói QFN-80 có và không có bộ nhớ flash.

- Chương 2: Quyền lực

Dòng RP2350 có một khối chuyển mạch trên chip mớitagBộ điều chỉnh điện áp có năm chân. Bộ điều chỉnh này yêu cầu các thành phần bên ngoài để vận hành nhưng cung cấp hiệu suất năng lượng cao hơn ở dòng điện tải cao hơn so với bộ điều chỉnh tuyến tính trong dòng RP2040. Hãy chú ý đến độ nhạy nhiễu trong chân VREG_AVDD cung cấp cho mạch tương tự.

Những câu hỏi thường gặp (FAQ)

- H: Sự khác biệt chính giữa RP2350A và RP2350B là gì?

A: Sự khác biệt chính nằm ở bộ nhớ flash bên trong. RP2350A không có bộ nhớ flash bên trong trong khi RP2350B thì có. - Q: Có bao nhiêu chân cắm vol?tagBộ điều chỉnh điện áp trong dòng RP2350 có gì?

A: TậptagBộ điều chỉnh trong dòng RP2350 có năm chân.

Thiết kế phần cứng với RP2350 Sử dụng vi điều khiển RP2350 để xây dựng bo mạch và sản phẩm

Bản quyền

- © 2023-2024 Raspberry Pi Ltd

- Tài liệu này được cấp phép theo giấy phép Creative Commons Ghi công-Không phái sinh 4.0 Quốc tế (CC BY-ND). ngày xây dựng: 2024-08-08 phiên bản xây dựng: c0acc5b-clean

- Thông báo từ chối trách nhiệm pháp lý

- DỮ LIỆU KỸ THUẬT VÀ ĐỘ TIN CẬY CHO CÁC SẢN PHẨM RASPBERRY PI (BAO GỒM CÁC BẢNG DỮ LIỆU) ĐƯỢC SỬA ĐỔI THEO THỜI GIAN (“NGUỒN LỰC”) ĐƯỢC RASPBERRY PI LTD (“RPL”) CUNG CẤP “NGUYÊN TRẠNG” VÀ BẤT KỲ BẢO HÀNH RÕ RÀNG HAY NGỤ Ý NÀO, BAO GỒM NHƯNG KHÔNG GIỚI HẠN Ở, CÁC BẢO HÀNH NGỤ Ý NÀO VỀ KHẢ NĂNG THƯƠNG MẠI VÀ SỰ PHÙ HỢP CHO MỘT MỤC ĐÍCH CỤ THỂ ĐỀU BỊ TỪ CHỐI. Ở MỨC TỐI ĐA ĐƯỢC LUẬT ÁP DỤNG CHO PHÉP, TRONG MỌI TRƯỜNG HỢP, RPL SẼ KHÔNG CHỊU TRÁCH NHIỆM ĐỐI VỚI BẤT KỲ THIỆT HẠI TRỰC TIẾP, GIÁN TIẾP, NGẪU NHIÊN, ĐẶC BIỆT, MANG TÍNH MẪU HOẶC HẬU QUẢ NÀO (BAO GỒM NHƯNG KHÔNG GIỚI HẠN Ở VIỆC MUA SẮM HÀNG HÓA HOẶC DỊCH VỤ THAY THẾ; MẤT QUYỀN SỬ DỤNG, DỮ LIỆU HOẶC LỢI NHUẬN; HOẶC GIÁN ĐOẠN KINH DOANH) BẤT KỂ DO NGUYÊN NHÂN GÌ VÀ THEO BẤT KỲ LÝ THUYẾT NÀO VỀ TRÁCH NHIỆM, CHO DÙ TRONG HỢP ĐỒNG, TRÁCH NHIỆM NGHIÊM NGẶT HOẶC HÀNH VI PHẠM PHÁP LÝ (BAO GỒM CẢ SỰ CẨU THẢ HOẶC CÁCH KHÁC) PHÁT SINH THEO BẤT KỲ CÁCH NÀO TỪ VIỆC SỬ DỤNG CÁC NGUỒN LỰC, NGAY CẢ KHI ĐÃ ĐƯỢC THÔNG BÁO VỀ KHẢ NĂNG XẢY RA THIỆT HẠI NHƯ V�

- RPL có quyền thực hiện bất kỳ cải tiến, sửa đổi, chỉnh sửa hoặc thay đổi nào đối với TÀI NGUYÊN hoặc bất kỳ sản phẩm nào được mô tả trong đó bất kỳ lúc nào và không cần thông báo thêm.

TÀI NGUYÊN dành cho người dùng có kỹ năng với trình độ kiến thức thiết kế phù hợp. Người dùng hoàn toàn chịu trách nhiệm về việc lựa chọn và sử dụng TÀI NGUYÊN và bất kỳ ứng dụng nào của các sản phẩm được mô tả trong đó. Người dùng đồng ý bồi thường và giữ cho RPL vô hại trước mọi trách nhiệm pháp lý, chi phí, thiệt hại hoặc tổn thất khác phát sinh do việc họ sử dụng TÀI NGUYÊN. - RPL cấp cho người dùng quyền sử dụng TÀI NGUYÊN chỉ kết hợp với các sản phẩm Raspberry Pi. Mọi cách sử dụng TÀI NGUYÊN khác đều bị cấm. Không cấp phép cho bất kỳ RPL nào khác hoặc quyền sở hữu trí tuệ của bên thứ ba nào khác.

- HOẠT ĐỘNG CÓ RỦI RO CAO. Các sản phẩm Raspberry Pi không được thiết kế, sản xuất hoặc dự định sử dụng trong các môi trường nguy hiểm đòi hỏi hiệu suất an toàn khi hỏng hóc, chẳng hạn như trong hoạt động của các cơ sở hạt nhân, hệ thống dẫn đường hoặc liên lạc máy bay, kiểm soát không lưu, hệ thống vũ khí hoặc các ứng dụng quan trọng về an toàn (bao gồm hệ thống hỗ trợ sự sống và các thiết bị y tế khác), trong đó sự cố của các sản phẩm có thể dẫn trực tiếp đến tử vong, thương tích cá nhân hoặc thiệt hại nghiêm trọng về thể chất hoặc môi trường ("Hoạt động có rủi ro cao"). RPL từ chối cụ thể bất kỳ bảo hành rõ ràng hoặc ngụ ý nào về tính phù hợp cho các Hoạt động có rủi ro cao và không chịu bất kỳ trách nhiệm nào đối với việc sử dụng hoặc đưa các sản phẩm Raspberry Pi vào các Hoạt động có rủi ro cao.

- Các sản phẩm Raspberry Pi được cung cấp theo Điều khoản chuẩn của RPL. Việc RPL cung cấp TÀI NGUYÊN không mở rộng hoặc sửa đổi Điều khoản chuẩn của RPL bao gồm nhưng không giới hạn ở các tuyên bố từ chối trách nhiệm và bảo đảm được nêu trong đó.

Chương 1. Giới thiệu

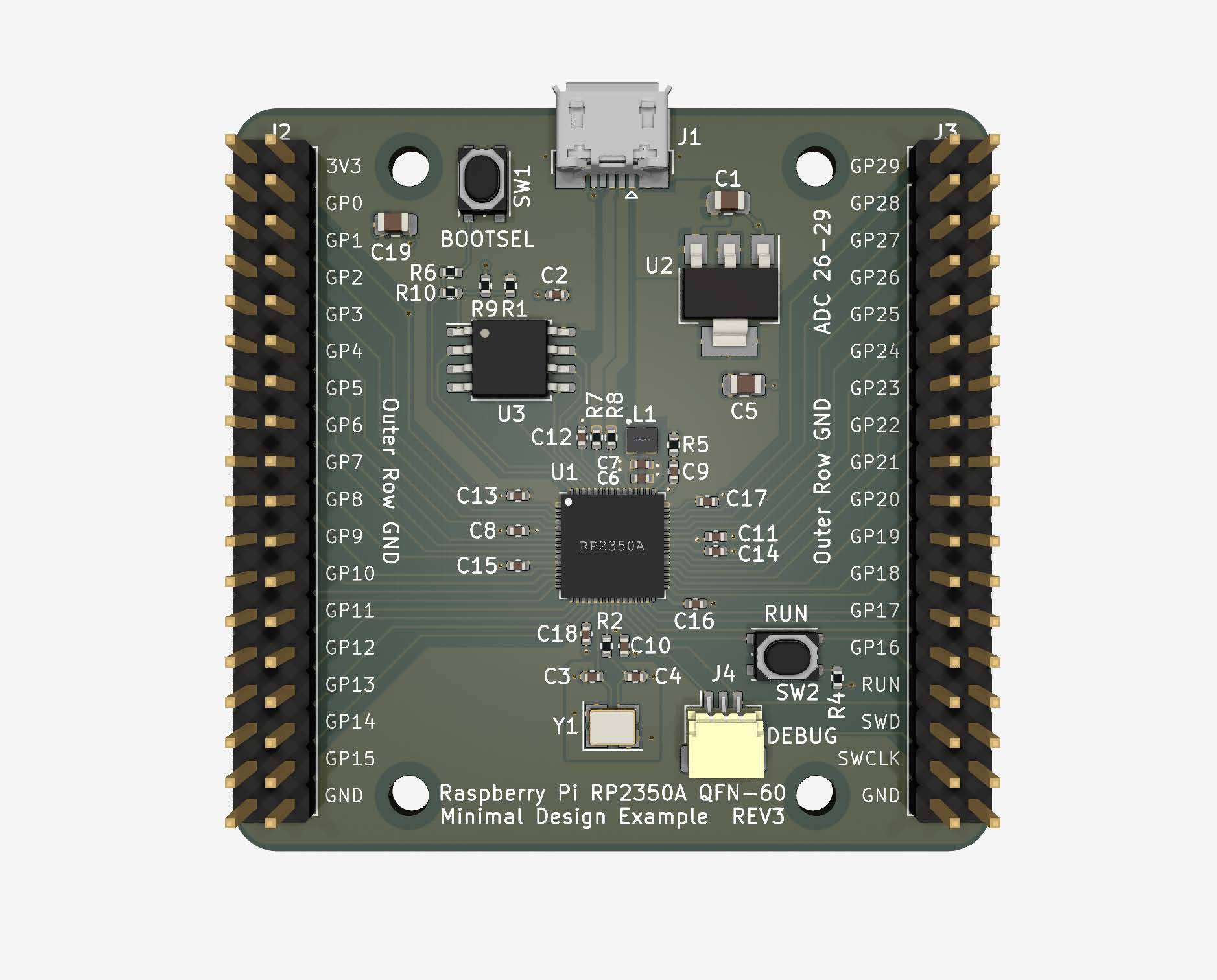

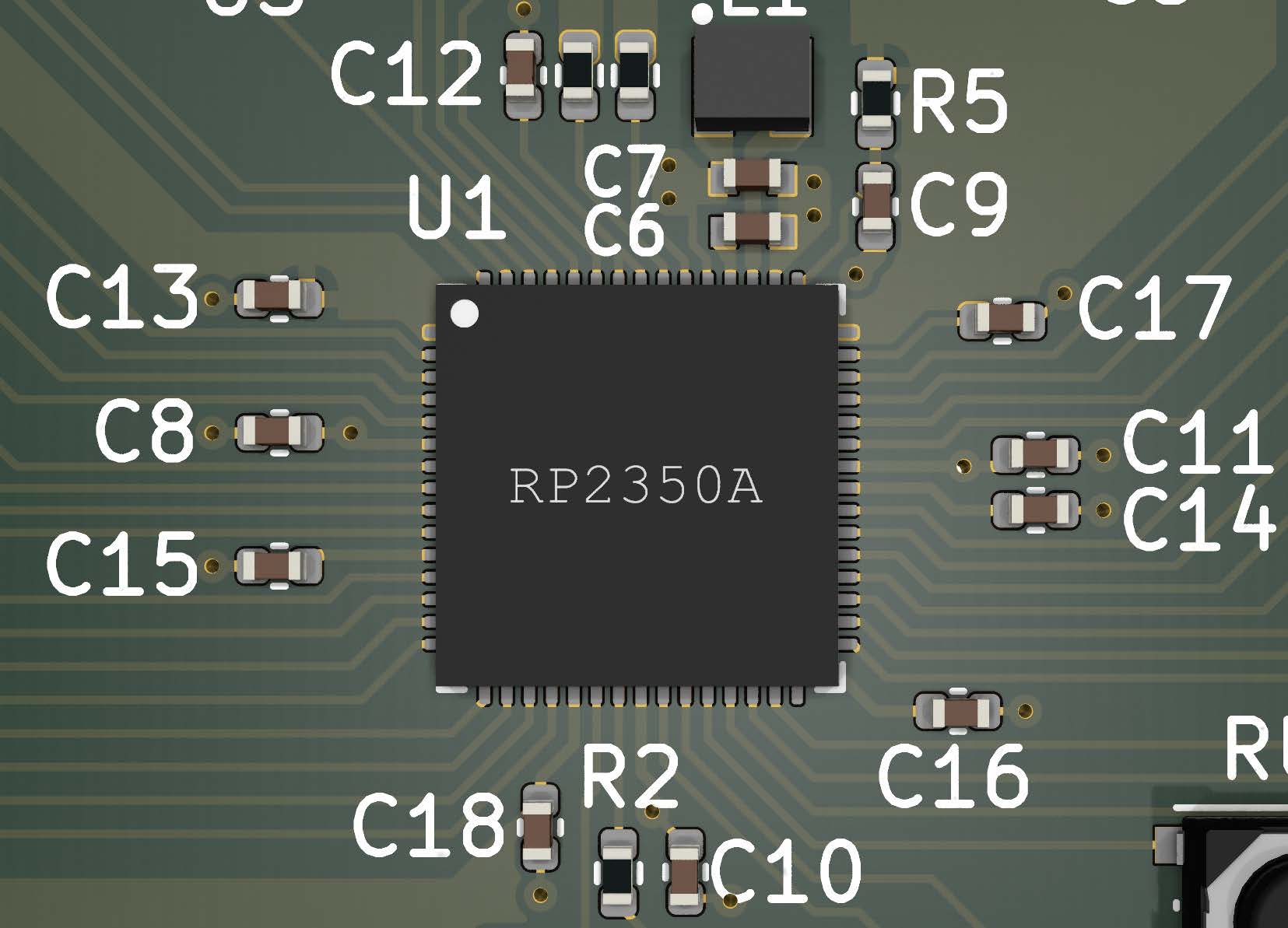

Hình 1. Bản vẽ 3D KiCad của RP2350A Thiết kế tối giảnample

Khi chúng tôi lần đầu tiên giới thiệu Raspberry Pi RP2040, chúng tôi cũng đã phát hành một thiết kế 'Tối giản'ample và hướng dẫn kèm theo Thiết kế phần cứng với RP2040 hy vọng sẽ giải thích cách sử dụng RP2040 trong một bảng mạch đơn giản và lý do tại sao lại có nhiều lựa chọn thành phần khác nhau. Với sự ra đời của dòng RP235x, đã đến lúc xem lại thiết kế RP2040 Minimal ban đầu và cập nhật để tính đến các tính năng mới, cũng như cho từng biến thể gói; RP2350A với gói QFN-60 và RP2350B là QFN-80. Một lần nữa, các thiết kế này ở định dạng Kicad (7.0) và có thể tải xuống (https://datasheets.raspberrypi.com/rp2350/Minimal-KiCAD.zip).

Bảng tối thiểu

Bo mạch Minimal ban đầu là một nỗ lực cung cấp một thiết kế tham chiếu đơn giản, sử dụng tối thiểu các thành phần bên ngoài cần thiết để chạy RP2040 và vẫn có tất cả các IO được hiển thị và có thể truy cập. Về cơ bản, bao gồm một nguồn điện (bộ điều chỉnh tuyến tính 5V đến 3.3V), bộ dao động tinh thể, bộ nhớ flash và các kết nối IO (ổ cắm micro USB và các đầu cắm GPIO). Các bo mạch Minimal dòng RP235x mới về cơ bản giống nhau, nhưng có một số thay đổi cần thiết do phần cứng mới. Ngoài ra, và mặc dù có phần đi ngược lại bản chất tối giản của thiết kế, tôi đã thêm một vài nút cho bootsel và run, cùng với một đầu cắm SWD riêng biệt, điều này có nghĩa là trải nghiệm gỡ lỗi ít gây khó chịu hơn nhiều lần này. Nói một cách nghiêm ngặt, các thiết kế không cần những nút này, các tín hiệu vẫn có sẵn trên các đầu cắm và bạn có thể bỏ qua chúng nếu bạn đặc biệt quan tâm đến chi phí hoặc không gian hoặc có xu hướng tự hành hạ mình.

Dòng RP2040 so với RP235x

Sự thay đổi rõ ràng nhất nằm ở các gói sản phẩm. Trong khi RP2040 là QFN-7 7x56mm, thì dòng RP235x hiện có bốn thành viên khác nhau. Có hai thiết bị chia sẻ cùng một gói QFN-60; RP2350A không chứa bộ nhớ flash bên trong và RP2354A có. Tương tự như vậy, QFN-80 cũng có hai loại; RP2354B có flash và RP2350B không có. Các thiết bị QFN-60 và RP2040 ban đầu chia sẻ chung mộttage.

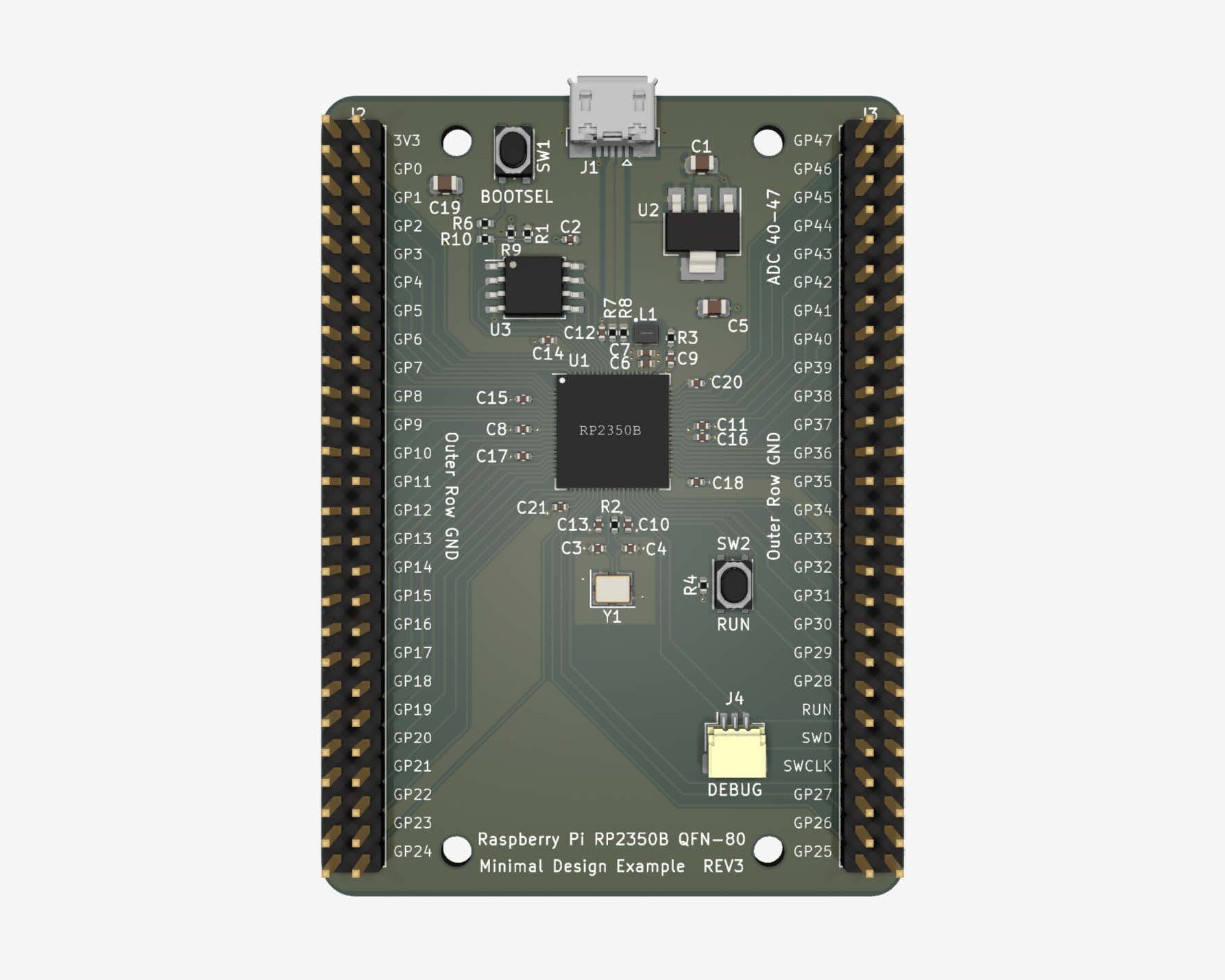

Mỗi chip có 30 GPIO, bốn trong số đó cũng được kết nối với ADC và có kích thước 7x7mm. Mặc dù vậy, RP2350A không phải là sự thay thế ngay lập tức cho RP2040 vì số chân trên mỗi chip là khác nhau. Ngược lại, chip QFN-80 hiện có 48 GPIO và tám trong số này hiện có khả năng ADC. Do đó, hiện chúng ta có hai bo mạch Minimal; một cho các thiết bị 60 chân và một cho các thiết bị 80 chân. Các bo mạch Minimal này chủ yếu được thiết kế cho các bộ phận không có đèn flash bên trong (RP2350), tuy nhiên các thiết kế này có thể dễ dàng được sử dụng với các thiết bị flash bên trong (RP2354) chỉ bằng cách bỏ bộ nhớ flash trên bo mạch hoặc thậm chí sử dụng nó như một thiết bị flash thứ cấp (sẽ nói thêm về điều này sau). Có rất ít sự khác biệt giữa hai bo mạch, ngoại trừ thực tế là phiên bản QFN-80 có các hàng đầu cắm dài hơn để chứa GPIO bổ sung và do đó bo mạch lớn hơn.

Ngoài gói sản phẩm, sự khác biệt lớn nhất ở cấp độ bo mạch giữa dòng RP235x và RP2040 là nguồn điện. Dòng RP235x có một số chân nguồn mới và bộ điều chỉnh bên trong khác. Bộ điều chỉnh tuyến tính 100mA của RP2040 đã được thay thế bằng bộ điều chỉnh chuyển mạch 200mA và do đó, nó yêu cầu một số mạch rất cụ thể và không ít sự cẩn thận với bố cục. Chúng tôi thực sự khuyên bạn nên theo dõi chặt chẽ bố cục và lựa chọn linh kiện của chúng tôi; chúng tôi đã trải qua nỗi đau khi phải thực hiện nhiều lần lặp lại thiết kế, vì vậy hy vọng bạn không phải làm vậy.

Hình 2. Bản vẽ 3D KiCad của RP2350B Thiết kế tối giảnample

Thiết kế

Mục đích của thiết kế tối giảnamples là tạo ra một cặp bo mạch đơn giản sử dụng dòng RP235x, có thể sản xuất dễ dàng và giá rẻ, mà không cần sử dụng các công nghệ PCB kỳ lạ không cần thiết. Do đó, các bo mạch Minimal có thiết kế 2 lớp, sử dụng các thành phần có sẵn phổ biến và tất cả được gắn ở mặt trên của bo mạch. Mặc dù sẽ rất tuyệt nếu sử dụng các thành phần lớn, dễ hàn bằng tay, nhưng bước nhỏ của chip QFN (0.4mm) có nghĩa là việc sử dụng một số thành phần thụ động 0402 (hệ mét 1005) là không thể tránh khỏi nếu muốn sử dụng tất cả các GPIO. Mặc dù hàn thủ công các thành phần 0402 không quá khó khăn với một chiếc máy hàn tốt, nhưng gần như không thể hàn QFN nếu không có thiết bị chuyên dụng.

Trong vài phần tiếp theo, tôi sẽ cố gắng giải thích mục đích của mạch bổ sung và hy vọng chúng ta sẽ đưa ra được những lựa chọn như vậy. Vì thực ra tôi sẽ nói về hai thiết kế riêng biệt, mỗi thiết kế cho một kích thước gói, nên tôi đã cố gắng giữ mọi thứ đơn giản nhất có thể. Trong khả năng có thể, tất cả các tham chiếu thành phần cho hai bo mạch đều giống hệt nhau, vì vậy nếu tôi tham chiếu đến U1, R1, v.v., thì nó có liên quan như nhau đến cả hai bo mạch. Ngoại lệ rõ ràng là khi thành phần chỉ nằm trên một trong hai bo mạch (trong mọi trường hợp, điều này sẽ nằm trên biến thể 80 chân lớn hơn), thì thành phần đang đề cập sẽ chỉ nằm trên thiết kế QFN-80; ví dụample, R13 chỉ xuất hiện trên bảng này.

Chương 2. Quyền lực

Nguồn điện của dòng RP235x và RP2040 có đôi chút khác biệt trong lần này, mặc dù trong cấu hình đơn giản nhất, nó vẫn cần hai nguồn điện, 3.3V và 1.1V. Dòng RP235x đồng thời ngốn điện hơn, vì hiệu suất cao hơn và cũng tiết kiệm hơn (khi ở trạng thái công suất thấp) so với thế hệ trước, do đó bộ điều chỉnh tuyến tính trên RP2040 đã được nâng cấp bằng bộ điều chỉnh chuyển mạch. Điều này cho phép chúng ta có hiệu suất công suất cao hơn ở dòng điện cao hơn (lên đến 200mA so với 100mA trước đây).

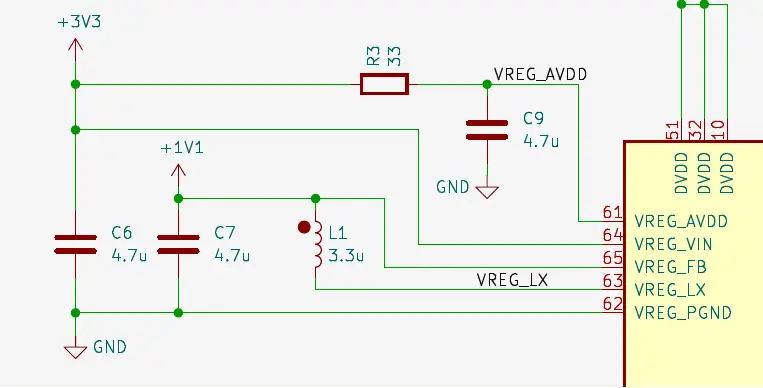

vol mới trên chiptagcơ quan quản lý điện tử

Hình 3. Sơ đồ mặt cắt cho thấy mạch điều chỉnh bên trong

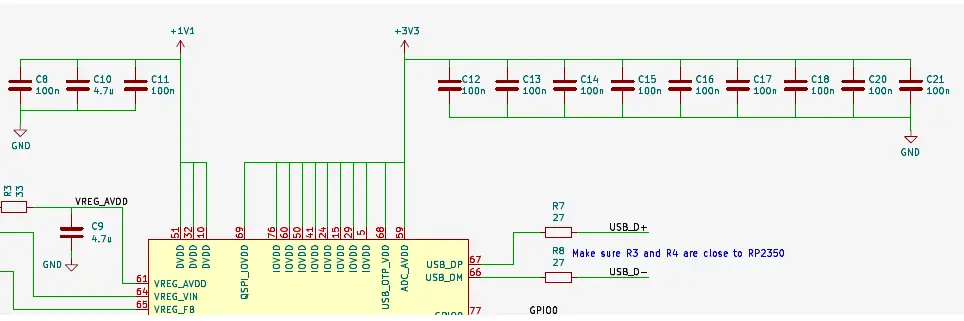

Bộ điều chỉnh tuyến tính của RP2040 có hai chân, đầu vào 3.3V và đầu ra 1.1V để cung cấp cho DVDD trên chip. Lần này, bộ điều chỉnh của dòng RP235x có năm chân và cần một số thành phần bên ngoài để hoạt động. Mặc dù điều này có vẻ hơi thụt lùi về mặt khả năng sử dụng, nhưng bộ điều chỉnh chuyển mạch có lợi thếtage có hiệu suất sử dụng điện năng cao hơn ở dòng điện tải cao hơn.

Như tên gọi của nó, bộ điều chỉnh này nhanh chóng bật và tắt một bóng bán dẫn bên trong kết nối với điện áp đầu vào 3.3V.tage (VREG_VIN) đến chân VREG_LX và với sự trợ giúp của cuộn cảm (L1) và tụ điện đầu ra (C7), nó có thể tạo ra một vol đầu ra DCtage đã được hạ xuống từ đầu vào. Chân VREG_FB theo dõi vol đầu ratage, và điều chỉnh tỷ lệ bật/tắt của chu kỳ chuyển mạch, để đảm bảo rằng âm lượng cần thiếttage được duy trì. Khi dòng điện lớn được chuyển từ VREG_VIN sang VREG_LX, cần có tụ điện lớn (C6) gần đầu vào, do đó chúng ta không làm xáo trộn nguồn cung cấp 3.3V quá nhiều. Nói về các dòng điện chuyển mạch lớn này, bộ điều chỉnh cũng đi kèm với kết nối trở về mặt đất của riêng nó, VREG_PGND. Tương tự như với VREG_VIN và VREG_LX, bố cục của kết nối này rất quan trọng và trong khi VREG_PGND phải kết nối với GND chính, thì phải thực hiện theo cách mà tất cả các dòng điện chuyển mạch lớn trở về trực tiếp chân PGND, mà không làm nhiễu phần còn lại của GND quá nhiều.

Chân cuối cùng là VREG_AVDD, cung cấp cho mạch tương tự bên trong bộ điều chỉnh và rất nhạy cảm với nhiễu.

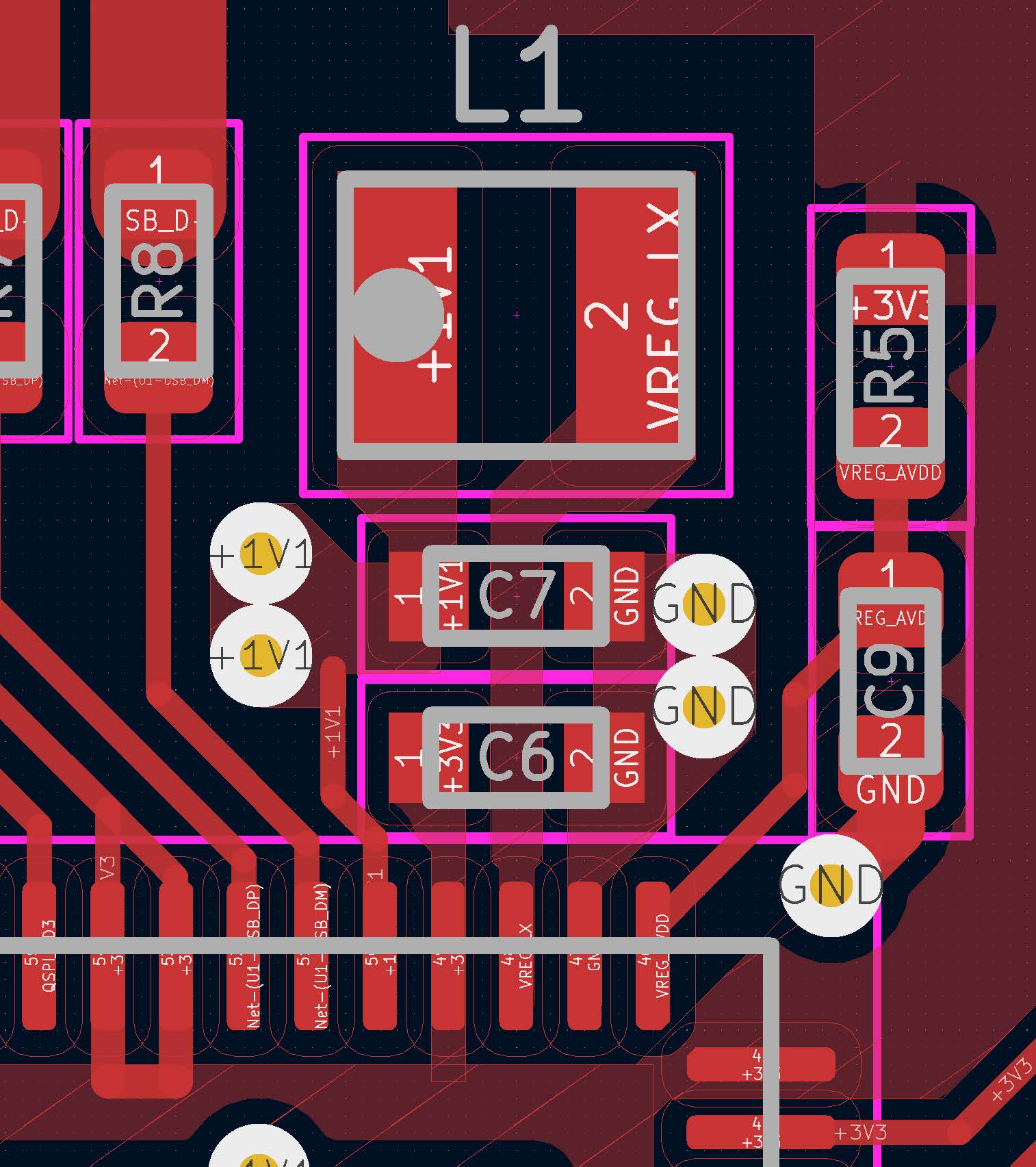

Hình 4. Sơ đồ mặt cắt cho thấy bố trí PCB của bộ điều chỉnh

- Bố cục của bộ điều chỉnh trên các bo mạch tối giản gần giống với Raspberry Pi Pico 2. Rất nhiều công sức đã được bỏ ra để thiết kế mạch này, với nhiều lần lặp lại PCB cần thiết để làm cho nó tốt nhất có thể. Mặc dù bạn có thể đặt các thành phần này theo nhiều cách khác nhau và vẫn khiến bộ điều chỉnh 'hoạt động' (tức là tạo ra một vol đầu ratage ở mức gần đúng, đủ tốt để chạy mã), chúng tôi thấy rằng bộ điều chỉnh của chúng tôi cần được xử lý theo đúng cách để giữ cho nó hoạt động tốt và khi nói đến hoạt động tốt, ý tôi là tạo ra mức đầu ra chính xác.tage trong một phạm vi điều kiện dòng tải khác nhau.

- Trong khi thực hiện các thí nghiệm của mình về vấn đề này, chúng tôi đã hơi thất vọng khi được nhắc nhở rằng thế giới vật lý bất tiện không phải lúc nào cũng có thể bị bỏ qua. Chúng tôi, với tư cách là các kỹ sư, phần lớn cố gắng và làm chính xác điều này; đơn giản hóa các thành phần, bỏ qua (thường là) các đặc tính vật lý không đáng kể và thay vào đó tập trung vào đặc tính mà chúng tôi quan tâm. Ví dụample, một điện trở đơn giản không chỉ có điện trở, mà còn có độ tự cảm, v.v. Trong trường hợp của chúng tôi, chúng tôi (tái) phát hiện ra rằng các cuộn cảm có một từ trường liên quan đến chúng và quan trọng là, bức xạ theo một hướng tùy thuộc vào cách cuộn dây được quấn và hướng dòng điện chạy qua. Chúng tôi cũng được nhắc nhở rằng một cuộn cảm được che chắn 'hoàn toàn' không có nghĩa là những gì bạn nghĩ. Từ trường bị suy yếu ở mức độ lớn, nhưng một số vẫn thoát ra ngoài. Chúng tôi thấy rằng hiệu suất của bộ điều chỉnh có thể được cải thiện đáng kể nếu cuộn cảm 'đúng chiều'.

- Hóa ra là từ trường phát ra từ một cuộn cảm 'ngược chiều' gây nhiễu tụ điện đầu ra của bộ điều chỉnh (C7), từ đó làm nhiễu mạch điều khiển bên trong RP2350. Với cuộn cảm ở đúng hướng, cùng với bố cục và lựa chọn linh kiện chính xác được sử dụng ở đây, thì vấn đề này sẽ biến mất. Chắc chắn sẽ có những bố cục, linh kiện, v.v. khác có thể hoạt động với cuộn cảm ở bất kỳ hướng nào, nhưng chúng rất có thể sẽ sử dụng nhiều không gian PCB hơn để làm như vậy. Chúng tôi đã cung cấp bố cục được đề xuất này để giúp mọi người tiết kiệm nhiều giờ kỹ thuật mà chúng tôi đã dành để phát triển và tinh chỉnh giải pháp nhỏ gọn và hoạt động tốt này.

- Quan trọng hơn, chúng tôi sẽ nói rằng nếu bạn chọn không sử dụng máy cũ của chúng tôiample, sau đó bạn tự chịu rủi ro. Giống như chúng tôi đã làm với RP2040 và mạch tinh thể, trong đó chúng tôi nhấn mạnh (tốt, đề xuất mạnh mẽ) bạn sử dụng một bộ phận cụ thể (chúng tôi sẽ làm lại như vậy trong phần tinh thể của tài liệu này).

- Hướng của các cuộn cảm nhỏ này hầu như bị bỏ qua trên toàn cầu, với hướng của cuộn dây không thể suy ra được, và cũng được phân phối ngẫu nhiên dọc theo một cuộn các thành phần. Các kích thước vỏ cuộn cảm lớn hơn thường có các dấu phân cực trên đó, tuy nhiên chúng tôi không thể tìm thấy các dấu phân cực phù hợp trong kích thước vỏ 0806 (hệ mét 2016) mà chúng tôi đã chọn. Để đạt được mục đích này, chúng tôi đã làm việc với Abracon để sản xuất một bộ phận 3.3μH có một dấu chấm để chỉ ra phân cực và quan trọng là được đưa vào một cuộn với tất cả chúng được căn chỉnh theo cùng một cách. Các TBD (hoặc sẽ sớm được) cung cấp cho công chúng từ các nhà phân phối. Như đã đề cập trước đó, nguồn cung cấp VREG_AVDD rất nhạy cảm với nhiễu và do đó cần phải được lọc. Chúng tôi thấy rằng vì VREG_AVDD chỉ tiêu thụ khoảng 200μA, nên bộ lọc RC 33Ω và 4.7μF là đủ.

- Tóm lại, các thành phần được sử dụng sẽ là…

- C6, C7 & C9 – 4.7μF (0402, 1005 mét)

- L1 – Abracon TBD (0806, hệ mét 2016)

- R3 – 33Ω (0402, 1005 mét)

- Bảng dữ liệu RP2350 có thảo luận chi tiết hơn về các khuyến nghị về bố trí bộ điều chỉnh, vui lòng xem Linh kiện bên ngoài và yêu cầu về bố trí PCB.

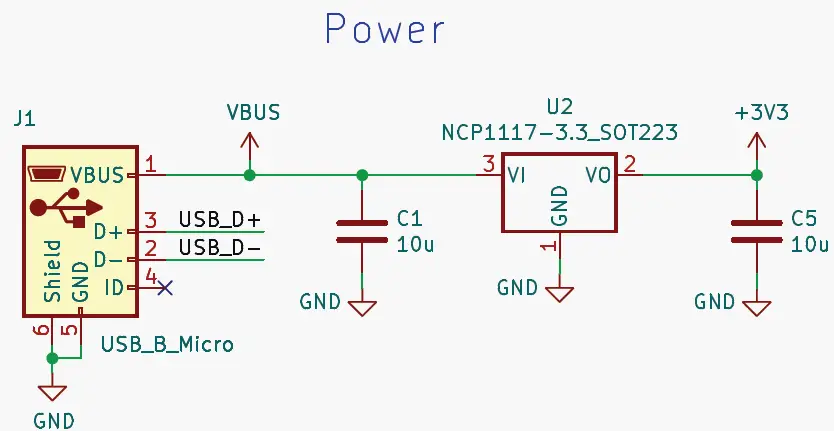

Nguồn cung cấp đầu vào

Kết nối nguồn điện đầu vào cho thiết kế này là thông qua chân VBUS 5V của đầu nối Micro-USB (được gắn nhãn J1 trong Hình 5). Đây là phương pháp phổ biến để cấp nguồn cho các thiết bị điện tử và điều này có ý nghĩa ở đây, vì RP2350 có chức năng USB, chúng ta sẽ đấu dây vào các chân dữ liệu của đầu nối này. Vì chúng ta chỉ cần 3.3V cho thiết kế này (nguồn cung cấp 1.1V đến từ bên trong), chúng ta cần hạ nguồn cung cấp USB 5V đầu vào, trong trường hợp này, sử dụng một vol ngoài kháctage regulator, trong trường hợp này là bộ điều chỉnh tuyến tính (hay còn gọi là bộ điều chỉnh Low Drop Out, hay LDO). Trước đây đã ca ngợi những ưu điểm của việc sử dụng bộ điều chỉnh chuyển mạch hiệu quả, thì việc sử dụng một bộ điều chỉnh chuyển mạch ở đây cũng có thể là một lựa chọn khôn ngoan, nhưng tôi đã chọn sự đơn giản. Đầu tiên, sử dụng LDO hầu như luôn dễ dàng hơn. Không cần tính toán để tìm ra kích thước cuộn cảm bạn nên sử dụng hoặc tụ điện đầu ra lớn như thế nào và cách bố trí thường cũng đơn giản hơn nhiều. Thứ hai, mục đích ở đây không phải là tiết kiệm từng giọt điện năng; nếu có, tôi sẽ nghiêm túc cân nhắc sử dụng bộ điều chỉnh chuyển mạch và bạn có thể tìm thấy mộtample của việc thực hiện như vậy trên Raspberry Pi Pico 2. Và thứ ba, tôi có thể chỉ cần 'mượn' mạch mà tôi đã sử dụng trước đó trên phiên bản RP2040 của bo mạch Minimal. NCP1117 (U2) được chọn ở đây có đầu ra cố định là 3.3V, có sẵn rộng rãi và có thể cung cấp dòng điện lên đến 1A, đủ cho hầu hết các thiết kế. Khi xem bảng dữ liệu của NCP1117, chúng ta thấy rằng thiết bị này yêu cầu tụ điện 10μF ở đầu vào và một tụ điện khác ở đầu ra (C1 và C5).

Tụ điện tách rời

Hình 6. Sơ đồ phần hiển thị các đầu vào nguồn điện RP2350, voltagbộ điều chỉnh và tụ tách ghép

Một khía cạnh khác của thiết kế nguồn điện là tụ điện tách ghép cần thiết cho RP2350. Chúng cung cấp hai chức năng cơ bản. Đầu tiên, chúng lọc nhiễu nguồn điện và thứ hai, cung cấp nguồn điện cục bộ mà các mạch bên trong RP2350 có thể sử dụng trong thời gian ngắn. Điều này ngăn chặn voltage mức ở vùng lân cận ngay lập tức không bị giảm quá nhiều khi nhu cầu dòng điện đột ngột tăng. Vì lý do này, điều quan trọng là phải đặt bộ tách ghép gần các chân nguồn. Thông thường, chúng tôi khuyên bạn nên sử dụng tụ điện 100nF cho mỗi chân nguồn, tuy nhiên, chúng tôi không tuân theo quy tắc này trong một vài trường hợp.

Hình 7. Phần bố trí hiển thị định tuyến và tách rời RP2350

- Đầu tiên, để có đủ không gian cho tất cả các chân chip có thể được định tuyến ra ngoài, tránh xa thiết bị, chúng ta phải thỏa hiệp với số lượng tụ điện tách rời mà chúng ta có thể sử dụng. Trong thiết kế này, chân 53 và 54 của RP2350A (chân 68 và 69 của RP2350B) chia sẻ một tụ điện duy nhất (C12 trong Hình 7 và Hình 6), vì không có nhiều không gian ở phía đó của thiết bị và các thành phần và bố cục của bộ điều chỉnh được ưu tiên.

- Thiếu không gian này có thể được khắc phục phần nào nếu chúng ta sử dụng công nghệ phức tạp/đắt tiền hơn, chẳng hạn như các thành phần nhỏ hơn hoặc PCB bốn lớp với các thành phần ở cả mặt trên và mặt dưới. Đây là một sự đánh đổi về thiết kế; chúng ta đã giảm độ phức tạp và chi phí, với cái giá phải trả là có ít điện dung tách rời hơn và các tụ điện cách xa chip hơn một chút so với mức tối ưu (điều này làm tăng độ tự cảm). Điều này có thể có tác dụng hạn chế tốc độ tối đa mà thiết kế có thể hoạt động, vì voltagNguồn cung cấp có thể trở nên quá ồn và giảm xuống dưới mức âm lượng tối thiểu được phéptage; nhưng đối với hầu hết các ứng dụng, sự đánh đổi này có thể chấp nhận được.

- Độ lệch khác so với quy tắc 100nF là để chúng ta có thể cải thiện thêm voltagHiệu suất của bộ điều chỉnh; chúng tôi khuyên bạn nên sử dụng 4.7μF cho C10, được đặt ở phía bên kia của chip so với bộ điều chỉnh.

Chương 3. Bộ nhớ Flash

Đèn flash chính

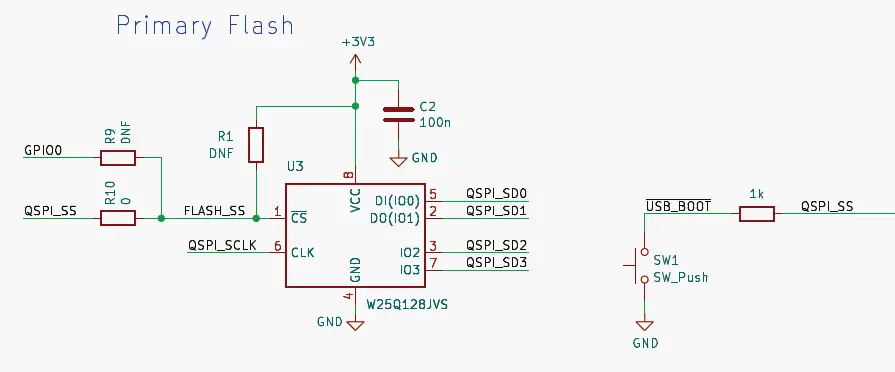

Hình 8. Sơ đồ phần hiển thị bộ nhớ flash chính và mạch USB_BOOT

- Để có thể lưu trữ mã chương trình mà RP2350 có thể khởi động và chạy, chúng ta cần sử dụng bộ nhớ flash, cụ thể là bộ nhớ flash SPI quad. Thiết bị được chọn ở đây là thiết bị W25Q128JVS (U3 trong Hình 8), là chip 128Mbit (16MB). Đây là kích thước bộ nhớ lớn nhất mà RP2350 có thể hỗ trợ. Nếu ứng dụng cụ thể của bạn không cần nhiều dung lượng lưu trữ, thì có thể sử dụng bộ nhớ nhỏ hơn, rẻ hơn thay thế.

- Vì bus dữ liệu này có thể có tần số khá cao và được sử dụng thường xuyên, các chân QSPI của RP2350 phải được nối trực tiếp với đèn flash, sử dụng các kết nối ngắn để duy trì tính toàn vẹn của tín hiệu và cũng để giảm nhiễu xuyên âm trong các mạch xung quanh. Nhiễu xuyên âm là nơi các tín hiệu trên một mạng mạch có thể gây ra vol không mong muốntagtrên mạch điện lân cận, có khả năng gây ra lỗi.

- Tín hiệu QSPI_SS là một trường hợp đặc biệt. Nó được kết nối trực tiếp với đèn flash, nhưng nó cũng có hai điện trở (thực ra là bốn, nhưng tôi sẽ nói đến sau) được kết nối với nó. Đầu tiên (R1) là một điện trở kéo lên nguồn cung cấp 3.3V. Bộ nhớ flash yêu cầu đầu vào chọn chip phải ở cùng một mức voltage là chân cung cấp 3.3V của riêng nó khi thiết bị được cấp nguồn, nếu không, nó sẽ không hoạt động chính xác. Khi RP2350 được cấp nguồn, chân QSPI_SS của nó sẽ tự động mặc định là kéo lên, nhưng có một khoảng thời gian ngắn trong quá trình bật mà trạng thái của chân QSPI_SS không thể được đảm bảo. Việc bổ sung một điện trở kéo lên đảm bảo rằng yêu cầu này sẽ luôn được đáp ứng. R1 được đánh dấu là DNF (Không phù hợp) trên sơ đồ, vì chúng tôi thấy rằng với thiết bị flash cụ thể này, việc kéo lên bên ngoài là không cần thiết. Tuy nhiên, nếu sử dụng một đèn flash khác, việc có thể chèn một điện trở 10kΩ ở đây có thể trở nên quan trọng, vì vậy nó đã được bao gồm để phòng ngừa.

- Điện trở thứ hai (R6) là điện trở 1kΩ, được kết nối với nút nhấn (SW1) có nhãn 'USB_BOOT'. Điều này là do chân QSPI_SS được sử dụng như một 'dây đeo khởi động'; RP2350 kiểm tra giá trị của I/O này trong chuỗi khởi động và nếu thấy giá trị là logic 0, thì RP2350 sẽ trở lại chế độ BOOTSEL, trong đó RP2350 tự biểu diễn như một thiết bị lưu trữ USB và mã có thể được sao chép trực tiếp vào đó. Nếu chúng ta chỉ cần nhấn nút, chúng ta kéo chân QSPI_SS xuống đất và nếu thiết bị sau đó được đặt lại (ví dụ bằng cách chuyển đổi chân RUN), RP2350 sẽ khởi động lại ở chế độ BOOTSEL thay vì cố gắng chạy nội dung của đèn flash. Các điện trở này, R2 và R6 (R9 và R10 cũng vậy), nên được đặt gần chip flash để tránh các đường dẫn bằng đồng bổ sung có thể ảnh hưởng đến tín hiệu.

- Tất cả những điều trên đều áp dụng cụ thể cho RP2350, không có flash bên trong. Tất nhiên, các thiết bị RP2354 có bộ nhớ flash 2MB bên trong, do đó không cần bộ nhớ U3 bên ngoài, do đó U3 có thể được gỡ bỏ an toàn khỏi sơ đồ mạch hoặc chỉ cần để nguyên không lắp. Trong cả hai trường hợp này, chúng ta vẫn muốn giữ công tắc USB_BOOT được kết nối với QSPI_SS để chúng ta vẫn có thể vào chế độ khởi động USB.

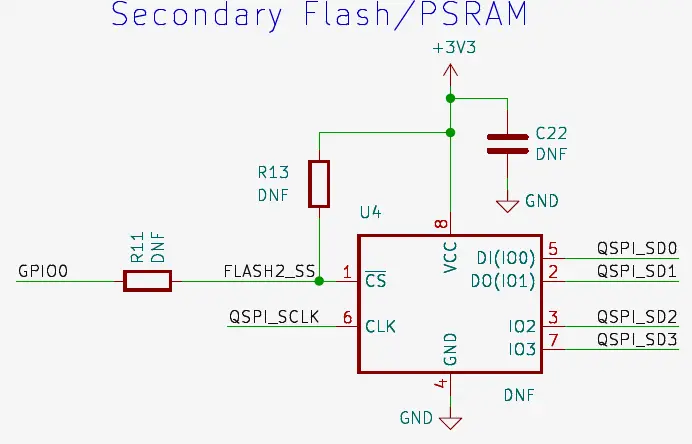

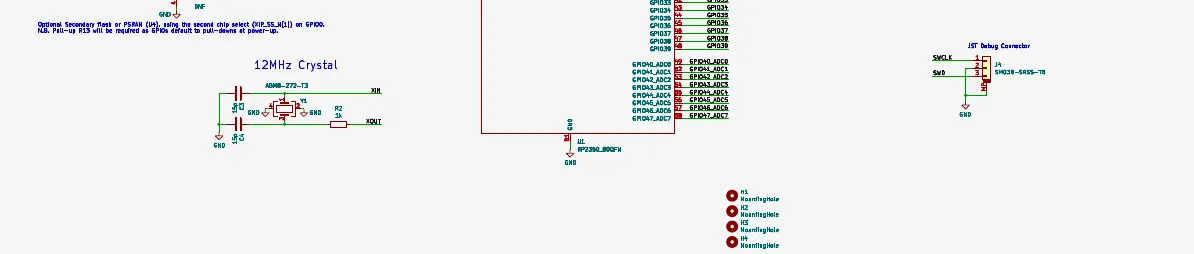

Flash thứ cấp hoặc PSRAM

- Dòng RP235x hiện hỗ trợ thiết bị bộ nhớ thứ hai sử dụng cùng chân QSPI, với GPIO cung cấp chức năng chọn chip bổ sung. Vì vậy, nếu chúng ta sử dụng RP2354 (có flash bên trong), thì chúng ta có thể sử dụng U3 làm flash thứ cấp hoặc thậm chí thay thế bằng thiết bị PSRAM. Để thực hiện việc này, chúng ta cần ngắt kết nối QSPI_SS khỏi U3 và thay vào đó kết nối nó với GPIO phù hợp. GPIO gần nhất có khả năng là chip select (XIP_CS1n) là GPIO0, vì vậy bằng cách loại bỏ 0Ω khỏi R10 và lắp nó vào R9, giờ đây chúng ta có thể truy cập U3 ngoài flash trên chip. Để tận dụng tối đatagTrong tính năng này, chúng ta có hai thiết bị bộ nhớ ngoài để các bộ phận RP2350 không có đèn flash có thể được hưởng lợi, bo mạch Minimal lớn hơn trong hai bo mạch, dành cho RP2350B, bao gồm một dấu chân tùy chọn (U4) cho một chip nhớ bổ sung.

Hình 9. Sơ đồ mặt cắt hiển thị thiết bị bộ nhớ thứ cấp tùy chọn

Để có thể sử dụng thiết bị này, rõ ràng là nó phải được lắp đầy, cũng như R11 (0Ω) và R13 (10KΩ). Việc bổ sung R11 kết nối GPIO0 (tín hiệu XIP_CS1n) với chip select của bộ nhớ thứ hai. Lần này chắc chắn cần phải kéo lên trên chân chip select, vì trạng thái mặc định của GPIO0 sẽ được kéo xuống mức thấp khi bật nguồn, điều này sẽ khiến thiết bị flash của chúng ta bị hỏng. C22 cũng cần thiết để cung cấp nguồn điện cục bộ tách rời cho U4.

Chip flash được hỗ trợ

Chuỗi đầu dò flash ban đầu, được sử dụng bởi phần dưới để trích xuất s thứ haitage từ flash, sử dụng lệnh đọc tuần tự 03h, với địa chỉ 24 bit và xung nhịp tuần tự khoảng 1MHz. Nó lặp đi lặp lại tuần hoàn qua bốn kết hợp của cực tính xung nhịp và pha xung nhịp, tìm kiếm một giây hợp lệ stage Tổng kiểm tra CRC32.

Như thứ hai stage sau đó có thể tự do cấu hình thực thi tại chỗ bằng cùng lệnh đọc nối tiếp 03h, RP2350 có thể thực hiện thực thi tại chỗ flash được lưu trong bộ nhớ đệm với bất kỳ chip nào hỗ trợ đọc nối tiếp 03h với địa chỉ 24 bit, bao gồm hầu hết các thiết bị flash dòng 25. SDK cung cấp một ví dụampgiây thứ haitage đối với CPOL=0 CPHA=0, tại https://github.com/raspberrypi/pico-sdk/blob/master/src/rp2350/boot_stage2/boot2_generic_03h.S. Để hỗ trợ lập trình flash bằng các lệnh ở phía dưới, thiết bị cũng phải phản hồi các lệnh sau:

- 02h Chương trình trang 256 byte

- 05h trạng thái đăng ký đọc

- 06h thiết lập chốt cho phép ghi

- Xóa sector 20kB 4h

RP2350 cũng hỗ trợ nhiều chế độ truy cập SPI kép và QSPI. Ví dụamplà, https://github.com/raspberrypi/pico-sdk/blob/master/src/rp2350/boot_stage2/boot2_w25q080.S cấu hình thiết bị Winbond W25Q-series cho chế độ đọc liên tục quad-IO, trong đó RP2350 gửi địa chỉ quad-IO (không có tiền tố lệnh) và bộ nhớ flash phản hồi bằng dữ liệu quad-IO.

Cần thận trọng với chế độ flash XIP khi thiết bị flash ngừng phản hồi với các lệnh tuần tự chuẩn, như chế độ đọc liên tục Winbond đã đề cập ở trên. Điều này có thể gây ra sự cố khi RP2350 được đặt lại, nhưng thiết bị flash không được cấp nguồn, vì khi đó flash sẽ không phản hồi với chuỗi dò flash của bootrom. Trước khi phát lệnh đọc tuần tự 03h, bootrom luôn phát chuỗi cố định sau, đây là chuỗi nỗ lực tốt nhất để ngừng XIP trên một loạt thiết bị flash:

- CSn=1, IO[3:0]=4'b0000 (thông qua kéo xuống để tránh tranh chấp), phát hành ×32 đồng hồ

- CSn=0, IO[3:0]=4'b1111 (thông qua pull up để tránh xung đột), phát hành ×32 đồng hồ

- CSn=1

- CSn=0, MOSI=1'b1 (điều khiển Z thấp, tất cả các I/O khác Hi-Z), phát hành ×16 xung nhịp

Nếu thiết bị bạn chọn không phản hồi trình tự này khi ở chế độ đọc liên tục, thì bạn phải giữ thiết bị ở trạng thái mà mỗi lần truyền dữ liệu đều được thêm tiền tố bằng lệnh nối tiếp, nếu không, RP2350 sẽ không thể phục hồi sau khi thiết lập lại nội bộ.

Để biết thêm chi tiết về QSPI, vui lòng xem Giao diện bộ nhớ QSPI (QMI) trong bảng dữ liệu RP2350.

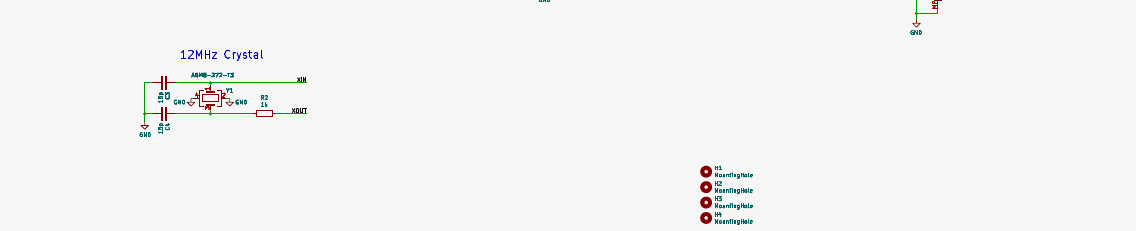

Chương 4. Bộ dao động tinh thể

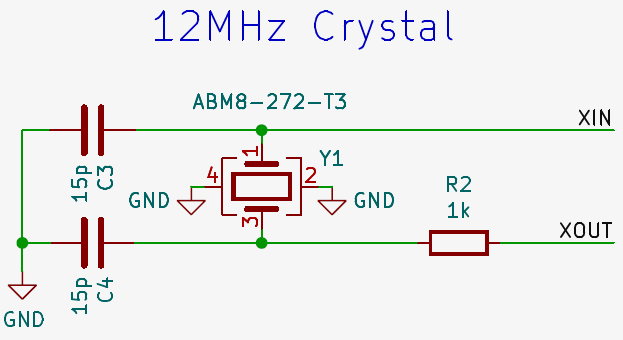

Hình 10. Sơ đồ mặt cắt cho thấy bộ dao động tinh thể và tụ điện tải

- Nói một cách chính xác, RP2350 thực sự không cần nguồn xung nhịp bên ngoài vì nó có bộ dao động bên trong riêng. Tuy nhiên, vì tần số của bộ dao động bên trong này không được xác định hoặc kiểm soát tốt, thay đổi tùy theo từng chip cũng như với các mức cung cấp khác nhautages và nhiệt độ, nên sử dụng nguồn tần số bên ngoài ổn định. Các ứng dụng dựa vào tần số chính xác không thể thực hiện được nếu không có nguồn tần số bên ngoài, USB là một ví dụ chínhamplà.

- Việc cung cấp nguồn tần số bên ngoài có thể được thực hiện theo một trong hai cách: hoặc bằng cách cung cấp nguồn xung nhịp với đầu ra CMOS (sóng vuông của vol IOVDDtage) vào chân XIN, hoặc bằng cách sử dụng tinh thể 12MHz được kết nối giữa

- XIN và XOUT. Sử dụng tinh thể là lựa chọn được ưu tiên ở đây vì chúng vừa tương đối rẻ vừa rất chính xác.

- Tinh thể được chọn cho thiết kế này là ABM8-272-T3 (Y1 trong Hình 10). Đây là tinh thể 12MHz giống như được sử dụng trên Raspberry Pi Pico và Raspberry Pi Pico 2. Chúng tôi đặc biệt khuyên bạn nên sử dụng tinh thể này cùng với mạch đi kèm để đảm bảo đồng hồ bắt đầu nhanh trong mọi điều kiện mà không làm hỏng tinh thể. Tinh thể có dung sai tần số 30ppm, đủ tốt cho hầu hết các ứng dụng. Cùng với dung sai tần số +/-30ppm, nó có ESR tối đa là 50Ω và điện dung tải là 10pF, cả hai đều có ảnh hưởng đến việc lựa chọn các thành phần đi kèm.

- Để tinh thể dao động ở tần số mong muốn, nhà sản xuất chỉ định điện dung tải mà nó cần để thực hiện như vậy và trong trường hợp này, điện dung tải là 10pF. Điện dung tải này đạt được bằng cách đặt hai tụ điện có giá trị bằng nhau, một tụ ở mỗi bên của tinh thể xuống đất (C3 và C4). Từ điểm của tinh thể view, các tụ điện này được kết nối nối tiếp giữa hai đầu cực của nó. Lý thuyết mạch cơ bản cho chúng ta biết rằng chúng kết hợp để tạo ra điện dung (C3*C4)/(C3+C4), và vì C3=C4, nên nó chỉ đơn giản là C3/2. Trong ví dụ nàyample, chúng ta đã sử dụng tụ điện 15pF, vì vậy tổ hợp nối tiếp là 7.5pF. Ngoài điện dung tải cố ý này, chúng ta cũng phải thêm một giá trị cho điện dung bổ sung không cố ý hoặc điện dung ký sinh, mà chúng ta nhận được từ các đường PCB và các chân XIN và XOUT của RP2350. Chúng ta sẽ giả sử giá trị này là 3pF và vì điện dung này song song với C3 và C4, chúng ta chỉ cần thêm giá trị này để có tổng điện dung tải là 10.5pF, đủ gần với mục tiêu là 10pF. Như bạn có thể thấy, điện dung ký sinh của các đường PCB là một yếu tố và do đó chúng ta cần giữ chúng nhỏ để không làm đảo lộn tinh thể và ngăn nó dao động như mong muốn. Cố gắng giữ bố cục càng ngắn càng tốt.

- Cân nhắc thứ hai là ESR (điện trở nối tiếp tương đương) tối đa của tinh thể. Chúng tôi đã chọn một thiết bị có giá trị tối đa là 50Ω, vì chúng tôi thấy rằng giá trị này, cùng với điện trở nối tiếp 1kΩ (R2), là một giá trị tốt để ngăn tinh thể bị quá tải và bị hỏng khi sử dụng mức IOVDD là 3.3V. Tuy nhiên, nếu IOVDD nhỏ hơn 3.3V, thì dòng điện truyền động của các chân XIN/XOUT sẽ giảm và bạn sẽ thấy rằng ampbiên độ của tinh thể thấp hơn hoặc thậm chí có thể không dao động chút nào. Trong trường hợp này, cần sử dụng giá trị nhỏ hơn của điện trở nối tiếp. Bất kỳ độ lệch nào so với mạch tinh thể được hiển thị ở đây hoặc với mức IOVDD khác 3.3V sẽ cần phải thử nghiệm rộng rãi để đảm bảo rằng tinh thể dao động trong mọi điều kiện và khởi động đủ nhanh để không gây ra sự cố cho ứng dụng của bạn.

Tinh thể được đề xuất

- Đối với các thiết kế ban đầu sử dụng RP2350, chúng tôi khuyên bạn nên sử dụng Abracon ABM8-272-T3. Ví dụample, ngoài thiết kế tối thiểu example, hãy xem sơ đồ bo mạch Pico 2 trong Phụ lục B của Bảng dữ liệu Raspberry Pi Pico 2 và thiết kế Pico 2 files.

- Để có hiệu suất và độ ổn định tốt nhất trong phạm vi nhiệt độ hoạt động thông thường, hãy sử dụng Abracon ABM8-272-T3. Bạn có thể lấy ABM8-272-T3 trực tiếp từ Abracon hoặc từ một đại lý được ủy quyền. Pico 2 đã được điều chỉnh cụ thể cho ABM8-272-T3, có các thông số kỹ thuật sau:

- Ngay cả khi bạn sử dụng tinh thể có thông số kỹ thuật tương tự, bạn vẫn cần phải thử nghiệm mạch ở nhiều nhiệt độ khác nhau để đảm bảo tính ổn định.

- Bộ dao động tinh thể được cấp nguồn từ IOVDD voltage. Kết quả là, tinh thể Abracon và d cụ thể đóampđiện trở ing được điều chỉnh cho hoạt động 3.3V. Nếu bạn sử dụng một vol IO kháctage, bạn sẽ cần phải điều chỉnh lại.

- Bất kỳ thay đổi nào về thông số tinh thể đều có nguy cơ gây mất ổn định ở mọi thành phần được kết nối với mạch tinh thể.

- Nếu bạn không thể tìm được tinh thể được đề xuất trực tiếp từ Abracon hoặc người bán lại, hãy liên hệ ứng dụng@raspberrypi.com.

Chương 5. IOs

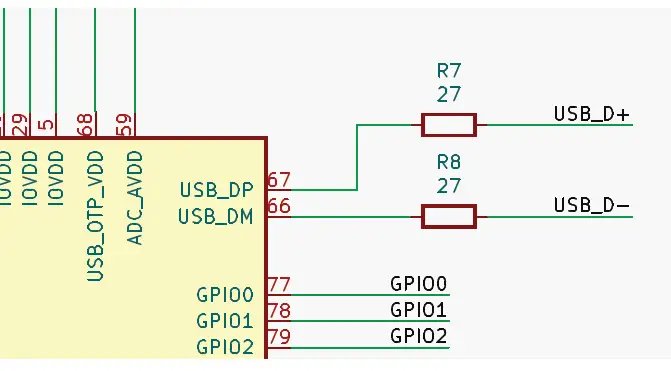

USB

Hình 11. Sơ đồ phần hiển thị các chân USB của RP2350 và đầu cuối nối tiếp

- RP2350 cung cấp hai chân để sử dụng cho USB tốc độ đầy đủ (FS) hoặc tốc độ thấp (LS), có thể là máy chủ hoặc thiết bị, tùy thuộc vào phần mềm được sử dụng. Như chúng ta đã thảo luận, RP2350 cũng có thể khởi động như một thiết bị lưu trữ USB, do đó, việc nối các chân này với đầu nối USB (J1 trong Hình 5) là hợp lý. Các chân USB_DP và USB_DM trên RP2350 không yêu cầu bất kỳ pull-up hoặc pull-down bổ sung nào (cần thiết để chỉ ra tốc độ, FS hoặc LS, hoặc liệu đó là máy chủ hay thiết bị), vì chúng được tích hợp sẵn vào I/O. Tuy nhiên, các I/O này yêu cầu điện trở kết thúc nối tiếp 27Ω (R7 và R8 trong Hình 11), được đặt gần chip, để đáp ứng thông số trở kháng USB.

- Mặc dù RP2350 bị giới hạn ở tốc độ dữ liệu đầy đủ (12Mbps), chúng ta nên thử và đảm bảo rằng trở kháng đặc trưng của các đường truyền (các đường đồng kết nối chip với đầu nối) gần với

- Thông số kỹ thuật USB là 90Ω (đo vi sai). Trên một bo mạch dày 1mm như thế này, nếu chúng ta sử dụng các đường ray rộng 0.8mm trên USB_DP và USB_DM, với khoảng cách 0.15mm giữa chúng, chúng ta sẽ có trở kháng đặc tính vi sai khoảng 90Ω. Điều này nhằm đảm bảo rằng các tín hiệu có thể truyền dọc theo các đường truyền này một cách sạch nhất có thể, giảm thiểu voltage phản xạ có thể làm giảm tính toàn vẹn của tín hiệu. Để các đường truyền này hoạt động bình thường, chúng ta cần đảm bảo rằng ngay bên dưới các đường truyền này là một mặt đất. Một khu vực đồng đất liền mạch, rắn chắc, kéo dài toàn bộ chiều dài của đường ray. Trong thiết kế này, hầu như toàn bộ lớp đồng dưới cùng được dành cho mặt đất và chúng tôi đặc biệt cẩn thận để đảm bảo rằng các đường ray USB chỉ đi qua mặt đất. Nếu chọn PCB dày hơn 1mm để xây dựng, thì chúng tôi có hai lựa chọn. Chúng tôi có thể thiết kế lại các đường truyền USB để bù cho khoảng cách lớn hơn giữa đường ray và mặt đất bên dưới (có thể là điều không thể về mặt vật lý) hoặc chúng tôi có thể bỏ qua nó và hy vọng điều tốt nhất. USB FS có thể khá dễ tính, nhưng hiệu quả của bạn có thể khác. Nó có thể hoạt động trong nhiều ứng dụng, nhưng có lẽ sẽ không tuân thủ tiêu chuẩn USB.

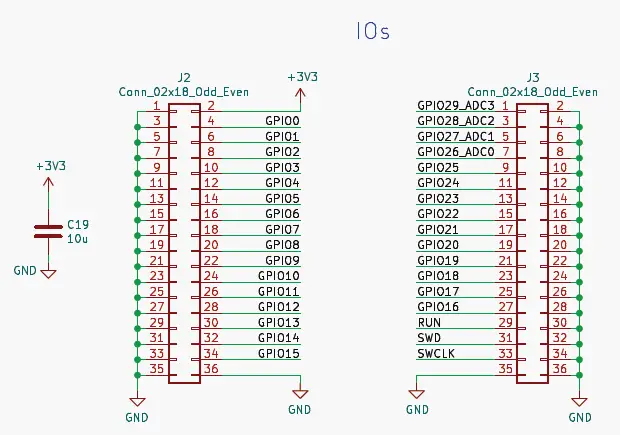

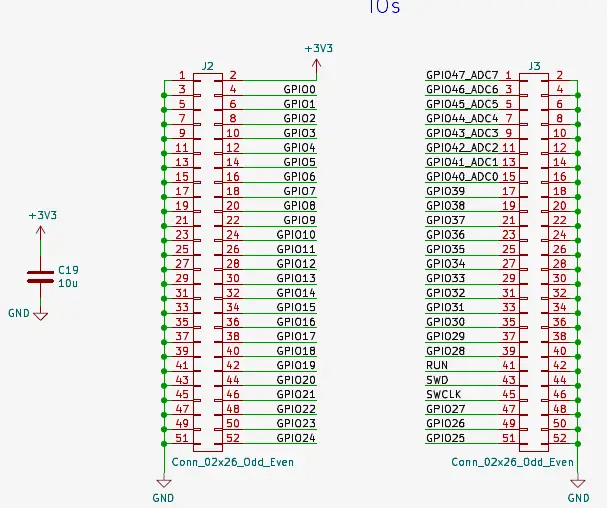

Tiêu đề I / O

Hình 12. Sơ đồ mặt cắt hiển thị các đầu cắm I/O 2.54mm của phiên bản QFN60

- Ngoài đầu nối USB đã đề cập ở trên, còn có một cặp đầu cắm 2.54mm hàng kép (J2 và J3 trong Hình 12), một đầu cắm ở mỗi bên của bo mạch, mà phần còn lại của I/O đã được kết nối. Có 30 GPIO trên RP2350A, trong khi có 48 GPIO trên RP2350B, do đó, các đầu cắm trên phiên bản bo mạch Minimal này lớn hơn để có thể có thêm chân cắm (xem Hình 13).

- Vì đây là thiết kế mục đích chung, không có ứng dụng cụ thể nào trong đầu, nên I/O đã được tạo sẵn để kết nối theo ý muốn của người dùng. Hàng chân bên trong trên mỗi đầu cắm là I/O và hàng ngoài cùng đều được kết nối với đất. Thực hành tốt là bao gồm nhiều đất trên các đầu nối I/O. Điều này giúp duy trì đất trở kháng thấp và cũng cung cấp nhiều đường dẫn trở về tiềm năng cho dòng điện đi đến và đi từ

- Kết nối I/O. Điều này rất quan trọng để giảm thiểu nhiễu điện từ có thể gây ra bởi dòng điện trở về của các tín hiệu chuyển mạch nhanh theo đường dẫn dài, lặp lại để hoàn thành mạch.

- Cả hai đầu cắm đều nằm trên cùng một lưới 2.54mm, giúp kết nối bo mạch này với các thứ khác, chẳng hạn như bảng mạch cắm, dễ dàng hơn. Bạn có thể cân nhắc chỉ lắp một đầu cắm một hàng thay vì đầu cắm hai hàng, bỏ qua hàng ngoài cùng của các kết nối đất, để lắp vào bảng mạch cắm thuận tiện hơn.

Hình 13. Sơ đồ mặt cắt hiển thị các đầu cắm I/O 2.54mm của phiên bản QFN80

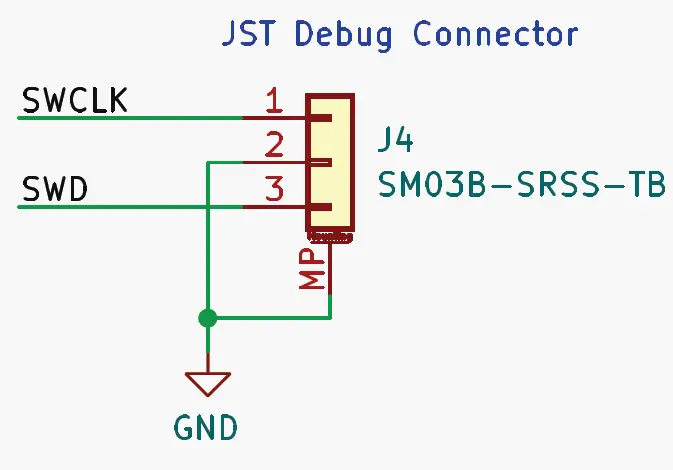

Đầu nối gỡ lỗi

Hình 14. Phần sơ đồ hiển thị đầu nối JST tùy chọn để gỡ lỗi SWD

Đối với gỡ lỗi trên chip, bạn có thể muốn kết nối với giao diện SWD của RP2350. Hai chân, SWD và SWCLK, có sẵn trên đầu cắm 2.54mm, J3, để cho phép đầu dò gỡ lỗi mà bạn chọn dễ dàng kết nối. Ngoài ra, tôi đã bao gồm một đầu cắm JST tùy chọn, cho phép kết nối dễ dàng với Đầu dò gỡ lỗi Raspberry Pi. Bạn không cần phải sử dụng đầu cắm này, các đầu cắm 2.54mm sẽ đủ nếu bạn có ý định gỡ lỗi phần mềm, nhưng tôi thấy làm như vậy thuận tiện hơn. Tôi đã chọn một đầu nối nằm ngang, chủ yếu là vì tôi thích vẻ ngoài của nó, ngay cả khi nó không nằm ở mép bảng, nhưng cũng có các đầu cắm thẳng đứng, mặc dù có diện tích hơi khác một chút.

Nút

Thiết kế Minimal hiện không chỉ có một mà là hai nút, trong khi phiên bản RP240 không có. Một nút để chọn khởi động USB như chúng ta đã thảo luận trước đó, nhưng nút thứ hai là nút 'reset', được nối với chân RUN. Cả hai nút này đều không thực sự cần thiết (mặc dù nút BOOTSEL sẽ phải được thay thế bằng một đầu cắm hoặc tương tự nếu cần chế độ khởi động USB) và có thể tháo ra nếu lo ngại về không gian hoặc chi phí, nhưng chúng chắc chắn giúp việc sử dụng RP2350 trở nên dễ chịu hơn nhiều.

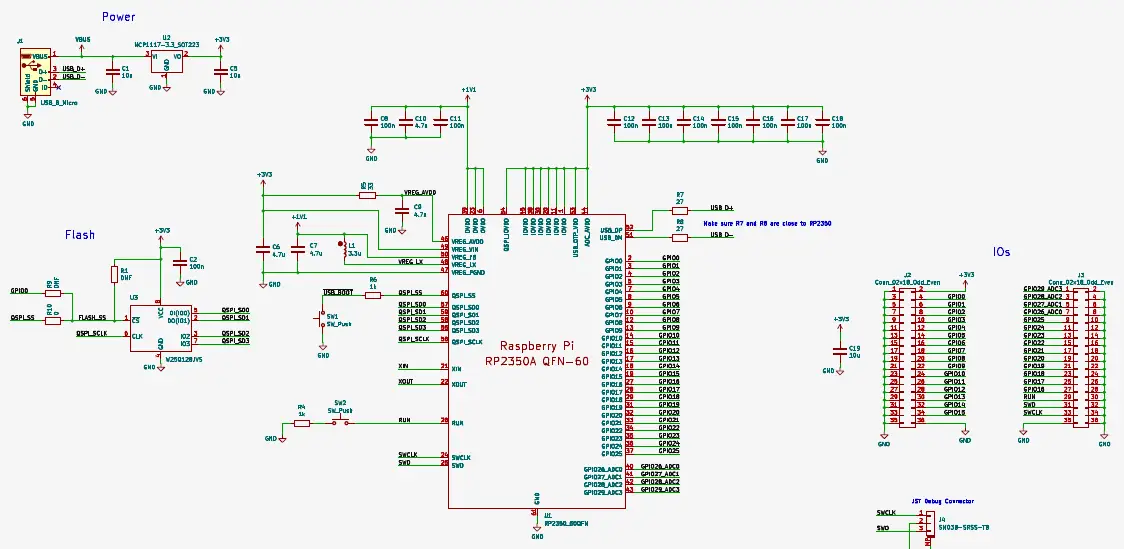

Phụ lục A: Sơ đồ hoàn chỉnh - Phiên bản RP2350A

Hình 15. Sơ đồ đầy đủ của Thiết kế tối thiểu cho RP2350A

Phụ lục B: Sơ đồ hoàn chỉnh - Phiên bản RP2350B

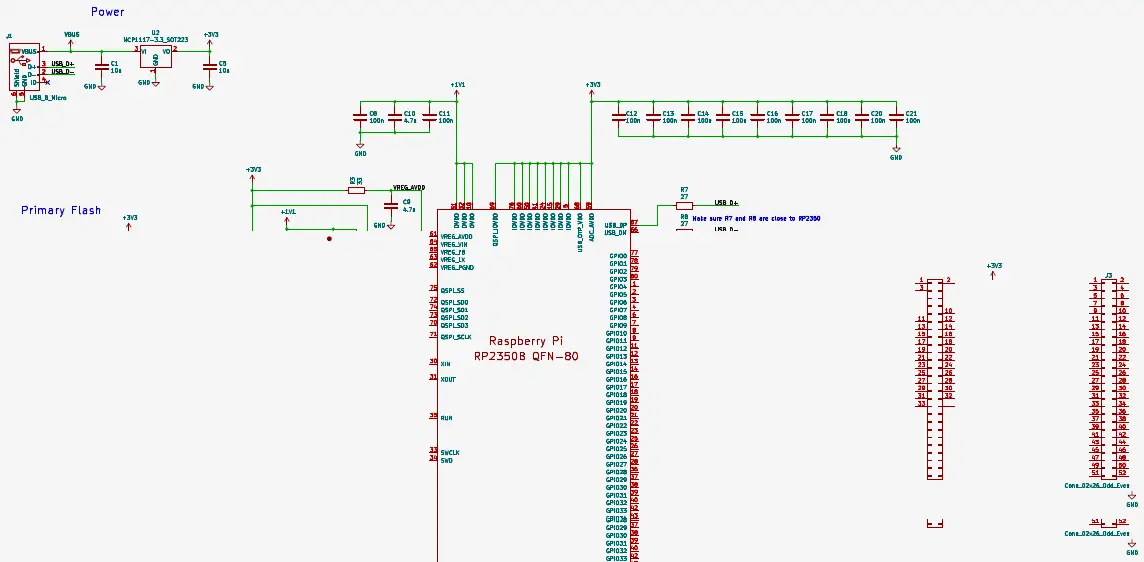

Hình 16. Sơ đồ đầy đủ của Thiết kế tối thiểu cho RP2350B

Phụ lục H: Lịch sử phát hành tài liệu

Ngày 8 tháng 2024 năm XNUMX

Phiên bản phát hành đầu tiên.

tôi Raspberry Pi

Raspberry Pi là nhãn hiệu của Raspberry Pi Ltd

Công ty TNHH Raspberry Pi

Tài liệu / Tài nguyên

|

Bộ vi điều khiển Raspberry Pi SC1631 Raspberry [tập tin pdf] Hướng dẫn sử dụng Vi điều khiển SC1631 Raspberry, SC1631, Vi điều khiển Raspberry, Vi điều khiển |