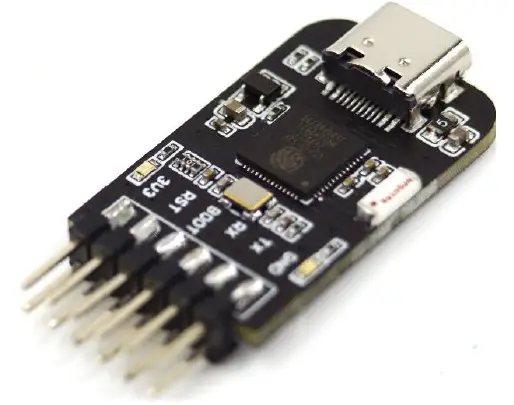

MuseLAB ESPLink v1.2 Debug Probe Tool

ESP لنڪ جو تعارف

ESP لنڪ هڪ ڊيبگ ٽول آهي Expressif جي ESP چپس لاءِ ٺهيل آهي MuseLab پاران ٺهيل آهي Espressif جي esp-usb-bridge جي بنياد تي، سڀ Espressif جي ESP چپس سپورٽ آهن، في الحال سپورٽ ڪري ٿي ESP8266/ESP32/ESP32-S2/ESP32-C3/ESP32-S3also ايسپريسف جي جديد چپس کي سپورٽ ڪرڻ لاءِ فرم ویئر کي اپڊيٽ ڪريو، يو ايس بي کان سيريل (روايتي استعمال سان مطابقت رکندڙ)، ڊريگ-اين-ڊراپ پروگرام، ۽ ج.tag ڊيبگ، ان کي ترقي ۽ امتحان لاء تمام آسان ڪيو. .

خاصيتون

USB-to-سيريل

روايتي استعمال سان مطابقت، esptool.py سان پروگرام ڪرڻ لاءِ استعمال ڪري سگھجي ٿو يا سيريل آئوٽ پٽ پيغام جي نگراني ڪري سگھجي ٿو. مثالampحوالن لاءِ:

$idf.py -p /dev/ttyACM0 فليش مانيٽر

$esptool.py -chip esp32c3 \

-p/dev/ttyACM0 \

-ب 115200 \

- کان اڳ = default_reset \

-بعد = هارڊ_ري سيٽ \

-نڌل \

لکو_ فليش \

-flash_mode dio \

-flash_freq 80m \

-flash_size 2MB \

0x0 esp32c3/bootloader.bin \

0x8000 esp32c3/partition-table.bin \

0x10000 esp32c3/blink_100.bin

ڇڪيو ۽ ڊراپ پروگرام

ESPLink سپورٽ drag-n-drop پروگرام، بورڊ تي پاور ٿيڻ کان پوءِ، ESPLink نالي هڪ ورچوئل USB ڊسڪ ظاهر ٿيندي، بس فليش تصوير کي ESPLink ۾ ڇڪيو، ڪجهه سيڪنڊن جو انتظار ڪريو، پوءِ ESPLink خود بخود پروگرام جو ڪم مڪمل ڪندو. اهو تمام آسان آهي ڇو ته ان کي ٻاهرين اوزارن تي ڀروسو ڪرڻ جي ضرورت ناهي ۽ ڪنهن به پليٽ فارم (Win/Linux/Mac .etc) تي سٺو ڪم ڪرڻ جي ضرورت ناهي، ڪجهه عام استعمال جا منظرنامو: جلدي تصديق، ڪلائوڊ سرور تي مرتب ڪريو ۽ ڪنهن به PC تي پروگرام، فرم ويئر اپ گريڊ جڏهن استعمال ڪيو وڃي تجارتي شين تي

نوٽ: فليش تصوير uf2 فارميٽ ۾ آهي، espressif جي سرڪاري ٽول idf.py $idf.py uf2 سان ٺاهي سگهجي ٿي

$cp build/uf2.bin /media/pi/ESPLink/

JTAG ڊيبگ

ESPLink سپورٽ جtag ESP32 سيريز چپ کي ڊيبگ ڪرڻ لاءِ انٽرفيس، اهو پراڊڪٽ ڊولپر لاءِ ڪارائتو آهي بگ کي درست ڪرڻ لاءِ جڏهن سسٽم حادثو، هتي حوالي لاءِ هدايتون آهن (هدف چپ ESP32-S2 آهي هتي اڳوڻي طور تيampلي)

Openocd انسٽال ڪريو

$git کلون https://github.com/espressif/openocd-esp32.git

$cd openocd-esp32

$./بوٽ اسٽريپ

$./ترتيب ڏيو

$make -j

$sudo انسٽال ڪريو

ESP32-S2 سان ڳنڍيو

pi@raspberrypi:~/oss/openocd-esp32 $ sudo ./src/openocd -s /home/pi/oss/openocd- esp32/tcl -f tcl/interface/esp_usb_bridge.cfg -f tcl/target/esp32s2.c اوپن آن-چپ ڊيبگر v0.11.0-esp32-20220411-5-g03cd2031 (2022-04-25-09:45) GNU GPL v2 تحت لائسنس يافته

بگ رپورٽن لاءِ، پڙهو

http://openocd.org/doc/doxygen/bugs.html

ڄاڻ: صرف هڪ ٽرانسپورٽ اختيار؛ خودڪار چونڊيو جيtag'

ڄاڻ: esp_usb_jtag: VID سيٽ 0x303a ۽ PID 0x1002 تي

ڄاڻ: esp_usb_jtag: قابليت بيان ڪندڙ 0x30a تي سيٽ ڪيو ويو

اڊاپٽر جي رفتار: 4000 kHz

خبردار: ٽرانسپورٽ "جيtag“ اڳ ۾ ئي چونڊيو ويو

ڄاڻ: ٽي سي ايل ڪنيڪشن لاءِ پورٽ 6666 تي ٻڌڻ

ڄاڻ: telnet ڪنيڪشن لاءِ پورٽ 4444 تي ٻڌڻ

ڄاڻ: esp_usb_jtag: سيريل (84F703D20134)

ڄاڻ: esp_usb_jtag: ڊوائيس مليو. بنيادي رفتار 750KHz، div رينج 1 کان 1

ڄاڻ: ڪلاڪ جي رفتار 750 kHz

ڄاڻ: جيTAG ٽيپ: esp32s2.cpu ٽيپ/ڊيوائس مليا: 0x120034e5 (mfg: 0x272 (Tensilica)، حصو: 0x2003، ver: 0x1)

ڄاڻ: esp32s2: ڊيبگ ڪنٽرولر ري سيٽ ڪيو ويو.

ڄاڻ: esp32s2: ڪور ري سيٽ ڪيو ويو.

ڄاڻ: 32 تي esp2s3333 لاءِ جي ڊي بي سرور شروع ڪري رهيو آهي

ڄاڻ: جي ڊي بي ڪنيڪشن لاءِ پورٽ 3333 تي ٻڌڻ

ڊيبگ

جڏهن ڪاميابي سان ڳنڍيو، ڊيبگ ڪرڻ لاء هڪ ٻيو ٽرنيمل کوليو، توهان استعمال ڪري سگهو ٿا gdb يا telnet، الڳ الڳ وضاحت هيٺ ڏنل آهي

Gdb سان ڊيبگ

$xtensa-esp32s2-elf-gdb -ex 'ٽارگٽ ريموٽ 127.0.0.1:3333' ./build/blink.elf

(gdb) ڄاڻ reg

(جي ڊي بي) ايس

(gdb) جاري رکو

telnet سان ڊيبگ

$telnet localhost 4444

ري سيٽ

رڪجڻ

reg

قدم

ٻيهر شروع ڪرڻ

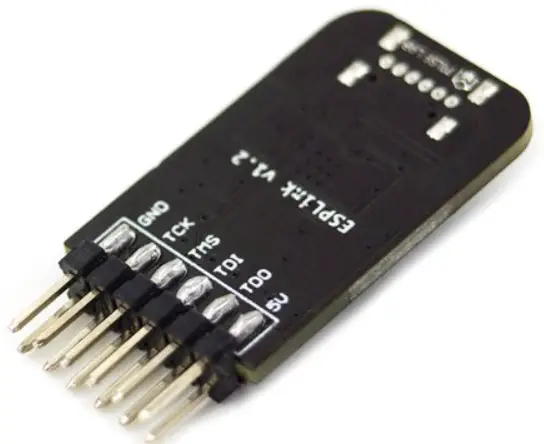

پن وضاحت

طاقت

جي اين ڊي، 3 وي 3,5، XNUMX وي

JTAG

TCK، TMS، TDI، TDO

UART

TX، RX

USB-سيريل TX ۽ RX

بوٽ

سيٽ لو، ۽ بورڊ کي ري سيٽ ڪريو، پوءِ بورڊ فليش پروگرام لاءِ بوٽ لوڊر ۾ داخل ٿيندو، نوٽ ڪريو ته BOOT ۽ RST ESPLink USB-Serial DTR ۽ RTS پاران ڪنٽرول ٿيل آهي، ٻين USB-سيريل چپ جهڙوڪ CP2102 ۽ CH340 سان گڏ.

دستاويز / وسيلا

|

MuseLAB ESPLink v1.2 Debug Probe Tool [pdf] استعمال ڪندڙ ھدايت ESPLink v1.2 Debug Probe Tool, ESPLink v1.2, Debug Probe Tool, Probe Tool |