रास्पबेरी Pi SC1631 रास्पबेरी माइक्रोकन्ट्रोलर

उत्पादन निर्दिष्टीकरण

- मोडेल: RP2350

- प्याकेज: QFN-60

- आन्तरिक फ्ल्यास भण्डारण: छैन

- भोल्युमtage नियामक: अन-चिप स्विचिंग नियामक

- नियामक पिन: 5 (3.3V इनपुट, 1.1V आउटपुट, VREG_AVDD, VREG_LX, VREG_PGND)

उत्पादन उपयोग निर्देशन

- अध्याय 1: परिचय

- RP2350 श्रृंखलाले RP2040 श्रृंखलाको तुलनामा विभिन्न प्याकेज विकल्पहरू प्रदान गर्दछ। RP2350A र RP2354A QFN-60 प्याकेजमा क्रमशः आन्तरिक फ्ल्यास भण्डारण बिना र बिना नै आउँछन्, जबकि RP2354B र RP2350B QFN-80 प्याकेजमा फ्ल्यास भण्डारण बिना र बिना नै आउँछन्।

- अध्याय 2: शक्ति

RP2350 श्रृंखलाले नयाँ अन-चिप स्विचिङ भोल्युम फिचर गर्दछtage नियामक पाँच पिन संग। यो नियामकलाई सञ्चालनका लागि बाह्य कम्पोनेन्टहरू चाहिन्छ तर RP2040 शृङ्खलाको रैखिक नियामकको तुलनामा उच्च भार प्रवाहहरूमा उच्च शक्ति दक्षता प्रदान गर्दछ। एनालग सर्किटरी आपूर्ति गर्ने VREG_AVDD पिनमा आवाज संवेदनशीलतामा ध्यान दिनुहोस्।

बारम्बार सोधिने प्रश्नहरू (FAQ)

- Q: RP2350A र RP2350B बीचको मुख्य भिन्नता के हो?

A: मुख्य भिन्नता आन्तरिक फ्ल्यास भण्डारणको उपस्थितिमा छ। RP2350A सँग आन्तरिक फ्ल्यास भण्डारण छैन जबकि RP2350B सँग छ। - प्रश्न: भोल्युमले कति पिन गर्छtagRP2350 श्रृंखला मा e नियामक छ?

A: भोल्युमtagRP2350 श्रृंखलामा e नियामकमा पाँच पिनहरू छन्।

बोर्ड र उत्पादनहरू निर्माण गर्न RP2350 माइक्रोकन्ट्रोलरहरू प्रयोग गरेर RP2350 सँग हार्डवेयर डिजाइन

कोलोफोन

- © 2023-2024 Raspberry Pi Ltd

- यो कागजात Creative Commons Attribution-NoDerivatives 4.0 International (CC BY-ND) अन्तर्गत इजाजतपत्र दिइएको छ। निर्माण-मिति: 2024-08-08 निर्माण-संस्करण: c0acc5b-clean

- कानूनी अस्वीकरण सूचना

- रास्पबेरी PI उत्पादनहरूका लागि प्राविधिक र विश्वसनीयता डेटा (डेटाशिटहरू सहित) समय-समयमा परिमार्जित ("स्रोतहरू") RASPBERRY PI LTD ("RPL") र ILUNCLIMP द्वारा उपलब्ध गराइन्छ DING, तर सीमित छैन को लागि, एक विशेष उद्देश्यको लागि व्यापारिकता र फिटनेसको निहित वारेन्टीहरू अस्वीकार गरिएको छ। लागू हुने कानून द्वारा अनुमति दिइएको अधिकतम हदसम्म कुनै पनि प्रत्यक्ष, अप्रत्यक्ष, आकस्मिक, विशेष, अनुकरणीय, वा परिणामात्मक क्षतिहरूका लागि उत्तरदायी हुनेछैन (अपरिचित, अनुचित TE सामान वा सेवाहरू, डाटाको हानि , वा नाफा वा व्यापार अवरोध) यद्यपि कारण र दायित्वको कुनै सिद्धान्तमा, चाहे सम्झौतामा होस्, कडा दायित्व होस्, वा ट्यार्ट (लापरवाही वा अन्य कुनै पनि कुरामा) EN यदि सम्भावनाको सल्लाह दिइयो भने यस्तो क्षतिको।

- RPL ले कुनै पनि समयमा र कुनै पनि सूचना बिना संसाधनहरू वा तिनीहरूमा वर्णन गरिएका कुनै पनि उत्पादनहरूमा कुनै पनि सुधार, सुधार, सुधार वा अन्य कुनै परिमार्जन गर्ने अधिकार सुरक्षित गर्दछ।

संसाधनहरू डिजाइन ज्ञानको उपयुक्त स्तर भएका दक्ष प्रयोगकर्ताहरूका लागि लक्षित छन्। प्रयोगकर्ताहरू तिनीहरूको चयन र संसाधनहरूको प्रयोग र तिनीहरूमा वर्णन गरिएका उत्पादनहरूको कुनै पनि अनुप्रयोगको लागि पूर्ण रूपमा जिम्मेवार छन्। प्रयोगकर्ता क्षतिपूर्ति गर्न र RPL लाई सबै दायित्वहरू, लागतहरू, क्षतिहरू वा तिनीहरूको स्रोतहरूको प्रयोगबाट उत्पन्न हुने अन्य हानिहरू विरुद्ध होल्ड गर्न सहमत छन्। - RPL ले प्रयोगकर्ताहरूलाई केवल Raspberry Pi उत्पादनहरूसँग संयोजनमा संसाधनहरू प्रयोग गर्न अनुमति दिन्छ। संसाधनहरूको अन्य सबै प्रयोग निषेधित छ। कुनै पनि अन्य RPL वा अन्य तेस्रो पक्ष बौद्धिक सम्पत्ति अधिकारलाई कुनै इजाजतपत्र प्रदान गरिएको छैन।

- उच्च जोखिम गतिविधिहरू। Raspberry Pi उत्पादनहरू डिजाइन, निर्माण वा खतरनाक वातावरणहरूमा प्रयोगको लागि अभिप्रेरित गरिएको छैन जसमा असफल सुरक्षित कार्यसम्पादन आवश्यक हुन्छ, जस्तै आणविक सुविधा, विमान नेभिगेसन वा सञ्चार प्रणाली, हवाई ट्राफिक नियन्त्रण, हतियार प्रणाली वा सुरक्षा-महत्वपूर्ण अनुप्रयोगहरू (जीवन समर्थन सहित) को सञ्चालनमा। प्रणाली र अन्य चिकित्सा उपकरणहरू), जसमा उत्पादनहरूको विफलताले प्रत्यक्ष रूपमा मृत्यु, व्यक्तिगत चोटपटक वा गम्भीर शारीरिक वा वातावरणीय क्षति ("उच्च जोखिम गतिविधिहरू") निम्त्याउन सक्छ। RPL ले उच्च जोखिम गतिविधिहरूको लागि फिटनेसको कुनै पनि स्पष्ट वा निहित वारेन्टीलाई विशेष रूपमा अस्वीकार गर्दछ र उच्च जोखिम गतिविधिहरूमा Raspberry Pi उत्पादनहरूको प्रयोग वा समावेशको लागि कुनै दायित्व स्वीकार गर्दैन।

- Raspberry Pi उत्पादनहरू RPL को मानक सर्तहरूको अधीनमा प्रदान गरिन्छ। RPL को रिसोर्सेसको प्रावधानले RPL का मानक सर्तहरू विस्तार वा परिमार्जन गर्दैन तर तिनीहरूमा व्यक्त गरिएका अस्वीकरण र वारेन्टीहरूमा सीमित छैन।

अध्याय १. परिचय

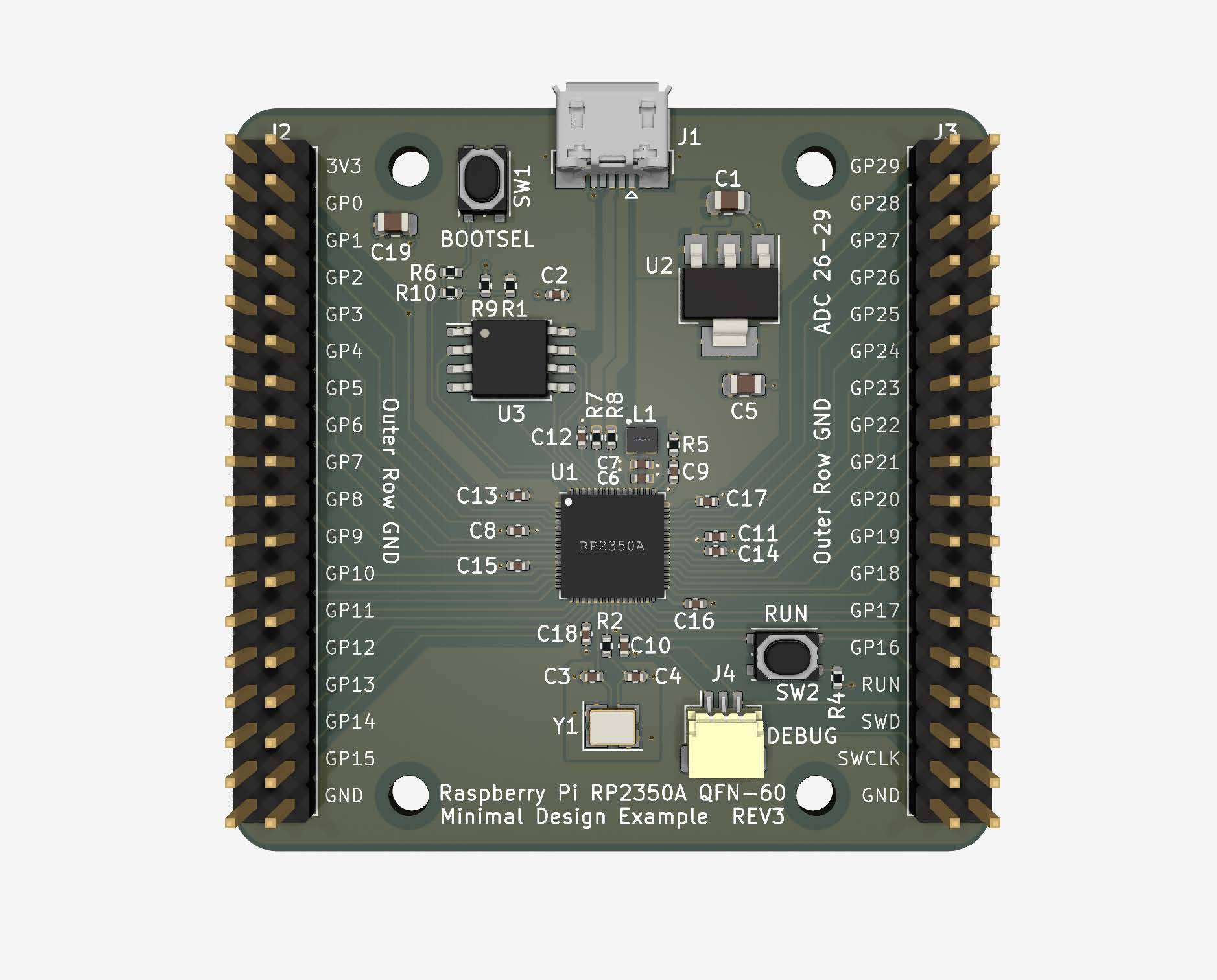

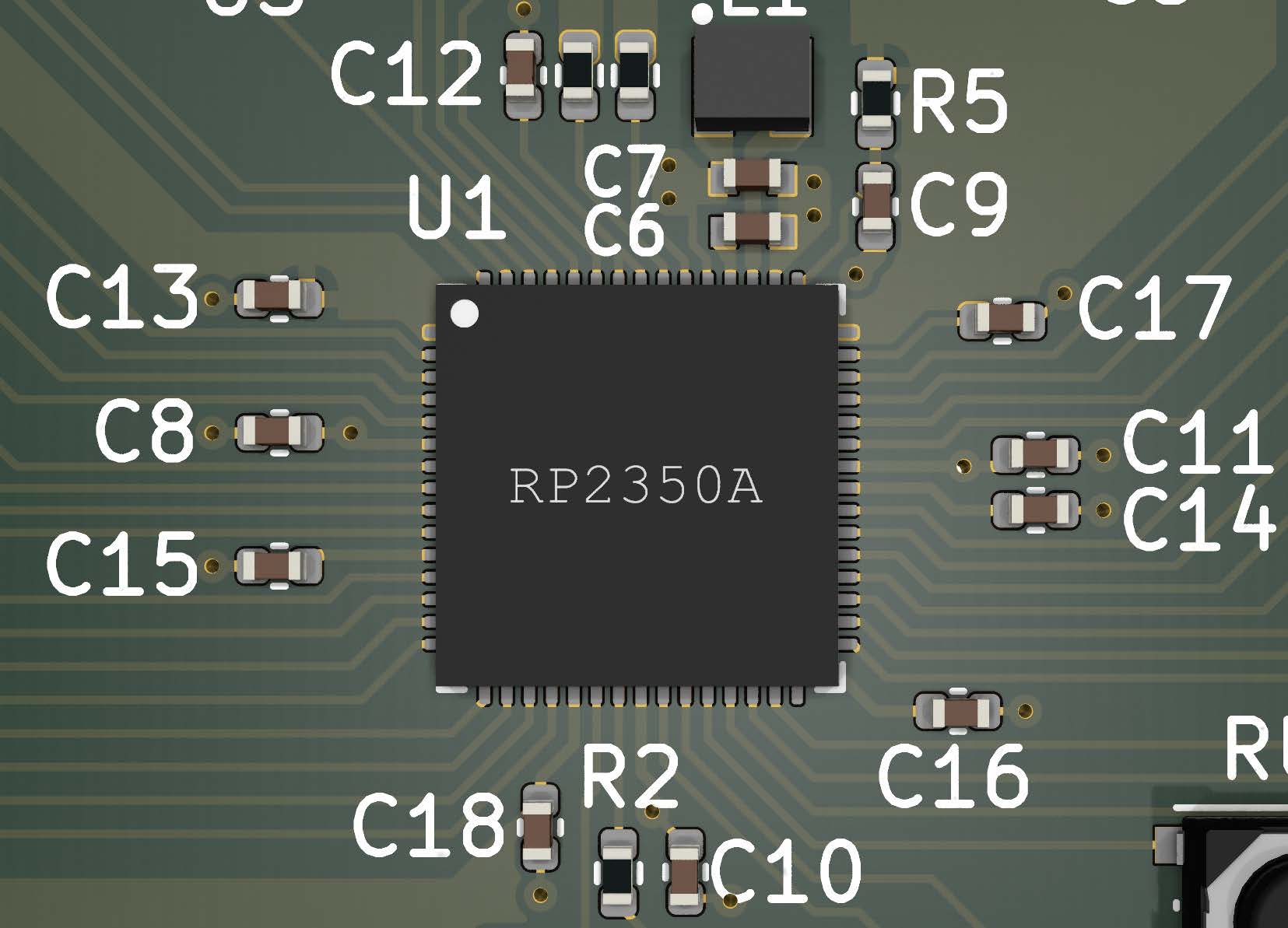

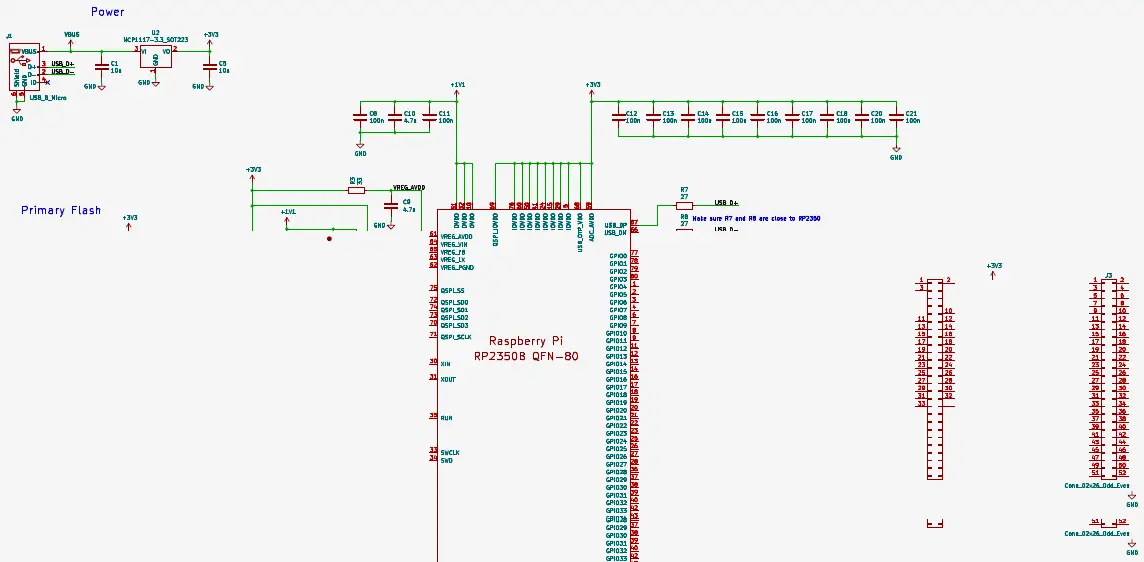

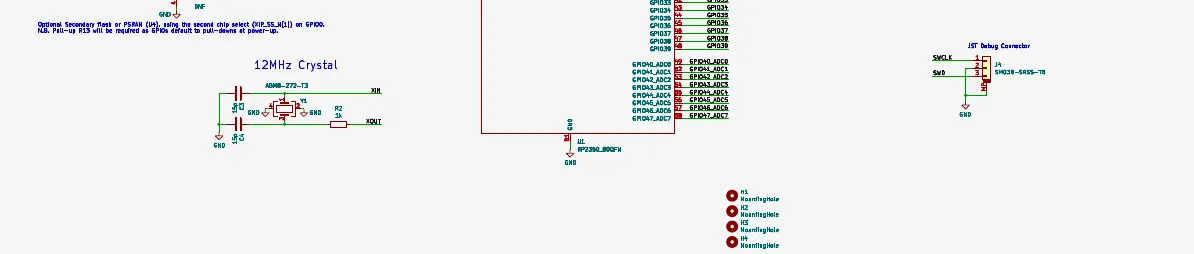

चित्र 1. RP3A को KiCad 2350D रेन्डरिङ न्यूनतम डिजाइन पूर्वample

जब हामीले पहिलो पटक रास्पबेरी Pi RP2040 प्रस्तुत गर्यौं, हामीले एक 'न्यूनतम' डिजाइन पनि जारी गर्यौं।ample र RP2040 सँगको गाइड हार्डवेयर डिजाइन जसले RP2040 लाई साधारण सर्किट बोर्डमा कसरी प्रयोग गर्न सकिन्छ र किन विभिन्न कम्पोनेन्ट छनोटहरू बनाइयो भन्ने आशा राखेको छ। RP235x शृङ्खलाको आगमनसँगै, यो मौलिक RP2040 Minimal डिजाइनलाई पुन: हेर्ने र नयाँ सुविधाहरू र प्रत्येक प्याकेज भेरियन्टहरूको लागि खातामा अद्यावधिक गर्ने समय हो। RP2350A यसको QFN-60 प्याकेजको साथ, र RP2350B जुन QFN-80 हो। फेरि, यी डिजाइनहरू Kicad (7.0) ढाँचामा छन्, र डाउनलोड गर्न उपलब्ध छन् (https://datasheets.raspberrypi.com/rp2350/Minimal-KiCAD.zip).

न्यूनतम बोर्ड

मूल न्यूनतम बोर्ड RP2040 चलाउन आवश्यक न्युनतम बाह्य कम्पोनेन्टहरू प्रयोग गरी सरल सन्दर्भ डिजाइन प्रदान गर्ने प्रयास थियो र अझै पनि सबै IO खुला र पहुँचयोग्य छ। यो अनिवार्य रूपमा पावर स्रोत (एक 5V देखि 3.3V रैखिक नियामक), क्रिस्टल ओसिलेटर, फ्ल्यास मेमोरी, र IO जडानहरू (एक माइक्रो USB सकेट र GPIO हेडरहरू) समावेश गरिएको थियो। नयाँ RP235x श्रृंखला न्यूनतम बोर्डहरू धेरै हदसम्म समान छन्, तर नयाँ हार्डवेयरको कारण केही परिवर्तनहरू आवश्यक छन्। यसका अतिरिक्त, र डिजाइनको न्यूनतम प्रकृतिको विरुद्धमा केही हदसम्म जाँदा, मैले बुटसेल र रनको लागि केही बटनहरू थपेको छु, छुट्टै SWD हेडरको साथ, जसको अर्थ यस पटक राम्रोसँग कम निराशाजनक डिबग अनुभव हुनुपर्छ। डिजाइनहरूलाई कडाइका साथ बोल्दा यी बटनहरू आवश्यक पर्दैन, संकेतहरू अझै पनि हेडरहरूमा उपलब्ध छन्, र यदि तपाईं विशेष रूपमा लागत वा स्पेस सचेत हुनुहुन्छ, वा मासोचिस्टिक प्रवृत्तिहरू छन् भने तिनीहरूलाई हटाउन सकिन्छ।

RP2040 बनाम RP235x श्रृंखला

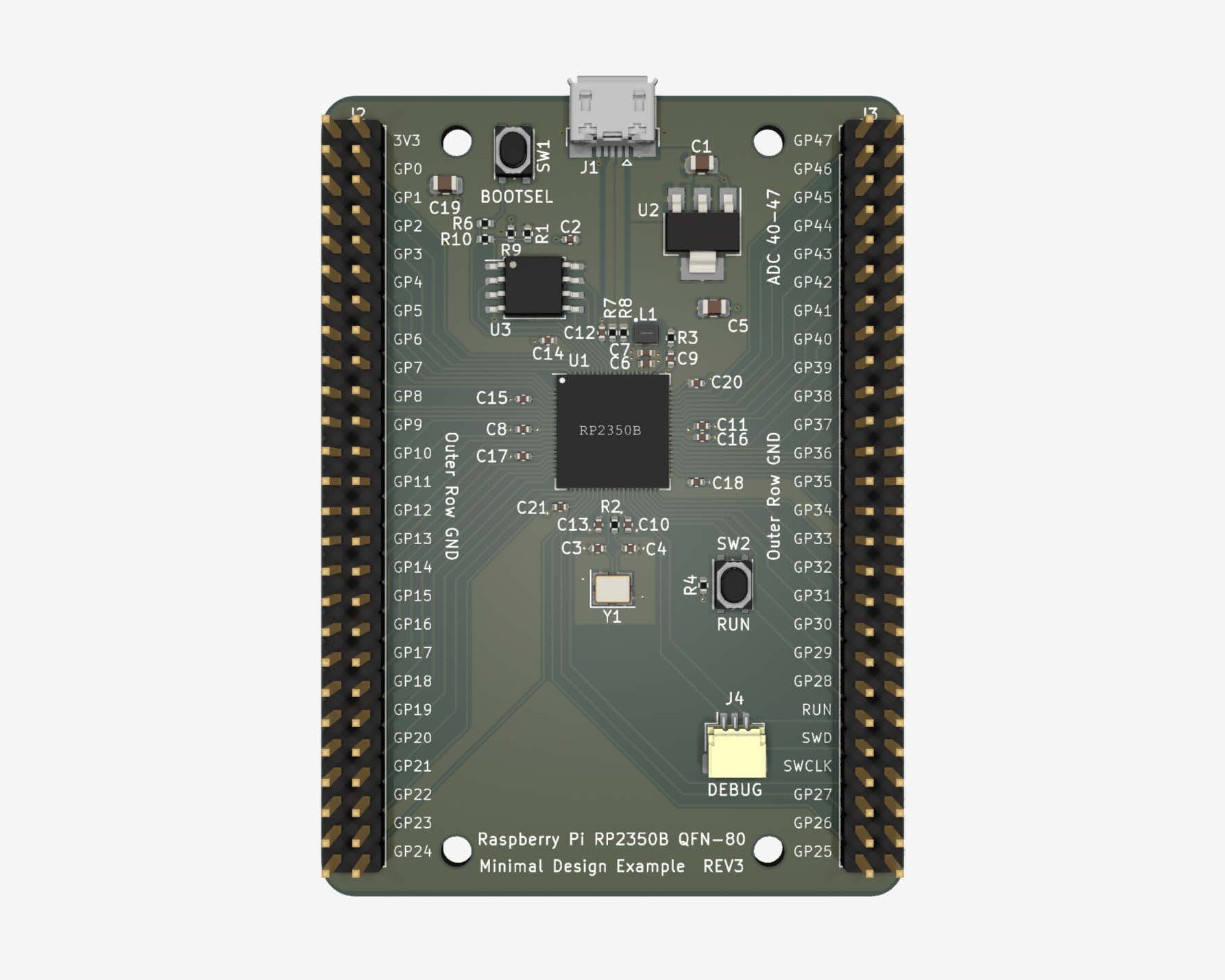

सबैभन्दा स्पष्ट परिवर्तन प्याकेजहरूमा छ। जहाँ RP2040 एक 7x7mm QFN-56 हो, RP235x श्रृंखलामा हाल चार फरक सदस्यहरू छन्। एउटै QFN-60 प्याकेज साझा गर्ने दुईवटा यन्त्रहरू छन्; RP2350A जसमा आन्तरिक फ्ल्यास भण्डारण छैन, र RP2354A जसमा हुन्छ। त्यस्तै, QFN-80 पनि दुई स्वादहरूमा आउँछ; RP2354B फ्ल्यासको साथ, र RP2350B बिना। QFN-60 यन्त्रहरू र मूल RP2040 साझा विरासतहरू छन्tage.

तिनीहरू प्रत्येकसँग 30 GPIO हरू छन्, जसमध्ये चार ADC मा पनि जोडिएका छन्, र 7x7mm आकारमा छन्। यसका बावजुद, RP2350A RP2040 को लागि ड्रप-इन प्रतिस्थापन होइन, किनकि प्रत्येकमा पिनको संख्या फरक छ। यसको विपरित, QFN-80 चिपहरूसँग अब 48 GPIO हरू छन्, र तीमध्ये आठहरू अब ADC सक्षम छन्। यसको कारण, हामीसँग अब दुईवटा न्यूनतम बोर्डहरू छन्; एउटा ६० पिन यन्त्रहरूका लागि र एउटा ८० का लागि। यी न्यूनतम बोर्डहरू मुख्य रूपमा आन्तरिक फ्ल्यास (RP60) बिना भागहरूका लागि डिजाइन गरिएका हुन्, तर डिजाइनहरू सजिलैसँग आन्तरिक फ्ल्यास यन्त्रहरू (RP80) मा अनबोर्ड फ्ल्यासलाई छोडेर प्रयोग गर्न सकिन्छ। मेमोरी, वा यसलाई माध्यमिक फ्ल्यास उपकरणको रूपमा प्रयोग गर्दै (यस पछि थप)। QFN-2350 संस्करणमा अतिरिक्त GPIO समायोजन गर्नका लागि हेडरहरूको लामो पङ्क्तिहरू छन्, र त्यसकारण बोर्ड ठूलो छ।

प्याकेज बाहेक, RP235x श्रृंखला र RP2040 बीचको सबैभन्दा ठूलो बोर्ड-स्तर भिन्नता पावर आपूर्तिहरू हुन्। RP235x श्रृंखलामा केही नयाँ पावर पिनहरू छन्, र फरक आन्तरिक नियामक। RP100 को 2040mA रैखिक नियामकलाई 200mA स्विचिङ नियामकको साथ प्रतिस्थापन गरिएको छ, र जस्तै, यसलाई केहि धेरै विशिष्ट सर्किटरी चाहिन्छ, र लेआउटको साथ कुनै सानो हेरचाह गरिएको छैन। यो अत्यधिक सिफारिस गरिएको छ कि तपाइँ हाम्रो लेआउट र कम्पोनेन्ट चयनहरू नजिकबाट पछ्याउनुहोस्; हामीले पहिले नै डिजाइनको धेरै पुनरावृत्तिहरू बनाउनु पर्ने पीडाबाट गुज्र्यौं, त्यसैले आशा छ तपाईंले गर्नुपर्दैन।

चित्र २. RP2B न्यूनतम डिजाइन पूर्वको KiCad 3D रेन्डरिङample

डिजाइन

न्यूनतम डिजाइनको इरादा पूर्वampलेस भनेको RP235x शृङ्खला प्रयोग गरेर सरल बोर्डहरूको एक जोडी बनाउनु हो, जुन अनावश्यक रूपमा विदेशी PCB प्रविधिहरू प्रयोग नगरी सस्तो र सजिलैसँग उत्पादनयोग्य हुनुपर्छ। त्यसैले न्यूनतम बोर्डहरू 2 तह डिजाइनहरू हुन्, कम्पोनेन्टहरू प्रयोग गरी जुन सामान्यतया उपलब्ध हुनुपर्छ, र सबै बोर्डको माथिल्लो छेउमा माउन्ट गरिएको छ। ठूला, सजिलै हात मिलाउन मिल्ने कम्पोनेन्टहरू प्रयोग गर्न राम्रो भए पनि QFN चिप्स (०.४ मिमी) को सानो पिचको अर्थ सबै GPIO हरू प्रयोग गरिएमा केही ०४०२ (१००५ मेट्रिक) निष्क्रिय कम्पोनेन्टहरू प्रयोग गर्नु अपरिहार्य छ। जबकि 0.4 कम्पोनेन्टहरू ह्यान्ड-सोल्डरिंग एक सभ्य सोल्डरिंग फलामको साथ धेरै चुनौतीपूर्ण छैन, यो विशेषज्ञ उपकरण बिना QFNs सोल्डर गर्न लगभग असम्भव छ।

अर्को केही खण्डहरूमा, म अतिरिक्त सर्किटरी के हो भनेर व्याख्या गर्ने प्रयास गर्न जाँदैछु, र आशा छ कि हामीले गरेका छनौटहरू कसरी गर्न आएका छौं। म वास्तवमा दुई अलग-अलग डिजाइनहरूको बारेमा कुरा गर्न जाँदैछु, प्रत्येक प्याकेज साइजको लागि एउटा, मैले चीजहरूलाई सकेसम्म सरल राख्न प्रयास गरेको छु। जहाँसम्म सम्भव छ, दुई बोर्डहरूका लागि सबै कम्पोनेन्ट सन्दर्भहरू समान छन्, त्यसैले यदि मैले U1, R1, इत्यादिलाई सन्दर्भ गर्छु भने, यो दुवै बोर्डहरूमा समान रूपमा सान्दर्भिक छ। स्पष्ट अपवाद हो जब कम्पोनेन्ट बोर्डहरू मध्ये एउटामा मात्र हुन्छ (सबै अवस्थामा, यो ठूलो 80 पिन संस्करणमा हुनेछ), त्यसपछि प्रश्नमा रहेको घटक QFN-80 डिजाइनमा मात्र हुनेछ; पूर्वका लागिample, R13 यो बोर्डमा मात्र देखिन्छ।

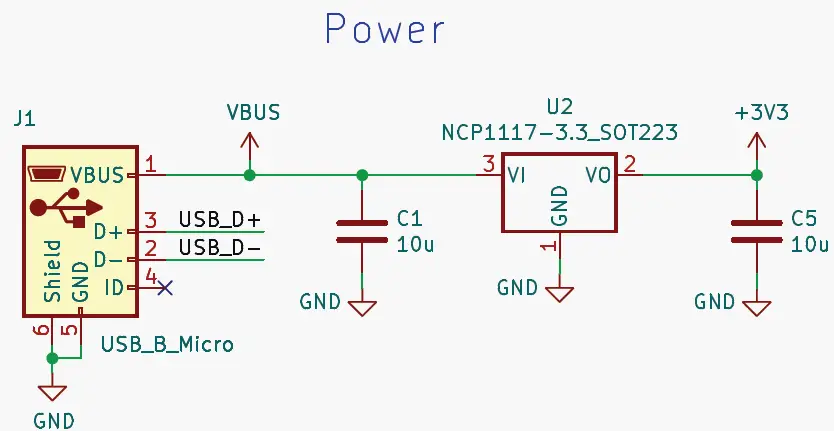

अध्याय 2. शक्ति

RP235x श्रृंखला र RP2040 को पावर आपूर्तिहरू यस पटक केही फरक छन्, यद्यपि यसको सरल कन्फिगरेसनमा, यसलाई अझै पनि दुई आपूर्तिहरू, 3.3V र 1.1V चाहिन्छ। RP235x शृङ्खलाहरू एकै साथ धेरै पावर भोका छन्, किनभने यो उच्च कार्यसम्पादन भएको छ, र यो पूर्ववर्ती भन्दा बढी मितव्ययी (कम पावर अवस्थामा हुँदा) छ, र त्यसैले RP2040 मा रैखिक नियामकलाई स्विचिङ नियामकसँग अपग्रेड गरिएको छ। यसले हामीलाई उच्च प्रवाहहरूमा (पहिले 200mA को तुलनामा 100mA सम्म) बढी शक्ति दक्षता दिन्छ।

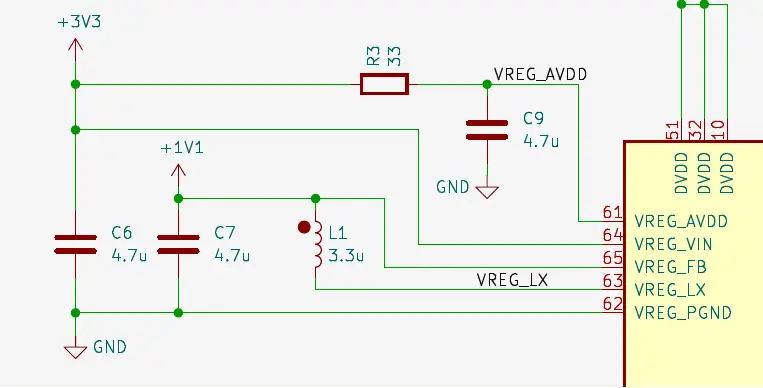

नयाँ अन-चिप भोल्युमtagई नियामक

चित्र ३. आन्तरिक नियामक सर्किट देखाउँदै योजनाबद्ध खण्ड

RP2040 को रैखिक नियामकसँग चिपमा DVDD आपूर्ति गर्न दुई पिन, 3.3V इनपुट, र 1.1V आउटपुट थियो। यस पटक, RP235x शृङ्खलाको नियामकमा पाँच पिनहरू छन्, र यसलाई काम गर्न केही बाह्य कम्पोनेन्टरी चाहिन्छ। जबकि यो उपयोगिता को मामला मा एक पछाडी कदम को एक बिट देखिन्छ, स्विचिंग नियामक को advan छ।tagउच्च भार प्रवाहहरूमा अधिक शक्ति कुशल हुनु।

नामले सुझाव दिए जस्तै, नियामकले 3.3V इनपुट भोल्युमलाई जोड्ने आन्तरिक ट्रान्जिस्टरलाई द्रुत रूपमा अन र अफ गर्छ।tage (VREG_VIN) लाई VREG_LX पिनमा, र इन्डक्टर (L1) र आउटपुट क्यापेसिटर (C7) को मद्दतले, यसले DC आउटपुट भोल्युम उत्पादन गर्न सक्छ।tage जुन इनपुटबाट स्टेप-डाउन गरिएको छ। VREG_FB पिनले आउटपुट भोल्युमलाई निगरानी गर्दछtage, र स्विचिङ चक्रको अन/अफ अनुपात समायोजन गर्दछ, यो सुनिश्चित गर्न आवश्यक भोल्युमtage राखिएको छ। ठूला धाराहरू VREG_VIN बाट VREG_LX मा स्विच गरिएकाले, इनपुटको नजिक ठूलो क्यापेसिटर (C6) आवश्यक छ, त्यसैले हामी 3.3V आपूर्तिलाई धेरै अप्ठ्यारो गर्दैनौं। यी ठूला स्विचिङ धाराहरूको कुरा गर्दा, नियामक पनि यसको आफ्नै ग्राउन्ड रिटर्न जडान, VREG_PGND सँग आउँछ। त्यस्तै VREG_VIN र VREG_LX सँग, यो जडानको लेआउट महत्वपूर्ण छ, र VREG_PGND मुख्य GND मा जडान हुनैपर्छ, यो यसरी गरिनुपर्छ कि सबै ठूला स्विचिङ धाराहरू सीधै PGND पिनमा फर्किन्छन्, बाँकीलाई बाधा नपुऱ्याई। GND धेरै।

अन्तिम पिन VREG_AVDD हो, जसले नियामक भित्र एनालग सर्किटरी आपूर्ति गर्दछ, र यो आवाजको लागि धेरै संवेदनशील छ।

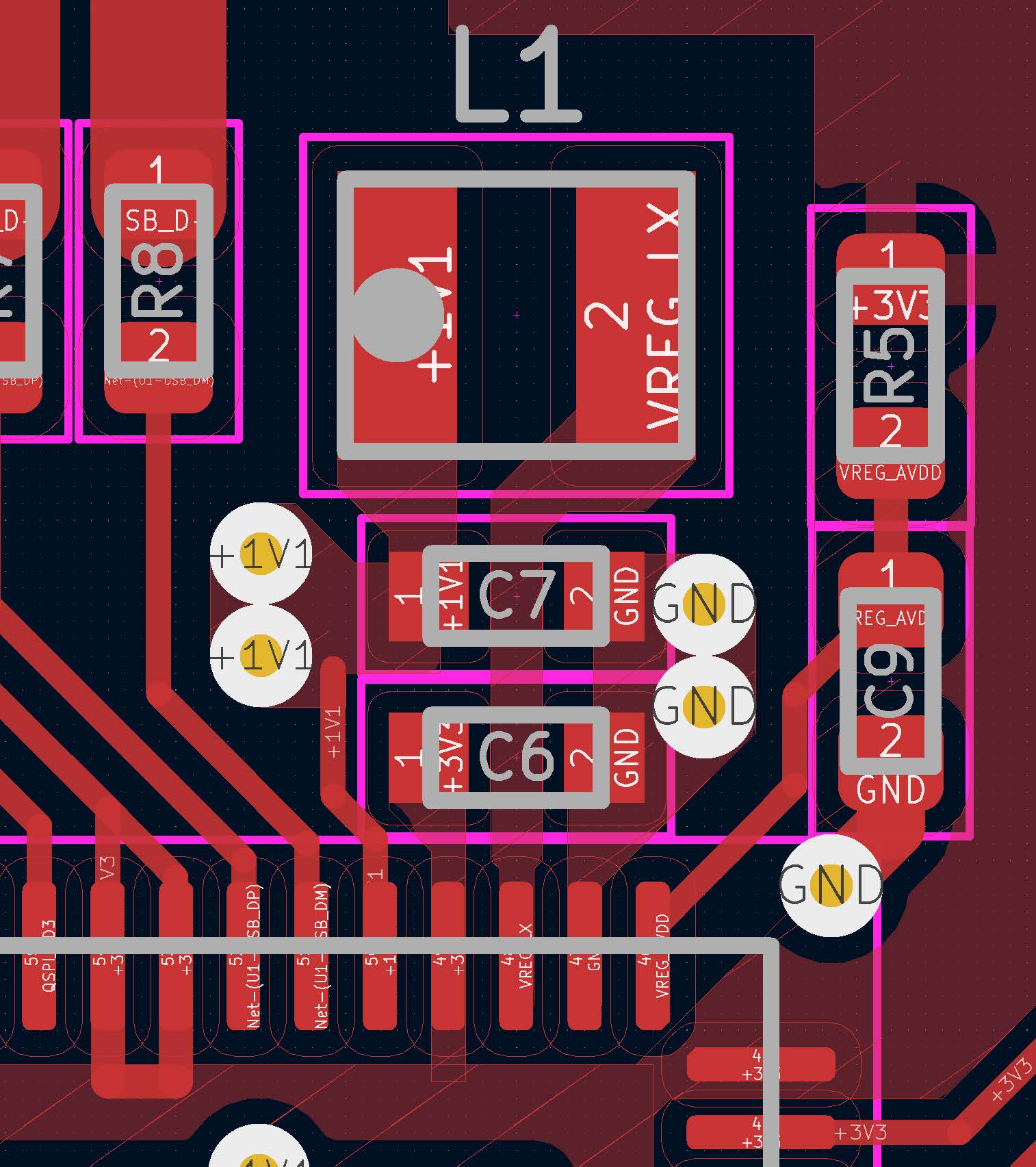

चित्र ४. नियामकको PCB लेआउट देखाउँदै योजनाबद्ध खण्ड

- न्यूनतम बोर्डहरूमा नियामकको लेआउटले रास्पबेरी Pi Pico 2 लाई नजिकबाट प्रतिबिम्बित गर्दछ। यस सर्किटको डिजाइनमा धेरै काम भएको छ, PCB को धेरै पुनरावृत्तिहरू आवश्यक छ जसलाई हामी सम्भवतः राम्रो बनाउन आवश्यक छ। सक्छ। जब तपाइँ यी कम्पोनेन्टहरू विभिन्न तरिकामा राख्न सक्नुहुन्छ र अझै पनि 'काम' गर्न नियामक प्राप्त गर्न सक्नुहुन्छ (अर्थात, आउटपुट भोल्युम उत्पादन गर्नुहोस्।tage लगभग सही स्तरमा, यो चलिरहेको कोड प्राप्त गर्न पर्याप्त राम्रो), हामीले फेला पारेका छौं कि हाम्रो नियामकलाई यसलाई खुसी राख्नको लागि ठीक तरिकाले व्यवहार गर्न आवश्यक छ, र खुशीले, मेरो मतलब सही आउटपुट भोल्युम उत्पादन गर्नु हो।tage लोड वर्तमान अवस्थाहरूको दायरा अन्तर्गत।

- यसमा हाम्रा प्रयोगहरू गर्दा, भौतिक विज्ञानको असुविधाजनक संसारलाई सधैं बेवास्ता गर्न सकिँदैन भनेर सम्झाउँदा हामी केही हदसम्म निराश भयौं। हामी, इन्जिनियरहरूको रूपमा, धेरै हदसम्म कोसिस गर्छौं र ठ्याक्कै यो गर्छौं; कम्पोनेन्टहरू सरलीकरण गर्दै, (अक्सर) तुच्छ भौतिक गुणहरूलाई बेवास्ता गर्दै, र यसको सट्टामा हामीले रुचि राखेको सम्पत्तिमा ध्यान केन्द्रित गर्ने।ampउदाहरणका लागि, साधारण प्रतिरोधकमा प्रतिरोध मात्र हुँदैन, तर इन्डक्टेन्स पनि हुन्छ। हाम्रो अवस्थामा, हामीले (पुनः) पत्ता लगायौं कि इन्डक्टरहरूसँग चुम्बकीय क्षेत्र सम्बन्धित छ, र महत्त्वपूर्ण कुरा, कुण्डली कुन बाटोमा निर्भर गर्दछ, दिशामा विकिरण हुन्छ। घाउ छ, र धारा को प्रवाह को दिशा। हामीलाई यो पनि सम्झाइयो कि एक 'पूर्ण' ढाल गरिएको इन्डक्टरको मतलब यो होइन कि तपाइँ सोच्नुहुन्छ कि यो हुन सक्छ। चुम्बकीय क्षेत्र धेरै हदसम्म कम भएको छ, तर केही अझै पनि भाग्छन्। हामीले पत्ता लगायौं कि नियामक कार्यसम्पादन व्यापक रूपमा सुधार गर्न सकिन्छ यदि इन्डक्टर 'सही बाटो राउन्ड' हो।

- यो बाहिर जान्छ कि 'गलत तरिका राउन्ड' इन्डक्टरबाट उत्सर्जन हुने चुम्बकीय क्षेत्रले नियामक आउटपुट क्यापेसिटर (C7) मा हस्तक्षेप गर्दछ, जसले RP2350 भित्र नियन्त्रण सर्किटलाई अपसेट गर्दछ। उचित अभिमुखीकरणमा इन्डक्टरको साथ, र यहाँ प्रयोग गरिएको सटीक लेआउट र कम्पोनेन्ट चयनहरू, त्यसपछि यो समस्या हट्छ। त्यहाँ निस्सन्देह अन्य लेआउटहरू, कम्पोनेन्टहरू, आदि हुनेछन्, जुन कुनै पनि अभिमुखीकरणमा इन्डक्टरसँग काम गर्न सक्छ, तर तिनीहरूले सम्भवतः त्यसो गर्नको लागि धेरै पीसीबी ठाउँ प्रयोग गर्नेछन्। हामीले यो कम्प्याक्ट र राम्रो व्यवहार गरिएको समाधानको विकास र परिष्कृत गर्न खर्च गरेका धेरै इन्जिनियरिङ घण्टाहरू मानिसहरूलाई बचाउनको लागि हामीले यो सिफारिस गरिएको लेआउट प्रदान गरेका छौं।

- बिन्दुमा थप, हामी यति टाढा जाँदैछौं कि यदि तपाईंले हाम्रो पूर्व प्रयोग नगर्ने छनौट गर्नुभयो भनेampले, त्यसपछि तपाईं आफ्नो जोखिममा त्यसो गर्नुहुन्छ। जसरी हामीले RP2040 र क्रिस्टल सर्किटसँग पहिले नै गरिसकेका छौं, जहाँ हामी जोड दिन्छौं (राम्रो रूपमा सुझाव दिन्छौं) तपाईंले एउटा विशेष भाग प्रयोग गर्नुहोस् (हामी यो कागजातको क्रिस्टल खण्डमा फेरि गर्नेछौं)।

- यी साना इन्डक्टरहरूको दिशात्मकतालाई विश्वव्यापी रूपमा बेवास्ता गरिएको छ, कुण्डल घुमाउने अभिमुखीकरणको साथ अनुमान गर्न असम्भव छ, र अनियमित रूपमा कम्पोनेन्टहरूको रिलको साथ वितरण गरिएको छ। ठूला इन्डक्टर केस आकारहरू प्रायः तिनीहरूमा ध्रुवता चिन्हहरू फेला पार्न सकिन्छ, यद्यपि हामीले छनौट गरेका 0806 (2016 मेट्रिक) केस साइजमा हामीले कुनै उपयुक्त फेला पार्न सकेनौं। यस उद्देश्यका लागि, हामीले Abracon सँग ध्रुवता संकेत गर्न थोप्लासहितको 3.3μH भाग उत्पादन गर्न काम गरेका छौं, र महत्त्वपूर्ण कुरा, ती सबैलाई समान रूपमा पङ्क्तिबद्ध गरी रिलमा आउनुहोस्। TBD वितरकहरूबाट सर्वसाधारणका लागि उपलब्ध गराइनेछ (वा चाँडै नै)। पहिले उल्लेख गरिए अनुसार, VREG_AVDD आपूर्ति शोरको लागि धेरै संवेदनशील छ, र त्यसैले फिल्टर गर्न आवश्यक छ। हामीले भेट्टायौं कि VREG_AVDD ले 200μA मात्र कोर्छ, 33Ω र 4.7μF को RC फिल्टर पर्याप्त छ।

- त्यसोभए, रिक्याप गर्न, प्रयोग गरिएका घटकहरू हुनेछन् ...

- C6, C7 र C9 - 4.7μF (0402, 1005 मेट्रिक)

- L1 - Abracon TBD (0806, 2016 मेट्रिक)

- R3 - 33Ω (0402, 1005 मेट्रिक)

- RP2350 डाटाशीटमा नियामक लेआउट सिफारिसहरूमा थप विस्तृत छलफल छ, कृपया बाह्य कम्पोनेन्टहरू र PCB लेआउट आवश्यकताहरू हेर्नुहोस्।

इनपुट आपूर्ति

यस डिजाइनको लागि इनपुट पावर जडान माइक्रो-USB कनेक्टरको 5V VBUS पिन मार्फत हो (चित्र 1 मा J5 लेबल गरिएको)। यो इलेक्ट्रोनिक उपकरणहरू पावर गर्ने एक सामान्य विधि हो, र यसले यहाँ अर्थ दिन्छ, किनकि RP2350 सँग USB कार्यक्षमता छ, जुन हामी यस कनेक्टरको डेटा पिनहरूमा तारिङ गर्नेछौं। हामीलाई यस डिजाइनको लागि केवल 3.3V चाहिन्छ (1.1V आपूर्ति आन्तरिकबाट आउँछ), हामीले आगमन 5V USB आपूर्तिलाई कम गर्न आवश्यक छ, यस अवस्थामा, अर्को, बाह्य भोल्युम प्रयोग गरेर।tage नियामक, यस अवस्थामा एक रेखीय नियामक (उर्फ लो ड्रप आउट नियामक, वा LDO)। पहिले एक कुशल स्विचिंग नियामक प्रयोग गर्ने गुणहरूको प्रशंसा गरिसकेपछि, यो यहाँ पनि एक प्रयोग गर्न बुद्धिमानी विकल्प हुन सक्छ, तर मैले सादगीको लागि रोजेको छु। पहिलो, LDO को प्रयोग लगभग सधैं सजिलो छ। तपाईले कुन साइज इन्डक्टर प्रयोग गर्नुपर्छ, वा आउटपुट क्यापेसिटरहरू कति ठूला छन् भनेर पत्ता लगाउन कुनै गणना आवश्यक छैन, र लेआउट सामान्यतया धेरै सीधा पनि हुन्छ। दोस्रो, शक्तिको प्रत्येक अन्तिम थोपा बचत गर्नु यहाँको उद्देश्य होइन; यदि यो थियो भने, म गम्भीरतापूर्वक एक स्विचिंग नियामक प्रयोग गर्ने विचार गर्नेछु, र तपाइँ एक पूर्व फेला पार्न सक्नुहुन्छampRaspberry Pi Pico 2 मा त्यसो गर्न सक्छु। र तेस्रो, मैले पहिले न्यूनतम बोर्डको RP2040 संस्करणमा प्रयोग गरेको सर्किटलाई 'उधारो' लिन सक्छु। यहाँ छनोट गरिएको NCP1117 (U2) सँग 3.3V को निश्चित आउटपुट छ, व्यापक रूपमा उपलब्ध छ, र वर्तमानको 1A सम्म प्रदान गर्न सक्छ, जुन धेरै डिजाइनहरूको लागि प्रशस्त हुनेछ। NCP1117 को लागि डाटाशीटमा एक नजरले हामीलाई बताउँछ कि यो यन्त्रलाई इनपुटमा 10μF क्यापेसिटर चाहिन्छ, र अर्को आउटपुटमा (C1 र C5)।

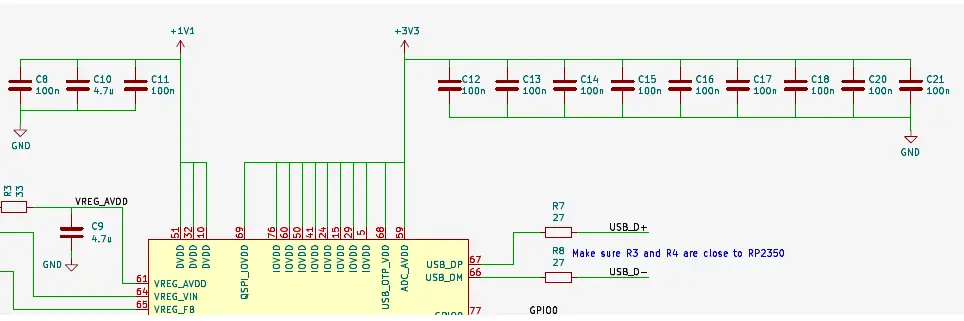

डिकपलिंग क्यापेसिटरहरू

चित्र 6. RP2350 पावर सप्लाई इनपुटहरू देखाउँदै योजनाबद्ध खण्ड, भोल्युमtage नियामक र decoupling capacitors

पावर सप्लाई डिजाइनको अर्को पक्ष भनेको RP2350 को लागि आवश्यक डिकपलिंग क्यापेसिटरहरू हुन्। यसले दुई आधारभूत कार्यहरू प्रदान गर्दछ। पहिलो, तिनीहरूले पावर सप्लाई शोर फिल्टर गर्छन्, र दोस्रो, RP2350 भित्रका सर्किटहरूले छोटो सूचनामा प्रयोग गर्न सक्ने चार्जको स्थानीय आपूर्ति प्रदान गर्छन्। यसले भोल्युमलाई रोक्छtage लेभल नजिकैको क्षेत्रमा धेरै खस्नुबाट जब हालको माग अचानक बढ्छ। किनभने, यसबाट, पावर पिनको नजिक डिकपलिंग राख्नु महत्त्वपूर्ण छ। सामान्यतया, हामी प्रति पावर पिन 100nF क्यापेसिटर प्रयोग गर्न सिफारिस गर्छौं, तथापि, हामी यस नियमबाट केही उदाहरणहरूमा विचलित हुन्छौं।

चित्र 7. लेआउट को खण्ड RP2350 राउटिंग र decoupling देखाउँदै

- सर्वप्रथम, यन्त्रबाट टाढा, सबै चिप पिनहरूलाई बाहिर निकाल्नको लागि पर्याप्त ठाउँ पाउनको लागि, हामीले प्रयोग गर्न सक्ने डिकपलिंग क्यापेसिटरहरूको मात्रासँग सम्झौता गर्नुपर्छ। यस डिजाइनमा, RP53A को 54 र 2350 पिनहरू (RP68B को 69 र 2350 पिनहरू) एकल क्यापेसिटर (चित्र 12 र चित्र 7 मा C6) साझा गर्छन्, किनभने त्यहाँ उपकरणको छेउमा धेरै ठाउँहरू छैनन्, र कम्पोनेन्टहरू र नियामकको लेआउट प्राथमिकता लिन्छ।

- यदि हामीले थप जटिल/महँगो प्रविधि, जस्तै साना कम्पोनेन्टहरू, वा माथि र तल्लो दुवै पक्षमा कम्पोनेन्टसहितको चार तहको PCB प्रयोग गर्यौं भने ठाउँको कमीलाई केही हदसम्म हटाउन सकिन्छ। यो एक डिजाइन व्यापार बन्द छ; हामीले जटिलता र लागत घटाएका छौं, कम डिकपलिंग क्यापेसिटन्स भएको खर्चमा, र क्यापेसिटरहरू जुन इष्टतम भन्दा चिपबाट अलि टाढा छन् (यसले इन्डक्टन्स बढाउँछ)। यसले डिजाइनले सञ्चालन गर्न सक्ने अधिकतम गतिलाई सीमित गर्ने प्रभाव हुन सक्छ, जस्तै भोल्युमtage आपूर्ति धेरै शोर हुन सक्छ र न्यूनतम अनुमति भोल्युम भन्दा तल खस्छtage; तर धेरैजसो अनुप्रयोगहरूको लागि, यो ट्रेड-अफ स्वीकार्य हुनुपर्छ।

- 100nF नियमबाट अर्को विचलन हो त्यसैले हामी भोल्युमलाई अझ सुधार गर्न सक्छौंtagई नियामक प्रदर्शन; हामी C4.7 को लागि 10μF प्रयोग गर्न सिफारिस गर्छौं, जुन नियामकबाट चिपको अर्को छेउमा राखिएको छ।

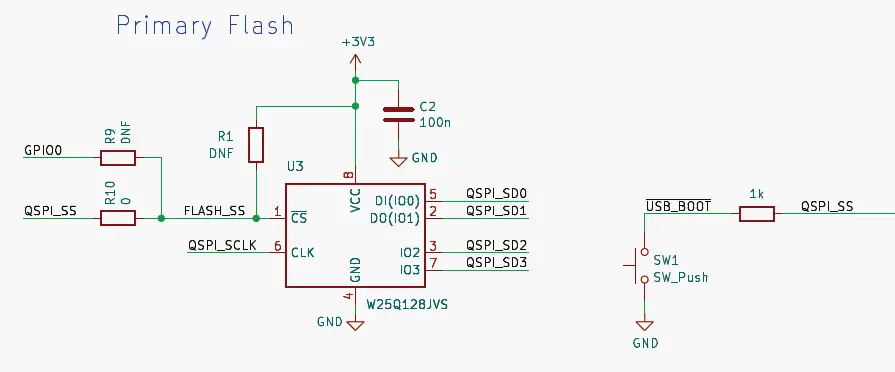

अध्याय ३। फ्ल्यास मेमोरी

प्राथमिक फ्लैश

चित्र 8. प्राथमिक फ्ल्यास मेमोरी र USB_BOOT सर्किटरी देखाउँदै योजनाबद्ध खण्ड

- RP2350 बुट र चलाउन सक्ने प्रोग्राम कोड भण्डारण गर्न सक्षम हुनको लागि, हामीले फ्ल्यास मेमोरी प्रयोग गर्न आवश्यक छ, विशेष गरी, क्वाड SPI फ्ल्याश मेमोरी। यहाँ छनोट गरिएको उपकरण W25Q128JVS उपकरण हो (चित्र 3 मा U8), जुन 128Mbit चिप (16MB) हो। यो RP2350 ले समर्थन गर्न सक्ने सबैभन्दा ठूलो मेमोरी साइज हो। यदि तपाईंको विशेष अनुप्रयोगलाई धेरै भण्डारण आवश्यक छैन भने, त्यसको सट्टा सानो, सस्तो मेमोरी प्रयोग गर्न सकिन्छ।

- यो डाटाबस धेरै उच्च फ्रिक्वेन्सी हुन सक्छ र नियमित रूपमा प्रयोगमा रहेको हुनाले, RP2350 को QSPI पिनहरू सिधै फ्ल्याशमा तार हुनुपर्छ, छोटो जडानहरू प्रयोग गरेर सिग्नल अखण्डता कायम राख्न, र वरपरका सर्किटहरूमा क्रसस्टक कम गर्न। क्रसस्टल्क भनेको एक सर्किट नेटमा संकेतहरूले अनावश्यक भोल्युम उत्पन्न गर्न सक्छtages छिमेकी सर्किटमा, सम्भावित रूपमा त्रुटिहरू उत्पन्न हुन सक्छ।

- QSPI_SS सिग्नल एक विशेष केस हो। यो सिधै फ्ल्याससँग जोडिएको छ, तर यसमा दुईवटा प्रतिरोधकहरू पनि छन् (राम्रो, चार, तर म पछि आउनेछु) यसमा जडान गरिएको छ। पहिलो (R1) 3.3V आपूर्तिमा पुल-अप हो। फ्ल्यास मेमोरीलाई चिप-चयन इनपुट एउटै भोल्युममा हुन आवश्यक छtage यसको आफ्नै 3.3V सप्लाई पिनको रूपमा यन्त्र पावर अप हुँदा, अन्यथा, यसले सही रूपमा काम गर्दैन। जब RP2350 पावर अप हुन्छ, यसको QSPI_SS पिन स्वचालित रूपमा पुल-अपमा पूर्वनिर्धारित हुनेछ, तर स्विच-अन गर्दा त्यहाँ छोटो अवधि हुन्छ जहाँ QSPI_SS पिनको अवस्था ग्यारेन्टी हुन सक्दैन। पुल-अप प्रतिरोधकको थपले यो आवश्यकता सधैं सन्तुष्ट हुनेछ भनेर सुनिश्चित गर्दछ। R1 लाई योजनाबद्धमा DNF (Do Not Fit) को रूपमा चिन्ह लगाइएको छ, किनकि हामीले फेला पारेका छौं कि यो विशेष फ्ल्यास उपकरणको साथ, बाह्य पुल-अप अनावश्यक छ। यद्यपि, यदि फरक फ्ल्यास प्रयोग गरिएको छ भने, यहाँ 10kΩ प्रतिरोधक सम्मिलित गर्न सक्षम हुनु महत्त्वपूर्ण हुन सक्छ, त्यसैले यसलाई केसमा मात्र समावेश गरिएको छ।

- दोस्रो प्रतिरोधक (R6) एक 1kΩ प्रतिरोधक हो, 'USB_BOOT' लेबल गरिएको पुश बटन (SW1) मा जडान गरिएको छ। यो किनभने QSPI_SS पिन 'बुट स्ट्र्याप' को रूपमा प्रयोग गरिन्छ; RP2350 ले बुट अनुक्रमको समयमा यो I/O को मान जाँच गर्दछ, र यदि यो तर्क 0 हो भने, त्यसपछि RP2350 BOOTSEL मोडमा फर्कन्छ, जहाँ RP2350 ले USB मास भण्डारण उपकरणको रूपमा प्रस्तुत गर्दछ, र कोड सीधा प्रतिलिपि गर्न सकिन्छ। यसलाई। यदि हामीले केवल बटन थिच्यौं भने, हामी QSPI_SS पिनलाई ग्राउन्डमा तान्दछौं, र यदि यन्त्र पछि रिसेट हुन्छ (जस्तै RUN पिन टगल गरेर), RP2350 फ्ल्यासको सामग्रीहरू चलाउन प्रयास गर्नुको सट्टा BOOTSEL मोडमा पुन: सुरु हुनेछ। यी प्रतिरोधकहरू, R2 र R6 (R9 र R10 पनि), फ्ल्याश चिपको नजिक राख्नुपर्छ, त्यसैले हामी तामा ट्र्याकहरूको अतिरिक्त लम्बाइबाट बच्न सक्छौं जसले संकेतलाई असर गर्न सक्छ।

- माथिका सबै विशेष रूपमा RP2350 मा लागू हुन्छ, जसमा कुनै आन्तरिक फ्ल्यास छैन। निस्सन्देह, RP2354 यन्त्रहरूमा आन्तरिक 2MB फ्ल्यास मेमोरीहरू छन्, त्यसैले बाह्य U3 मेमोरी आवश्यक पर्दैन, त्यसैले U3 लाई योजनाबद्धबाट सुरक्षित रूपमा हटाउन सकिन्छ, वा बस अलोकप्रिय छोड्न सकिन्छ। यी मध्ये कुनै पनि अवस्थामा, हामी अझै पनि USB_BOOT स्विच QSPI_SS मा जडान गर्न चाहन्छौं, ताकि हामी अझै पनि USB बुट मोडमा प्रवेश गर्न सक्छौं।

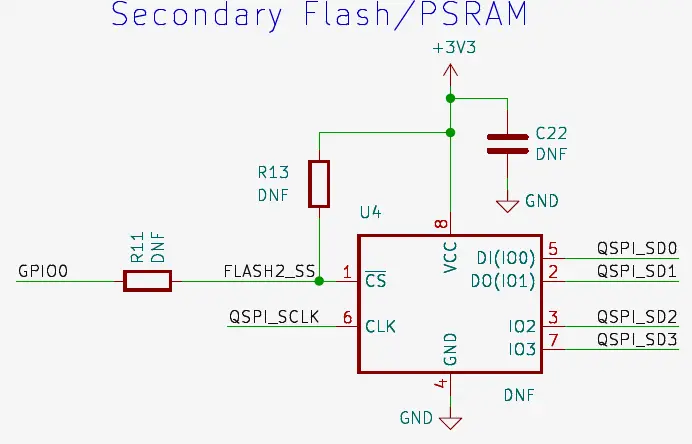

माध्यमिक फ्ल्यास वा PSRAM

- RP235x शृङ्खलाले अब उही QSPI पिन प्रयोग गरेर दोस्रो मेमोरी यन्त्रलाई समर्थन गर्दछ, GPIO ले थप चिप चयन प्रदान गर्दछ। त्यसोभए, यदि हामीले RP2354 प्रयोग गर्दैछौं (जसमा आन्तरिक फ्ल्यास छ), तब हामी U3 लाई माध्यमिक फ्ल्यासको रूपमा प्रयोग गर्न सक्छौं, वा यसलाई PSRAM उपकरणसँग बदल्न पनि सक्छौं। यो गर्नको लागि, हामीले U3 बाट QSPI_SS लाई विच्छेद गर्नुपर्छ, र यसको सट्टा उपयुक्त GPIO मा जडान गर्नुपर्छ। चिप चयन (XIP_CS1n) हुन सक्ने सबैभन्दा नजिकको GPIO GPIO0 हो, त्यसैले R0 बाट 10Ω हटाएर, यसलाई R9 मा फिट गरेर, हामी अब अन-चिप फ्ल्यासको अतिरिक्त U3 पहुँच गर्न सक्छौं। पूर्ण रूपमा एडभान लिनको लागिtagयो सुविधाको e, जहाँ हामीसँग दुईवटा बाह्य मेमोरी यन्त्रहरू छन् ताकि फ्ल्यास-रहित RP2350 भागहरूले फाइदा लिन सक्छ, RP2350B का लागि दुईवटा मिनिमल बोर्डहरूमध्ये ठूलोमा अतिरिक्त मेमोरी चिपको लागि वैकल्पिक फुटप्रिन्ट (U4) समावेश छ।

चित्र 9. वैकल्पिक माध्यमिक मेमोरी उपकरण देखाउँदै योजनाबद्ध खण्ड

यो यन्त्र प्रयोग गर्न सक्षम हुन, यो स्पष्ट रूपमा आबादी हुनुपर्छ, साथै R11 (0Ω), र R13 (10KΩ)। R11 को थपले GPIO0 (XIP_CS1n सिग्नल) लाई दोस्रो मेमोरीको चिप चयनमा जोड्छ। चिप चयन पिनमा पुल-अप यस पटक निश्चित रूपमा आवश्यक छ, किनकि GPIO0 को पूर्वनिर्धारित अवस्था पावर-अपमा कम तान्नु पर्ने हुन्छ, जसले हाम्रो फ्ल्यास यन्त्रलाई असफल बनाउँछ। U22 को लागि स्थानीय बिजुली आपूर्ति डिकपलिंग प्रदान गर्न C4 लाई पनि आवश्यक पर्दछ।

समर्थित फ्लैश चिप्स

दोस्रो s निकाल्न तलबाट प्रयोग गरिएको प्रारम्भिक फ्ल्यास प्रोब अनुक्रमtage फ्ल्याशबाट, 03h सिरियल पढ्ने आदेश प्रयोग गर्दछ, 24-बिट ठेगानाको साथ, र लगभग 1MHz को एक क्रमिक घडी। यो बारम्बार घडी ध्रुवता र घडी चरण को चार संयोजन मार्फत चक्र, एक मान्य दोस्रो s खोज्दै।tage CRC32 चेकसम।

दोस्रो रूपमा एसtage त्यसपछि एउटै 03h सिरियल रिड कमाण्ड प्रयोग गरेर एक्जिक्यूट-इन-प्लेस कन्फिगर गर्न स्वतन्त्र छ, RP2350 ले 03-बिट ठेगानाको साथ 24h सिरियल रिडलाई समर्थन गर्ने कुनै पनि चिपको साथ क्यास फ्लैश कार्यान्वयन-इन-प्लेस प्रदर्शन गर्न सक्छ, जसमा अधिकांश 25-श्रृंखला फ्ल्यास उपकरणहरू समावेश छन्। । SDK ले एक पूर्व प्रदान गर्दछampले दोस्रो एसtage का लागि CPOL=0 CPHA=0, at https://github.com/raspberrypi/pico-sdk/blob/master/src/rp2350/boot_stage2/boot2_generic_03h.S। तलको दिनचर्याहरू प्रयोग गरेर फ्ल्यास प्रोग्रामिङलाई समर्थन गर्न, उपकरणले निम्न आदेशहरूमा पनि प्रतिक्रिया दिनै पर्छ:

- 02h 256-बाइट पृष्ठ कार्यक्रम

- 05 घन्टा स्थिति दर्ता पढ्नुहोस्

- ०६ घन्टा सेट लेखन सक्षम कुंडी

- 20h 4kB क्षेत्र मेटाउनुहोस्

RP2350 ले डुअल-SPI र QSPI पहुँच मोडहरूको विस्तृत विविधतालाई पनि समर्थन गर्दछ। पूर्वका लागिampले, https://github.com/raspberrypi/pico-sdk/blob/master/src/rp2350/boot_stage2/boot2_w25q080.S Quad-IO निरन्तर पढ्ने मोडको लागि Winbond W25Q-श्रृङ्खला यन्त्र कन्फिगर गर्दछ, जहाँ RP2350 ले क्वाड-IO ठेगानाहरू पठाउँछ (कमाण्ड उपसर्ग बिना) र फ्ल्याशले क्वाड-IO डेटासँग प्रतिक्रिया दिन्छ।

फ्ल्यास XIP मोडहरूसँग केही सावधानी आवश्यक छ जहाँ फ्ल्यास उपकरणले मानक सिरियल आदेशहरूमा प्रतिक्रिया दिन रोक्छ, जस्तै माथि उल्लिखित Winbond लगातार पढ्ने मोड। RP2350 रिसेट गर्दा यसले समस्याहरू निम्त्याउन सक्छ, तर फ्ल्यास यन्त्र पावर-साइकल गरिएको छैन, किनभने फ्ल्यासले बुट्रोमको फ्ल्यास प्रोब अनुक्रममा प्रतिक्रिया दिने छैन। 03h सिरियल रिड जारी गर्नु अघि, बुट्रोमले सधैं निम्न निश्चित अनुक्रम जारी गर्दछ, जुन फ्ल्याश उपकरणहरूको दायरामा XIP बन्द गर्नको लागि उत्तम प्रयासको अनुक्रम हो:

- CSn=1, IO[3:0]=4'b0000 (विवादबाट बच्न पुल डाउन मार्फत), अंक ×32 घडीहरू

- CSn=0, IO[3:0]=4'b1111 (विवादबाट बच्न पुल अप मार्फत), अंक ×32 घडीहरू

- CSn=1

- CSn=0, MOSI=1'b1 (चालित Low-Z, अन्य सबै I/Os Hi-Z), अंक ×16 घडीहरू

यदि तपाइँको छनोट गरिएको यन्त्रले यसको निरन्तर पढ्ने मोडमा हुँदा यो क्रमलाई प्रतिक्रिया दिँदैन भने, त्यसपछि यसलाई एक राज्यमा राख्नु पर्छ जहाँ प्रत्येक स्थानान्तरणलाई क्रमबद्ध आदेशद्वारा उपसर्ग गरिएको छ, अन्यथा RP2350 आन्तरिक रिसेट पछि पुन: प्राप्ति गर्न सक्षम हुनेछैन।

QSPI मा थप विवरणहरूको लागि, कृपया RP2350 डाटाशीटमा QSPI मेमोरी इन्टरफेस (QMI) हेर्नुहोस्।

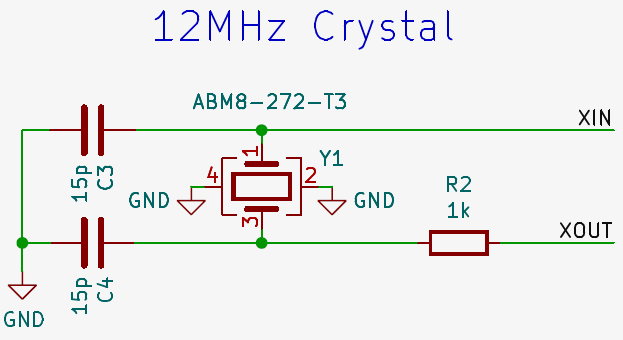

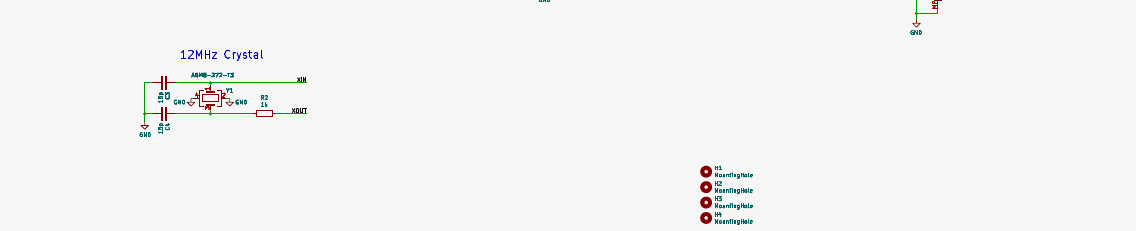

अध्याय 4. क्रिस्टल ओसिलेटर

चित्र 10. क्रिस्टल ओसिलेटर र लोड क्यापेसिटरहरू देखाउँदै योजनाबद्ध खण्ड

- कडा शब्दमा भन्नुपर्दा, RP2350 लाई वास्तवमा बाह्य घडी स्रोतको आवश्यकता पर्दैन, किनकि यसको आफ्नै आन्तरिक ओसिलेटर छ। यद्यपि, यस आन्तरिक ओसिलेटरको फ्रिक्वेन्सी राम्रोसँग परिभाषित वा नियन्त्रित नभएकोले, चिपदेखि चिपमा भिन्न हुन्छ, साथै विभिन्न आपूर्ति भोल्युमसँगtages र तापमान, यो एक स्थिर बाह्य आवृत्ति स्रोत प्रयोग गर्न सिफारिस गरिएको छ। सटीक फ्रिक्वेन्सीहरूमा भर पर्ने एप्लिकेसनहरू बाह्य फ्रिक्वेन्सी स्रोत बिना सम्भव छैन, USB एक प्राइम एक्स हो।ample।

- बाह्य फ्रिक्वेन्सी स्रोत उपलब्ध गराउने दुई मध्ये कुनै एक तरिकामा गर्न सकिन्छ: या त CMOS आउटपुटको साथ घडी स्रोत प्रदान गरेर (IOVDD भोल्युमको वर्ग लहरtage) XIN पिन मा, वा बीच जोडिएको 12MHz क्रिस्टल प्रयोग गरेर

- XIN र XOUT। क्रिस्टलको प्रयोग यहाँ मनपर्ने विकल्प हो, किनकि तिनीहरू दुवै अपेक्षाकृत सस्तो र धेरै सटीक छन्।

- यस डिजाइनको लागि चयन गरिएको क्रिस्टल ABM8-272-T3 (चित्र 1 मा Y10) हो। यो Raspberry Pi Pico र Raspberry Pi Pico 12 मा प्रयोग गरिएको एउटै 2MHz क्रिस्टल हो। हामी क्रिस्टललाई हानी नगरी सबै अवस्थामा छिटो सुरु हुने कुरा सुनिश्चित गर्न सँगैको सर्किटरीसँगै यो क्रिस्टल प्रयोग गर्न सिफारिस गर्छौं। क्रिस्टलसँग 30ppm फ्रिक्वेन्सी सहिष्णुता छ, जुन धेरै अनुप्रयोगहरूको लागि पर्याप्त राम्रो हुनुपर्छ। +/-30ppm को फ्रिक्वेन्सी सहिष्णुताको साथमा, यसको अधिकतम ESR 50Ω, र 10pF को लोड क्यापेसिटन्स छ, जसको दुवैले सँगैका कम्पोनेन्टहरूको छनोटमा प्रभाव पारेको थियो।

- क्रिस्टललाई चाहिएको फ्रिक्वेन्सीमा ओसिलिलेट गर्नको लागि, निर्माताले लोड क्यापेसिटन्स निर्दिष्ट गर्दछ जुन यसलाई त्यसो गर्नको लागि आवश्यक छ, र यस अवस्थामा, यो 10pF हो। यो लोड क्यापेसिटन्स बराबर मूल्यका दुई क्यापेसिटरहरू राखेर प्राप्त गरिन्छ, क्रिस्टलको प्रत्येक छेउमा एउटा (C3 र C4)। क्रिस्टलको बिन्दुबाट view, यी क्यापेसिटरहरू यसको दुई टर्मिनलहरू बीच श्रृंखलामा जोडिएका छन्। आधारभूत सर्किट सिद्धान्तले हामीलाई बताउँछ कि तिनीहरूले (C3*C4)/(C3+C4) को क्यापेसिटन्स दिन संयोजन गर्छ, र C3=C4 को रूपमा, त्यसपछि यो केवल C3/2 हो। यस मा पूर्वample, हामीले 15pF capacitors प्रयोग गरेका छौं, त्यसैले श्रृंखला संयोजन 7.5pF हो। यो जानाजानी लोड क्यापेसिटन्सको अतिरिक्त, हामीले PCB ट्र्याकहरू र RP2350 को XIN र XOUT पिनहरूबाट प्राप्त गर्ने अनावश्यक अतिरिक्त क्यापेसिटन्स, वा परजीवी क्यापेसिटन्सको लागि मान पनि थप्नु पर्छ। हामी यसको लागि 3pF को मान मान्नेछौं, र यो क्यापेसिटन्स C3 र C4 सँग समानान्तरमा छ, हामी यसलाई 10.5pF को कुल लोड क्यापेसिटन्स दिनको लागि थप्छौं, जुन 10pF को लक्ष्यको नजिक छ। तपाईंले देख्न सक्नुहुने रूपमा, PCB ट्रेसहरूको परजीवी क्यापेसिटन्स एक कारक हो, र त्यसैले हामीले तिनीहरूलाई सानो राख्न आवश्यक छ ताकि हामी क्रिस्टललाई विचलित गर्दैनौं र यसलाई अभिप्रेरित रूपमा दोलन रोक्न सक्दैनौं। प्रयास गर्नुहोस् र लेआउट सकेसम्म छोटो राख्नुहोस्।

- दोस्रो विचार क्रिस्टलको अधिकतम ESR (समान श्रृंखला प्रतिरोध) हो। हामीले अधिकतम ५०Ω भएको यन्त्रको लागि रोजेका छौं, किनकि हामीले पत्ता लगायौं कि यो, 50kΩ श्रृंखला प्रतिरोधक (R1) को साथमा, IOVDD प्रयोग गर्दा क्रिस्टललाई अधिक-संचालित हुन र क्षतिग्रस्त हुनबाट रोक्नको लागि राम्रो मूल्य हो। 2V को स्तर। यद्यपि, यदि IOVDD 3.3V भन्दा कम छ भने, XIN/XOUT पिनको ड्राइभ वर्तमान घटाइन्छ, र तपाईंले फेला पार्नुहुनेछ कि ampक्रिस्टलको लिट्यूड कम छ, वा कत्ति पनि दोलन नहुन सक्छ। यस अवस्थामा, श्रृंखला प्रतिरोधकको सानो मान प्रयोग गर्न आवश्यक हुनेछ। यहाँ देखाइएको क्रिस्टल सर्किटबाट कुनै पनि विचलन, वा 3.3V बाहेकको IOVDD स्तरको साथमा, क्रिस्टल सबै अवस्थाहरूमा ओसिलिट हुन्छ, र तपाईंको अनुप्रयोगमा समस्याहरू नपरोस् भनेर पर्याप्त छिटो सुरु हुन्छ भनी सुनिश्चित गर्न व्यापक परीक्षणको आवश्यकता पर्दछ।

crystal सिफारिस गर्नुभयो

- RP2350 प्रयोग गरी मौलिक डिजाइनहरूको लागि हामी Abracon ABM8-272-T3 प्रयोग गर्न सिफारिस गर्छौं। पूर्वका लागिample, न्यूनतम डिजाइन पूर्वको अतिरिक्तample, रास्पबेरी Pi Pico 2 डाटाशीट र Pico 2 डिजाइनको परिशिष्ट B मा Pico 2 बोर्ड योजनाबद्ध हेर्नुहोस् files.

- सामान्य सञ्चालन तापक्रम दायराहरूमा उत्कृष्ट प्रदर्शन र स्थिरताको लागि, Abracon ABM8-272-T3 प्रयोग गर्नुहोस्। तपाईंले ABM8-272-T3 सीधै Abracon वा आधिकारिक पुनर्विक्रेताबाट प्राप्त गर्न सक्नुहुन्छ। Pico 2 विशेष रूपमा ABM8-272-T3 को लागि ट्युन गरिएको छ, जसमा निम्न विनिर्देशहरू छन्:

- यदि तपाइँ समान विनिर्देशहरूको साथ क्रिस्टल प्रयोग गर्नुहुन्छ भने, तपाइँले स्थिरता सुनिश्चित गर्न तापमानको दायरामा सर्किट परीक्षण गर्न आवश्यक पर्दछ।

- क्रिस्टल ओसिलेटर IOVDD भोल्युमबाट संचालित छtage नतिजाको रूपमा, अब्राकोन क्रिस्टल र त्यो विशेष डीamping प्रतिरोधक 3.3V सञ्चालनको लागि ट्युन गरिएको छ। यदि तपाइँ फरक IO भोल्युम प्रयोग गर्नुहुन्छtagई, तपाईंले पुन: ट्युन गर्न आवश्यक हुनेछ।

- क्रिस्टल मापदण्डहरूमा कुनै पनि परिवर्तनले क्रिस्टल सर्किटमा जडान भएका कुनै पनि कम्पोनेन्टहरूमा अस्थिरताको जोखिम हुन्छ।

- यदि तपाइँ सिधै Abracon वा पुनर्विक्रेताबाट सिफारिस गरिएको क्रिस्टल स्रोत गर्न सक्नुहुन्न भने, सम्पर्क गर्नुहोस् applications@raspberrypi.com.

अध्याय 5. IOs

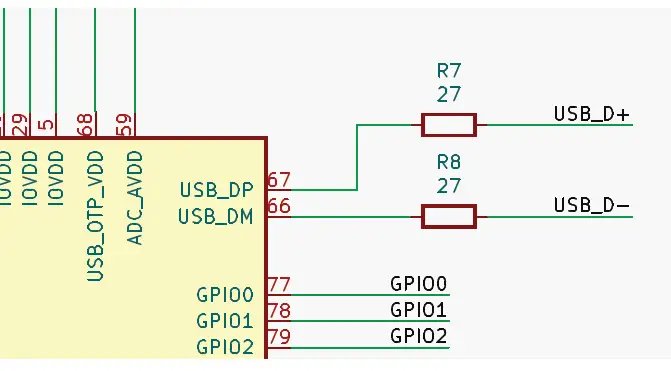

USB

चित्र 11. योजनाबद्ध खण्ड RP2350 को USB पिन र श्रृंखला समाप्ति देखाउँदै

- RP2350 ले प्रयोग गरिएको सफ्टवेयरको आधारमा पूर्ण गति (FS) वा कम गति (LS) USB को लागि होस्ट वा उपकरणको रूपमा प्रयोग गर्न दुई पिनहरू प्रदान गर्दछ। हामीले पहिले नै छलफल गरिसकेका छौं, RP2350 ले USB मास स्टोरेज यन्त्रको रूपमा पनि बुट गर्न सक्छ, त्यसैले यी पिनहरूलाई USB कनेक्टरमा तारिङ गर्नु (चित्र 1 मा J5) अर्थपूर्ण हुन्छ। RP2350 मा USB_DP र USB_DM पिनहरूलाई कुनै पनि अतिरिक्त पुल-अप वा पुल-डाउनको आवश्यकता पर्दैन (गति, FS वा LS, वा यो होस्ट वा उपकरण हो भनेर संकेत गर्न आवश्यक), किनकि यी I/Os मा निर्मित छन्। यद्यपि, यी I/Os लाई 27Ω श्रृंखला समाप्ति प्रतिरोधकहरू आवश्यक पर्दछ (चित्र 7 मा R8 र R11), चिपको नजिक राखिएको छ, USB प्रतिबाधा विशिष्टता पूरा गर्नको लागि।

- RP2350 पूर्ण गति डाटा दर (12Mbps) मा सीमित भएता पनि, हामीले प्रयास गर्नुपर्छ र प्रसारण लाइनहरूको विशेषता प्रतिबाधा (चिपलाई कनेक्टरमा जोड्ने तामा ट्र्याकहरू) नजिकै छन् भनेर सुनिश्चित गर्नुपर्छ।

- 90Ω को USB विशिष्टता (भिन्न मापन)। १ मिलिमिटर बाक्लो बोर्डमा, यदि हामीले USB_DP र USB_DM मा 1mm चौडा ट्र्याकहरू प्रयोग गर्छौं, तिनीहरूको बीचमा 0.8mm को अन्तर छ भने, हामीले लगभग 0.15Ω को भिन्न विशेषता प्रतिबाधा प्राप्त गर्नुपर्छ। यो सुनिश्चित गर्नको लागि हो कि संकेतहरू यी प्रसारण लाइनहरूमा सकेसम्म सफासँग यात्रा गर्न सक्छन्, भोल्युमलाई न्यूनतम गर्दै।tagई प्रतिबिम्ब जसले संकेत को अखण्डता कम गर्न सक्छ। यी प्रसारण लाइनहरू ठीकसँग काम गर्नको लागि, हामीले यी लाइनहरू सीधै तल ग्राउन्ड हो भनेर सुनिश्चित गर्न आवश्यक छ। ग्राउन्ड कपरको ठोस, अविरल क्षेत्र, ट्र्याकको सम्पूर्ण लम्बाइ फैलाउने। यस डिजाइनमा, तलको तामाको तहको लगभग सम्पूर्ण भाग जमिनमा समर्पित छ, र USB ट्र्याकहरू जमिन बाहेक अरू केही पनि नपुगेको सुनिश्चित गर्न विशेष हेरचाह गरिएको थियो। यदि तपाइँको निर्माणको लागि 1mm भन्दा मोटो PCB छनोट गरिएको छ भने, हामीसँग दुई विकल्पहरू छन्। हामीले ट्र्याक र मुनिको जमिन (जुन भौतिक असम्भव हुन सक्छ) बीचको ठूलो दूरीको लागि क्षतिपूर्ति गर्न USB प्रसारण लाइनहरू पुन: इन्जिनियर गर्न सक्छौं, वा हामीले यसलाई बेवास्ता गर्न सक्छौं, र उत्तमको लागि आशा गर्न सक्छौं। USB FS धेरै क्षमा गर्न सक्छ, तर तपाईंको माइलेज फरक हुन सक्छ। यसले धेरै अनुप्रयोगहरूमा काम गर्ने सम्भावना छ, तर यो सम्भवतः USB मानक अनुरूप हुने छैन।

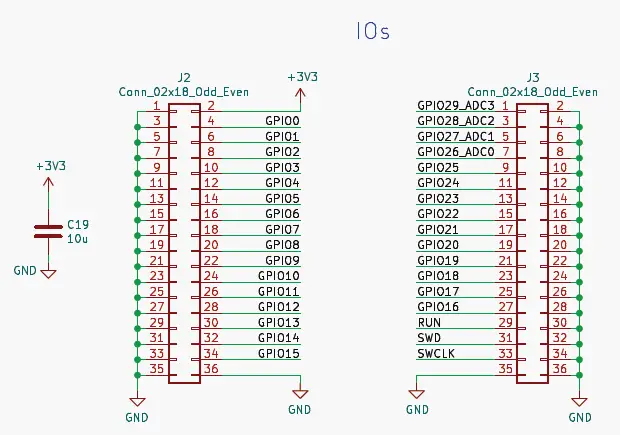

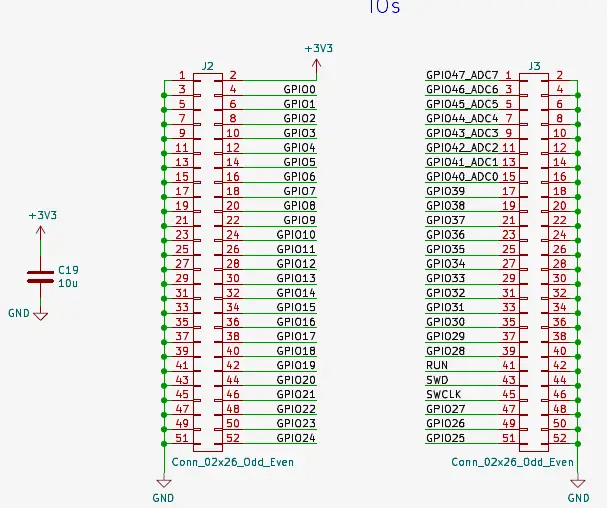

I/O हेडरहरू

चित्र 12. QFN2.54 संस्करणको 60mm I/O हेडरहरू देखाउँदै योजनाबद्ध खण्ड

- पहिले नै उल्लेख गरिएको USB कनेक्टरको अतिरिक्त, त्यहाँ दुईवटा पङ्क्ति 2.54mm हेडरहरू (चित्र 2 मा J3 र J12), बोर्डको प्रत्येक छेउमा एक जोडी छन्, जसमा बाँकी I/O जडान गरिएको छ। त्यहाँ RP30A मा 2350 GPIO छन्, जबकि RP48B मा 2350 GPIO छन्, त्यसैले मिनिमल बोर्डको यो संस्करणमा हेडरहरू थप पिनहरूको लागि अनुमति दिन ठूला हुन्छन् (चित्र 13 हेर्नुहोस्)।

- यो सामान्य उद्देश्यको डिजाइन भएको हुनाले, कुनै विशेष अनुप्रयोगलाई दिमागमा नराखी, I/O लाई प्रयोगकर्ताको इच्छा अनुसार जडान गर्न उपलब्ध गराइएको छ। प्रत्येक हेडरमा पिनको भित्री पङ्क्ति I/Os हो, र बाहिरी पङ्क्तिहरू सबै जमिनमा जोडिएका छन्। I/O कनेक्टरहरूमा धेरै आधारहरू समावेश गर्नु राम्रो अभ्यास हो। यसले कम प्रतिबाधा ग्राउन्डलाई कायम राख्न मद्दत गर्दछ, र प्रवाहहरूका लागि धेरै सम्भावित फिर्ती मार्गहरू प्रदान गर्न र त्यहाँबाट यात्रा गर्न मद्दत गर्दछ।

- I/O जडानहरू। यो इलेक्ट्रो-चुम्बकीय हस्तक्षेपलाई कम गर्न महत्त्वपूर्ण छ जुन सर्किट पूरा गर्न लामो, लूपिङ मार्गहरू लिने द्रुत स्विचिङ सिग्नलहरूको रिटर्न करन्टहरूको कारणले हुन सक्छ।

- दुबै हेडरहरू एउटै 2.54mm ग्रिडमा छन्, जसले यस बोर्डलाई अन्य चीजहरूमा जडान गर्न सजिलो बनाउँदछ, जस्तै ब्रेडबोर्डहरू। तपाईं दोहोरो पङ्क्ति हेडरको सट्टा एकल पङ्क्ति हेडरलाई फिट गर्ने विचार गर्न सक्नुहुन्छ, ग्राउन्ड जडानहरूको बाहिरी पङ्क्तिसँग वितरण गर्दै, यसलाई ब्रेडबोर्डमा फिट गर्न थप सुविधाजनक बनाउन।

चित्र 13. QFN2.54 संस्करणको 80mm I/O हेडरहरू देखाउँदै योजनाबद्ध खण्ड

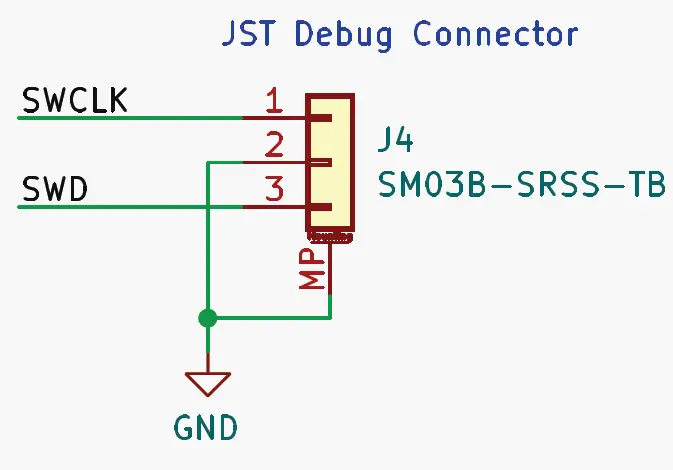

डिबग कनेक्टर

चित्र 14. SWD डिबगको लागि वैकल्पिक JST कनेक्टर देखाउँदै योजनाबद्ध खण्ड

अन-चिप डिबगिङको लागि, तपाईंले RP2350 को SWD इन्टरफेसमा जडान गर्न चाहनुहुन्छ। दुई पिन, SWD र SWCLK, 2.54mm हेडर, J3 मा उपलब्ध छन्, तपाईको रोजाइको डिबग प्रोबलाई सजिलैसँग जडान गर्न अनुमति दिन। यसका अतिरिक्त, मैले एक वैकल्पिक JST हेडर समावेश गरेको छु, जसले Raspberry Pi Debug Probe मा सजिलो जडानलाई अनुमति दिन्छ। तपाईंले यसलाई प्रयोग गर्न आवश्यक छैन, यदि तपाइँ सफ्टवेयर डिबग गर्न चाहानुहुन्छ भने 2.54mm हेडरहरू पर्याप्त हुनेछ, तर मलाई त्यसो गर्न थप सुविधाजनक लाग्छ। मैले तेर्सो कनेक्टर छनोट गरेको छु, धेरै जसो किनभने मलाई यसको रूप मनपर्छ, यो बोर्डको किनारमा नभए पनि, तर ठाडोहरू उपलब्ध छन्, थोरै फरक पदचिह्नको साथ।

बटनहरू

न्यूनतम डिजाइनमा अब एउटा होइन, तर दुईवटा बटनहरू छन्, जहाँ RP240 संस्करणमा कुनै पनि थिएन। एउटा USB बुट चयनको लागि हो जुन हामीले पहिले छलफल गरिसकेका छौं, तर दोस्रो 'रिसेट' बटन हो, जुन RUN पिनमा जोडिएको छ। यी मध्ये कुनै पनि कडा रूपमा आवश्यक छैन (यद्यपि USB बुट मोड आवश्यक भएमा BOOTSEL बटनलाई हेडर वा समानसँग प्रतिस्थापन गर्नुपर्नेछ), र यदि स्पेस वा लागत चिन्ताको विषय हो भने हटाउन सकिन्छ, तर तिनीहरू निश्चित रूपमा RP2350 प्रयोग गरेर धेरै टाढा छन्। थप सुखद अनुभव।

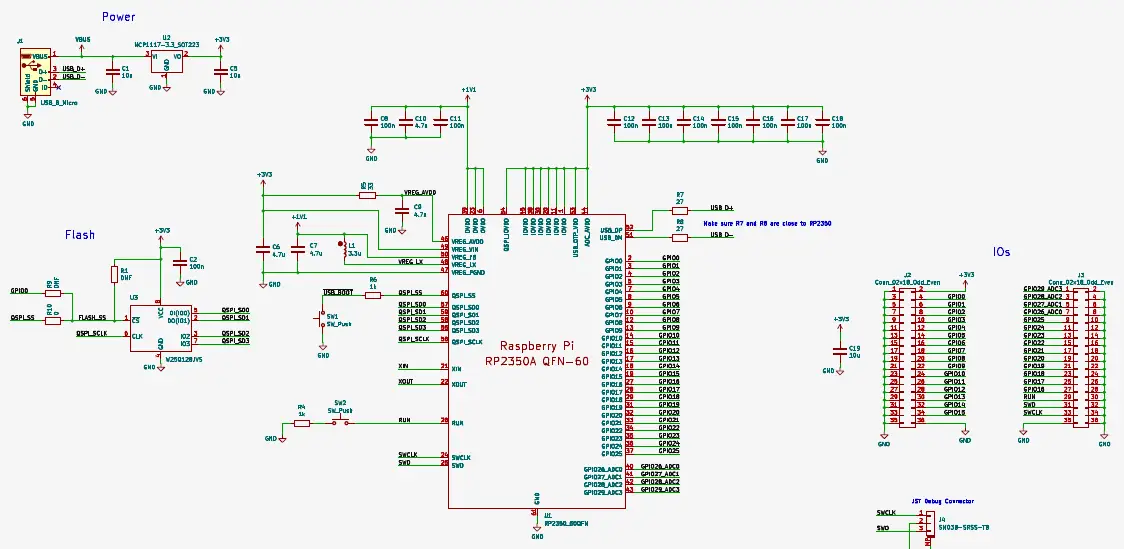

परिशिष्ट A: पूरा योजनाबद्ध -RP2350A संस्करण

चित्र 15. RP2350A को लागि न्यूनतम डिजाइनको पूर्ण योजना

परिशिष्ट B: पूरा योजनाबद्ध -RP2350B संस्करण

चित्र 16. RP2350B को लागि न्यूनतम डिजाइनको पूर्ण योजना

परिशिष्ट H: दस्तावेज रिलीज इतिहास

अगस्ट ८, २०२४

प्रारम्भिक रिलीज।

र रास्पबेरी पाई

Raspberry Pi Raspberry Pi Ltd को ट्रेडमार्क हो

रास्पबेरी पाई लिमिटेड

कागजातहरू / स्रोतहरू

|

रास्पबेरी Pi SC1631 रास्पबेरी माइक्रोकन्ट्रोलर [pdf] निर्देशन पुस्तिका SC1631 रास्पबेरी माइक्रोकन्ट्रोलर, SC1631, रास्पबेरी माइक्रोकन्ट्रोलर, माइक्रोकन्ट्रोलर |