Pengawal Mikro Raspberi Pi SC1631

Spesifikasi Produk

- Model: RP2350

- Pakej: QFN-60

- Storan Denyar Dalaman: Tidak

- Voltage Pengatur: Pengatur pensuisan pada cip

- Pin Pengatur: 5 (input 3.3V, output 1.1V, VREG_AVDD, VREG_LX, VREG_PGND)

Arahan Penggunaan Produk

- Bab 1: Pengenalan

- Siri RP2350 menawarkan pilihan pakej yang berbeza berbanding dengan siri RP2040. RP2350A dan RP2354A datang dalam pakej QFN-60 masing-masing tanpa dan dengan storan denyar dalaman, manakala RP2354B dan RP2350B datang dalam pakej QFN-80 dengan dan tanpa storan denyar.

- Bab 2: Kuasa

Siri RP2350 menampilkan vol pensuisan pada cip baharutage pengawal selia dengan lima pin. Pengawal selia ini memerlukan komponen luaran untuk operasi tetapi menawarkan kecekapan kuasa yang lebih tinggi pada arus beban yang lebih tinggi berbanding dengan pengawal selia linear dalam siri RP2040. Beri perhatian kepada sensitiviti hingar dalam pin VREG_AVDD yang membekalkan litar analog.

Soalan Lazim (FAQ)

- S: Apakah perbezaan utama antara RP2350A dan RP2350B?

A: Perbezaan utama terletak pada kehadiran storan denyar dalaman. RP2350A tidak mempunyai storan denyar dalaman manakala RP2350B. - S: Berapakah bilangan pin voltage pengawal selia dalam siri RP2350 mempunyai?

A: Jiltage regulator dalam siri RP2350 mempunyai lima pin.

Reka bentuk perkakasan dengan RP2350 Menggunakan mikropengawal RP2350 untuk membina papan dan produk

Kolofon

- © 2023-2024 Raspberry Pi Ltd

- Dokumentasi ini dilesenkan di bawah Creative Commons Attribution-NoDerivatives 4.0 International (CC BY-ND). tarikh binaan: 2024-08-08 versi binaan: c0acc5b-clean

- Notis penafian undang-undang

- DATA TEKNIKAL DAN KEBOLEHPERCAYAAN UNTUK PRODUK RASPBERRY PI (TERMASUK LEMBARAN DATA) SEPERTI YANG DIUBAHSUAI DARI SEMASA KE SEMASA (“SUMBER”) DISEDIAKAN OLEH RASPBERRY PI LTD (“RPL”) “SEBAGAIMANA ADANYA” DAN MANA-MANA WARANTI NYATA ATAU TERSIRAT, TIDAK TERMASUK, KEPADA, WARANTI TERSIRAT KEBOLEHPERDAGANGAN DAN KESESUAIAN UNTUK TUJUAN TERTENTU ADALAH DITOLAK. SEJAUH MAKSIMUM YANG DIBENARKAN OLEH UNDANG-UNDANG YANG BERKENAAN DALAM APA PUN RPL TIDAK AKAN BERTANGGUNGJAWAB ATAS SEBARANG KEROSAKAN LANGSUNG, TIDAK LANGSUNG, SAMPINGAN, KHAS, TEladan ATAU AKIBAT (TERMASUK, TETAPI TIDAK TERHAD KEPADA, PEROLEHAN PEROLEHAN PERKHIDMATAN PENGGANTIAN, DIRI PENGGANTIAN; , ATAU KEUNTUNGAN; ATAU GANGGUAN PERNIAGAAN) WALAUPUN APA PUN BERPUNCA DAN ATAS MANA-MANA TEORI LIABILITI, SAMA ADA DALAM KONTRAK, LIABILITI KETAT ATAU TORT (TERMASUK KECUAIAN ATAU LAIN-LAIN) YANG TIMBUL DALAM MANA-MANA CARA KELUAR DARIPADA PENGGUNAAN SUMBER DAYA, KEROSAKAN TERSEBUT.

- RPL berhak untuk membuat sebarang penambahbaikan, penambahbaikan, pembetulan atau sebarang pengubahsuaian lain pada SUMBER atau mana-mana produk yang diterangkan di dalamnya pada bila-bila masa dan tanpa notis lanjut.

RESOURCES bertujuan untuk pengguna mahir dengan tahap pengetahuan reka bentuk yang sesuai. Pengguna bertanggungjawab sepenuhnya untuk pemilihan dan penggunaan SUMBER dan sebarang aplikasi produk yang diterangkan di dalamnya. Pengguna bersetuju untuk menanggung rugi dan memastikan RPL tidak berbahaya terhadap semua liabiliti, kos, kerosakan atau kerugian lain yang timbul daripada penggunaan SUMBER. - RPL memberikan pengguna kebenaran untuk menggunakan RESOURCES semata-mata bersama dengan produk Raspberry Pi. Semua penggunaan lain SUMBER adalah dilarang. Tiada lesen diberikan kepada mana-mana RPL lain atau hak harta intelek pihak ketiga yang lain.

- AKTIVITI BERISIKO TINGGI. Produk Raspberry Pi tidak direka bentuk, dikilangkan atau dimaksudkan untuk digunakan dalam persekitaran berbahaya yang memerlukan prestasi selamat yang gagal, seperti dalam pengendalian kemudahan nuklear, navigasi pesawat atau sistem komunikasi, kawalan trafik udara, sistem senjata atau aplikasi kritikal keselamatan (termasuk sokongan hayat). sistem dan peranti perubatan lain), di mana kegagalan produk boleh membawa kepada kematian, kecederaan peribadi atau kerosakan fizikal atau alam sekitar yang teruk ("Aktiviti Berisiko Tinggi"). RPL secara khusus menafikan sebarang waranti tersurat atau tersirat kesesuaian untuk Aktiviti Berisiko Tinggi dan tidak menerima liabiliti untuk penggunaan atau kemasukan produk Raspberry Pi dalam Aktiviti Berisiko Tinggi.

- Produk Raspberry Pi disediakan tertakluk kepada Syarat Standard RPL. Peruntukan RPL bagi RESOURCES tidak mengembangkan atau mengubah suai Terma Standard RPL termasuk tetapi tidak terhad kepada penafian dan waranti yang dinyatakan di dalamnya.

Bab 1. Pengenalan

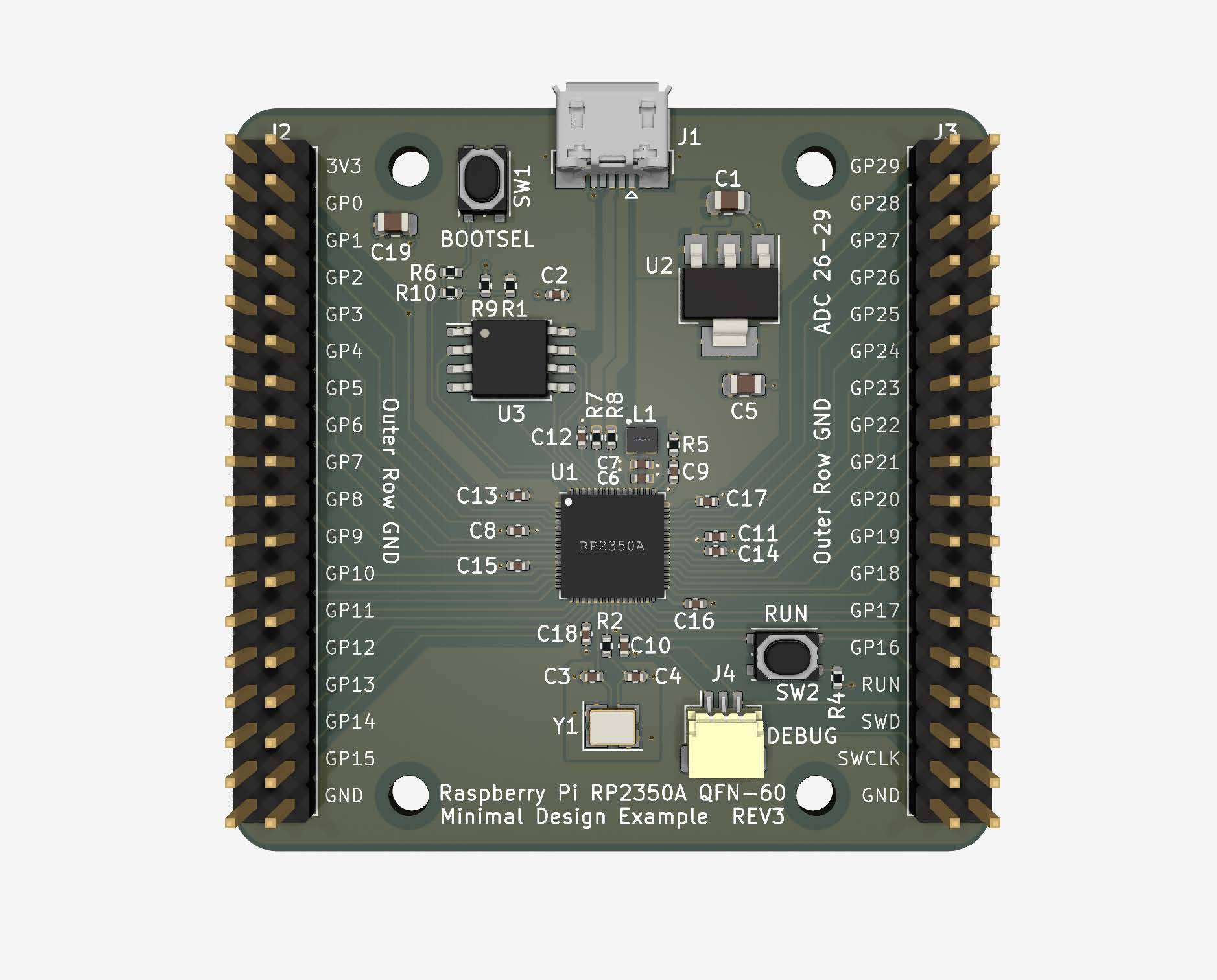

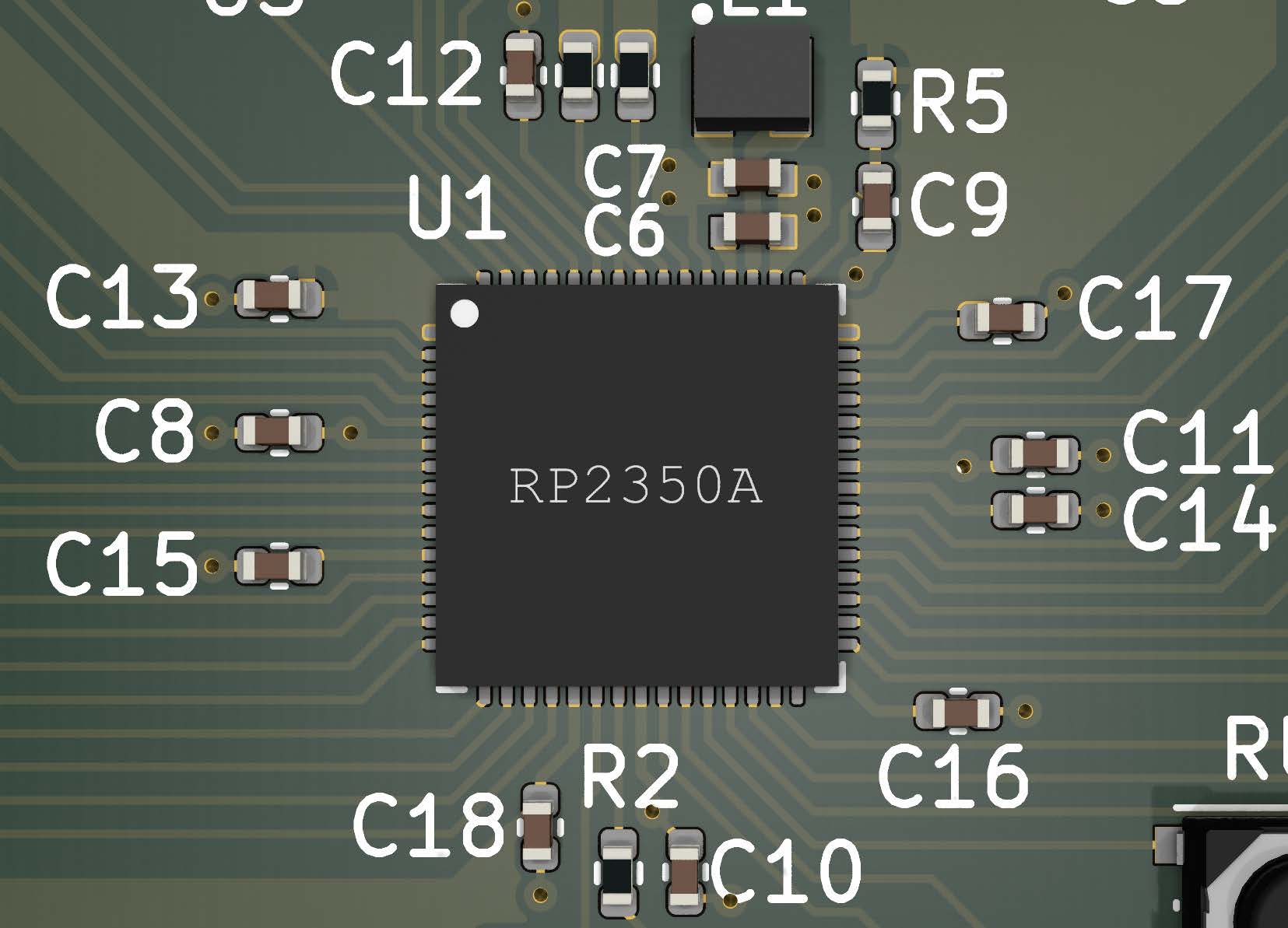

Rajah 1. Paparan KiCad 3D bagi bekas reka bentuk Minimal RP2350Aample

Apabila kami mula-mula memperkenalkan Raspberry Pi RP2040, kami juga mengeluarkan bekas reka bentuk 'Minimal'ample dan panduan yang disertakan Reka bentuk perkakasan dengan RP2040 yang diharapkan dapat menjelaskan bagaimana RP2040 boleh digunakan dalam papan litar ringkas, dan mengapa pelbagai pilihan komponen dibuat. Dengan ketibaan siri RP235x, tiba masanya untuk menyemak semula reka bentuk asal RP2040 Minimal, dan mengemas kininya untuk mengambil kira ciri baharu, dan juga untuk setiap varian pakej; RP2350A dengan pakej QFN-60, dan RP2350B yang merupakan QFN-80. Sekali lagi, reka bentuk ini dalam format Kicad (7.0), dan tersedia untuk dimuat turun (https://datasheets.raspberrypi.com/rp2350/Minimal-KiCAD.zip).

Papan Minimum

Papan Minimal asal adalah percubaan untuk menyediakan reka bentuk rujukan yang ringkas, menggunakan komponen luaran minimum yang diperlukan untuk menjalankan RP2040 dan masih mempunyai semua IO yang terdedah dan boleh diakses. Ini pada asasnya terdiri daripada sumber kuasa (pengatur linear 5V hingga 3.3V), pengayun kristal, memori denyar dan sambungan IO (soket USB mikro dan pengepala GPIO). Papan Minimal siri RP235x baharu sebahagian besarnya sama, tetapi dengan beberapa perubahan yang diperlukan disebabkan perkakasan baharu. Di samping itu, dan walaupun agak bertentangan dengan sifat reka bentuk yang minimum, saya telah menambah beberapa butang untuk bootsel dan run, bersama-sama dengan pengepala SWD yang berasingan, yang sepatutnya bermakna pengalaman nyahpepijat yang kurang mengecewakan kali ini. Reka bentuk tidak semestinya memerlukan butang ini, isyarat masih tersedia pada pengepala, dan ia boleh ditinggalkan jika anda sangat mementingkan kos atau ruang, atau mempunyai kecenderungan masokistik.

RP2040 vs siri RP235x

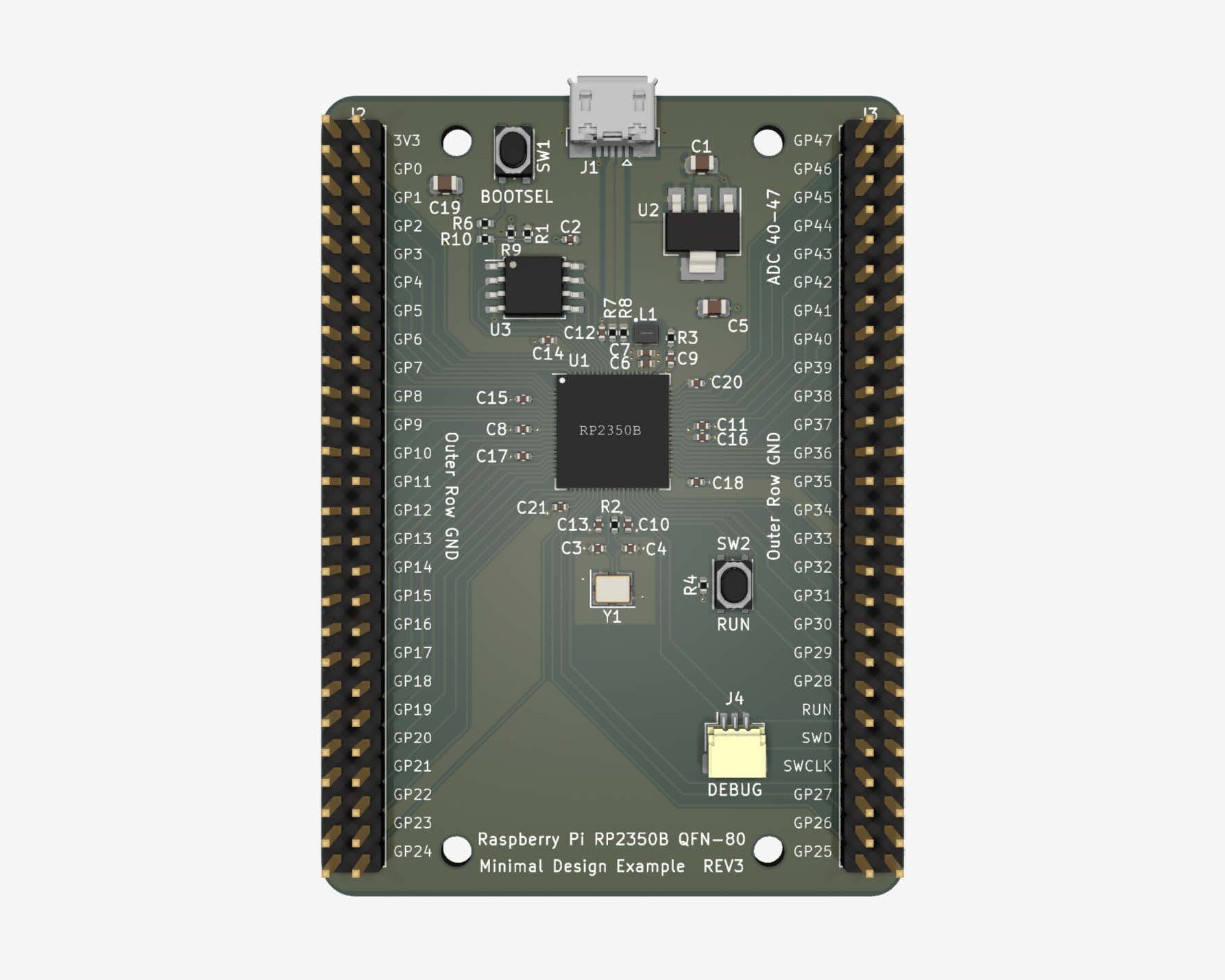

Perubahan yang paling jelas adalah dalam pakej. Manakala RP2040 ialah 7x7mm QFN-56, siri RP235x kini mempunyai empat ahli berbeza. Terdapat dua peranti yang berkongsi pakej QFN-60 yang sama; RP2350A yang tidak mengandungi storan denyar dalaman, dan RP2354A yang mengandungi. Begitu juga, QFN-80 juga datang dalam dua perisa; RP2354B dengan denyar, dan RP2350B tanpa. Peranti QFN-60 dan RP2040 asal berkongsi warisan yang samatage.

Setiap satunya mempunyai 30 GPIO, empat daripadanya juga disambungkan ke ADC, dan bersaiz 7x7mm. Walaupun begitu, RP2350A bukanlah pengganti drop-in untuk RP2040, kerana bilangan pin pada setiap satu adalah berbeza. Sebaliknya, cip QFN-80 kini mempunyai 48 GPIO, dan lapan daripadanya kini mampu ADC. Oleh sebab itu, kami kini mempunyai dua papan Minimal; satu untuk peranti 60 pin dan satu untuk 80. Papan Minimal ini direka terutamanya untuk bahagian tanpa denyar dalaman (RP2350), namun reka bentuk boleh digunakan dengan mudah dengan peranti denyar dalaman (RP2354) dengan hanya mengecualikan denyar onboard. memori, atau bahkan menggunakannya sebagai peranti denyar sekunder (lebih lanjut mengenai perkara ini kemudian). Terdapat sedikit perbezaan antara kedua-dua papan, selain fakta versi QFN-80 mempunyai baris pengepala yang lebih panjang untuk menampung GPIO tambahan, dan oleh itu papan itu lebih besar.

Selain daripada pakej, perbezaan peringkat papan terbesar antara siri RP235x dan RP2040 ialah bekalan kuasa. Siri RP235x mempunyai beberapa pin kuasa baharu dan pengawal selia dalaman yang berbeza. Pengawal selia linear 100mA RP2040 telah digantikan dengan pengawal selia pensuisan 200mA, dan oleh itu, ia memerlukan beberapa litar yang sangat khusus, dan tiada sedikit penjagaan yang diambil dengan susun atur. Adalah amat disyorkan agar anda mengikuti dengan teliti susun atur dan pemilihan komponen kami; kami telah pun melalui kesakitan kerana perlu membuat beberapa lelaran reka bentuk, jadi harap anda tidak perlu melakukannya.

Rajah 2. Paparan KiCad 3D bagi bekas reka bentuk Minimal RP2350Bample

Reka Bentuk

Niat reka bentuk Minimal examples adalah untuk mencipta sepasang papan ringkas menggunakan siri RP235x, yang sepatutnya murah dan mudah dibuat, tanpa menggunakan teknologi PCB yang eksotik yang tidak perlu. Oleh itu, papan Minimal adalah reka bentuk 2 lapisan, menggunakan komponen yang sepatutnya tersedia secara umum, dan semuanya dipasang pada bahagian atas papan. Walaupun bagus untuk menggunakan komponen yang besar dan mudah dipateri dengan tangan, nada kecil cip QFN (0.4mm) bermakna menggunakan beberapa komponen pasif 0402 (1005 metrik) tidak dapat dielakkan jika semua GPIO akan digunakan. Walaupun komponen pematerian tangan 0402 tidak terlalu mencabar dengan besi pematerian yang baik, adalah sangat mustahil untuk memateri QFN tanpa peralatan pakar.

Dalam beberapa bahagian seterusnya, saya akan cuba menerangkan untuk tujuan litar tambahan, dan mudah-mudahan bagaimana kami membuat pilihan yang kami lakukan. Memandangkan saya sebenarnya akan bercakap tentang dua reka bentuk berasingan, satu untuk setiap saiz pakej, saya telah cuba memastikan perkara semudah yang saya boleh. Seboleh-bolehnya, semua rujukan komponen untuk kedua-dua papan adalah sama, jadi jika saya merujuk kepada U1, R1, dan lain-lain, maka ia sama relevan dengan kedua-dua papan. Pengecualian yang jelas adalah apabila komponen hanya berada pada salah satu papan (dalam semua kes, ini akan berada pada varian 80 pin yang lebih besar), maka komponen yang dimaksudkan hanya akan berada pada reka bentuk QFN-80; untuk bekasample, R13 hanya muncul di papan ini.

Bab 2. Kuasa

Bekalan kuasa siri RP235x dan RP2040 agak berbeza kali ini, walaupun dalam konfigurasi paling mudah, ia masih memerlukan dua bekalan, 3.3V dan 1.1V. Siri RP235x pada masa yang sama lebih mementingkan kuasa, kerana prestasinya lebih tinggi, dan juga lebih jimat (apabila dalam keadaan kuasa rendah) berbanding pendahulunya, jadi pengawal selia linear pada RP2040 telah dinaik taraf dengan pengawal selia pensuisan. Ini membolehkan kami lebih cekap kuasa pada arus yang lebih tinggi (sehingga 200mA berbanding 100mA sebelumnya).

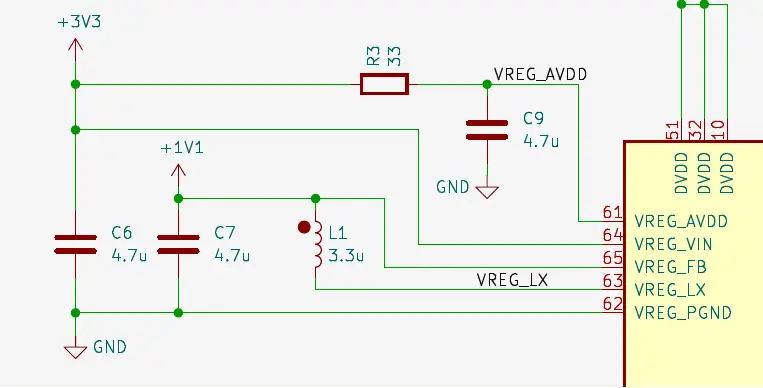

Jilid pada cip baharutage pengawal selia

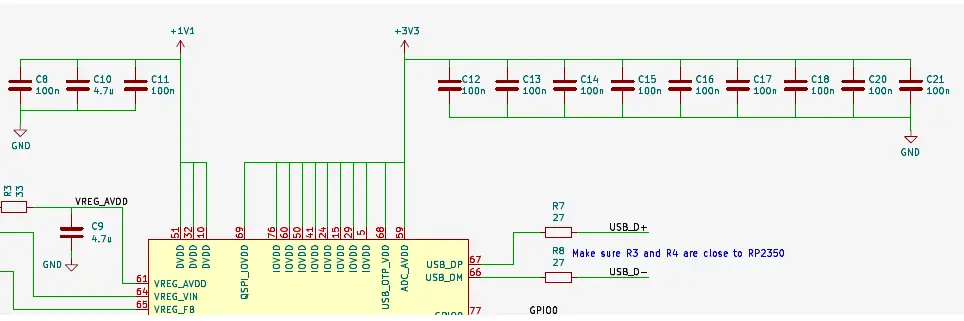

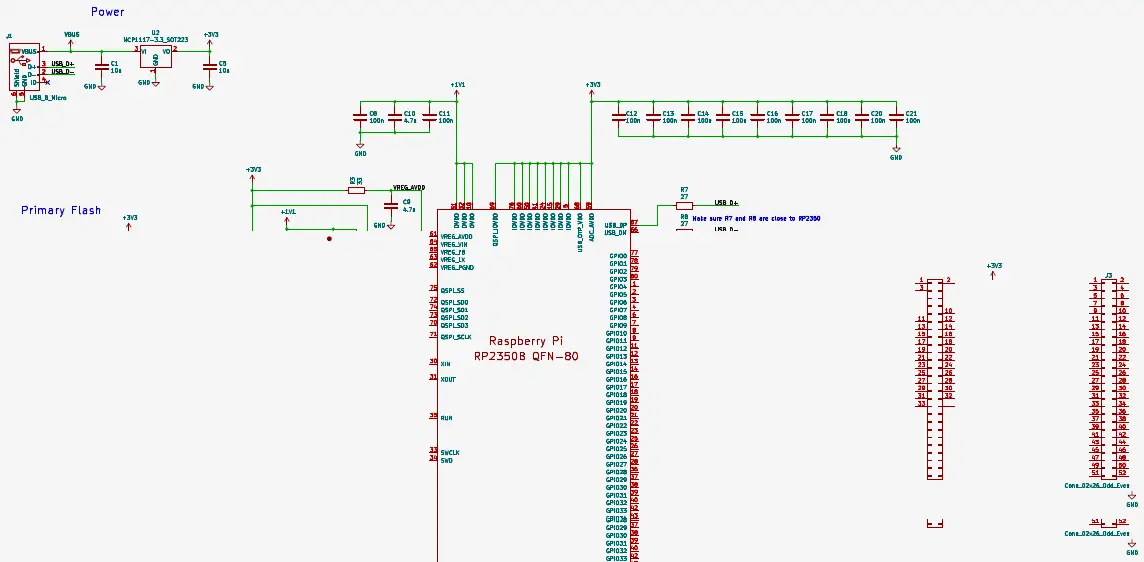

Rajah 3. Bahagian skematik menunjukkan litar pengatur dalaman

Pengatur linear RP2040 mempunyai dua pin, input 3.3V dan output 1.1V untuk membekalkan DVDD pada cip. Kali ini, pengawal selia siri RP235x mempunyai lima pin, dan memerlukan beberapa komponen luaran untuk menjadikannya berfungsi. Walaupun ini kelihatan agak mundur dari segi kebolehgunaan, pengawal selia pensuisan mempunyai advantage menjadi lebih cekap kuasa pada arus beban yang lebih tinggi.

Seperti namanya, pengawal selia dengan pantas menghidupkan dan mematikan transistor dalaman yang menyambungkan vol input 3.3Vtage (VREG_VIN) ke pin VREG_LX, dan dengan bantuan induktor (L1) dan kapasitor keluaran (C7), ia boleh menghasilkan vol keluaran DCtage yang telah diundur daripada input. Pin VREG_FB memantau vol keluartage, dan melaraskan nisbah hidup/mati bagi kitaran pensuisan, untuk memastikan bahawa vol yang diperlukantage dikekalkan. Memandangkan arus besar ditukar daripada VREG_VIN ke VREG_LX, kapasitor besar (C6) yang hampir dengan input diperlukan, jadi kami tidak terlalu mengganggu bekalan 3.3V. Bercakap tentang arus pensuisan yang besar ini, pengawal selia juga dilengkapi dengan sambungan balik tanah sendiri, VREG_PGND. Begitu juga dengan VREG_VIN dan VREG_LX, susun atur sambungan ini adalah kritikal, dan sementara VREG_PGND mesti disambungkan ke GND utama, ia mesti dilakukan dengan cara yang semua arus pensuisan besar kembali terus ke pin PGND, tanpa mengganggu seluruh GND terlalu banyak.

Pin terakhir ialah VREG_AVDD, yang membekalkan litar analog dalam pengawal selia, dan ini sangat sensitif kepada bunyi.

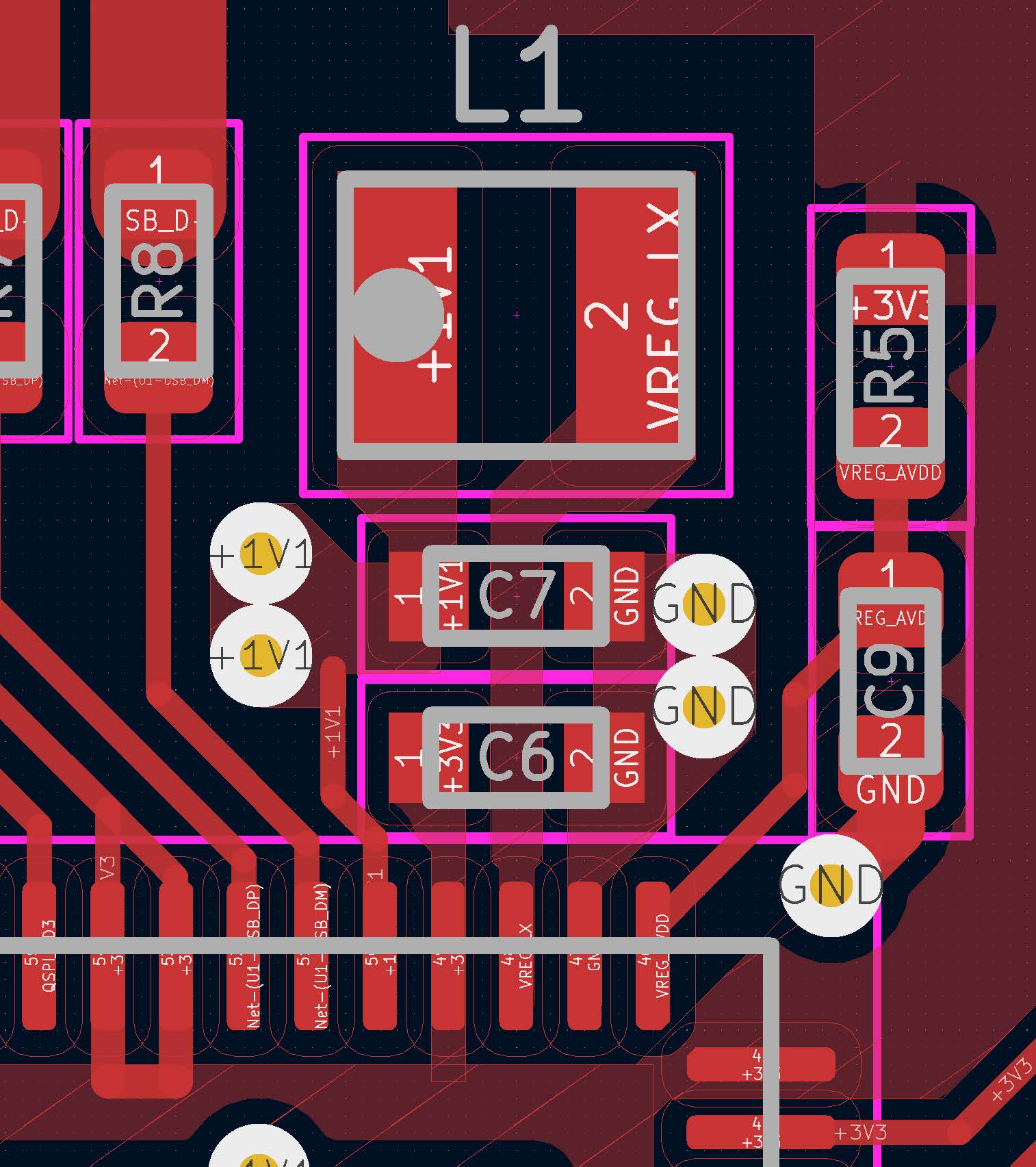

Rajah 4. Bahagian skematik menunjukkan susun atur PCB pengawal selia

- Susun atur pengawal selia pada papan minimum mencerminkan rapat Raspberry Pi Pico 2. Banyak kerja telah dilakukan dalam reka bentuk litar ini, dengan banyak lelaran PCB diperlukan untuk menjadikannya sebaik mungkin. boleh. Walaupun anda boleh meletakkan komponen ini dalam pelbagai cara yang berbeza dan masih membuat pengawal selia 'berfungsi' (iaitu, menghasilkan vol outputtage pada kira-kira tahap yang betul, cukup baik untuk menjalankan kodnya), kami mendapati bahawa pengawal selia kami perlu dirawat dengan cara yang betul untuk memastikan ia gembira, dan dengan gembira, saya maksudkan menghasilkan vol keluaran yang betultage di bawah julat keadaan arus beban.

- Semasa menjalankan eksperimen kami mengenai perkara ini, kami agak kecewa kerana diingatkan bahawa dunia fizik yang menyusahkan tidak boleh selalu diabaikan. Kami, sebagai jurutera, sebahagian besarnya mencuba dan melakukan perkara ini; memudahkan komponen, mengabaikan (selalunya) sifat fizikal yang tidak penting dan sebaliknya memfokuskan pada harta yang kita minati. Contohnyaample, perintang mudah bukan sahaja mempunyai rintangan, tetapi juga induktansi, dan lain-lain. Dalam kes kami, kami (semula) mendapati bahawa induktor mempunyai medan magnet yang berkaitan dengannya, dan yang penting, memancar ke arah bergantung pada arah mana gegelung adalah luka, dan arah aliran arus. Kami juga diingatkan bahawa induktor terlindung 'sepenuhnya' tidak bermakna apa yang anda fikirkan. Medan magnet dilemahkan pada tahap yang besar, tetapi ada yang masih terlepas. Kami mendapati bahawa prestasi pengawal selia boleh dipertingkatkan secara besar-besaran jika induktor adalah 'cara bulat yang betul'.

- Ternyata medan magnet yang dipancarkan daripada induktor 'salah arah pusingan' mengganggu kapasitor keluaran pengawal selia (C7), yang seterusnya mengganggu litar kawalan dalam RP2350. Dengan induktor dalam orientasi yang betul, dan susun atur yang tepat serta pemilihan komponen yang digunakan di sini, maka masalah ini hilang. Sudah pasti akan ada susun atur, komponen, dll, yang boleh berfungsi dengan induktor dalam sebarang orientasi, tetapi mereka kemungkinan besar akan menggunakan lebih banyak ruang PCB untuk berbuat demikian. Kami telah menyediakan reka letak yang disyorkan ini untuk menjimatkan banyak masa kejuruteraan yang telah kami habiskan untuk membangunkan dan memperhalusi penyelesaian yang padat dan berkelakuan baik ini.

- Lebih penting lagi, kami akan mengatakan bahawa jika anda memilih untuk tidak menggunakan bekas kamiample, maka anda berbuat demikian atas risiko anda sendiri. Sama seperti yang telah kami lakukan dengan RP2040 dan litar kristal, di mana kami menegaskan (baik, amat mencadangkan) anda menggunakan bahagian tertentu (kami akan melakukannya sekali lagi dalam bahagian kristal dokumen ini).

- Arah arah induktor kecil ini agak diabaikan secara universal, dengan orientasi penggulungan gegelung mustahil untuk disimpulkan, dan juga diedarkan secara rawak di sepanjang gulungan komponen. Saiz bekas induktor yang lebih besar selalunya didapati mempunyai tanda kekutuban padanya, namun kami tidak menemui yang sesuai dalam saiz kes 0806 (2016 metrik) yang telah kami pilih. Untuk tujuan ini, kami telah bekerjasama dengan Abracon untuk menghasilkan bahagian 3.3μH dengan titik untuk menunjukkan kekutuban, dan yang penting, datang pada kekili dengan semuanya sejajar dengan cara yang sama. TBD akan (atau tidak lama lagi) disediakan kepada orang ramai daripada pengedar. Seperti yang dinyatakan sebelum ini, bekalan VREG_AVDD sangat sensitif kepada bunyi bising, dan oleh itu perlu ditapis. Kami mendapati bahawa kerana VREG_AVDD hanya menarik sekitar 200μA, penapis RC 33Ω dan 4.7μF adalah memadai.

- Jadi, untuk meringkaskan, komponen yang digunakan akan…

- C6, C7 & C9 – 4.7μF (0402, 1005 metrik)

- L1 – Abracon TBD (0806, 2016 metrik)

- R3 – 33Ω (0402, 1005 metrik)

- Lembaran data RP2350 mempunyai perbincangan yang lebih terperinci tentang cadangan susun atur pengawal selia, sila lihat Komponen Luaran dan keperluan susun atur PCB.

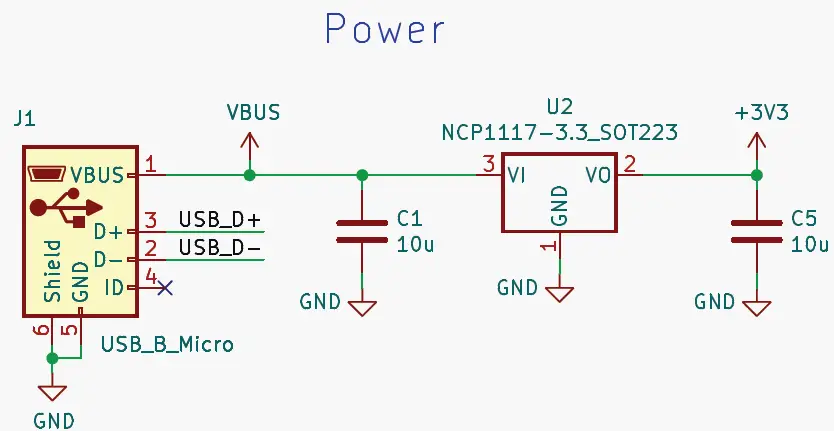

Bekalan input

Sambungan kuasa input untuk reka bentuk ini adalah melalui pin 5V VBUS penyambung Micro-USB (dilabelkan J1 dalam Rajah 5). Ini ialah kaedah biasa untuk menjanakan peranti elektronik, dan ia masuk akal di sini, kerana RP2350 mempunyai fungsi USB, yang akan kami pendawaian ke pin data penyambung ini. Memandangkan kami hanya memerlukan 3.3V untuk reka bentuk ini (bekalan 1.1V datang dari dalaman), kami perlu menurunkan bekalan USB 5V yang masuk, dalam kes ini, menggunakan vol luaran yang laintage pengawal selia, dalam kes ini pengawal selia linear (aka pengawal selia Low Drop Out, atau LDO). Setelah memuji kebaikan menggunakan pengawal selia pensuisan yang cekap sebelum ini, ia juga boleh menjadi pilihan yang bijak untuk menggunakannya di sini juga, tetapi saya telah memilih untuk kesederhanaan. Pertama, menggunakan LDO hampir selalu lebih mudah. Tidak ada pengiraan yang diperlukan untuk mengetahui saiz induktor yang perlu anda gunakan, atau berapa besar kapasitor keluaran, dan susun atur biasanya juga lebih mudah. Kedua, menyelamatkan setiap titisan kuasa terakhir bukanlah matlamat di sini; jika ya, saya serius akan mempertimbangkan untuk menggunakan pengawal selia pensuisan, dan anda boleh mencari bekasampdengan berbuat demikian pada Raspberry Pi Pico 2. Dan ketiga, saya boleh 'meminjam' litar yang saya gunakan sebelum ini pada papan Minimal versi RP2040. NCP1117 (U2) yang dipilih di sini mempunyai output tetap 3.3V, tersedia secara meluas, dan boleh memberikan arus sehingga 1A, yang akan mencukupi untuk kebanyakan reka bentuk. Melihat lembaran data untuk NCP1117 memberitahu kami bahawa peranti ini memerlukan kapasitor 10μF pada input, dan satu lagi pada output (C1 dan C5).

Pemuat penyahgandingan

Rajah 6. Bahagian skema yang menunjukkan input bekalan kuasa RP2350, voltage pengawal selia dan pemuat penyahgandingan

Satu lagi aspek reka bentuk bekalan kuasa ialah kapasitor penyahgandingan yang diperlukan untuk RP2350. Ini menyediakan dua fungsi asas. Pertama, mereka menapis bunyi bekalan kuasa, dan kedua, menyediakan bekalan cas tempatan yang boleh digunakan oleh litar di dalam RP2350 dalam masa yang singkat. Ini menghalang voltage tahap di kawasan berhampiran daripada menurun terlalu banyak apabila permintaan semasa tiba-tiba meningkat. Kerana ini, adalah penting untuk meletakkan penyahgandingan dekat dengan pin kuasa. Biasanya, kami mengesyorkan penggunaan kapasitor 100nF bagi setiap pin kuasa, namun, kami menyimpang daripada peraturan ini dalam beberapa keadaan.

Rajah 7. Bahagian susun atur yang menunjukkan penghalaan dan penyahgandingan RP2350

- Pertama, untuk dapat mempunyai ruang yang cukup untuk semua pin cip boleh dialihkan keluar, jauh dari peranti, kita perlu berkompromi dengan jumlah kapasitor penyahgandingan yang boleh kita gunakan. Dalam reka bentuk ini, pin 53 dan 54 RP2350A (pin 68 dan 69 RP2350B) berkongsi satu kapasitor (C12 dalam Rajah 7 dan Rajah 6), kerana tidak terdapat banyak ruang pada sisi peranti itu, dan komponen dan susun atur pengawal selia diutamakan.

- Kekurangan ruang ini agak boleh diatasi jika kita menggunakan teknologi yang lebih kompleks/mahal, seperti komponen yang lebih kecil, atau PCB empat lapisan dengan komponen pada kedua-dua bahagian atas dan bawah. Ini adalah pertukaran reka bentuk; kami telah mengurangkan kerumitan dan kos, dengan mengorbankan kemuatan penyahgandingan yang kurang, dan kapasitor yang jauh sedikit daripada cip daripada yang optimum (ini meningkatkan kearuhan). Ini boleh mempunyai kesan mengehadkan kelajuan maksimum reka bentuk boleh beroperasi pada, sebagai voltage bekalan boleh menjadi terlalu bising dan jatuh di bawah vol minimum yang dibenarkantage; tetapi untuk kebanyakan aplikasi, pertukaran ini sepatutnya boleh diterima.

- Sisihan lain daripada peraturan 100nF adalah supaya kita boleh menambah baik voltage prestasi pengawal selia; kami mengesyorkan menggunakan 4.7μF untuk C10, yang diletakkan pada sisi lain cip daripada pengawal selia.

Bab 3. Memori Denyar

kilat utama

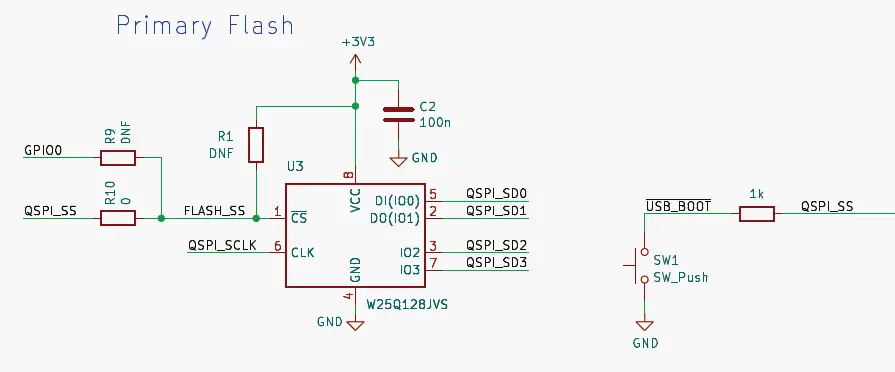

Rajah 8. Bahagian skematik menunjukkan memori denyar utama dan litar USB_BOOT

- Untuk dapat menyimpan kod program yang mana RP2350 boleh boot dan dijalankan, kita perlu menggunakan memori kilat, khususnya, memori kilat quad SPI. Peranti yang dipilih di sini ialah peranti W25Q128JVS (U3 dalam Rajah 8), iaitu cip 128Mbit (16MB). Ini adalah saiz memori terbesar yang boleh disokong oleh RP2350. Jika aplikasi tertentu anda tidak memerlukan storan sebanyak itu, maka memori yang lebih kecil dan lebih murah boleh digunakan sebagai ganti.

- Memandangkan bas data ini boleh menjadi frekuensi yang agak tinggi dan kerap digunakan, pin QSPI RP2350 harus disambungkan terus ke denyar, menggunakan sambungan pendek untuk mengekalkan integriti isyarat, dan juga mengurangkan crosstalk dalam litar sekeliling. Crosstalk adalah di mana isyarat pada satu rangkaian litar boleh mendorong vol yang tidak diinginitages pada litar jiran, yang berpotensi menyebabkan ralat berlaku.

- Isyarat QSPI_SS ialah kes khas. Ia disambungkan kepada denyar secara langsung, tetapi ia juga mempunyai dua perintang (baik, empat, tetapi saya akan meneruskannya kemudian) yang disambungkan kepadanya. Yang pertama (R1) ialah penarikan ke atas kepada bekalan 3.3V. Memori denyar memerlukan input pilih cip berada pada vol yang samatage sebagai pin bekalan 3.3V sendiri apabila peranti dikuasakan, jika tidak, ia tidak berfungsi dengan betul. Apabila RP2350 dikuasakan, pin QSPI_SSnya akan lalai secara automatik kepada pull-up, tetapi terdapat tempoh masa yang singkat semasa menghidupkan di mana keadaan pin QSPI_SS tidak dapat dijamin. Penambahan perintang tarik-up memastikan bahawa keperluan ini akan sentiasa dipenuhi. R1 ditandakan sebagai DNF (Do Not Fit) pada skema, kerana kami telah mendapati bahawa dengan peranti denyar khusus ini, penarikan luar tidak diperlukan. Walau bagaimanapun, jika denyar yang berbeza digunakan, ia mungkin menjadi penting untuk dapat memasukkan perintang 10kΩ di sini, jadi ia telah disertakan untuk berjaga-jaga.

- Perintang kedua (R6) ialah perintang 1kΩ, disambungkan kepada butang tekan (SW1) berlabel 'USB_BOOT'. Ini kerana pin QSPI_SS digunakan sebagai 'tali but'; RP2350 menyemak nilai I/O ini semasa jujukan but, dan jika ia didapati logik 0, maka RP2350 kembali kepada mod BOOTSEL, di mana RP2350 menampilkan dirinya sebagai peranti storan massa USB, dan kod boleh disalin terus kepadanya. Jika kita hanya menekan butang, kita tarik pin QSPI_SS ke tanah, dan jika peranti kemudiannya ditetapkan semula (cth dengan menogol pin RUN), RP2350 akan dimulakan semula dalam mod BOOTSEL dan bukannya cuba menjalankan kandungan denyar. Perintang ini, R2 dan R6 (R9 dan R10 juga), harus diletakkan berdekatan dengan cip denyar, jadi kami mengelakkan panjang tambahan trek tembaga yang boleh menjejaskan isyarat.

- Semua perkara di atas digunakan secara khusus untuk RP2350, yang tidak mempunyai denyar dalaman. Sudah tentu, peranti RP2354 mempunyai memori kilat dalaman 2MB, jadi memori U3 luaran tidak diperlukan, jadi U3 boleh dialih keluar dengan selamat daripada skema, atau dibiarkan tanpa penghuni. Dalam mana-mana kes ini, kami masih mahu memastikan suis USB_BOOT disambungkan ke QSPI_SS, supaya kami masih boleh memasuki mod but USB.

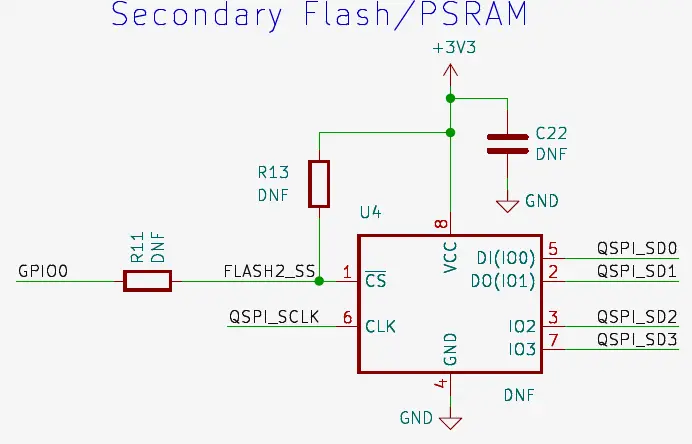

Denyar sekunder atau PSRAM

- Siri RP235x kini menyokong peranti memori kedua menggunakan pin QSPI yang sama, dengan GPIO menyediakan pilihan cip tambahan. Jadi, jika kita menggunakan RP2354 (yang mempunyai denyar dalaman), maka kita boleh menggunakan U3 sebagai denyar sekunder, atau malah menggantikannya dengan peranti PSRAM. Untuk melakukan ini, kita perlu memutuskan sambungan QSPI_SS daripada U3, dan sebaliknya menyambungkannya kepada GPIO yang sesuai. GPIO terdekat yang mampu menjadi pilihan cip (XIP_CS1n) ialah GPIO0, jadi dengan mengalih keluar 0Ω daripada R10, dan memasangkannya pada R9, kami kini boleh mengakses U3 sebagai tambahan kepada denyar pada cip. Untuk mengambil advan sepenuhnyatage daripada ciri ini, di mana kami mempunyai dua peranti memori luaran supaya bahagian RP2350 tanpa denyar boleh mendapat manfaat, lebih besar daripada dua papan Minimal, untuk RP2350B, termasuk jejak pilihan (U4) untuk cip memori tambahan.

Rajah 9. Bahagian skema yang menunjukkan peranti memori sekunder pilihan

Untuk dapat menggunakan peranti ini, ia pastinya perlu diisi , serta R11 (0Ω), dan R13 (10KΩ). Penambahan R11 menghubungkan GPIO0 (isyarat XIP_CS1n) ke pilihan cip memori kedua. Tarik ke atas pada pin pilih cip pasti diperlukan kali ini, kerana keadaan lalai GPIO0 akan ditarik rendah pada kuasa naik, yang akan menyebabkan peranti denyar kami gagal. C22 juga diperlukan untuk menyediakan penyahgandingan bekalan kuasa tempatan untuk U4.

Cip kilat yang disokong

Urutan probe kilat awal, digunakan oleh bahagian bawah untuk mengekstrak s keduatage daripada denyar, menggunakan perintah baca bersiri 03h, dengan pengalamatan 24-bit, dan jam bersiri lebih kurang 1MHz. Ia berulang kali mengitar melalui empat kombinasi kekutuban jam dan fasa jam, mencari detik yang sahtage CRC32 checksum.

Sebagai s keduatage kemudian bebas untuk mengkonfigurasi laksana-di-tempat menggunakan perintah baca bersiri 03h yang sama, RP2350 boleh melakukan eksekusi flash cache di tempat dengan mana-mana cip yang menyokong bacaan bersiri 03h dengan pengalamatan 24-bit, yang merangkumi kebanyakan peranti flash 25-siri . SDK menyediakan bekasample kedua stage untuk CPOL=0 CPHA=0, pada https://github.com/raspberrypi/pico-sdk/blob/master/src/rp2350/boot_stage2/boot2_generic_03h.S. Untuk menyokong pengaturcaraan kilat menggunakan rutin di bahagian bawah , peranti juga mesti bertindak balas kepada arahan berikut:

- 02j 256-bait program halaman

- Daftar status 05j dibaca

- 06h set tulis dayakan selak

- Padam sektor 20j 4kB

RP2350 juga menyokong pelbagai jenis mod akses dwi-SPI dan QSPI. Untuk example, https://github.com/raspberrypi/pico-sdk/blob/master/src/rp2350/boot_stage2/boot2_w25q080.S mengkonfigurasi peranti Winbond W25Q-siri untuk mod baca berterusan quad-IO, di mana RP2350 menghantar alamat quad-IO (tanpa awalan arahan) dan denyar bertindak balas dengan data quad-IO.

Beberapa berhati-hati diperlukan dengan mod XIP denyar apabila peranti denyar berhenti bertindak balas kepada arahan bersiri standard, seperti mod baca berterusan Winbond yang dinyatakan di atas. Ini boleh menyebabkan masalah apabila RP2350 ditetapkan semula, tetapi peranti denyar tidak dikitar kuasa, kerana denyar kemudiannya tidak akan bertindak balas kepada urutan probe denyar bootrom. Sebelum mengeluarkan bacaan bersiri 03h, bootrom sentiasa mengeluarkan urutan tetap berikut, yang merupakan urutan usaha terbaik untuk menghentikan XIP pada julat peranti denyar:

- CSn=1, IO[3:0]=4'b0000 (melalui tarik ke bawah untuk mengelakkan pertengkaran), keluarkan ×32 jam

- CSn=0, IO[3:0]=4'b1111 (melalui tarik naik untuk mengelakkan pertengkaran), keluarkan ×32 jam

- CSn=1

- CSn=0, MOSI=1'b1 (didorong rendah-Z, semua I/Os Hi-Z lain), keluarkan ×16 jam

Jika peranti pilihan anda tidak bertindak balas kepada jujukan ini apabila dalam mod bacaan berterusannya, maka ia mesti disimpan dalam keadaan di mana setiap pemindahan diawali dengan arahan bersiri, jika tidak, RP2350 tidak akan dapat pulih selepas tetapan semula dalaman.

Untuk butiran lanjut tentang QSPI , sila lihat QSPI Memory Interface (QMI) dalam lembaran data RP2350.

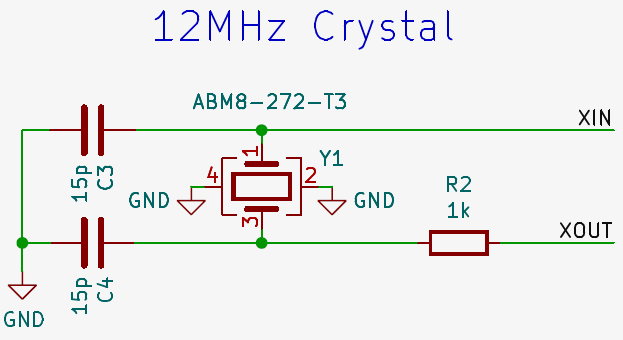

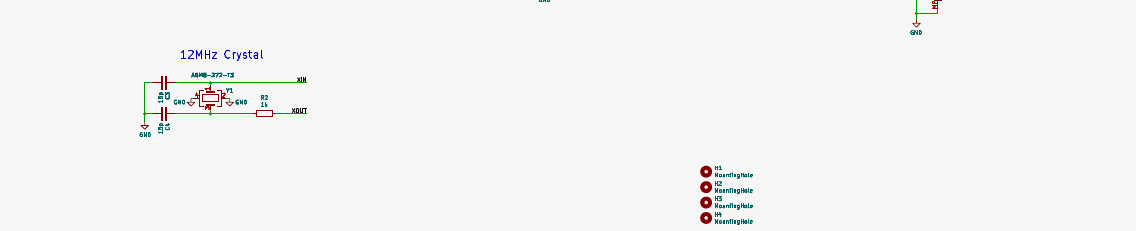

Bab 4. Pengayun Kristal

Rajah 10. Bahagian skematik menunjukkan pengayun kristal dan kapasitor beban

- Tegasnya, RP2350 sebenarnya tidak memerlukan sumber jam luaran, kerana ia mempunyai pengayun dalaman sendiri. Walau bagaimanapun, kerana kekerapan pengayun dalaman ini tidak ditakrifkan atau dikawal dengan baik, berbeza dari cip ke cip, serta dengan vol bekalan yang berbeza.tages dan suhu, adalah disyorkan untuk menggunakan sumber frekuensi luaran yang stabil. Aplikasi yang bergantung pada frekuensi tepat tidak boleh dilakukan tanpa sumber frekuensi luaran, USB adalah bekas utamaample.

- Menyediakan sumber frekuensi luaran boleh dilakukan dalam satu daripada dua cara: sama ada dengan menyediakan sumber jam dengan output CMOS (gelombang persegi IOVDD voltage) ke dalam pin XIN, atau dengan menggunakan kristal 12MHz yang disambungkan antara

- XIN dan XOUT. Menggunakan kristal adalah pilihan pilihan di sini, kerana kedua-duanya agak murah dan sangat tepat.

- Kristal yang dipilih untuk reka bentuk ini ialah ABM8-272-T3 (Y1 dalam Rajah 10). Ini adalah kristal 12MHz yang sama yang digunakan pada Raspberry Pi Pico dan Raspberry Pi Pico 2. Kami amat mengesyorkan menggunakan kristal ini bersama-sama dengan litar yang disertakan untuk memastikan jam bermula dengan cepat dalam semua keadaan tanpa merosakkan kristal itu sendiri. Kristal mempunyai toleransi frekuensi 30ppm, yang sepatutnya cukup baik untuk kebanyakan aplikasi. Bersama-sama dengan toleransi kekerapan +/-30ppm, ia mempunyai ESR maksimum 50Ω, dan kapasitansi beban 10pF, yang kedua-duanya mempunyai kaitan dengan pilihan komponen yang disertakan.

- Untuk kristal berayun pada frekuensi yang diingini, pengilang menentukan kapasitansi beban yang diperlukan untuknya, dan dalam kes ini, ia adalah 10pF. Kapasiti beban ini dicapai dengan meletakkan dua kapasitor yang sama nilai, satu pada setiap sisi kristal ke tanah (C3 dan C4). Dari sudut kristal view, kapasitor ini disambung secara bersiri antara dua terminalnya. Teori litar asas memberitahu kita bahawa ia bergabung untuk memberikan kapasitansi (C3*C4)/(C3+C4), dan sebagai C3=C4, maka ia hanyalah C3/2. Dalam bekas iniampOleh itu, kami telah menggunakan kapasitor 15pF, jadi gabungan siri ialah 7.5pF. Sebagai tambahan kepada kapasitans beban yang disengajakan ini, kita juga mesti menambah nilai untuk kapasitans tambahan yang tidak disengajakan, atau kapasitans parasit, yang kita dapat daripada trek PCB dan pin XIN dan XOUT RP2350. Kami akan menganggap nilai 3pF untuk ini, dan kerana kapasitansi ini selari dengan C3 dan C4, kami hanya menambah ini untuk memberi kami jumlah kapasitans beban sebanyak 10.5pF, yang cukup hampir dengan sasaran 10pF. Seperti yang anda lihat, kapasitansi parasit bagi kesan PCB adalah faktor, dan oleh itu kita perlu memastikannya kecil supaya kita tidak mengganggu kristal dan menghentikannya berayun seperti yang dimaksudkan. Cuba dan pastikan reka letak sesingkat mungkin.

- Pertimbangan kedua ialah ESR maksimum (rintangan siri setara) kristal. Kami telah memilih peranti dengan maksimum 50Ω, kerana kami telah mendapati bahawa ini, bersama-sama dengan perintang siri 1kΩ (R2), adalah nilai yang baik untuk mengelakkan kristal didorong secara berlebihan dan rosak apabila menggunakan IOVDD tahap 3.3V. Walau bagaimanapun, jika IOVDD kurang daripada 3.3V, maka arus pemacu pin XIN/XOUT dikurangkan, dan anda akan mendapati bahawa amplitud kristal lebih rendah, atau mungkin tidak berayun sama sekali. Dalam kes ini, nilai perintang siri yang lebih kecil perlu digunakan. Sebarang sisihan daripada litar kristal yang ditunjukkan di sini, atau dengan tahap IOVDD selain daripada 3.3V, akan memerlukan ujian yang meluas untuk memastikan bahawa kristal berayun di bawah semua keadaan, dan dimulakan dengan cukup cepat supaya tidak menyebabkan masalah dengan aplikasi anda.

Kristal yang disyorkan

- Untuk reka bentuk asal menggunakan RP2350 kami mengesyorkan menggunakan Abracon ABM8-272-T3. Untuk example, sebagai tambahan kepada reka bentuk minimum exampKemudian, lihat skema papan Pico 2 dalam Lampiran B Lembaran Data Raspberry Pi Pico 2 dan reka bentuk Pico 2 files.

- Untuk prestasi dan kestabilan terbaik merentas julat suhu operasi biasa, gunakan Abracon ABM8-272-T3. Anda boleh mendapatkan sumber ABM8-272-T3 terus daripada Abracon atau daripada penjual semula yang dibenarkan. Pico 2 telah ditala secara khusus untuk ABM8-272-T3, yang mempunyai spesifikasi berikut:

- Walaupun anda menggunakan kristal dengan spesifikasi yang sama, anda perlu menguji litar pada julat suhu untuk memastikan kestabilan.

- Pengayun kristal dikuasakan daripada vol IOVDDtage. Akibatnya, kristal Abracon dan dampperintang ditala untuk operasi 3.3V. Jika anda menggunakan IO voltage, anda perlu menala semula.

- Sebarang perubahan pada parameter kristal berisiko ketidakstabilan merentas mana-mana komponen yang disambungkan ke litar kristal.

- Jika anda tidak boleh mendapatkan kristal yang disyorkan terus daripada Abracon atau penjual semula, hubungi applications@raspberrypi.com.

Bab 5. IOs

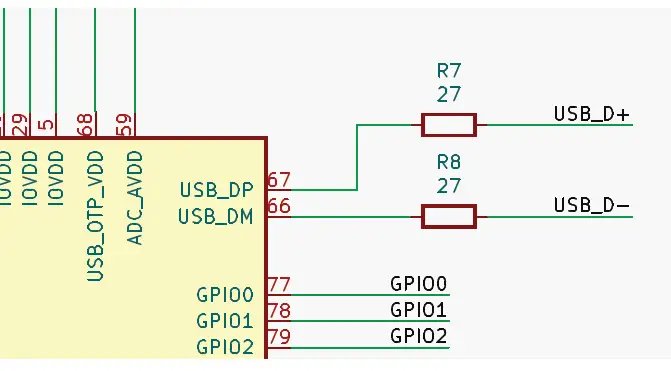

USB

Rajah 11. Bahagian skema yang menunjukkan pin USB RP2350 dan penamatan siri

- RP2350 menyediakan dua pin untuk digunakan untuk USB kelajuan penuh (FS) atau kelajuan rendah (LS), sama ada sebagai hos atau peranti, bergantung pada perisian yang digunakan. Seperti yang telah kita bincangkan, RP2350 juga boleh but sebagai peranti storan massa USB, jadi pendawaian pin ini ke penyambung USB (J1 dalam Rajah 5) masuk akal. Pin USB_DP dan USB_DM pada RP2350 tidak memerlukan sebarang tarik naik atau tarik turun tambahan (diperlukan untuk menunjukkan kelajuan, FS atau LS, atau sama ada ia adalah hos atau peranti), kerana ini terbina dalam I/O. Walau bagaimanapun, I/O ini memerlukan perintang penamatan siri 27Ω (R7 dan R8 dalam Rajah 11), diletakkan berdekatan dengan cip, untuk memenuhi spesifikasi impedans USB.

- Walaupun RP2350 dihadkan kepada kadar data berkelajuan penuh (12Mbps), kita harus mencuba dan memastikan bahawa galangan ciri talian penghantaran (trek tembaga yang menyambungkan cip ke penyambung) adalah hampir dengan

- Spesifikasi USB 90Ω (diukur secara berbeza). Pada papan setebal 1mm seperti ini, jika kita menggunakan trek lebar 0.8mm pada USB_DP dan USB_DM, dengan jurang 0.15mm di antara mereka, kita harus mendapat impedans ciri pembezaan sekitar 90Ω. Ini adalah untuk memastikan bahawa isyarat boleh bergerak sepanjang talian penghantaran ini sebersih mungkin, meminimumkan voltage pantulan yang boleh mengurangkan integriti isyarat. Untuk membolehkan talian penghantaran ini berfungsi dengan betul, kita perlu memastikan bahawa betul-betul di bawah talian ini adalah tanah. Kawasan pepejal kuprum tanah yang tidak terganggu, meregangkan keseluruhan panjang trek. Pada reka bentuk ini, hampir keseluruhan lapisan tembaga bawah ditumpukan kepada tanah, dan penjagaan khusus telah diambil untuk memastikan bahawa trek USB tidak melepasi apa-apa kecuali tanah. Jika PCB lebih tebal daripada 1mm dipilih untuk binaan anda, maka kami mempunyai dua pilihan. Kami boleh merekayasa semula talian penghantaran USB untuk mengimbangi jarak yang lebih jauh antara trek dan tanah di bawahnya (yang mungkin merupakan kemustahilan fizikal), atau kami boleh mengabaikannya, dan mengharapkan yang terbaik. USB FS boleh memaafkan, tetapi perbatuan anda mungkin berbeza-beza. Ia mungkin berfungsi dalam banyak aplikasi, tetapi ia mungkin tidak mematuhi standard USB.

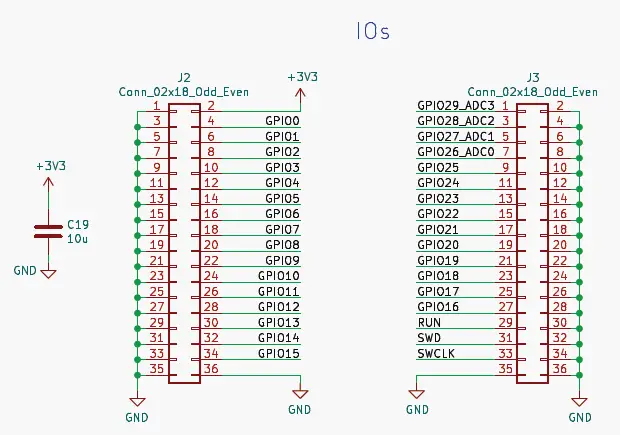

Pengepala I/O

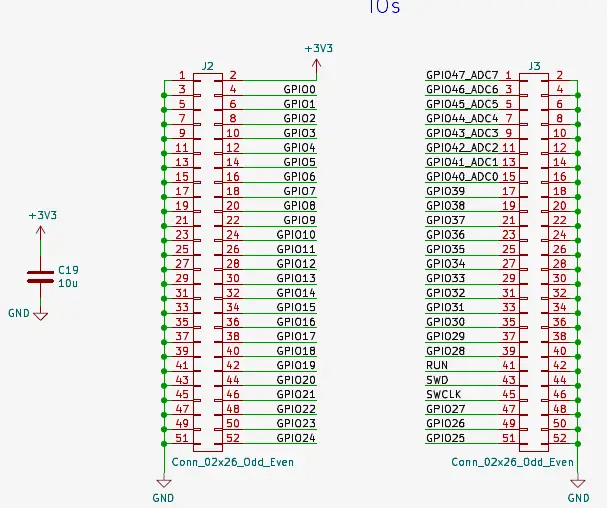

Rajah 12. Bahagian skematik menunjukkan pengepala I/O 2.54mm versi QFN60

- Sebagai tambahan kepada penyambung USB yang telah disebutkan, terdapat sepasang pengepala dwi baris 2.54mm (J2 dan J3 dalam Rajah 12), satu pada setiap sisi papan, yang mana seluruh I/O telah disambungkan. Terdapat 30 GPIO pada RP2350A, manakala terdapat 48 GPIO pada RP2350B, jadi pengepala pada versi papan Minimal ini lebih besar untuk membolehkan pin tambahan (lihat Rajah 13).

- Oleh kerana ini adalah reka bentuk tujuan umum, tanpa menggunakan aplikasi tertentu, I/O telah disediakan untuk disambungkan mengikut kehendak pengguna. Barisan dalam pin pada setiap pengepala ialah I/O, dan baris luar semuanya disambungkan ke tanah. Amalan yang baik untuk memasukkan banyak alasan pada penyambung I/O. Ini membantu mengekalkan tanah galangan yang rendah, dan juga untuk menyediakan banyak laluan pulangan yang berpotensi untuk arus yang bergerak ke dan dari

- Sambungan I/O. Ini penting untuk meminimumkan gangguan elektro-magnet yang boleh disebabkan oleh arus balik isyarat bertukar dengan cepat yang mengambil laluan gelung yang panjang untuk melengkapkan litar.

- Kedua-dua pengepala berada pada grid 2.54mm yang sama, yang menjadikan penyambungan papan ini kepada perkara lain, seperti papan roti, lebih mudah. Anda mungkin ingin mempertimbangkan untuk memasangkan hanya satu pengepala baris dan bukannya pengepala baris dua, mendispens dengan baris luar sambungan tanah, untuk menjadikannya lebih mudah untuk dimuatkan pada papan roti.

Rajah 13. Bahagian skematik menunjukkan pengepala I/O 2.54mm versi QFN80

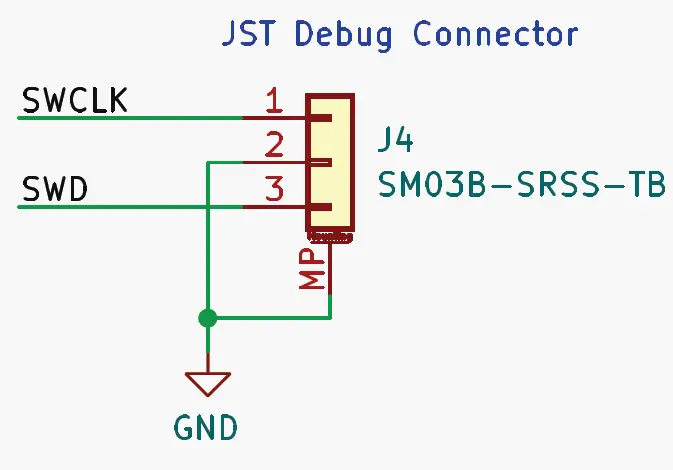

Penyambung nyahpepijat

Rajah 14. Bahagian skema yang menunjukkan penyambung JST pilihan untuk nyahpepijat SWD

Untuk penyahpepijatan pada cip, anda mungkin ingin menyambung ke antara muka SWD RP2350. Dua pin, SWD dan SWCLK, tersedia pada pengepala 2.54mm, J3, untuk membolehkan siasatan nyahpepijat pilihan anda disambungkan dengan mudah. Di samping itu, saya telah menyertakan pengepala JST pilihan, yang membolehkan sambungan mudah kepada Raspberry Pi Debug Probe. Anda tidak perlu menggunakan ini, pengepala 2.54mm sudah memadai jika anda berniat untuk menyahpepijat perisian, tetapi saya rasa lebih mudah untuk berbuat demikian. Saya telah memilih penyambung mendatar, kebanyakannya kerana saya suka rupanya, walaupun ia tidak berada di tepi papan, tetapi yang menegak tersedia, walaupun dengan jejak yang sedikit berbeza.

Butang

Reka bentuk Minimal kini tidak mengandungi satu, tetapi dua butang, di mana versi RP240 tiada. Satu adalah untuk pemilihan but USB seperti yang telah kita bincangkan sebelum ini, tetapi yang kedua ialah butang 'set semula', disambungkan ke pin RUN. Kedua-duanya tidak diperlukan (walaupun butang BOOTSEL perlu diganti dengan pengepala atau serupa jika mod but USB diperlukan), dan boleh dialih keluar jika ruang atau kos membimbangkan, tetapi mereka pasti menggunakan RP2350 jauh. pengalaman yang lebih menyenangkan.

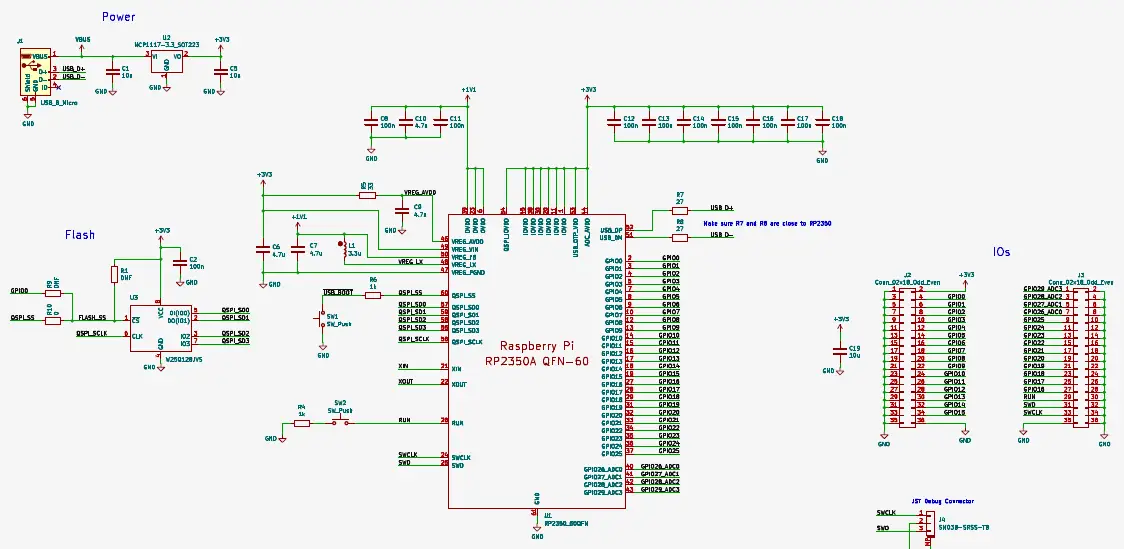

Lampiran A: Skema Lengkap -RP2350A versi

Rajah 15. Skema penuh Reka Bentuk Minimum untuk RP2350A

Lampiran B: Skema Lengkap -RP2350B versi

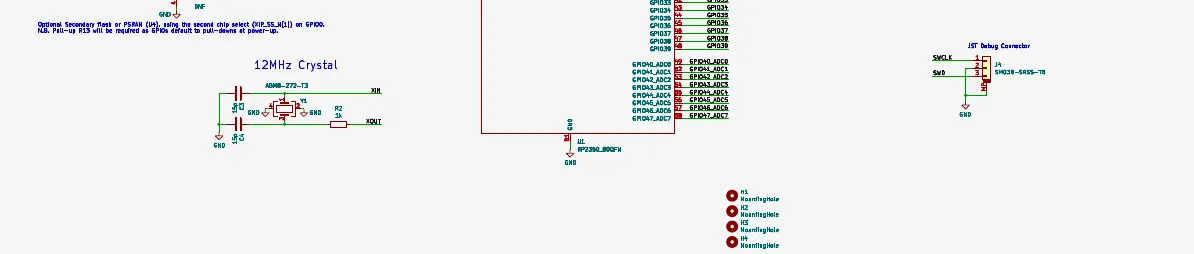

Rajah 16. Skema penuh Reka Bentuk Minimum untuk RP2350B

Lampiran H: Sejarah Keluaran Dokumentasi

8 Ogos 2024

Keluaran awal.

i Raspberry Pi

Raspberry Pi ialah tanda dagangan Raspberry Pi Ltd

Raspberry Pi Ltd

Dokumen / Sumber

|

Pengawal Mikro Raspberi Pi SC1631 [pdf] Manual Arahan SC1631 Pengawal Mikro Raspberi, SC1631, Pengawal Mikro Raspberi, Pengawal Mikro |