Raspberry Pi SC1631 Raspberry Microcontroller

ຂໍ້ມູນຈໍາເພາະຂອງຜະລິດຕະພັນ

- ຮຸ່ນ: RP2350

- ການຫຸ້ມຫໍ່: QFN-60

- ການເກັບຮັກສາ Flash ພາຍໃນ: ບໍ່

- ສະບັບtage Regulator: on-chip switching regulator

- Regulator Pins: 5 (3.3V input, 1.1V output, VREG_AVDD, VREG_LX, VREG_PGND)

ຄໍາແນະນໍາການນໍາໃຊ້ຜະລິດຕະພັນ

- ບົດທີ 1: ບົດແນະນຳ

- ຊຸດ RP2350 ສະເຫນີທາງເລືອກຊຸດທີ່ແຕກຕ່າງກັນເມື່ອທຽບກັບຊຸດ RP2040. RP2350A ແລະ RP2354A ມາຢູ່ໃນຊຸດ QFN-60 ໂດຍບໍ່ມີແລະບ່ອນເກັບຂໍ້ມູນພາຍໃນ flash ຕາມລໍາດັບ, ໃນຂະນະທີ່ RP2354B ແລະ RP2350B ມາໃນຊຸດ QFN-80 ທີ່ມີແລະບໍ່ມີ flash storage.

- ບົດທີ 2: ພະລັງງານ

ຊຸດ RP2350 ມີຄຸນສົມບັດການສະຫຼັບຊິບໃໝ່tage regulator ກັບຫ້າ pins. ເຄື່ອງຄວບຄຸມນີ້ຮຽກຮ້ອງໃຫ້ມີອົງປະກອບພາຍນອກສໍາລັບການປະຕິບັດງານແຕ່ສະຫນອງປະສິດທິພາບພະລັງງານທີ່ສູງຂຶ້ນໃນກະແສການໂຫຼດທີ່ສູງຂຶ້ນເມື່ອທຽບກັບເຄື່ອງຄວບຄຸມເສັ້ນຊື່ໃນຊຸດ RP2040. ເອົາໃຈໃສ່ກັບຄວາມອ່ອນໄຫວຂອງສິ່ງລົບກວນໃນ pin VREG_AVDD ທີ່ສະຫນອງວົງຈອນອະນາລັອກ.

ຄຳຖາມທີ່ຖາມເລື້ອຍໆ (FAQ)

- Q: ຄວາມແຕກຕ່າງຕົ້ນຕໍລະຫວ່າງ RP2350A ແລະ RP2350B ແມ່ນຫຍັງ?

A: ຄວາມແຕກຕ່າງຕົ້ນຕໍແມ່ນຢູ່ໃນການເກັບຮັກສາແຟດພາຍໃນ. RP2350A ບໍ່ມີບ່ອນເກັບຂໍ້ມູນພາຍໃນໃນຂະນະທີ່ RP2350B ເຮັດ. - ຖາມ: ຈໍານວນ pins ບໍ່ voltage regulator ໃນຊຸດ RP2350 ມີ?

A: ສະບັບເລກທີtage regulator ໃນຊຸດ RP2350 ມີຫ້າ pins.

ການອອກແບບຮາດແວດ້ວຍ RP2350 ການໃຊ້ microcontrollers RP2350 ເພື່ອສ້າງກະດານແລະຜະລິດຕະພັນ

ໂຄໂລໂຟນ

- © 2023-2024 Raspberry Pi Ltd

- ເອກະສານນີ້ແມ່ນໄດ້ຮັບອະນຸຍາດພາຍໃຕ້ Creative Commons Attribution-NoDerivatives 4.0 International (CC BY-ND). ວັນທີສ້າງ: 2024-08-08 ລຸ້ນສ້າງ: c0acc5b-clean

- ແຈ້ງການປະຕິເສດຄວາມຮັບຜິດຊອບທາງກົດໝາຍ

- ຂໍ້ມູນດ້ານວິຊາການແລະຄວາມຫນ້າເຊື່ອຖືສໍາລັບຜະລິດຕະພັນ RASPBERRY PI (ລວມທັງ DATASHEETS) ຕາມການດັດແກ້ຈາກເວລາເຖິງເວລາ ("ຊັບພະຍາກອນ") ແມ່ນສະຫນອງໃຫ້ໂດຍ RASPBERRY PI LTD ("RPL") "ບໍ່ເກີນ" ແລະຍັງບໍ່ມີ OT ຈຳກັດ ແທ້ຈິງແລ້ວ, ການຮັບປະກັນທາງດ້ານການຄ້າ ແລະ ຄວາມສອດຄ່ອງສໍາລັບຈຸດປະສົງສະເພາະແມ່ນຖືກປະຕິເສດ. ໃນຂອບເຂດສູງສຸດທີ່ກົດໝາຍສາມາດນຳໃຊ້ໄດ້ ໃນກໍລະນີທີ່ບໍ່ມີ RPL ຈະຕ້ອງຮັບຜິດຊອບຕໍ່ຄວາມເສຍຫາຍທາງກົງ, ທາງອ້ອມ, ໂດຍບັງເອີນ, ພິເສດ, ເປັນຕົວຢ່າງ, ຫຼືຄວາມເສຍຫາຍທີ່ເກີດຂຶ້ນ (ລວມທັງ, ບໍ່ວ່າຈະເປັນ, ເປັນຕົ້ນ ການບໍລິການ; , ຫຼືຜົນກໍາໄລ; ISED ຂອງຄວາມເປັນໄປໄດ້ ຂອງຄວາມເສຍຫາຍດັ່ງກ່າວ.

- RPL ສະຫງວນສິດທີ່ຈະປັບປຸງ, ປັບປຸງ, ແກ້ໄຂ ຫຼືການດັດແກ້ອື່ນໆຕໍ່ກັບຊັບພະຍາກອນ ຫຼືຜະລິດຕະພັນທີ່ອະທິບາຍໄວ້ໃນພວກມັນໄດ້ທຸກເວລາ ແລະໂດຍບໍ່ມີການແຈ້ງການເພີ່ມເຕີມ.

ແຫຼ່ງຂໍ້ມູນແມ່ນມີຈຸດປະສົງສໍາລັບຜູ້ໃຊ້ທີ່ມີຄວາມຊໍານິຊໍານານທີ່ມີລະດັບຄວາມຮູ້ດ້ານການອອກແບບທີ່ເຫມາະສົມ. ຜູ້ໃຊ້ມີຄວາມຮັບຜິດຊອບພຽງແຕ່ສໍາລັບການຄັດເລືອກແລະການນໍາໃຊ້ຂອງເຂົາເຈົ້າຂອງແຫຼ່ງຂໍ້ມູນແລະຄໍາຮ້ອງສະຫມັກຂອງຜະລິດຕະພັນທີ່ອະທິບາຍໃນພວກເຂົາ. ຜູ້ໃຊ້ຕົກລົງທີ່ຈະຊົດເຊີຍແລະຖື RPL ທີ່ບໍ່ເປັນອັນຕະລາຍຕໍ່ຄວາມຮັບຜິດຊອບ, ຄ່າໃຊ້ຈ່າຍ, ຄວາມເສຍຫາຍຫຼືການສູນເສຍອື່ນໆທີ່ເກີດຂື້ນຈາກການນໍາໃຊ້ຊັບພະຍາກອນຂອງພວກເຂົາ. - RPL ອະນຸຍາດໃຫ້ຜູ້ໃຊ້ໃຊ້ RESOURCES ໂດຍສົມທົບກັບຜະລິດຕະພັນ Raspberry Pi ເທົ່ານັ້ນ. ຫ້າມໃຊ້ຊັບພະຍາກອນອື່ນໆທັງໝົດ. ບໍ່ມີໃບອະນຸຍາດໃຫ້ RPL ຫຼືສິດທິຊັບສິນທາງປັນຍາພາກສ່ວນທີສາມອື່ນໆ.

- ກິດຈະກໍາທີ່ມີຄວາມສ່ຽງສູງ. ຜະລິດຕະພັນ Raspberry Pi ບໍ່ໄດ້ອອກແບບ, ຜະລິດ ຫຼື ມີຈຸດປະສົງເພື່ອໃຊ້ໃນສະພາບແວດລ້ອມທີ່ເປັນອັນຕະລາຍທີ່ຮຽກຮ້ອງໃຫ້ມີການປະຕິບັດທີ່ປອດໄພເຊັ່ນ: ໃນການດໍາເນີນງານຂອງສະຖານທີ່ນິວເຄລຍ, ລະບົບນໍາທາງຂອງເຮືອບິນຫຼືການສື່ສານ, ການຄວບຄຸມການຈະລາຈອນທາງອາກາດ, ລະບົບອາວຸດຫຼືຄໍາຮ້ອງສະຫມັກຄວາມປອດໄພ (ລວມທັງການຊ່ວຍເຫຼືອຊີວິດ. ລະບົບແລະອຸປະກອນທາງການແພດອື່ນໆ), ເຊິ່ງຄວາມລົ້ມເຫຼວຂອງຜະລິດຕະພັນສາມາດນໍາໄປສູ່ການເສຍຊີວິດໂດຍກົງ, ການບາດເຈັບສ່ວນບຸກຄົນຫຼືຄວາມເສຍຫາຍທາງດ້ານຮ່າງກາຍຫຼືສິ່ງແວດລ້ອມທີ່ຮ້າຍແຮງ ("ກິດຈະກໍາທີ່ມີຄວາມສ່ຽງສູງ"). RPL ໂດຍສະເພາະປະຕິເສດການຮັບປະກັນທີ່ສະແດງອອກຫຼືໂດຍຄວາມຫມາຍຂອງການສອດຄ່ອງສໍາລັບກິດຈະກໍາທີ່ມີຄວາມສ່ຽງສູງແລະຍອມຮັບບໍ່ມີຄວາມຮັບຜິດຊອບຕໍ່ການນໍາໃຊ້ຫຼືການລວມເອົາຜະລິດຕະພັນ Raspberry Pi ໃນກິດຈະກໍາທີ່ມີຄວາມສ່ຽງສູງ.

- ຜະລິດຕະພັນ Raspberry Pi ໄດ້ຖືກສະໜອງໃຫ້ພາຍໃຕ້ເງື່ອນໄຂມາດຕະຖານຂອງ RPL. ການສະໜອງຊັບພະຍາກອນຂອງ RPL ບໍ່ໄດ້ຂະຫຍາຍ ຫຼື ແກ້ໄຂເງື່ອນໄຂມາດຕະຖານຂອງ RPL ລວມທັງແຕ່ບໍ່ຈຳກັດການປະຕິເສດຄວາມຮັບຜິດຊອບ ແລະ ການຮັບປະກັນທີ່ສະແດງອອກໃນພວກມັນ.

ບົດທີ 1. ບົດແນະນຳ

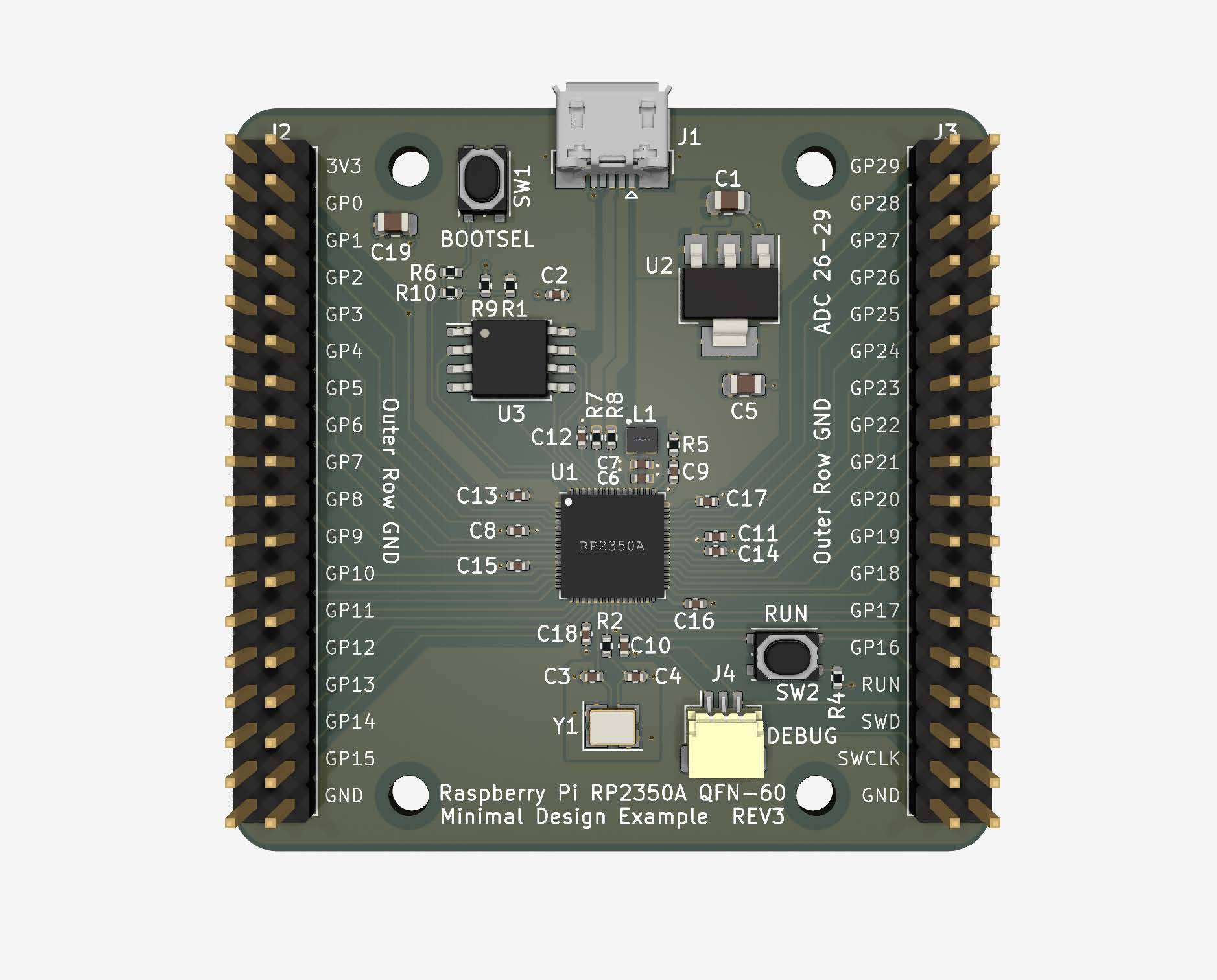

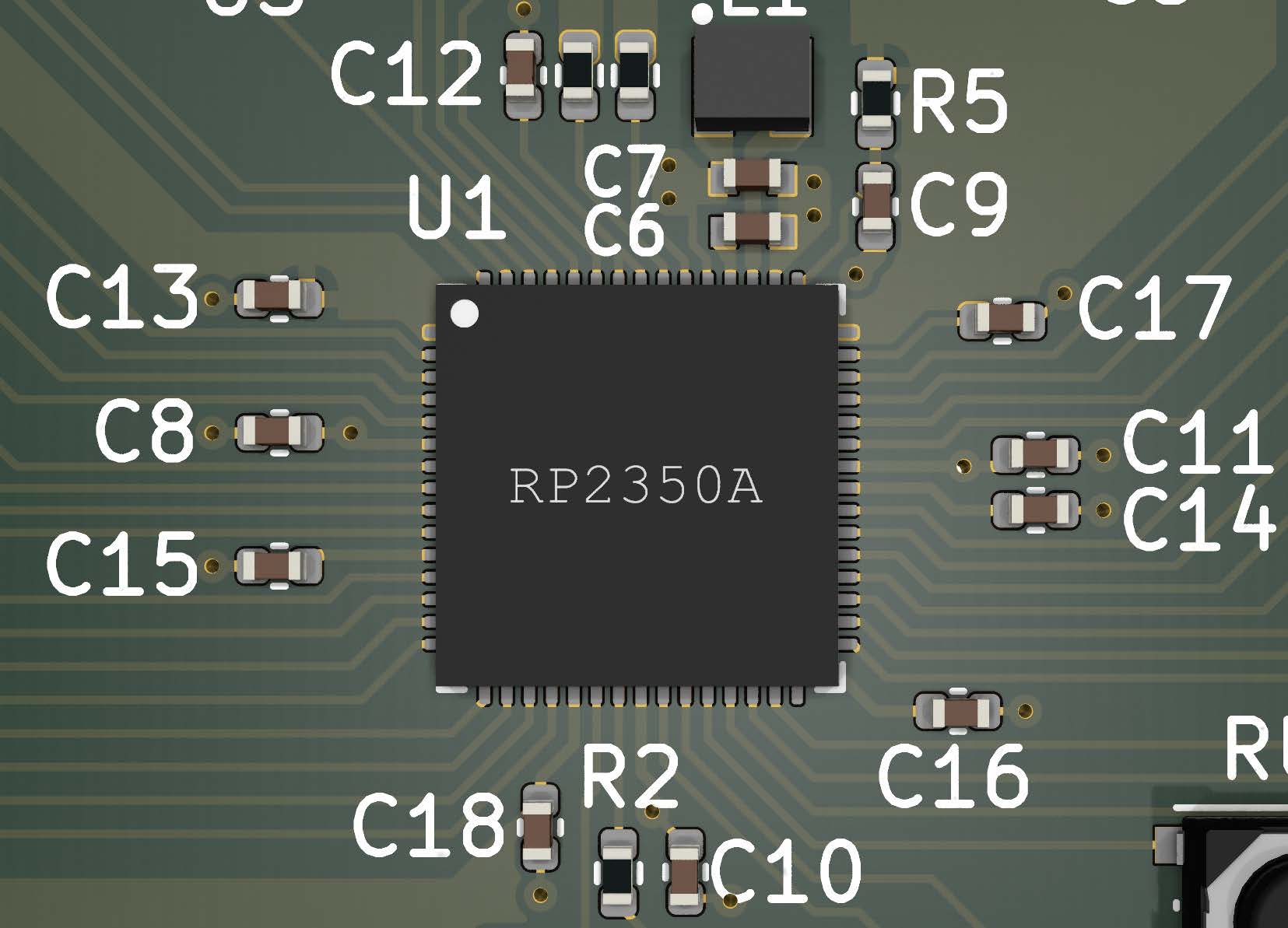

ຮູບ 1. KiCad 3D rendering ຂອງ RP2350A ການອອກແບບຫນ້ອຍ example

ເມື່ອພວກເຮົາແນະນໍາ Raspberry Pi RP2040 ຄັ້ງທໍາອິດ, ພວກເຮົາຍັງໄດ້ອອກການອອກແບບ 'Minimal' example ແລະຄູ່ມືທີ່ມາພ້ອມກັບການອອກແບບຮາດແວກັບ RP2040 ເຊິ່ງຫວັງວ່າຈະອະທິບາຍວິທີການ RP2040 ສາມາດນໍາໃຊ້ໃນກະດານວົງຈອນງ່າຍດາຍ, ແລະເປັນຫຍັງການເລືອກອົງປະກອບຕ່າງໆ. ດ້ວຍການມາເຖິງຂອງຊຸດ RP235x, ມັນແມ່ນເວລາທີ່ຈະທົບທວນຄືນ RP2040 ຕົ້ນສະບັບການອອກແບບຫນ້ອຍ, ແລະປັບປຸງມັນເພື່ອບັນຊີສໍາລັບລັກສະນະໃຫມ່, ແລະສໍາລັບແຕ່ລະ variants ຂອງຊຸດ; RP2350A ກັບຊຸດ QFN-60 ຂອງມັນ, ແລະ RP2350B ເຊິ່ງເປັນ QFN-80. ອີກເທື່ອ ໜຶ່ງ, ການອອກແບບເຫຼົ່ານີ້ແມ່ນຢູ່ໃນຮູບແບບ Kicad (7.0), ແລະມີໃຫ້ດາວໂຫລດ (https://datasheets.raspberrypi.com/rp2350/Minimal-KiCAD.zip).

ຄະນະກໍາມະການຫນ້ອຍ

ກະດານ Minimal ຕົ້ນສະບັບແມ່ນຄວາມພະຍາຍາມທີ່ຈະສະຫນອງການອອກແບບການອ້າງອິງທີ່ງ່າຍດາຍ, ໂດຍໃຊ້ອົງປະກອບພາຍນອກຕ່ໍາສຸດທີ່ຈໍາເປັນເພື່ອດໍາເນີນການ RP2040 ແລະຍັງມີ IO ທັງຫມົດທີ່ເປີດເຜີຍແລະສາມາດເຂົ້າເຖິງໄດ້. ອັນນີ້ແມ່ນປະກອບດ້ວຍແຫຼ່ງພະລັງງານ (5V ຫາ 3.3V linear regulator), crystal oscillator, flash memory, ແລະ IO connections (socket micro USB ແລະ headers GPIO). ຊຸດ RP235x ໃຫມ່ ກະດານ Minimal ສ່ວນໃຫຍ່ແມ່ນຄືກັນ, ແຕ່ມີການປ່ຽນແປງບາງຢ່າງທີ່ມີຄວາມຈໍາເປັນເນື່ອງຈາກຮາດແວໃຫມ່. ນອກເຫນືອໄປຈາກນີ້, ແລະເຖິງແມ່ນວ່າຈະກົງກັນຂ້າມກັບລັກສະນະຫນ້ອຍຂອງການອອກແບບ, ຂ້າພະເຈົ້າໄດ້ເພີ່ມສອງສາມປຸ່ມສໍາລັບ bootsel ແລະແລ່ນ, ພ້ອມກັບ header SWD ແຍກຕ່າງຫາກ, ເຊິ່ງຄວນຈະຫມາຍຄວາມວ່າປະສົບການ debug ທີ່ຫນ້າເສົ້າໃຈຫນ້ອຍທີ່ສຸດໃນເວລານີ້. ການອອກແບບບໍ່ໄດ້ເວົ້າຢ່າງເຂັ້ມງວດວ່າຕ້ອງການປຸ່ມເຫຼົ່ານີ້, ສັນຍານຍັງມີຢູ່ໃນສ່ວນຫົວ, ແລະພວກມັນສາມາດຖືກຍົກເລີກໄດ້ຖ້າທ່ານມີຄ່າໃຊ້ຈ່າຍໂດຍສະເພາະຫຼືສະຕິໃນພື້ນທີ່, ຫຼືມີແນວໂນ້ມ masochistic.

ຊຸດ RP2040 ທຽບກັບ RP235x

ການປ່ຽນແປງທີ່ຊັດເຈນທີ່ສຸດແມ່ນຢູ່ໃນຊຸດ. ໃນຂະນະທີ່ RP2040 ເປັນ 7x7mm QFN-56, ຊຸດ RP235x ໃນປັດຈຸບັນມີສີ່ສະມາຊິກທີ່ແຕກຕ່າງກັນ. ມີສອງອຸປະກອນທີ່ແບ່ງປັນຊຸດ QFN-60 ດຽວກັນ; RP2350A ທີ່ບໍ່ມີບ່ອນເກັບຂໍ້ມູນພາຍໃນ, ແລະ RP2354A ທີ່ເຮັດ. ເຊັ່ນດຽວກັນ, QFN-80 ຍັງມາໃນສອງລົດຊາດ; RP2354B ທີ່ມີແຟດ, ແລະ RP2350B ໂດຍບໍ່ມີ. ອຸປະກອນ QFN-60 ແລະ RP2040 ຕົ້ນສະບັບມີສ່ວນແບ່ງທົ່ວໄປtage.

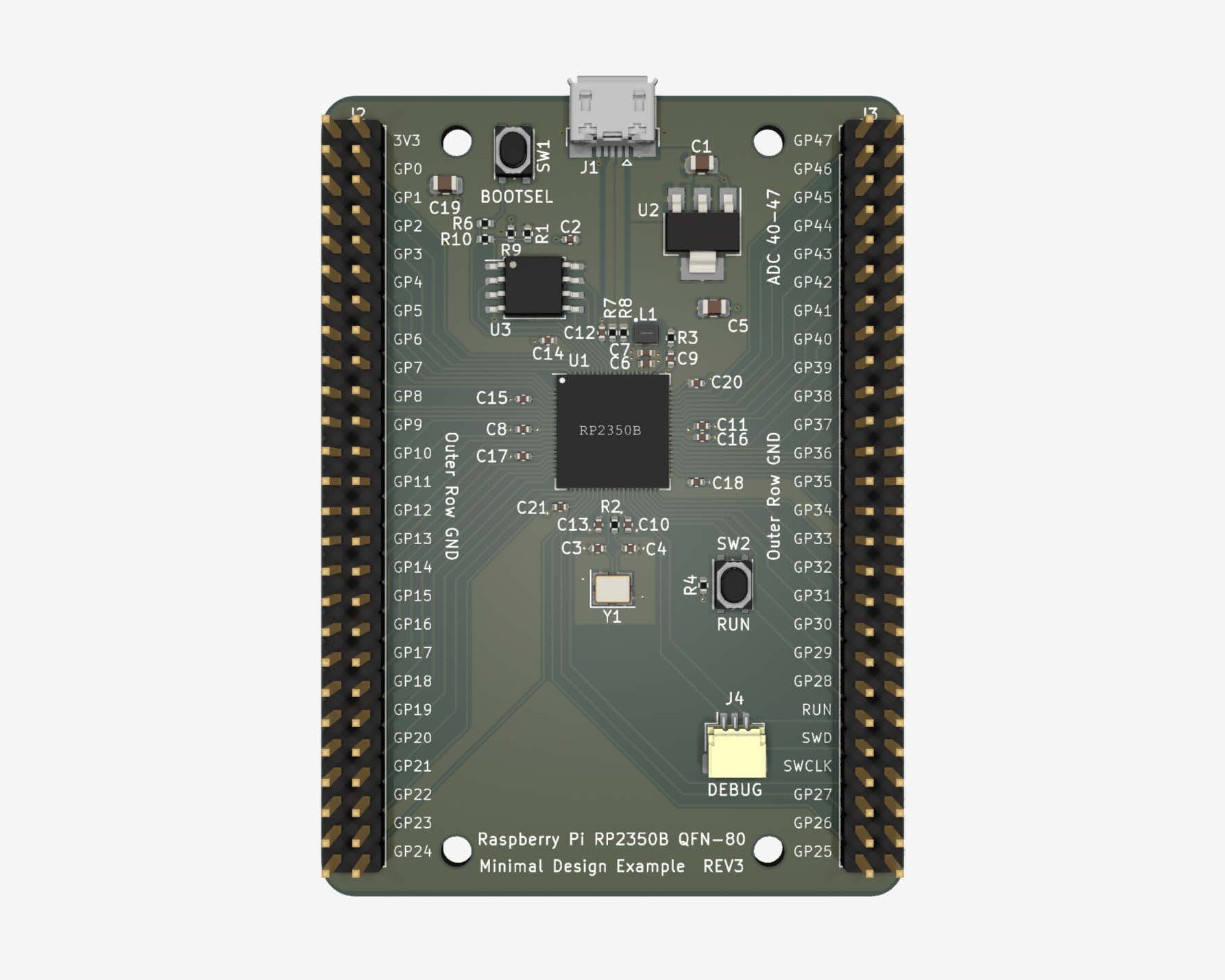

ພວກເຂົາແຕ່ລະມີ 30 GPIO, ສີ່ອັນທີ່ເຊື່ອມຕໍ່ກັບ ADC, ແລະມີຂະຫນາດ 7x7 ມມ. ເຖິງວ່າຈະມີນີ້, RP2350A ບໍ່ແມ່ນການຫຼຸດລົງໃນການທົດແທນ RP2040, ເນື່ອງຈາກວ່າຈໍານວນຂອງ pins ໃນແຕ່ລະແມ່ນແຕກຕ່າງກັນ. ໃນທາງກົງກັນຂ້າມ, ຊິບ QFN-80 ປະຈຸບັນມີ 48 GPIOs, ແລະແປດຂອງເຫຼົ່ານີ້ໃນປັດຈຸບັນມີຄວາມສາມາດ ADC. ເນື່ອງຈາກວ່ານີ້, ໃນປັດຈຸບັນພວກເຮົາມີສອງກະດານ Minimal; ຫນຶ່ງສໍາລັບອຸປະກອນ 60 pin, ແລະຫນຶ່ງສໍາລັບ 80. ກະດານ Minimal ເຫຼົ່ານີ້ແມ່ນອອກແບບຕົ້ນຕໍສໍາລັບພາກສ່ວນທີ່ບໍ່ມີ flash ພາຍໃນ (RP2350), ແນວໃດກໍ່ຕາມການອອກແບບສາມາດຖືກນໍາໃຊ້ໄດ້ຢ່າງງ່າຍດາຍກັບອຸປະກອນ flash ພາຍໃນ (RP2354) ໂດຍພຽງແຕ່ຍົກເລີກ flash onboard. ຫນ່ວຍຄວາມຈໍາ, ຫຼືແມ້ກະທັ້ງການນໍາໃຊ້ມັນເປັນອຸປະກອນ flash ທີສອງ (ເພີ່ມເຕີມໃນນີ້ຕໍ່ມາ). ມີຄວາມແຕກຕ່າງກັນຫນ້ອຍຫນຶ່ງລະຫວ່າງສອງກະດານ, ນອກເຫນືອຈາກຄວາມຈິງທີ່ວ່າຮຸ່ນ QFN-80 ມີຫົວແຖວຍາວກວ່າເພື່ອຮອງຮັບ GPIO ພິເສດ, ແລະກະດານຈຶ່ງໃຫຍ່ກວ່າ.

ນອກເຫນືອຈາກຊຸດ, ຄວາມແຕກຕ່າງລະດັບກະດານທີ່ໃຫຍ່ທີ່ສຸດລະຫວ່າງຊຸດ RP235x ແລະ RP2040 ແມ່ນການສະຫນອງພະລັງງານ. ຊຸດ RP235x ມີ pins ພະລັງງານໃຫມ່, ແລະເຄື່ອງຄວບຄຸມພາຍໃນທີ່ແຕກຕ່າງກັນ. ເຄື່ອງຄວບຄຸມເສັ້ນ 100mA ຂອງ RP2040 ໄດ້ຖືກປ່ຽນແທນດ້ວຍຕົວຄວບຄຸມການປ່ຽນ 200mA, ແລະດັ່ງນັ້ນ, ມັນຮຽກຮ້ອງໃຫ້ມີວົງຈອນສະເພາະບາງອັນ, ແລະບໍ່ມີການເບິ່ງແຍງເລັກນ້ອຍກັບຮູບແບບ. ມັນແນະນໍາໃຫ້ທ່ານຕິດຕາມຮູບແບບຂອງພວກເຮົາຢ່າງໃກ້ຊິດແລະການຄັດເລືອກອົງປະກອບ; ພວກເຮົາໄດ້ຜ່ານຄວາມເຈັບປວດຂອງການທີ່ຈະເຮັດໃຫ້ການເຮັດໃຫ້ການອອກແບບຄືນໃຫມ່ຈໍານວນຫນຶ່ງ, ສະນັ້ນຫວັງເປັນຢ່າງຍິ່ງວ່າທ່ານບໍ່ຈໍາເປັນຕ້ອງ.

ຮູບທີ 2. ການສະແດງພາບ KiCad 3D ຂອງ RP2350B ການອອກແບບໜ້ອຍສຸດ example

ການອອກແບບ

ຄວາມຕັ້ງໃຈຂອງການອອກແບບ Minimal examples ແມ່ນການສ້າງຄູ່ຂອງກະດານງ່າຍດາຍໂດຍໃຊ້ຊຸດ RP235x, ເຊິ່ງຄວນຈະມີລາຄາຖືກແລະສາມາດຜະລິດໄດ້ງ່າຍ, ໂດຍບໍ່ຕ້ອງໃຊ້ເຕັກໂນໂລຢີ PCB ທີ່ບໍ່ຈໍາເປັນ. ກະດານນ້ອຍທີ່ສຸດແມ່ນການອອກແບບ 2 ຊັ້ນ, ໂດຍນໍາໃຊ້ອົງປະກອບທີ່ຄວນຈະມີຢູ່ທົ່ວໄປ, ແລະທັງຫມົດຕິດຕັ້ງຢູ່ດ້ານເທິງຂອງກະດານ. ໃນຂະນະທີ່ມັນເປັນສິ່ງທີ່ດີທີ່ຈະໃຊ້ອົງປະກອບທີ່ສາມາດເຮັດດ້ວຍມືທີ່ໃຫຍ່, ງ່າຍດາຍ, ຂະຫນາດນ້ອຍຂອງຊິບ QFN (0.4 ມມ) ຫມາຍຄວາມວ່າການໃຊ້ອົງປະກອບຕົວຕັ້ງຕົວຕີ 0402 (1005 metric) ແມ່ນຫຼີກລ້ຽງບໍ່ໄດ້ຖ້າ GPIOs ທັງຫມົດຈະຖືກນໍາໃຊ້. ໃນຂະນະທີ່ອົງປະກອບ 0402 soldering ດ້ວຍມືບໍ່ທ້າທາຍເກີນໄປກັບທາດເຫຼັກ soldering ທີ່ເຫມາະສົມ, ມັນເກືອບເປັນໄປບໍ່ໄດ້ທີ່ຈະ solder QFNs ໂດຍບໍ່ມີອຸປະກອນພິເສດ.

ໃນສອງສາມພາກຕໍ່ໄປ, ຂ້າພະເຈົ້າຈະພະຍາຍາມອະທິບາຍສິ່ງທີ່ວົງຈອນເພີ່ມເຕີມແມ່ນສໍາລັບ, ແລະຫວັງວ່າພວກເຮົາມາເພື່ອເຮັດໃຫ້ທາງເລືອກທີ່ພວກເຮົາໄດ້ເຮັດ. ແທ້ຈິງແລ້ວ, ຂ້ອຍ ກຳ ລັງຈະເວົ້າກ່ຽວກັບການອອກແບບສອງຢ່າງແຍກຕ່າງຫາກ, ໜຶ່ງ ສຳ ລັບແຕ່ລະຂະ ໜາດ ຂອງຊຸດ, ຂ້ອຍໄດ້ພະຍາຍາມຮັກສາສິ່ງທີ່ງ່າຍດາຍເທົ່າທີ່ຂ້ອຍສາມາດເຮັດໄດ້. ເທົ່າທີ່ເປັນໄປໄດ້, ການອ້າງອິງອົງປະກອບທັງຫມົດຂອງສອງກະດານແມ່ນຄືກັນ, ດັ່ງນັ້ນຖ້າຂ້ອຍອ້າງເຖິງ U1, R1, ແລະອື່ນໆ, ມັນມີຄວາມກ່ຽວຂ້ອງເທົ່າທຽມກັນກັບທັງສອງກະດານ. ຂໍ້ຍົກເວັ້ນທີ່ຊັດເຈນແມ່ນໃນເວລາທີ່ອົງປະກອບພຽງແຕ່ຢູ່ໃນຫນຶ່ງຂອງກະດານ (ໃນທຸກກໍລະນີ, ນີ້ຈະຢູ່ໃນຕົວແປ 80 pin ຂະຫນາດໃຫຍ່), ຫຼັງຈາກນັ້ນອົງປະກອບໃນຄໍາຖາມຈະມີພຽງແຕ່ກ່ຽວກັບການອອກແບບ QFN-80; ສໍາລັບ example, R13 ພຽງແຕ່ປາກົດຢູ່ໃນກະດານນີ້.

ບົດທີ 2. ພະລັງງານ

ການສະຫນອງພະລັງງານຂອງຊຸດ RP235x ແລະ RP2040 ແຕກຕ່າງກັນປະມານນີ້, ເຖິງແມ່ນວ່າໃນການຕັ້ງຄ່າທີ່ງ່າຍດາຍທີ່ສຸດ, ມັນຍັງຕ້ອງການສອງອຸປະກອນ, 3.3V ແລະ 1.1V. ຊຸດ RP235x ໃນເວລາດຽວກັນມີຄວາມອຶດຢາກຫຼາຍ, ຍ້ອນວ່າມັນມີປະສິດທິພາບທີ່ສູງກວ່າ, ແລະຍັງປະຫຍັດຫຼາຍກວ່າ (ເມື່ອຢູ່ໃນສະພາບພະລັງງານຕ່ໍາ) ກ່ວາລຸ້ນກ່ອນ, ແລະດັ່ງນັ້ນເຄື່ອງຄວບຄຸມເສັ້ນຊື່ໃນ RP2040 ໄດ້ຖືກປັບປຸງດ້ວຍເຄື່ອງຄວບຄຸມການສະຫຼັບ. ນີ້ຊ່ວຍໃຫ້ພວກເຮົາມີປະສິດທິພາບພະລັງງານຫຼາຍກວ່າເກົ່າໃນກະແສໄຟຟ້າທີ່ສູງຂຶ້ນ (ເຖິງ 200mA ເມື່ອທຽບກັບ 100mA ກ່ອນຫນ້ານີ້).

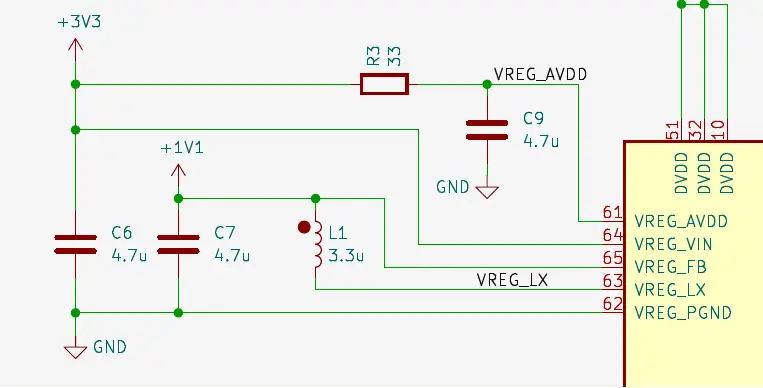

ສະບັບໃໝ່ໃນຊິບtage ລະບຽບການ

ຮູບທີ 3. ພາກສ່ວນ Schematic ສະແດງວົງຈອນຄວບຄຸມພາຍໃນ

ເຄື່ອງຄວບຄຸມເສັ້ນຊື່ຂອງ RP2040 ມີສອງ pins, ວັດສະດຸປ້ອນ 3.3V, ແລະຜົນຜະລິດ 1.1V ເພື່ອສະຫນອງ DVDD ໃນຊິບ. ເວລານີ້, ຜູ້ຄວບຄຸມຂອງຊຸດ RP235x ມີຫ້າ pins, ແລະຕ້ອງການອົງປະກອບພາຍນອກບາງຢ່າງເພື່ອເຮັດໃຫ້ມັນເຮັດວຽກ. ໃນຂະນະທີ່ນີ້ເບິ່ງຄືວ່າເປັນບາດກ້າວຂ້າງຫຼັງເລັກນ້ອຍໃນແງ່ຂອງການນໍາໃຊ້ໄດ້, ການຄວບຄຸມການສະຫຼັບມີ advan ໄດ້tage ຂອງການເປັນພະລັງງານປະສິດທິພາບຫຼາຍໃນກະແສການໂຫຼດທີ່ສູງຂຶ້ນ.

ດັ່ງທີ່ຊື່ແນະນໍາ, regulator ເປີດແລະປິດຢ່າງໄວວາ transistor ພາຍໃນທີ່ເຊື່ອມຕໍ່ input vol 3.3V.tage (VREG_VIN) ໄປຫາ pin VREG_LX, ແລະດ້ວຍການຊ່ວຍເຫຼືອຂອງ inductor (L1) ແລະ capacitor ຂາອອກ (C7), ມັນສາມາດຜະລິດເປັນ DC output voltage ທີ່ໄດ້ຖືກເລື່ອນລົງຈາກວັດສະດຸປ້ອນ. ເຂັມ VREG_FB ຕິດຕາມກວດກາຜົນຜະລິດ voltage, ແລະປັບອັດຕາສ່ວນການເປີດ / ປິດຂອງວົງຈອນການສະຫຼັບ, ເພື່ອໃຫ້ແນ່ໃຈວ່າ vol ໄດ້tage ຖືກຮັກສາໄວ້. ເນື່ອງຈາກກະແສໄຟຟ້າຂະຫນາດໃຫຍ່ຖືກປ່ຽນຈາກ VREG_VIN ເປັນ VREG_LX, ຕົວເກັບປະຈຸຂະຫນາດໃຫຍ່ (C6) ຢູ່ໃກ້ກັບວັດສະດຸປ້ອນ, ດັ່ງນັ້ນພວກເຮົາບໍ່ເຮັດໃຫ້ການສະຫນອງ 3.3V ຫຼາຍເກີນໄປ. ເວົ້າກ່ຽວກັບກະແສໄຟຟ້າສະຫຼັບຂະຫນາດໃຫຍ່ເຫຼົ່ານີ້, ຜູ້ຄວບຄຸມຍັງມາພ້ອມກັບການເຊື່ອມຕໍ່ກັບຄືນຫນ້າດິນຂອງຕົນເອງ, VREG_PGND. ເຊັ່ນດຽວກັນກັບ VREG_VIN ແລະ VREG_LX, ຮູບແບບຂອງການເຊື່ອມຕໍ່ນີ້ແມ່ນສໍາຄັນ, ແລະໃນຂະນະທີ່ VREG_PGND ຕ້ອງເຊື່ອມຕໍ່ກັບ GND ຕົ້ນຕໍ, ມັນຕ້ອງເຮັດໃນລັກສະນະທີ່ທຸກກະແສສະຫຼັບຂະຫນາດໃຫຍ່ກັບຄືນໂດຍກົງກັບ pin PGND, ໂດຍບໍ່ມີການລົບກວນສ່ວນທີ່ເຫຼືອຂອງ. GND ຫຼາຍເກີນໄປ.

pin ສຸດທ້າຍແມ່ນ VREG_AVDD, ເຊິ່ງສະຫນອງວົງຈອນອະນາລັອກພາຍໃນເຄື່ອງຄວບຄຸມ, ແລະນີ້ແມ່ນມີຄວາມອ່ອນໄຫວຫຼາຍຕໍ່ສິ່ງລົບກວນ.

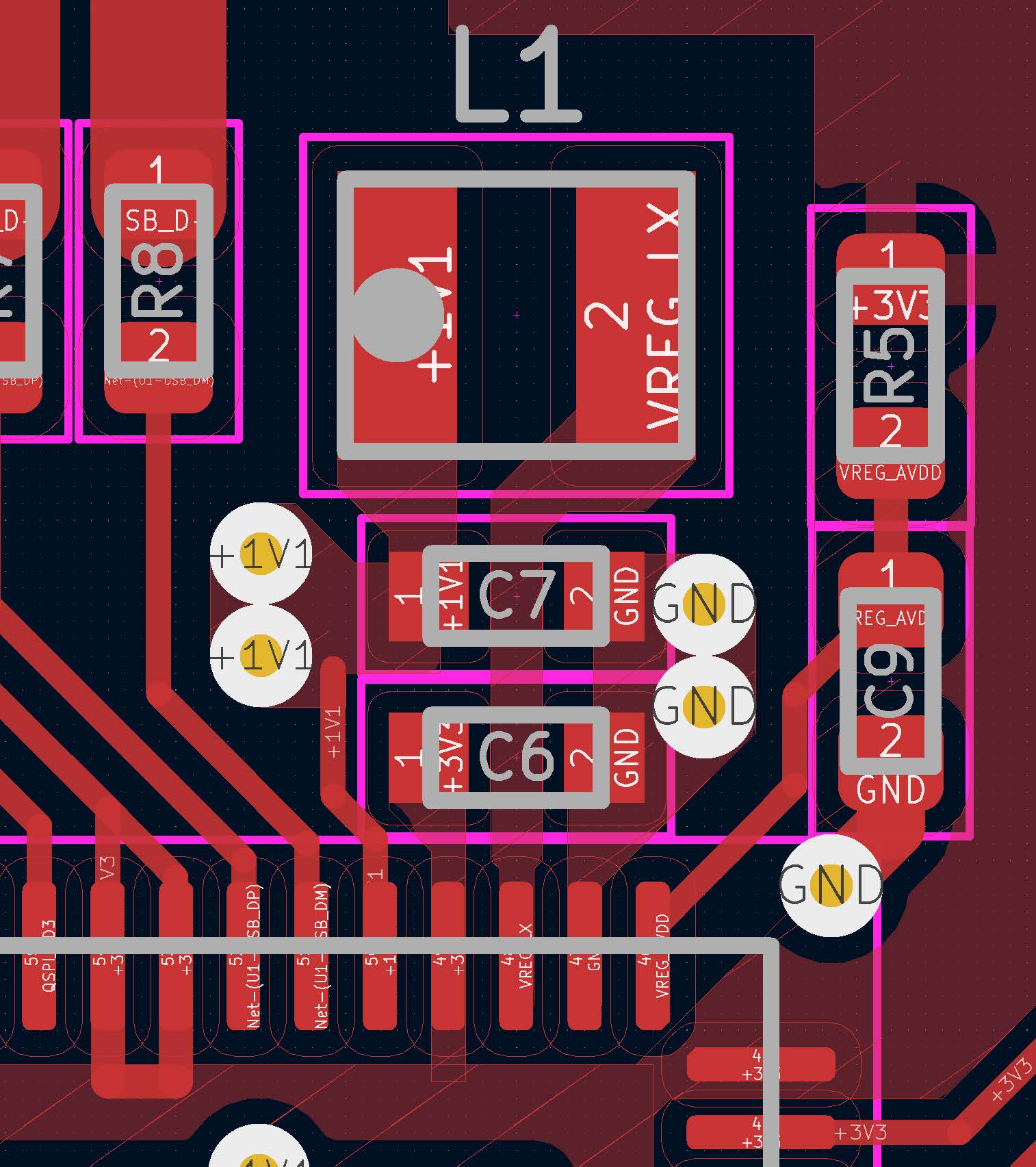

ຮູບທີ 4. ພາກສ່ວນແຜນຜັງສະແດງຮູບແບບ PCB ຂອງເຄື່ອງຄວບຄຸມ

- ການຈັດວາງຂອງເຄື່ອງຄວບຄຸມຢູ່ໃນກະດານນ້ອຍທີ່ສຸດສະທ້ອນເຖິງ Raspberry Pi Pico 2 ຢ່າງໃກ້ຊິດ. ການເຮັດວຽກຢ່າງຫຼວງຫຼາຍໄດ້ເຂົ້າໄປໃນການອອກແບບຂອງວົງຈອນນີ້, ໂດຍມີ PCB ຫຼາຍໆຄັ້ງທີ່ຕ້ອງການເພື່ອເຮັດໃຫ້ມັນດີເທົ່າທີ່ພວກເຮົາເປັນໄປໄດ້. ສາມາດ. ໃນຂະນະທີ່ທ່ານສາມາດຈັດວາງອົງປະກອບເຫຼົ່ານີ້ໃນຫຼາຍວິທີທີ່ແຕກຕ່າງກັນແລະຍັງໄດ້ຮັບການຄວບຄຸມເພື່ອ 'ເຮັດວຽກ' (ie, ຜະລິດຜົນຜະລິດ vol.tage ໃນລະດັບທີ່ເຫມາະສົມ, ດີພໍທີ່ຈະໄດ້ຮັບການແລ່ນລະຫັດ), ພວກເຮົາໄດ້ພົບເຫັນວ່າຜູ້ຄວບຄຸມຂອງພວກເຮົາຕ້ອງໄດ້ຮັບການປະຕິບັດຢ່າງແນ່ນອນເພື່ອໃຫ້ມັນມີຄວາມສຸກ, ແລະມີຄວາມສຸກ, ຂ້າພະເຈົ້າຫມາຍຄວາມວ່າການຜະລິດຜົນຜະລິດທີ່ຖືກຕ້ອງ.tage ພາຍໃຕ້ຂອບເຂດຂອງເງື່ອນໄຂການໂຫຼດໃນປະຈຸບັນ.

- ໃນຂະນະທີ່ປະຕິບັດການທົດລອງຂອງພວກເຮົາກ່ຽວກັບເລື່ອງນີ້, ພວກເຮົາມີຄວາມຜິດຫວັງບາງຢ່າງທີ່ຈະໄດ້ຮັບການເຕືອນວ່າໂລກທີ່ບໍ່ສະດວກຂອງຟີຊິກບໍ່ສາມາດຖືກລະເລີຍສະ ເໝີ ໄປ. ພວກເຮົາ, ໃນຖານະເປັນວິສະວະກອນ, ສ່ວນໃຫຍ່ພະຍາຍາມແລະເຮັດແນວນີ້ແທ້ໆ; ເຮັດໃຫ້ອົງປະກອບທີ່ງ່າຍດາຍ, ບໍ່ສົນໃຈ (ເລື້ອຍໆ) ຄຸນສົມບັດທາງກາຍະພາບທີ່ບໍ່ສໍາຄັນ, ແລະແທນທີ່ຈະສຸມໃສ່ຊັບສິນທີ່ພວກເຮົາສົນໃຈ.ample, ຕົວຕ້ານທານແບບງ່າຍໆບໍ່ພຽງແຕ່ມີຄວາມຕ້ານທານ, ແຕ່ຍັງມີ inductance, ແລະອື່ນໆ. ໃນກໍລະນີຂອງພວກເຮົາ, ພວກເຮົາຄົ້ນພົບວ່າ inductors ມີສະຫນາມແມ່ເຫຼັກທີ່ກ່ຽວຂ້ອງກັບພວກມັນ, ແລະສໍາຄັນ, radiates ໃນທິດທາງຂຶ້ນກັບວິທີການ coil. ແມ່ນບາດແຜ, ແລະທິດທາງຂອງການໄຫຼຂອງປະຈຸບັນ. ພວກເຮົາຍັງໄດ້ຮັບການເຕືອນວ່າ inductor ປ້ອງກັນ 'ຢ່າງເຕັມສ່ວນ' ບໍ່ໄດ້ຫມາຍຄວາມວ່າສິ່ງທີ່ທ່ານຄິດວ່າມັນອາດຈະ. ສະຫນາມແມ່ເຫຼັກໄດ້ຖືກຫຼຸດລົງເປັນຂອບເຂດຂະຫນາດໃຫຍ່, ແຕ່ບາງຄົນຍັງຫລົບຫນີ. ພວກເຮົາພົບວ່າປະສິດທິພາບຂອງເຄື່ອງຄວບຄຸມສາມາດໄດ້ຮັບການປັບປຸງຢ່າງຫຼວງຫຼາຍຖ້າຫາກວ່າ inductor ແມ່ນ 'ວິທີການທີ່ຖືກຕ້ອງຕະຫຼອດ'.

- ມັນ turns ໃຫ້ເຫັນວ່າສະຫນາມແມ່ເຫຼັກປ່ອຍອອກຈາກ inductor 'ທາງຜິດຮອບ' interferes ກັບຕົວເກັບຮັກສາການຜະລິດ (C7), ຊຶ່ງເຮັດໃຫ້ການ upsets ວົງຈອນການຄວບຄຸມພາຍໃນ RP2350. ດ້ວຍ inductor ໃນທິດທາງທີ່ເຫມາະສົມ, ແລະຮູບແບບທີ່ຊັດເຈນແລະການຄັດເລືອກອົງປະກອບທີ່ໃຊ້ຢູ່ທີ່ນີ້, ຫຼັງຈາກນັ້ນບັນຫານີ້ຈະຫມົດໄປ. ແນ່ນອນວ່າມັນຈະມີການຈັດວາງ, ອົງປະກອບອື່ນໆ, ແລະອື່ນໆ, ເຊິ່ງສາມາດເຮັດວຽກກັບ inductor ໃນທິດທາງໃດກໍ່ຕາມ, ແຕ່ພວກເຂົາມັກຈະໃຊ້ພື້ນທີ່ PCB ຫຼາຍເພື່ອເຮັດແນວນັ້ນ. ພວກເຮົາໄດ້ຈັດວາງໂຄງຮ່າງທີ່ແນະນຳນີ້ໄວ້ເພື່ອຊ່ວຍປະຢັດຄົນໃນຫຼາຍຊົ່ວໂມງທາງວິສະວະກຳທີ່ພວກເຮົາໄດ້ໃຊ້ເວລາໃນການພັດທະນາ ແລະປັບປຸງການແກ້ໄຂທີ່ກະທັດຮັດ ແລະມີຄວາມປະພຶດດີນີ້.

- ເພີ່ມເຕີມຕໍ່ກັບຈຸດ, ພວກເຮົາກໍາລັງໄປເຖິງຕອນນັ້ນວ່າຖ້າຫາກວ່າທ່ານເລືອກທີ່ຈະບໍ່ໃຊ້ ex ຂອງພວກເຮົາample, ຫຼັງຈາກນັ້ນທ່ານເຮັດແນວນັ້ນຢູ່ໃນຄວາມສ່ຽງຂອງທ່ານເອງ. ຄືກັນກັບພວກເຮົາໄດ້ເຮັດແລ້ວກັບ RP2040 ແລະວົງຈອນໄປເຊຍກັນ, ບ່ອນທີ່ພວກເຮົາຮຽກຮ້ອງໃຫ້ (ດີ, ແນະນໍາຢ່າງແຂງແຮງ) ທ່ານໃຊ້ສ່ວນຫນຶ່ງໂດຍສະເພາະ (ພວກເຮົາຈະເຮັດແນວນັ້ນອີກເທື່ອຫນຶ່ງໃນພາກໄປເຊຍກັນຂອງເອກະສານນີ້).

- ທິດທາງຂອງ inductors ຂະຫນາດນ້ອຍເຫຼົ່ານີ້ແມ່ນຂ້ອນຂ້າງບໍ່ສົນໃຈທົ່ວໄປ, ມີການກໍານົດທິດທາງຂອງ coil winding ບໍ່ສາມາດ deduce, ແລະຍັງແຈກຢາຍແບບສຸ່ມຕາມ reel ຂອງອົງປະກອບ. ຂະຫນາດຂອງກໍລະນີ inductor ທີ່ໃຫຍ່ກວ່າສາມາດພົບເຫັນວ່າມີເຄື່ອງຫມາຍຂົ້ວຢູ່ໃນພວກມັນ, ແນວໃດກໍ່ຕາມ, ພວກເຮົາບໍ່ສາມາດຊອກຫາອັນໃດທີ່ເຫມາະສົມໃນຂະຫນາດກໍລະນີ 0806 (2016 metric) ທີ່ພວກເຮົາເລືອກ. ເພື່ອເຮັດສິ່ງນີ້, ພວກເຮົາໄດ້ເຮັດວຽກກັບ Abracon ເພື່ອຜະລິດສ່ວນ 3.3μH ທີ່ມີຈຸດເພື່ອຊີ້ບອກ polarity, ແລະສໍາຄັນ, ມາກັບ reel ກັບພວກເຂົາທັງຫມົດສອດຄ່ອງກັບວິທີດຽວກັນ. TBD ແມ່ນ (ຫຼືຈະຫຼາຍໃນໄວໆນີ້) ສາມາດໃຊ້ໄດ້ກັບປະຊາຊົນທົ່ວໄປຈາກຜູ້ຈັດຈໍາຫນ່າຍ. ດັ່ງທີ່ໄດ້ກ່າວມາກ່ອນຫນ້ານີ້, ການສະຫນອງ VREG_AVDD ແມ່ນມີຄວາມອ່ອນໄຫວຫຼາຍຕໍ່ສິ່ງລົບກວນ, ແລະດັ່ງນັ້ນຈິ່ງຕ້ອງໄດ້ຮັບການກັ່ນຕອງ. ພວກເຮົາພົບເຫັນວ່າ VREG_AVDD ພຽງແຕ່ແຕ້ມປະມານ 200μA, ຕົວກອງ RC ຂອງ 33Ω ແລະ 4.7μF ແມ່ນພຽງພໍ.

- ດັ່ງນັ້ນ, ເພື່ອສະຫຼຸບ, ອົງປະກອບທີ່ໃຊ້ຈະເປັນ ...

- C6, C7 & C9 – 4.7μF (0402, 1005 ແມັດ)

- L1 – Abracon TBD (0806, 2016 metric)

- R3 – 33Ω (0402, 1005 ແມັດ)

- ເອກະສານຂໍ້ມູນ RP2350 ມີການສົນທະນາລາຍລະອຽດເພີ່ມເຕີມກ່ຽວກັບຄໍາແນະນໍາການຈັດວາງຂອງລະບຽບການ, ກະລຸນາເບິ່ງອົງປະກອບພາຍນອກແລະຄວາມຕ້ອງການຮູບແບບ PCB.

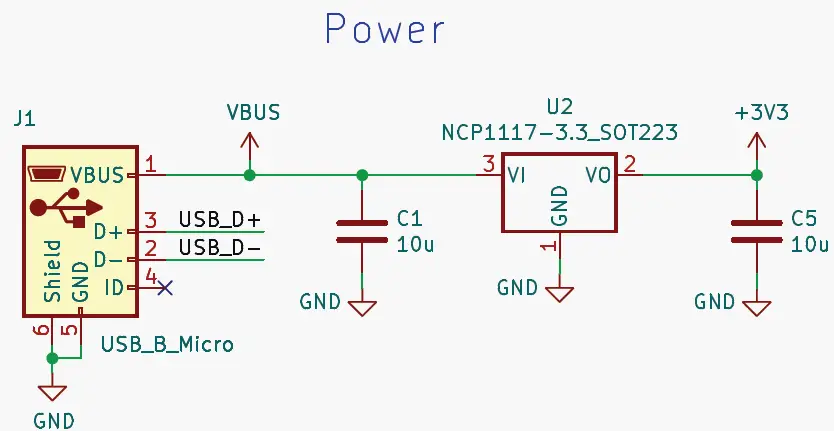

ການສະ ໜອງ ຂາເຂົ້າ

ການເຊື່ອມຕໍ່ພະລັງງານຂາເຂົ້າສໍາລັບການອອກແບບນີ້ແມ່ນຜ່ານ pin 5V VBUS ຂອງຕົວເຊື່ອມຕໍ່ Micro-USB (ມີປ້າຍຊື່ J1 ໃນຮູບ 5). ນີ້ແມ່ນວິທີການທົ່ວໄປຂອງພະລັງງານອຸປະກອນເອເລັກໂຕຣນິກ, ແລະມັນເຮັດໃຫ້ຄວາມຮູ້ສຶກຢູ່ທີ່ນີ້, ເນື່ອງຈາກວ່າ RP2350 ມີຫນ້າທີ່ USB, ເຊິ່ງພວກເຮົາຈະສາຍກັບ pins ຂໍ້ມູນຂອງຕົວເຊື່ອມຕໍ່ນີ້. ດັ່ງທີ່ພວກເຮົາຕ້ອງການພຽງແຕ່ 3.3V ສໍາລັບການອອກແບບນີ້ (ການສະຫນອງ 1.1V ມາຈາກພາຍໃນ), ພວກເຮົາຈໍາເປັນຕ້ອງຫຼຸດລົງການສະຫນອງ USB 5V ຂາເຂົ້າ, ໃນກໍລະນີນີ້, ການນໍາໃຊ້ອື່ນ vol ພາຍນອກ.tage regulator, ໃນກໍລະນີນີ້ເປັນລະບຽບເສັ້ນ (aka Low Drop Out regulator, ຫຼື LDO). ກ່ອນຫນ້ານີ້ໄດ້ຍົກໃຫ້ເຫັນເຖິງຄຸນງາມຄວາມດີຂອງການນໍາໃຊ້ເຄື່ອງຄວບຄຸມການສະຫຼັບທີ່ມີປະສິດທິພາບ, ມັນກໍ່ອາດຈະເປັນທາງເລືອກທີ່ສະຫລາດທີ່ຈະໃຊ້ຫນຶ່ງຢູ່ທີ່ນີ້ເຊັ່ນດຽວກັນ, ແຕ່ຂ້ອຍໄດ້ເລືອກຄວາມງ່າຍດາຍ. ກ່ອນອື່ນ ໝົດ, ການໃຊ້ LDO ແມ່ນງ່າຍກວ່າສະ ເໝີ ໄປ. ບໍ່ມີການຄິດໄລ່ທີ່ຕ້ອງການເພື່ອຄິດໄລ່ວ່າຕົວ inductor ຂະຫນາດໃດທີ່ທ່ານຄວນໃຊ້, ຫຼືຕົວເກັບປະຈຸຜົນຜະລິດມີຂະຫນາດໃຫຍ່ເທົ່າໃດ, ແລະຮູບແບບປົກກະຕິແມ່ນກົງໄປກົງມາຫຼາຍ. ອັນທີສອງ, ການປະຫຍັດພະລັງງານທຸກຄັ້ງສຸດທ້າຍບໍ່ແມ່ນຈຸດປະສົງຢູ່ທີ່ນີ້; ຖ້າມັນແມ່ນ, ຂ້ອຍຈະພິຈາລະນາຢ່າງຈິງຈັງໂດຍໃຊ້ຕົວຄວບຄຸມການສະຫຼັບ, ແລະເຈົ້າສາມາດຊອກຫາ ex ໄດ້ample ຂອງການເຮັດແນວນັ້ນໃນ Raspberry Pi Pico 2. ແລະອັນທີສາມ, ຂ້າພະເຈົ້າພຽງແຕ່ສາມາດ 'ຢືມ' ວົງຈອນທີ່ຂ້ອຍເຄີຍໃຊ້ໃນ RP2040 ຂອງກະດານ Minimal. NCP1117 (U2) ທີ່ເລືອກຢູ່ທີ່ນີ້ມີຜົນຜະລິດຄົງທີ່ຂອງ 3.3V, ສາມາດໃຊ້ໄດ້ຢ່າງກວ້າງຂວາງ, ແລະສາມາດສະຫນອງໄດ້ເຖິງ 1A ຂອງປະຈຸບັນ, ເຊິ່ງຈະມີຫຼາຍສໍາລັບການອອກແບບສ່ວນໃຫຍ່. ການເບິ່ງແຜ່ນຂໍ້ມູນສໍາລັບ NCP1117 ບອກພວກເຮົາວ່າອຸປະກອນນີ້ຕ້ອງການຕົວເກັບປະຈຸ 10μF ຢູ່ໃນວັດສະດຸປ້ອນ, ແລະອີກອັນຫນຶ່ງຢູ່ໃນຜົນຜະລິດ (C1 ແລະ C5).

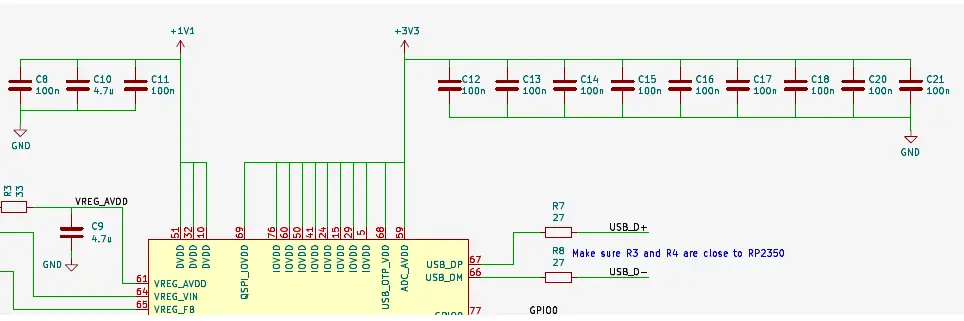

Decoupling capacitor

ຮູບທີ 6. ພາກສ່ວນ Schematic ສະແດງໃຫ້ເຫັນການປ້ອນຂໍ້ມູນການສະຫນອງພະລັງງານ RP2350, voltage regulator ແລະ decoupling capacitor

ລັກສະນະອື່ນຂອງການອອກແບບການສະຫນອງພະລັງງານແມ່ນ capacitors decoupling ທີ່ຕ້ອງການສໍາລັບ RP2350. ເຫຼົ່ານີ້ສະຫນອງສອງຫນ້າທີ່ພື້ນຖານ. ປະການທໍາອິດ, ພວກເຂົາເຈົ້າການກັ່ນຕອງອອກສິ່ງລົບກວນການສະຫນອງພະລັງງານ, ແລະອັນທີສອງ, ສະຫນອງການສະຫນອງທ້ອງຖິ່ນຂອງຄ່າໃຊ້ຈ່າຍທີ່ວົງຈອນພາຍໃນ RP2350 ສາມາດນໍາໃຊ້ໃນເວລາສັ້ນໆ. ນີ້ປ້ອງກັນບໍ່ໃຫ້ voltage ລະດັບໃນເຂດໄກ້ຄຽງທັນທີຈາກການຫຼຸດລົງຫຼາຍເກີນໄປໃນເວລາທີ່ຄວາມຕ້ອງການໃນປະຈຸບັນເພີ່ມຂຶ້ນຢ່າງກະທັນຫັນ. ເນື່ອງຈາກວ່ານີ້, ມັນເປັນສິ່ງສໍາຄັນທີ່ຈະວາງ decoupling ໃກ້ຊິດກັບ pins ພະລັງງານ. ໂດຍປົກກະຕິ, ພວກເຮົາແນະນໍາໃຫ້ໃຊ້ຕົວເກັບປະຈຸ 100nF ຕໍ່ສາຍພະລັງງານ, ຢ່າງໃດກໍຕາມ, ພວກເຮົາ deviate ຈາກກົດລະບຽບນີ້ໃນສອງສາມກໍລະນີ.

ຮູບ 7. ພາກສ່ວນຂອງການຈັດວາງສະແດງ RP2350 routing ແລະ decoupling

- ກ່ອນອື່ນ ໝົດ, ເພື່ອໃຫ້ສາມາດມີພື້ນທີ່ພຽງພໍ ສຳ ລັບທຸກໆ pins ຊິບເພື່ອສາມາດສົ່ງອອກ, ຫ່າງຈາກອຸປະກອນ, ພວກເຮົາຕ້ອງປະນີປະນອມກັບປະລິມານຂອງ capacitors decoupling ທີ່ພວກເຮົາສາມາດນໍາໃຊ້ໄດ້. ໃນການອອກແບບນີ້, pins 53 ແລະ 54 ຂອງ RP2350A (pins 68 ແລະ 69 ຂອງ RP2350B) ແບ່ງປັນ capacitor ດຽວ (C12 ໃນຮູບ 7 ແລະຮູບ 6), ເນື່ອງຈາກວ່າບໍ່ມີຫ້ອງຫຼາຍຢູ່ຂ້າງຂອງອຸປະກອນ, ແລະອົງປະກອບ. ແລະຮູບແບບຂອງລະບຽບການມີຄວາມສໍາຄັນ.

- ການຂາດພື້ນທີ່ນີ້ສາມາດເອົາຊະນະໄດ້ບາງຢ່າງຖ້າພວກເຮົາໃຊ້ເຕັກໂນໂລຢີທີ່ສັບສົນ / ລາຄາແພງກວ່າ, ເຊັ່ນ: ອົງປະກອບຂະຫນາດນ້ອຍກວ່າ, ຫຼືສີ່ຊັ້ນ PCB ທີ່ມີສ່ວນປະກອບທັງດ້ານເທິງແລະດ້ານລຸ່ມ. ນີ້ແມ່ນການຄ້າອອກແບບ; ພວກເຮົາໄດ້ຫຼຸດລົງຄວາມສັບສົນແລະຄ່າໃຊ້ຈ່າຍ, ໃນຄ່າໃຊ້ຈ່າຍຂອງການມີ decoupling capacitance ຫນ້ອຍ, ແລະ capacitors ທີ່ຢູ່ຫ່າງຈາກ chip ເລັກນ້ອຍກ່ວາທີ່ດີທີ່ສຸດ (ນີ້ເຮັດໃຫ້ inductance ເພີ່ມຂຶ້ນ). ນີ້ອາດຈະມີຜົນກະທົບຂອງການຈໍາກັດຄວາມໄວສູງສຸດທີ່ການອອກແບບສາມາດດໍາເນີນການໄດ້, ເປັນ voltage ການສະຫນອງສາມາດໄດ້ຮັບສິ່ງລົບກວນເກີນໄປແລະຫຼຸດລົງຕ່ໍາກວ່າລະດັບຕໍາ່ສຸດທີ່ອະນຸຍາດtage; ແຕ່ສໍາລັບຄໍາຮ້ອງສະຫມັກສ່ວນໃຫຍ່, ການຄ້ານີ້ຄວນຈະເປັນທີ່ຍອມຮັບ.

- ການ deviation ອື່ນໆຈາກກົດລະບຽບ 100nF ແມ່ນດັ່ງນັ້ນພວກເຮົາສາມາດປັບປຸງ vol ໄດ້tage ການປະຕິບັດລະບຽບ; ພວກເຮົາແນະນໍາໃຫ້ໃຊ້ 4.7μF ສໍາລັບ C10, ເຊິ່ງຖືກຈັດໃສ່ໃນດ້ານອື່ນໆຂອງຊິບຈາກຜູ້ຄວບຄຸມ.

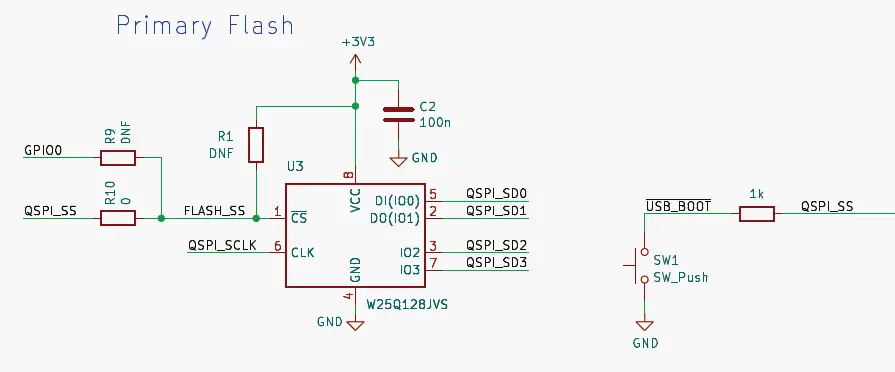

ບົດທີ 3. Flash Memory

ແຟລດຫຼັກ

ຮູບທີ 8. ພາກສ່ວນແຜນຜັງສະແດງໜ່ວຍຄວາມຈຳແຟລດຫຼັກ ແລະວົງຈອນ USB_BOOT

- ເພື່ອໃຫ້ສາມາດເກັບຮັກສາລະຫັດໂຄງການທີ່ RP2350 ສາມາດ boot ແລະດໍາເນີນການໄດ້, ພວກເຮົາຈໍາເປັນຕ້ອງໃຊ້ flash memory, ໂດຍສະເພາະ, quad SPI flash memory. ອຸປະກອນທີ່ເລືອກຢູ່ນີ້ແມ່ນອຸປະກອນ W25Q128JVS (U3 ໃນຮູບ 8), ເຊິ່ງເປັນຊິບ 128Mbit (16MB). ນີ້ແມ່ນຂະຫນາດຫນ່ວຍຄວາມຈໍາທີ່ໃຫຍ່ທີ່ສຸດທີ່ RP2350 ສາມາດຮອງຮັບໄດ້. ຖ້າແອັບພລິເຄຊັນສະເພາະຂອງເຈົ້າບໍ່ຕ້ອງການບ່ອນເກັບຂໍ້ມູນຫຼາຍ, ໜ່ວຍຄວາມຈຳທີ່ນ້ອຍກວ່າ ແລະລາຄາຖືກກວ່າສາມາດໃຊ້ແທນໄດ້.

- ເນື່ອງຈາກ databus ນີ້ສາມາດມີຄວາມຖີ່ຂ້ອນຂ້າງສູງແລະຖືກນໍາໃຊ້ເປັນປົກກະຕິ, pins QSPI ຂອງ RP2350 ຄວນຖືກສາຍໂດຍກົງກັບ flash, ການນໍາໃຊ້ການເຊື່ອມຕໍ່ສັ້ນເພື່ອຮັກສາຄວາມສົມບູນຂອງສັນຍານ, ແລະຍັງຫຼຸດຜ່ອນ crosstalk ໃນວົງຈອນອ້ອມຂ້າງ. Crosstalk ແມ່ນບ່ອນທີ່ສັນຍານຢູ່ໃນຕາຫນ່າງວົງຈອນຫນຶ່ງສາມາດກະຕຸ້ນ vol ທີ່ບໍ່ຕ້ອງການtages ໃນວົງຈອນໃກ້ຄຽງ, ອາດຈະເຮັດໃຫ້ເກີດຄວາມຜິດພາດ.

- ສັນຍານ QSPI_SS ເປັນກໍລະນີພິເສດ. ມັນເຊື່ອມຕໍ່ກັບແຟດໂດຍກົງ, ແຕ່ມັນຍັງມີຕົວຕ້ານທານສອງຕົວ (ດີ, ສີ່, ແຕ່ຂ້ອຍຈະມາຮອດໃນພາຍຫລັງ) ເຊື່ອມຕໍ່ກັບມັນ. ທໍາອິດ (R1) ແມ່ນການດຶງເຖິງການສະຫນອງ 3.3V. ໜ່ວຍຄວາມຈຳແຟລດຕ້ອງການການປ້ອນຂໍ້ມູນເລືອກຊິບໃຫ້ຢູ່ໃນປະລິມານດຽວກັນtage ເປັນ pin ການສະຫນອງ 3.3V ຂອງຕົນເອງຍ້ອນວ່າອຸປະກອນໄດ້ຖືກເປີດຂຶ້ນ, ຖ້າບໍ່ດັ່ງນັ້ນ, ມັນບໍ່ເຮັດວຽກຢ່າງຖືກຕ້ອງ. ເມື່ອ RP2350 ຖືກເປີດ, PIN QSPI_SS ຂອງມັນຈະເລີ່ມຕົ້ນອັດຕະໂນມັດເປັນການດຶງຂຶ້ນ, ແຕ່ມີໄລຍະເວລາສັ້ນໆໃນລະຫວ່າງການເປີດທີ່ສະຖານະຂອງ PIN QSPI_SS ບໍ່ສາມາດຮັບປະກັນໄດ້. ການເພີ່ມຕົວຕ້ານທານແບບດຶງຂຶ້ນຮັບປະກັນວ່າຄວາມຕ້ອງການນີ້ຈະມີຄວາມພໍໃຈສະເຫມີ. R1 ຖືກຫມາຍເປັນ DNF (ບໍ່ເຫມາະ) ໃນ schematic, ດັ່ງທີ່ພວກເຮົາໄດ້ພົບເຫັນວ່າອຸປະກອນ flash ໂດຍສະເພາະນີ້, ການດຶງພາຍນອກແມ່ນບໍ່ຈໍາເປັນ. ຢ່າງໃດກໍຕາມ, ຖ້າ flash ທີ່ແຕກຕ່າງກັນຖືກນໍາໃຊ້, ມັນອາດຈະກາຍເປັນສິ່ງສໍາຄັນທີ່ຈະສາມາດໃສ່ຕົວຕ້ານທານ 10kΩ ຢູ່ທີ່ນີ້, ດັ່ງນັ້ນມັນໄດ້ຖືກລວມເຂົ້າໃນກໍລະນີ.

- ຕົວຕ້ານທານທີສອງ (R6) ແມ່ນຕົວຕ້ານທານ 1kΩ, ເຊື່ອມຕໍ່ກັບປຸ່ມກົດ (SW1) ທີ່ມີປ້າຍຊື່ 'USB_BOOT'. ນີ້ແມ່ນຍ້ອນວ່າ PIN QSPI_SS ຖືກໃຊ້ເປັນ 'ສາຍໃສ່ເກີບ'; RP2350 ກວດເບິ່ງຄ່າຂອງ I/O ນີ້ໃນລະຫວ່າງລໍາດັບການບູດ, ແລະຖ້າພົບວ່າມັນເປັນ logic 0, ຫຼັງຈາກນັ້ນ RP2350 ກັບຄືນສູ່ໂຫມດ BOOTSEL, ບ່ອນທີ່ RP2350 ນໍາສະເຫນີຕົວມັນເອງເປັນອຸປະກອນເກັບຮັກສາ USB, ແລະລະຫັດສາມາດຖືກຄັດລອກໂດຍກົງ. ກັບມັນ. ຖ້າພວກເຮົາພຽງແຕ່ກົດປຸ່ມ, ພວກເຮົາດຶງ PIN QSPI_SS ກັບດິນ, ແລະຖ້າອຸປະກອນຖືກຕັ້ງຄ່າໃຫມ່ຫຼັງຈາກນັ້ນ (ເຊັ່ນ: ໂດຍການປິດລັບ RUN), RP2350 ຈະປິດເປີດໃຫມ່ໃນໂຫມດ BOOTSEL ແທນທີ່ຈະພະຍາຍາມແລ່ນເນື້ອຫາຂອງແຟດ. ຕົວຕ້ານທານເຫຼົ່ານີ້, R2 ແລະ R6 (R9 ແລະ R10 ຍັງ), ຄວນຖືກວາງໄວ້ໃກ້ໆກັບຊິບແຟດ, ດັ່ງນັ້ນພວກເຮົາຫຼີກເວັ້ນການຕິດຕາມທອງແດງທີ່ມີຄວາມຍາວເພີ່ມເຕີມເຊິ່ງສາມາດສົ່ງຜົນກະທົບຕໍ່ສັນຍານ.

- ທັງຫມົດຂ້າງເທິງນີ້ໂດຍສະເພາະໃຊ້ກັບ RP2350, ເຊິ່ງບໍ່ມີແຟດພາຍໃນ. ແນ່ນອນ, ອຸປະກອນ RP2354 ມີຄວາມຊົງຈໍາພາຍໃນ 2MB flash, ດັ່ງນັ້ນຫນ່ວຍຄວາມຈໍາ U3 ພາຍນອກແມ່ນບໍ່ຈໍາເປັນ, ດັ່ງນັ້ນ U3 ສາມາດຖືກໂຍກຍ້າຍອອກຈາກ schematic ໄດ້ຢ່າງປອດໄພ, ຫຼືພຽງແຕ່ປະໄວ້ໂດຍບໍ່ມີປະຊາຊົນ. ໃນທັງສອງກໍລະນີນີ້, ພວກເຮົາຍັງຕ້ອງການຮັກສາສະວິດ USB_BOOT ເຊື່ອມຕໍ່ກັບ QSPI_SS, ດັ່ງນັ້ນພວກເຮົາຍັງສາມາດເຂົ້າໄປໃນໂຫມດບູດ USB ໄດ້.

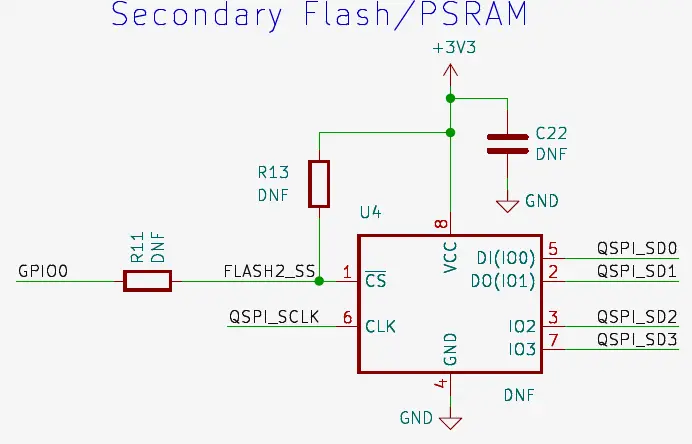

ແຟດສຳຮອງ ຫຼື PSRAM

- ຊຸດ RP235x ໃນປັດຈຸບັນສະຫນັບສະຫນູນອຸປະກອນຫນ່ວຍຄວາມຈໍາທີສອງໂດຍໃຊ້ pins QSPI ດຽວກັນ, ໂດຍມີ GPIO ສະຫນອງການເລືອກເອົາຊິບເພີ່ມເຕີມ. ດັ່ງນັ້ນ, ຖ້າພວກເຮົາໃຊ້ RP2354 (ເຊິ່ງມີແຟດພາຍໃນ), ພວກເຮົາສາມາດໃຊ້ U3 ເປັນແຟດຮອງ, ຫຼືແມ້ກະທັ້ງປ່ຽນມັນດ້ວຍອຸປະກອນ PSRAM. ເພື່ອເຮັດສິ່ງນີ້, ພວກເຮົາຈໍາເປັນຕ້ອງໄດ້ຕັດການເຊື່ອມຕໍ່ QSPI_SS ຈາກ U3, ແລະເຊື່ອມຕໍ່ມັນກັບ GPIO ທີ່ເຫມາະສົມແທນ. GPIO ທີ່ໃກ້ທີ່ສຸດທີ່ສາມາດເປັນຊິບເລືອກ (XIP_CS1n) ແມ່ນ GPIO0, ດັ່ງນັ້ນໂດຍການຖອນ 0Ω ຈາກ R10, ແລະເຫມາະກັບ R9, ຕອນນີ້ພວກເຮົາສາມາດເຂົ້າເຖິງ U3 ນອກຈາກແຟລດເທິງຊິບ. ໃນຄໍາສັ່ງທີ່ຈະເອົາ advan ຢ່າງເຕັມສ່ວນtage ຂອງຄຸນນະສົມບັດນີ້, ບ່ອນທີ່ພວກເຮົາມີສອງອຸປະກອນຫນ່ວຍຄວາມຈໍາພາຍນອກເພື່ອໃຫ້ພາກສ່ວນ flash-less RP2350 ໄດ້ຮັບຜົນປະໂຫຍດ, ຂະຫນາດໃຫຍ່ຂອງສອງກະດານ Minimal, ສໍາລັບ RP2350B, ປະກອບມີ footprint ທາງເລືອກ (U4) ສໍາລັບຊິບຫນ່ວຍຄວາມຈໍາເພີ່ມເຕີມ.

ຮູບທີ 9. ພາກສ່ວນແຜນຜັງສະແດງອຸປະກອນໜ່ວຍຄວາມຈຳສຳຮອງທີ່ເປັນທາງເລືອກ

ເພື່ອຈະສາມາດນໍາໃຊ້ອຸປະກອນນີ້, ມັນຈະແນ່ນອນວ່າຈະມີປະຊາຊົນ, ເຊັ່ນດຽວກັນກັບ R11 (0Ω), ແລະ R13 (10KΩ). ການເພີ່ມ R11 ເຊື່ອມຕໍ່ GPIO0 (ສັນຍານ XIP_CS1n) ກັບຊິບເລືອກຂອງຫນ່ວຍຄວາມຈໍາທີສອງ. ການດຶງຂຶ້ນເທິງຊິບເລືອກ pin ແມ່ນຈໍາເປັນແນ່ນອນໃນເວລານີ້, ເນື່ອງຈາກວ່າສະຖານະເລີ່ມຕົ້ນຂອງ GPIO0 ຈະຖືກດຶງຕ່ໍາໃນເວລາເປີດໄຟ, ເຊິ່ງຈະເຮັດໃຫ້ອຸປະກອນແຟດຂອງພວກເຮົາລົ້ມເຫລວ. C22 ຍັງຕ້ອງການເພື່ອສະຫນອງການແຍກການສະຫນອງພະລັງງານໃນທ້ອງຖິ່ນສໍາລັບ U4.

ສະຫນັບສະຫນູນ chip flash

ລໍາດັບ flash probe ເບື້ອງຕົ້ນ, ໃຊ້ໂດຍດ້ານລຸ່ມເພື່ອສະກັດ s ທີສອງtage ຈາກ flash, ໃຊ້ຄໍາສັ່ງອ່ານ 03h serial, ທີ່ມີທີ່ຢູ່ 24-bit, ແລະໂມງ serial ປະມານ 1MHz. ມັນຊ້ຳໆຮອບວຽນຜ່ານສີ່ປະສົມຂອງຂົ້ວໂມງ ແລະໄລຍະໂມງ, ຊອກຫາວິນາທີທີ່ຖືກຕ້ອງ.tage CRC32 checksum.

ໃນຖານະເປັນທີສອງ stagຫຼັງຈາກນັ້ນ, e ແມ່ນບໍ່ເສຍຄ່າເພື່ອຕັ້ງຄ່າ execute-in-place ໂດຍໃຊ້ຄໍາສັ່ງອ່ານ serial 03h ດຽວກັນ, RP2350 ສາມາດປະຕິບັດ flash cached ໃນສະຖານທີ່ທີ່ມີຊິບໃດໆທີ່ສະຫນັບສະຫນູນ 03h serial read ກັບ 24-bit addressing, ເຊິ່ງປະກອບມີອຸປະກອນ flash 25-series ສ່ວນໃຫຍ່. . SDK ໃຫ້ example ສອງ stage ສໍາລັບ CPOL=0 CPHA=0, ຢູ່ https://github.com/raspberrypi/pico-sdk/blob/master/src/rp2350/boot_stage2/boot2_generic_03h.S. ເພື່ອຮອງຮັບການຂຽນໂປລແກລມແຟລດໂດຍໃຊ້ປົກກະຕິໃນດ້ານລຸ່ມ, ອຸປະກອນຍັງຕ້ອງຕອບສະຫນອງຄໍາສັ່ງຕໍ່ໄປນີ້:

- 02h 256-byte ໂຄງການຫນ້າ

- ອ່ານສະຖານະ 05h

- 06h set write enable latch

- 20h 4kB ພາກສ່ວນລົບ

RP2350 ຍັງຮອງຮັບຫຼາກຫຼາຍຮູບແບບການເຂົ້າເຖິງແບບ dual-SPI ແລະ QSPI. ຕົວຢ່າງampເລ, https://github.com/raspberrypi/pico-sdk/blob/master/src/rp2350/boot_stage2/boot2_w25q080.S ຕັ້ງຄ່າອຸປະກອນ Winbond W25Q-series ສໍາລັບຮູບແບບການອ່ານຕໍ່ເນື່ອງຂອງ quad-IO, ບ່ອນທີ່ RP2350 ສົ່ງທີ່ຢູ່ quad-IO (ໂດຍບໍ່ມີຄໍານໍາຫນ້າ) ແລະ flash ຕອບສະຫນອງກັບຂໍ້ມູນ quad-IO.

ຄວາມລະມັດລະວັງບາງຢ່າງແມ່ນຈໍາເປັນກັບໂຫມດ Flash XIP ທີ່ອຸປະກອນ flash ຢຸດເຊົາການຕອບສະຫນອງຕໍ່ຄໍາສັ່ງ serial ມາດຕະຖານເຊັ່ນ: ຮູບແບບການອ່ານຕໍ່ເນື່ອງ Winbond ທີ່ໄດ້ກ່າວມາຂ້າງເທິງ. ນີ້ສາມາດເຮັດໃຫ້ເກີດບັນຫາເມື່ອ RP2350 ຖືກຣີເຊັດ, ແຕ່ອຸປະກອນແຟລດບໍ່ໄດ້ເປີດວົງຈອນ, ເພາະວ່າ flash ຈະບໍ່ຕອບສະຫນອງຕໍ່ລໍາດັບ flash probe ຂອງ bootrom. ກ່ອນທີ່ຈະອອກການອ່ານ 03h serial, bootrom ສະເຫມີອອກລໍາດັບຄົງທີ່ຕໍ່ໄປນີ້, ເຊິ່ງເປັນລໍາດັບທີ່ພະຍາຍາມດີທີ່ສຸດສໍາລັບການຢຸດ XIP ໃນອຸປະກອນແຟດຕ່າງໆ:

- CSn=1, IO[3:0]=4'b0000 (ຜ່ານດຶງລົງເພື່ອຫຼີກເວັ້ນການຂັດແຍ້ງ), ບັນຫາ ×32 ໂມງ

- CSn=0, IO[3:0]=4'b1111 (ຜ່ານການດຶງຂຶ້ນເພື່ອຫຼີກເວັ້ນການຂັດແຍ້ງ), ບັນຫາ ×32 ໂມງ

- CSn=1

- CSn=0, MOSI=1'b1 (ຂັບເຄື່ອນ low-Z, ທັງຫມົດ I/Os Hi-Z), ອອກ ×16 ໂມງ

ຖ້າອຸປະກອນທີ່ທ່ານເລືອກບໍ່ຕອບສະຫນອງຕໍ່ລໍາດັບນີ້ໃນເວລາທີ່ຢູ່ໃນໂຫມດການອ່ານຢ່າງຕໍ່ເນື່ອງຂອງມັນ, ມັນຕ້ອງຖືກເກັບໄວ້ໃນສະຖານະທີ່ແຕ່ລະການໂອນຈະຖືກນໍາຫນ້າໂດຍຄໍາສັ່ງ serial, ຖ້າບໍ່ດັ່ງນັ້ນ RP2350 ຈະບໍ່ສາມາດຟື້ນຕົວໄດ້ຫຼັງຈາກການຕັ້ງຄ່າພາຍໃນ.

ສໍາລັບລາຍລະອຽດເພີ່ມເຕີມກ່ຽວກັບ QSPI, ກະລຸນາເບິ່ງ QSPI Memory Interface (QMI) ໃນເອກະສານຂໍ້ມູນ RP2350.

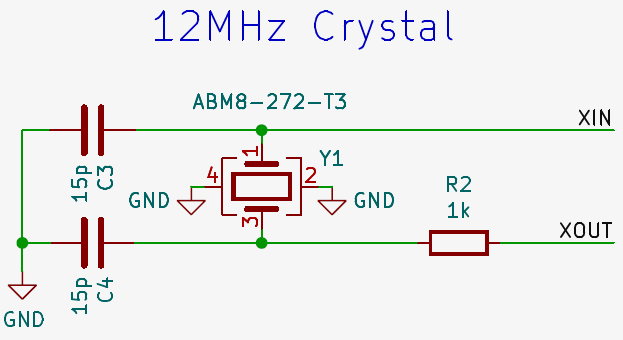

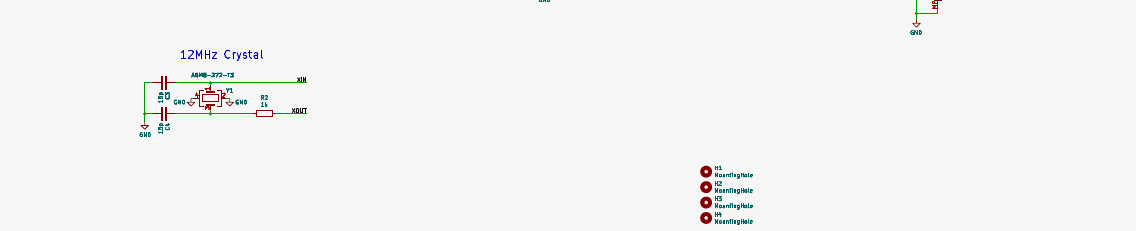

ບົດທີ 4. Crystal Oscillator

ຮູບທີ 10. ພາກສ່ວນ Schematic ສະແດງການ oscillator crystal ແລະ Load capacitors

- ເວົ້າຢ່າງເຂັ້ມງວດ, RP2350 ບໍ່ໄດ້ຮຽກຮ້ອງໃຫ້ມີແຫຼ່ງໂມງພາຍນອກ, ເນື່ອງຈາກວ່າມັນມີ oscillator ພາຍໃນຂອງຕົນເອງ. ຢ່າງໃດກໍຕາມ, ເນື່ອງຈາກວ່າຄວາມຖີ່ຂອງ oscillator ພາຍໃນນີ້ບໍ່ໄດ້ຖືກກໍານົດດີຫຼືຄວບຄຸມ, ແຕກຕ່າງກັນຈາກ chip ກັບ chip, ເຊັ່ນດຽວກັນກັບການສະຫນອງທີ່ແຕກຕ່າງກັນ.tages ແລະອຸນຫະພູມ, ແນະນໍາໃຫ້ໃຊ້ແຫຼ່ງຄວາມຖີ່ພາຍນອກທີ່ຫມັ້ນຄົງ. ຄໍາຮ້ອງສະຫມັກທີ່ອີງໃສ່ຄວາມຖີ່ທີ່ແນ່ນອນແມ່ນບໍ່ເປັນໄປໄດ້ໂດຍບໍ່ມີແຫຼ່ງຄວາມຖີ່ພາຍນອກ, USB ເປັນ ex primeampເລ.

- ການສະຫນອງແຫຼ່ງຄວາມຖີ່ພາຍນອກສາມາດເຮັດໄດ້ໃນຫນຶ່ງໃນສອງວິທີ: ບໍ່ວ່າຈະໂດຍການສະຫນອງແຫຼ່ງໂມງທີ່ມີຜົນຜະລິດ CMOS (ຄື້ນສີ່ຫລ່ຽມຂອງ IOVDD voltage) ເຂົ້າໄປໃນ XIN pin, ຫຼືໂດຍການນໍາໃຊ້ໄປເຊຍກັນ 12MHz ເຊື່ອມຕໍ່ລະຫວ່າງ

- XIN ແລະ XOUT. ການນໍາໃຊ້ໄປເຊຍກັນເປັນທາງເລືອກທີ່ຕ້ອງການຢູ່ທີ່ນີ້, ຍ້ອນວ່າພວກເຂົາເຈົ້າທັງສອງແມ່ນຂ້ອນຂ້າງລາຄາຖືກແລະຖືກຕ້ອງຫຼາຍ.

- ແກ້ວທີ່ເລືອກສໍາລັບການອອກແບບນີ້ແມ່ນ ABM8-272-T3 (Y1 ໃນຮູບ 10). ນີ້ແມ່ນໄປເຊຍກັນ 12MHz ດຽວກັນທີ່ໃຊ້ໃນ Raspberry Pi Pico ແລະ Raspberry Pi Pico 2. ພວກເຮົາຂໍແນະນໍາໃຫ້ໃຊ້ໄປເຊຍກັນນີ້ພ້ອມກັບວົງຈອນທີ່ມາພ້ອມກັບເພື່ອຮັບປະກັນວ່າໂມງເລີ່ມຕົ້ນຢ່າງໄວວາພາຍໃຕ້ທຸກເງື່ອນໄຂໂດຍບໍ່ມີການທໍາລາຍໄປເຊຍກັນເອງ. Crystal ມີຄວາມທົນທານຕໍ່ຄວາມຖີ່ 30ppm, ເຊິ່ງຄວນຈະດີພໍສໍາລັບຄໍາຮ້ອງສະຫມັກສ່ວນໃຫຍ່. ຄຽງຄູ່ກັບຄວາມທົນທານຄວາມຖີ່ຂອງ +/-30ppm, ມັນມີ ESR ສູງສຸດຂອງ 50Ω, ແລະຄວາມອາດສາມາດໂຫຼດຂອງ 10pF, ທັງສອງມີ bearing ກ່ຽວກັບທາງເລືອກຂອງອົງປະກອບປະກອບ.

- ສໍາລັບໄປເຊຍກັນທີ່ຈະ oscillate ໃນຄວາມຖີ່ທີ່ຕ້ອງການ, ຜູ້ຜະລິດກໍານົດຄວາມອາດສາມາດໂຫຼດທີ່ມັນຕ້ອງການສໍາລັບມັນເຮັດແນວນັ້ນ, ແລະໃນກໍລະນີນີ້, ມັນແມ່ນ 10pF. capacitance ໂຫຼດນີ້ແມ່ນບັນລຸໄດ້ໂດຍການວາງສອງ capacitors ມູນຄ່າເທົ່າທຽມກັນ, ຫນຶ່ງໃນແຕ່ລະດ້ານຂອງໄປເຊຍກັນກັບດິນ (C3 ແລະ C4). ຈາກຈຸດໄປເຊຍກັນຂອງ view, capacitors ເຫຼົ່ານີ້ແມ່ນເຊື່ອມຕໍ່ໃນຊຸດລະຫວ່າງສອງ terminals ຂອງມັນ. ທິດສະດີວົງຈອນພື້ນຖານບອກພວກເຮົາວ່າພວກມັນປະສົມກັນເພື່ອໃຫ້ຄວາມອາດສາມາດຂອງ (C3*C4)/(C3+C4), ແລະເປັນ C3=C4, ຫຼັງຈາກນັ້ນມັນເປັນພຽງແຕ່ C3/2. ໃນນີ້ exampດັ່ງນັ້ນ, ພວກເຮົາໄດ້ໃຊ້ຕົວເກັບປະຈຸ 15pF, ດັ່ງນັ້ນການປະສົມປະສານຂອງຊຸດແມ່ນ 7.5pF. ນອກເຫນືອໄປຈາກຄວາມອາດສາມາດໂຫຼດໂດຍເຈດຕະນານີ້, ພວກເຮົາຍັງຕ້ອງເພີ່ມມູນຄ່າສໍາລັບ capacitance ພິເສດທີ່ບໍ່ໄດ້ຕັ້ງໃຈ, ຫຼື capacitance parasitic, ທີ່ພວກເຮົາໄດ້ຮັບຈາກການຕິດຕາມ PCB ແລະ XIN ແລະ XOUT pins ຂອງ RP2350. ພວກເຮົາຈະສົມມຸດມູນຄ່າຂອງ 3pF ສໍາລັບການນີ້, ແລະຍ້ອນວ່າ capacitance ນີ້ຢູ່ໃນຂະຫນານກັບ C3 ແລະ C4, ພວກເຮົາພຽງແຕ່ເພີ່ມນີ້ເພື່ອໃຫ້ພວກເຮົາມີຄວາມສາມາດໃນການໂຫຼດທັງຫມົດ 10.5pF, ເຊິ່ງຢູ່ໃກ້ກັບເປົ້າຫມາຍຂອງ 10pF. ດັ່ງທີ່ເຈົ້າສາມາດເຫັນໄດ້, ຄວາມຈຸຂອງກາຝາກຂອງການຕິດຕາມ PCB ແມ່ນປັດໃຈຫນຶ່ງ, ແລະດັ່ງນັ້ນພວກເຮົາຈໍາເປັນຕ້ອງຮັກສາພວກມັນໃຫ້ນ້ອຍເພື່ອວ່າພວກເຮົາບໍ່ເຮັດໃຫ້ກ້ອນຫີນຕົກໃຈແລະຢຸດເຊົາການສັ່ນສະເທືອນຕາມຈຸດປະສົງ. ພະຍາຍາມ ແລະຮັກສາການຈັດວາງໃຫ້ສັ້ນເທົ່າທີ່ເປັນໄປໄດ້.

- ການພິຈາລະນາທີສອງແມ່ນ ESR ສູງສຸດ (ຄວາມຕ້ານທານຊຸດທຽບເທົ່າ) ຂອງໄປເຊຍກັນ. ພວກເຮົາໄດ້ເລືອກອຸປະກອນທີ່ມີສູງສຸດ 50Ω, ດັ່ງທີ່ພວກເຮົາໄດ້ພົບເຫັນວ່ານີ້, ພ້ອມກັບຕົວຕ້ານທານຊຸດ 1kΩ (R2), ເປັນມູນຄ່າທີ່ດີທີ່ຈະປ້ອງກັນບໍ່ໃຫ້ໄປເຊຍກັນຖືກຂັບເກີນແລະເສຍຫາຍໃນເວລາທີ່ໃຊ້ IOVDD. ລະດັບ 3.3V. ຢ່າງໃດກໍຕາມ, ຖ້າ IOVDD ຫນ້ອຍກວ່າ 3.3V, ຫຼັງຈາກນັ້ນ, ປະຈຸບັນຂັບຂອງ pins XIN / XOUT ຈະຫຼຸດລົງ, ແລະທ່ານຈະພົບເຫັນວ່າ. amplitude ຂອງໄປເຊຍກັນແມ່ນຕ່ໍາ, ຫຼືອາດຈະບໍ່ເຖິງແມ່ນ oscillate ທັງຫມົດ. ໃນກໍລະນີນີ້, ຄ່າທີ່ນ້ອຍກວ່າຂອງຕົວຕ້ານທານຊຸດຈະຕ້ອງໃຊ້. ການບ່ຽງເບນໃດໆຈາກວົງຈອນໄປເຊຍກັນທີ່ສະແດງຢູ່ທີ່ນີ້, ຫຼືດ້ວຍລະດັບ IOVDD ນອກເຫນືອຈາກ 3.3V, ຈະຕ້ອງມີການທົດສອບຢ່າງກວ້າງຂວາງເພື່ອຮັບປະກັນວ່າການສັ່ນສະເທືອນຂອງ crystal ພາຍໃຕ້ທຸກເງື່ອນໄຂ, ແລະເລີ່ມຕົ້ນຢ່າງໄວວາພຽງພໍເພື່ອບໍ່ເຮັດໃຫ້ເກີດບັນຫາກັບຄໍາຮ້ອງສະຫມັກຂອງທ່ານ.

ແນະນໍາ crystal

- ສໍາລັບການອອກແບບຕົ້ນສະບັບໂດຍໃຊ້ RP2350 ພວກເຮົາແນະນໍາໃຫ້ໃຊ້ Abrcon ABM8-272-T3. ຕົວຢ່າງample, ນອກເຫນືອໄປຈາກການອອກແບບຫນ້ອຍທີ່ສຸດ example, ເບິ່ງແຜນຜັງກະດານ Pico 2 ໃນເອກະສານຊ້ອນທ້າຍ B ຂອງເອກະສານຂໍ້ມູນ Raspberry Pi Pico 2 ແລະການອອກແບບ Pico 2 files.

- ສໍາລັບການປະຕິບັດທີ່ດີທີ່ສຸດແລະຄວາມຫມັ້ນຄົງໃນທົ່ວລະດັບອຸນຫະພູມປະຕິບັດການປົກກະຕິ, ໃຊ້ Abracon ABM8-272-T3. ທ່ານສາມາດແຫຼ່ງ ABM8-272-T3 ໂດຍກົງຈາກ Abracon ຫຼືຈາກຕົວແທນຈໍາຫນ່າຍທີ່ໄດ້ຮັບອະນຸຍາດ. Pico 2 ໄດ້ຮັບການປັບແຕ່ງສະເພາະສໍາລັບ ABM8-272-T3, ເຊິ່ງມີຄຸນສົມບັດດັ່ງຕໍ່ໄປນີ້:

- ເຖິງແມ່ນວ່າທ່ານຈະໃຊ້ໄປເຊຍກັນທີ່ມີຄຸນລັກສະນະທີ່ຄ້າຍຄືກັນ, ທ່ານຈະຕ້ອງທົດສອບວົງຈອນໃນໄລຍະອຸນຫະພູມເພື່ອຮັບປະກັນຄວາມຫມັ້ນຄົງ.

- ການ oscillator ໄປເຊຍກັນແມ່ນຂັບເຄື່ອນຈາກ IOVDD voltage. ດັ່ງນັ້ນ, ການໄປເຊຍກັນ Abracon ແລະໂດຍສະເພາະ damping resistor ແມ່ນ tuned ສໍາລັບການດໍາເນີນງານ 3.3V. ຖ້າທ່ານໃຊ້ IO voltage, ທ່ານຈະຕ້ອງປັບໃຫມ່.

- ການປ່ຽນແປງໃດໆຕໍ່ກັບພາລາມິເຕີໄປເຊຍກັນມີຄວາມສ່ຽງຕໍ່ຄວາມບໍ່ສະຖຽນລະພາບໃນທົ່ວອົງປະກອບທີ່ເຊື່ອມຕໍ່ກັບວົງຈອນຂອງຜລຶກ.

- ຖ້າທ່ານບໍ່ສາມາດເອົາໄປເຊຍກັນທີ່ແນະນໍາໂດຍກົງຈາກ Abracon ຫຼືຕົວແທນຈໍາຫນ່າຍ, ໃຫ້ຕິດຕໍ່ applications@raspberrypi.com.

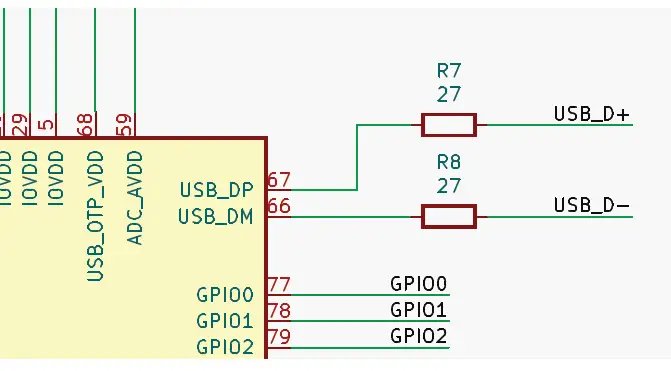

ບົດທີ 5. IOs

USB

ຮູບທີ 11. ພາກສ່ວນແຜນຜັງສະແດງ pins USB ຂອງ RP2350 ແລະການປິດຊຸດ.

- RP2350 ໃຫ້ສອງ pins ເພື່ອໃຊ້ສໍາລັບຄວາມໄວເຕັມ (FS) ຫຼືຄວາມໄວຕ່ໍາ (LS) USB, ບໍ່ວ່າຈະເປັນເຈົ້າພາບຫຼືອຸປະກອນ, ຂຶ້ນກັບຊອບແວທີ່ໃຊ້. ດັ່ງທີ່ພວກເຮົາໄດ້ສົນທະນາແລ້ວ, RP2350 ຍັງສາມາດບູດເປັນອຸປະກອນເກັບຂໍ້ມູນ USB ໄດ້, ດັ່ງນັ້ນການສາຍ pins ເຫຼົ່ານີ້ໄປຫາຕົວເຊື່ອມຕໍ່ USB (J1 ໃນຮູບ 5) ແມ່ນມີຄວາມຫມາຍ. ປັກໝຸດ USB_DP ແລະ USB_DM ໃນ RP2350 ບໍ່ຕ້ອງການການດຶງ ຫຼື ດຶງລົງເພີ່ມເຕີມໃດໆ (ຕ້ອງລະບຸຄວາມໄວ, FS ຫຼື LS, ຫຼືວ່າມັນເປັນເຈົ້າພາບ ຫຼື ອຸປະກອນ), ເພາະວ່າສິ່ງເຫຼົ່ານີ້ຖືກສ້າງຢູ່ໃນ I/Os. ຢ່າງໃດກໍ່ຕາມ, I/Os ເຫຼົ່ານີ້ຕ້ອງການຕົວຕ້ານການສິ້ນສຸດຊຸດ 27Ω (R7 ແລະ R8 ໃນຮູບທີ 11), ວາງໄວ້ໃກ້ກັບຊິບ, ເພື່ອໃຫ້ໄດ້ຕາມເງື່ອນໄຂ USB impedance.

- ເຖິງແມ່ນວ່າ RP2350 ຈະຖືກຈໍາກັດກັບອັດຕາຂໍ້ມູນຄວາມໄວເຕັມ (12Mbps), ພວກເຮົາຄວນພະຍາຍາມແລະໃຫ້ແນ່ໃຈວ່າ impedance ລັກສະນະຂອງສາຍສົ່ງ (ຕິດຕາມທອງແດງທີ່ເຊື່ອມຕໍ່ຊິບກັບຕົວເຊື່ອມຕໍ່) ຢູ່ໃກ້ກັບ.

- ສະເພາະ USB ຂອງ 90Ω (ວັດແທກຄວາມແຕກຕ່າງ). ໃນກະດານຫນາ 1 ມມເຊັ່ນນີ້, ຖ້າພວກເຮົາໃຊ້ເສັ້ນທາງກວ້າງ 0.8 ມມໃນ USB_DP ແລະ USB_DM, ທີ່ມີຊ່ອງຫວ່າງລະຫວ່າງ 0.15 ມມ, ພວກເຮົາຄວນຈະໄດ້ຮັບ impedance ລັກສະນະທີ່ແຕກຕ່າງກັນປະມານ 90Ω. ນີ້ແມ່ນເພື່ອຮັບປະກັນວ່າສັນຍານສາມາດເດີນທາງຕາມສາຍສົ່ງເຫຼົ່ານີ້ໄດ້ສະອາດເທົ່າທີ່ເປັນໄປໄດ້, ຫຼຸດຜ່ອນ voltage ການສະທ້ອນທີ່ສາມາດຫຼຸດຜ່ອນຄວາມສົມບູນຂອງສັນຍານ. ເພື່ອໃຫ້ສາຍສົ່ງເຫຼົ່ານີ້ເຮັດວຽກຢ່າງຖືກຕ້ອງ, ພວກເຮົາຈໍາເປັນຕ້ອງໃຫ້ແນ່ໃຈວ່າໂດຍກົງຂ້າງລຸ່ມນີ້ສາຍເຫຼົ່ານີ້ແມ່ນຫນ້າດິນ. ພື້ນທີ່ແຂງ, ບໍ່ຕິດຂັດຂອງດິນທອງແດງ, stretching ຄວາມຍາວທັງຫມົດຂອງການຕິດຕາມ. ໃນການອອກແບບນີ້, ເກືອບທັງຫມົດຂອງຊັ້ນທອງແດງດ້ານລຸ່ມແມ່ນອຸທິດຕົນເພື່ອພື້ນດິນ, ແລະລະມັດລະວັງໂດຍສະເພາະເພື່ອຮັບປະກັນວ່າສາຍ USB ບໍ່ຜ່ານທາງນອກ. ຖ້າ PCB ຫນາກວ່າ 1mm ຖືກເລືອກສໍາລັບການກໍ່ສ້າງຂອງທ່ານ, ຫຼັງຈາກນັ້ນພວກເຮົາມີສອງທາງເລືອກ. ພວກເຮົາສາມາດປັບປຸງວິສະວະກໍາສາຍສົ່ງ USB ເພື່ອຊົດເຊີຍສໍາລັບໄລຍະຫ່າງຫຼາຍກວ່າລະຫວ່າງການຕິດຕາມແລະພື້ນທີ່ຂ້າງລຸ່ມນີ້ (ຊຶ່ງອາດຈະເປັນໄປບໍ່ໄດ້ທາງດ້ານຮ່າງກາຍ), ຫຼືພວກເຮົາສາມາດບໍ່ສົນໃຈມັນ, ແລະຫວັງວ່າສໍາລັບການທີ່ດີທີ່ສຸດ. USB FS ສາມາດໃຫ້ອະໄພໄດ້ຫຼາຍ, ແຕ່ໄລຍະທາງຂອງທ່ານອາດຈະແຕກຕ່າງກັນ. ມັນອາດຈະເຮັດວຽກຢູ່ໃນຫຼາຍຄໍາຮ້ອງສະຫມັກ, ແຕ່ມັນອາດຈະບໍ່ສອດຄ່ອງກັບມາດຕະຖານ USB.

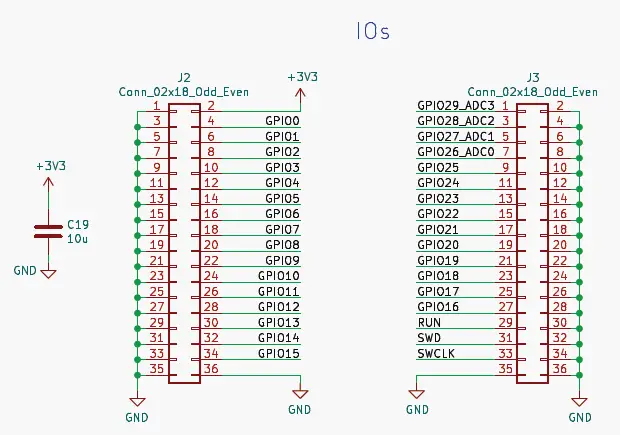

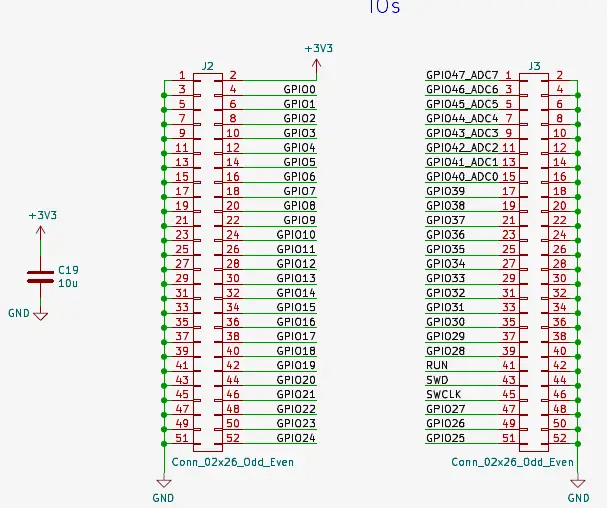

ສ່ວນຫົວ I/O

ຮູບທີ 12. ພາກສ່ວນແຜນຜັງສະແດງສ່ວນຫົວ I/O 2.54mm ຂອງລຸ້ນ QFN60

- ນອກເຫນືອໄປຈາກຕົວເຊື່ອມຕໍ່ USB ທີ່ໄດ້ກ່າວມາແລ້ວ, ມີຄູ່ຂອງຫົວ 2.54 ມມສອງແຖວ (J2 ແລະ J3 ໃນຮູບ 12), ຫນຶ່ງໃນແຕ່ລະດ້ານຂອງກະດານ, ເຊິ່ງສ່ວນທີ່ເຫຼືອຂອງ I / O ໄດ້ເຊື່ອມຕໍ່. ມີ 30 GPIO ໃນ RP2350A, ໃນຂະນະທີ່ມີ 48 GPIO ໃນ RP2350B, ດັ່ງນັ້ນສ່ວນຫົວໃນກະດານ Minimal ສະບັບນີ້ມີຂະຫນາດໃຫຍ່ກວ່າເພື່ອໃຫ້ມີ pins ເພີ່ມເຕີມ (ເບິ່ງຮູບ 13).

- ເນື່ອງຈາກວ່ານີ້ແມ່ນການອອກແບບຈຸດປະສົງທົ່ວໄປ, ໂດຍບໍ່ມີຄໍາຮ້ອງສະຫມັກໂດຍສະເພາະຢູ່ໃນໃຈ, I/O ໄດ້ຖືກເຮັດໃຫ້ສາມາດເຊື່ອມຕໍ່ໄດ້ຕາມຄວາມຕ້ອງການຂອງຜູ້ໃຊ້. ແຖວໃນຂອງ pins ໃນແຕ່ລະຫົວແມ່ນ I/Os, ແລະແຖວນອກແມ່ນເຊື່ອມຕໍ່ທັງຫມົດກັບດິນ. ມັນເປັນການປະຕິບັດທີ່ດີທີ່ຈະປະກອບມີຫຼາຍພື້ນຖານກ່ຽວກັບຕົວເຊື່ອມຕໍ່ I/O. ນີ້ຊ່ວຍຮັກສາພື້ນທີ່ impedance ຕ່ໍາ, ແລະຍັງສະຫນອງຫຼາຍເສັ້ນທາງກັບຄືນທີ່ມີທ່າແຮງສໍາລັບກະແສທີ່ເດີນທາງໄປແລະຈາກ.

- ການເຊື່ອມຕໍ່ I/O. ນີ້ແມ່ນສິ່ງສໍາຄັນເພື່ອຫຼຸດຜ່ອນການແຊກແຊງຂອງແມ່ເຫຼັກໄຟຟ້າເຊິ່ງສາມາດເກີດຈາກກະແສການກັບຄືນຂອງສັນຍານທີ່ປ່ຽນຢ່າງໄວວາໃຊ້ເວລາຍາວ, ເສັ້ນທາງ looping ເພື່ອສໍາເລັດວົງຈອນ.

- ທັງສອງຫົວແມ່ນຢູ່ໃນຕາຂ່າຍໄຟຟ້າ 2.54 ມມດຽວກັນ, ເຊິ່ງເຮັດໃຫ້ການເຊື່ອມຕໍ່ກະດານນີ້ກັບສິ່ງອື່ນໆ, ເຊັ່ນ: ກະດານເຂົ້າຈີ່, ງ່າຍຂຶ້ນ. ທ່ານອາດຈະຕ້ອງການພິຈາລະນາການໃສ່ຫົວແຖວດຽວເທົ່ານັ້ນແທນທີ່ຈະເປັນຫົວແຖວສອງ, ການແຈກຢາຍກັບແຖວນອກຂອງການເຊື່ອມຕໍ່ພື້ນດິນ, ເພື່ອເຮັດໃຫ້ມັນສະດວກກວ່າທີ່ຈະເຫມາະກັບ breadboard.

ຮູບທີ 13. ພາກສ່ວນແຜນຜັງສະແດງສ່ວນຫົວ I/O 2.54mm ຂອງລຸ້ນ QFN80

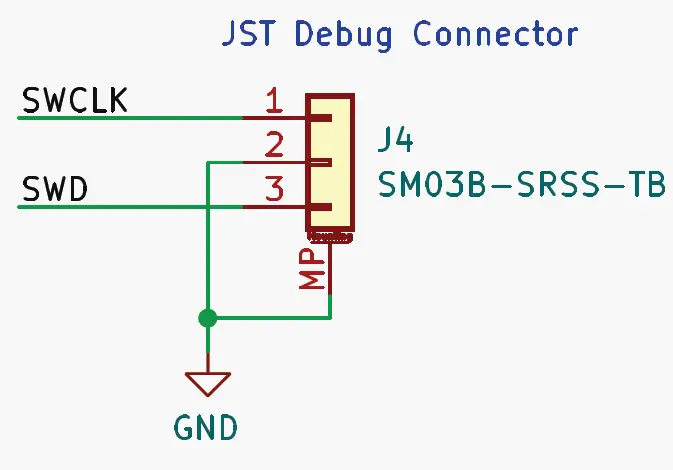

ຕົວເຊື່ອມຕໍ່ດີບັກ

ຮູບທີ 14. ພາກສ່ວນ Schematic ສະແດງຕົວເຊື່ອມຕໍ່ JST ທາງເລືອກສໍາລັບການດີບັກ SWD

ສໍາລັບການດີບັ໊ກເທິງຊິບ, ທ່ານອາດຈະຕ້ອງການເຊື່ອມຕໍ່ກັບການໂຕ້ຕອບ SWD ຂອງ RP2350. ສອງ pins, SWD ແລະ SWCLK, ມີຢູ່ໃນຫົວ 2.54mm, J3, ເພື່ອເຮັດໃຫ້ການສືບສວນການດີບັກທີ່ທ່ານເລືອກສາມາດເຊື່ອມຕໍ່ໄດ້ຢ່າງງ່າຍດາຍ. ນອກເຫນືອໄປຈາກນີ້, ຂ້າພະເຈົ້າໄດ້ລວມເອົາຫົວຂໍ້ JST ທາງເລືອກ, ເຊິ່ງຊ່ວຍໃຫ້ການເຊື່ອມຕໍ່ງ່າຍກັບ Raspberry Pi Debug Probe. ທ່ານບໍ່ຈໍາເປັນຕ້ອງໃຊ້ນີ້, ຫົວ 2.54mm ຈະພຽງພໍຖ້າຫາກວ່າທ່ານຕັ້ງໃຈທີ່ຈະ debug ຊອບແວ, ແຕ່ຂ້າພະເຈົ້າເຫັນວ່າມັນສະດວກກວ່າທີ່ຈະເຮັດແນວນັ້ນ. ຂ້ອຍໄດ້ເລືອກຕົວເຊື່ອມຕໍ່ຕາມແນວນອນ, ສ່ວນຫຼາຍແມ່ນຍ້ອນຂ້ອຍມັກຮູບລັກສະນະຂອງມັນ, ເຖິງແມ່ນວ່າມັນບໍ່ຢູ່ໃນຂອບຂອງກະດານ, ແຕ່ແນວຕັ້ງແມ່ນມີຢູ່, ເຖິງແມ່ນວ່າມີຮອຍຕີນທີ່ແຕກຕ່າງກັນເລັກນ້ອຍ.

ປຸ່ມ

ການອອກແບບ Minimal ໃນປັດຈຸບັນບໍ່ມີປຸ່ມຫນຶ່ງ, ແຕ່ມີສອງປຸ່ມ, ບ່ອນທີ່ຮຸ່ນ RP240 ບໍ່ມີ. ອັນຫນຶ່ງແມ່ນສໍາລັບການເລືອກ boot USB ດັ່ງທີ່ພວກເຮົາໄດ້ສົນທະນາກ່ອນຫນ້ານີ້, ແຕ່ທີສອງແມ່ນປຸ່ມ 'reset', ຕິດກັບ RUN pin. ທັງສອງອັນນີ້ບໍ່ມີຄວາມຈໍາເປັນຢ່າງເຂັ້ມງວດ (ເຖິງແມ່ນວ່າປຸ່ມ BOOTSEL ຈະຕ້ອງຖືກປ່ຽນແທນດ້ວຍຫົວຫຼືຄ້າຍຄືກັນຖ້າຕ້ອງການໂຫມດບູດ USB), ແລະສາມາດເອົາອອກໄດ້ຖ້າພື້ນທີ່ຫຼືຄ່າໃຊ້ຈ່າຍເປັນຄວາມກັງວົນ, ແຕ່ແນ່ນອນວ່າພວກເຂົາໃຊ້ RP2350 ໄກ. ປະສົບການທີ່ມີຄວາມສຸກຫຼາຍ.

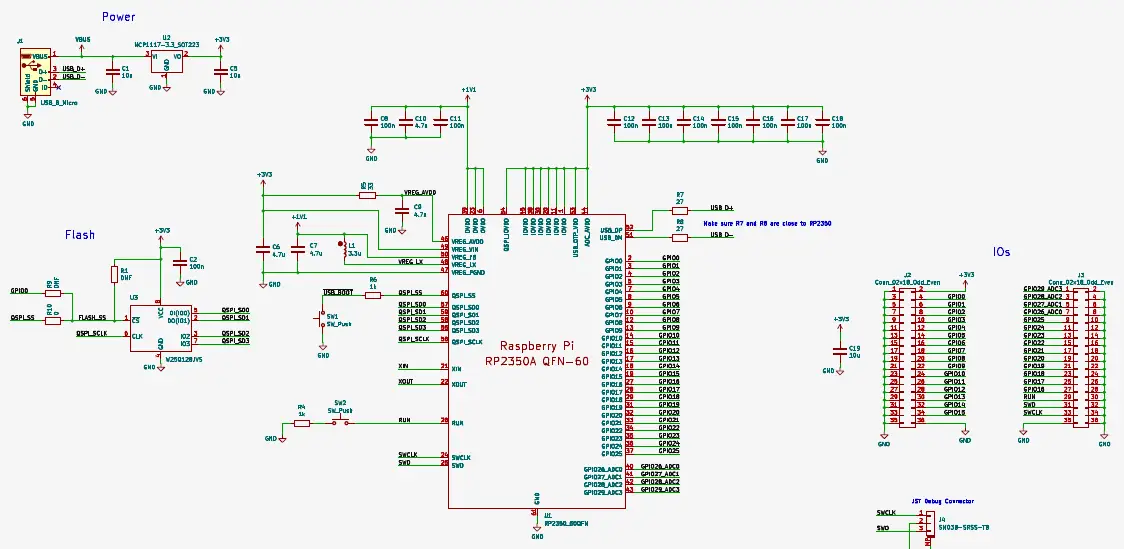

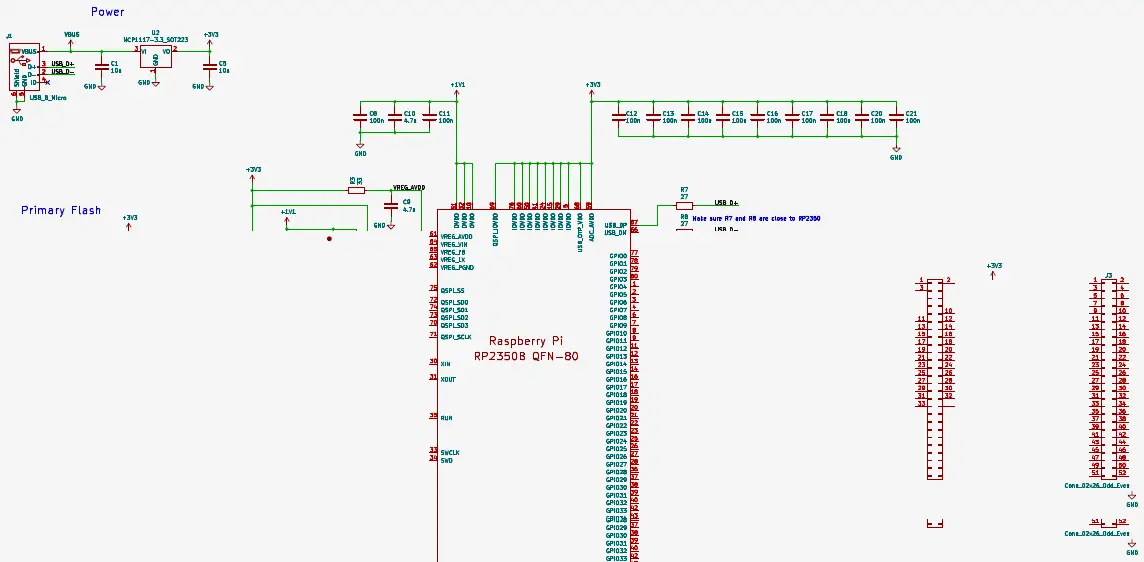

ເອກະສານຊ້ອນທ້າຍ A: ສະບັບ Schematic -RP2350A ສໍາເລັດ

ຮູບທີ 15. ແຜນຜັງອັນເຕັມທີ່ຂອງການອອກແບບໜ້ອຍສຸດສຳລັບ RP2350A

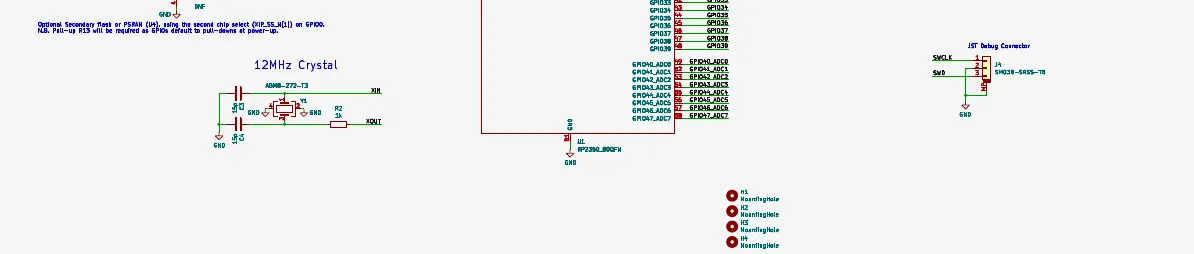

ເອກະສານຊ້ອນທ້າຍ B: ສະບັບສົມບູນ Schematic -RP2350B

ຮູບທີ 16. ແຜນຜັງອັນເຕັມທີ່ຂອງການອອກແບບໜ້ອຍສຸດສຳລັບ RP2350B

ເອກະສານຊ້ອນທ້າຍ H: ປະຫວັດການເຜີຍແຜ່ເອກະສານ

ວັນທີ 8 ສິງຫາ 2024

ການປ່ອຍຕົວໃນເບື້ອງຕົ້ນ.

ແລະ Raspberry Pi

Raspberry Pi ເປັນເຄື່ອງໝາຍການຄ້າຂອງ Raspberry Pi Ltd

Raspberry Pi Ltd

ເອກະສານ / ຊັບພະຍາກອນ

|

Raspberry Pi SC1631 Raspberry Microcontroller [pdf] ຄູ່ມືການສອນ SC1631 Raspberry Microcontroller, SC1631, Raspberry Microcontroller, Microcontroller |