intel Agilex Logic Array Blocks និង Adaptive Logic Modules

Intel® Agilex™ LAB និង ALM ជាងview

ប្លុកអារេតក្កវិជ្ជា (LAB) ត្រូវបានផ្សំឡើងពីប្លុកអគារមូលដ្ឋានដែលគេស្គាល់ថាជាម៉ូឌុលតក្កវិជ្ជាសម្របខ្លួន (ALMs)។ អ្នកអាចកំណត់រចនាសម្ព័ន្ធ LABs ដើម្បីអនុវត្តមុខងារតក្កវិជ្ជា អនុគមន៍នព្វន្ធ និងមុខងារចុះឈ្មោះ។

អ្នកអាចប្រើពាក់កណ្តាលនៃ LABs ដែលមាននៅក្នុងឧបករណ៍ Intel® Agilex™ ជា memory LABs (MLABs)។ ឧបករណ៍មួយចំនួនអាចមានសមាមាត្រ MLAB ខ្ពស់ជាង។

កម្មវិធី Intel Quartus® Prime និងឧបករណ៍សំយោគភាគីទីបីដែលគាំទ្រផ្សេងទៀតជ្រើសរើសរបៀបសមរម្យសម្រាប់មុខងារទូទៅដូចជា បញ្ជរ ធាតុបន្ថែម ដកដក និងមុខងារនព្វន្ធ។

ស្ថាបត្យកម្មស្នូល Intel Hyperflex™, ឧបករណ៍ Intel Agilex បានបញ្ចប់view

ផ្តល់ព័ត៌មានបន្ថែមអំពី Hyper-Registers និងស្ថាបត្យកម្មស្នូល Intel Hyperflex™។ Hyper-Registers គឺជាការចុះឈ្មោះបន្ថែមដែលមាននៅគ្រប់ផ្នែកបញ្ជូនផ្លូវអន្តរទំនាក់ទំនងទូទាំងក្រណាត់ស្នូល រួមទាំងផ្នែកនាំផ្លូវដែលតភ្ជាប់ទៅធាតុចូល និងលទ្ធផលរបស់ LAB ។

ចុះឈ្មោះ Intel Hyperflex™

គ្រួសារឧបករណ៍ Intel Agilex គឺផ្អែកលើស្ថាបត្យកម្មស្នូល Intel Hyperflex™។

Intel Agilex LAB មានការចុះឈ្មោះ Intel Hyperflex និងលក្ខណៈពិសេសផ្សេងទៀតដែលបានរចនាឡើងដើម្បីជួយសម្រួលដល់ការចូលនិវត្តន៍។ ការចុះឈ្មោះ Intel Hyperflex មាននៅក្នុង ALMs និងខ្សែសង្វាក់។ ដូចដែលបានបង្ហាញនៅក្នុងតួរលេខលម្អិតនៃការតភ្ជាប់ Intel Agilex ALM ការចុះឈ្មោះ Intel Hyperflex មានទីតាំងនៅលើសមកាលកម្មច្បាស់លាស់ ហើយនាឡិកាអាចឱ្យធាតុបញ្ចូលដើម្បីបង្កើន ឬកាត់បន្ថយការពន្យារពេលផ្លូវ។ រាល់ការចុះឈ្មោះ Intel Hyperflex អាចត្រូវបានបើក និងត្រូវបានគ្រប់គ្រងដោយកម្មវិធី Intel Quartus Prime កំឡុងពេលកំណត់ឡើងវិញ។

Intel Agilex LAB និង ALM ស្ថាបត្យកម្ម និងលក្ខណៈពិសេស

ផ្នែកខាងក្រោមពិពណ៌នាអំពី LAB និង ALM សម្រាប់ឧបករណ៍ Intel Agilex ។

មន្ទីរពិសោធន៍

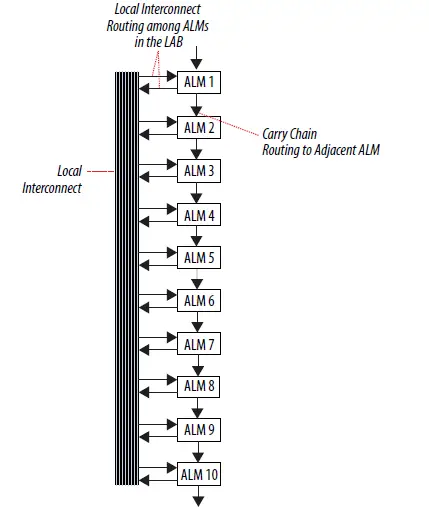

LABs គឺជាប្លុកតក្កវិជ្ជាដែលអាចកំណត់រចនាសម្ព័ន្ធបានដែលមានក្រុមនៃធនធានតក្កវិជ្ជា។ LAB នីមួយៗមានតក្កវិជ្ជាជាក់លាក់សម្រាប់សញ្ញាត្រួតពិនិត្យការបើកបរទៅកាន់ ALMs របស់វា។ MLAB គឺជា superset នៃ LAB ហើយរួមបញ្ចូលនូវមុខងារ LAB ទាំងអស់។ មាន ALMs សរុបចំនួន 10 នៅក្នុង LAB នីមួយៗ ដូចបានបង្ហាញក្នុងរូប Intel Agilex LAB និង MLAB Structure។

រូបភាពទី 1 ។

Intel Agilex LAB Structure និង Interconnects ជាងview

តួលេខនេះបង្ហាញពីការបញ្ចប់view នៃរចនាសម្ព័ន្ធ Intel Agilex LAB និង MLAB ជាមួយនឹង LAB interconnects ។

ព័ត៌មានពាក់ព័ន្ធ

ព័ត៌មានពាក់ព័ន្ធ

MLAB នៅទំព័រទី 6

MLAB

MLAB នីមួយៗគាំទ្រដល់អតិបរមា 640 ប៊ីតនៃ SRAM ច្រកពីរសាមញ្ញ។ អ្នកអាចកំណត់រចនាសម្ព័ន្ធ ALM នីមួយៗក្នុង MLAB ជាប្លុកអង្គចងចាំ 32 (ជម្រៅ) x 2 (ទទឹង) ដែលបណ្តាលឱ្យមានការកំណត់រចនាសម្ព័ន្ធនៃ 32 (ជម្រៅ) x 20 (ទទឹង) ប្លុក SRAM ពីរច្រកសាមញ្ញ។

រូបភាពទី 2 ។

រចនាសម្ព័ន្ធ Intel Agilex LAB និង MLAB តំណភ្ជាប់ក្នុងស្រុក និងដោយផ្ទាល់ តំណភ្ជាប់អន្តរកម្ម

តំណភ្ជាប់ក្នុងស្រុក និងដោយផ្ទាល់ តំណភ្ជាប់អន្តរកម្ម

LAB នីមួយៗអាចបញ្ចេញលទ្ធផល ALM 60 ។ សំណុំរងនៃទាំងនេះអាចជំរុញការបញ្ចូល LAB ដោយផ្ទាល់ ប៉ុន្តែការភ្ជាប់ណាមួយទៅជួរ ឬជួរឈរផ្សេងត្រូវតែប្រើខ្សែបញ្ជូនទិសដៅទូទៅយ៉ាងហោចណាស់មួយ។

ការតភ្ជាប់អន្តរមូលដ្ឋានជំរុញការបញ្ចូល ALM ។ លទ្ធផល ALM ក៏ដូចជាការភ្ជាប់គ្នារវាងជួរឈរ និងជួរដេកជំរុញឱ្យមានការភ្ជាប់គ្នាទៅវិញទៅមក។

រូបភាពទី 3 ។ Intel Agilex LAB Local និង Direct Link Interconnect  ភ្ជាប់ខ្សែសង្វាក់អន្តរកម្ម

ភ្ជាប់ខ្សែសង្វាក់អន្តរកម្ម

មានផ្លូវខ្សែសង្វាក់ដឹកជញ្ជូនជាក់លាក់មួយរវាង ALMs ។ ឧបករណ៍ Intel Agilex រួមបញ្ចូលនូវរចនាសម្ព័ន្ធទំនាក់ទំនងដែលប្រសើរឡើងនៅក្នុង LABs សម្រាប់ការបញ្ជូនបន្តខ្សែសង្វាក់សម្រាប់មុខងារនព្វន្ធប្រកបដោយប្រសិទ្ធភាព។ ការតភ្ជាប់ ALM-to-ALM ទាំងនេះឆ្លងកាត់ការភ្ជាប់អន្តរទំនាក់ទំនងក្នុងតំបន់។

ការចុះឈ្មោះរបស់ Intel Hyperflex ត្រូវបានបន្ថែមទៅខ្សែសង្វាក់ដឹកជញ្ជូន ដើម្បីឱ្យការពន្យាពេលដែលអាចបត់បែនបានតាមខ្សែសង្វាក់នៃ LABs ហើយ Intel Quartus Prime Compiler នឹងយក advan ដោយស្វ័យប្រវត្តិ។tage នៃធនធានទាំងនេះ ដើម្បីកែលម្អការប្រើប្រាស់ និងការអនុវត្ត។

រូបភាពទី 4 ។ ភ្ជាប់ខ្សែសង្វាក់អន្តរកម្ម សញ្ញាត្រួតពិនិត្យមន្ទីរពិសោធន៍

សញ្ញាត្រួតពិនិត្យមន្ទីរពិសោធន៍

មានប្រភពនាឡិកាពីរនៅក្នុងប្លុកត្រួតពិនិត្យ LAB នីមួយៗ ដែលបង្កើតនាឡិកា LAB ពីរ (LABCLK[1:0]) និងនាឡិកា LAB ដែលពន្យារពេលពីរ (LABCLK_Phi1[1:0]) ដើម្បីជំរុញការចុះឈ្មោះ ALM និង Hyper-Registers នៅក្នុង LAB ។ LAB គាំទ្រសញ្ញាបើកនាឡិកាតែមួយគត់ ក៏ដូចជាសញ្ញាច្បាស់លាស់បន្ថែមសម្រាប់ការចុះឈ្មោះ ALM ។

LAB row clock [5..0] និង LAB local interconnects បង្កើតសញ្ញាបញ្ជា LAB-wide ។ បណ្តាញនាឡិការលាក់ទាបចែកចាយសញ្ញាសកលទៅនាឡិកាជួរដេក [5..0]។ MultiTrack interconnect មានខ្សែបញ្ជូនបន្តដែលដំណើរការបានល្អបំផុតដែលមានប្រវែង និងល្បឿនខុសៗគ្នាដែលប្រើសម្រាប់ប្រសិទ្ធភាពនៃការបញ្ជូន។ Intel Quartus Prime Compiler បញ្ជូនផ្លូវរចនាសំខាន់ៗដោយស្វ័យប្រវត្តិ លើការភ្ជាប់ទំនាក់ទំនងគ្នាកាន់តែលឿន ដើម្បីបង្កើនប្រសិទ្ធភាពនៃការរចនា និងបង្កើនប្រសិទ្ធភាពធនធានឧបករណ៍។

ជម្រះការគ្រប់គ្រងតក្កវិជ្ជា

សញ្ញា LAB-wide គ្រប់គ្រងតក្កវិជ្ជាសម្រាប់សញ្ញាច្បាស់លាស់នៃការចុះឈ្មោះ ALM ។ ការចុះឈ្មោះ ALM គាំទ្រដោយផ្ទាល់ទាំងការធ្វើសមកាលកម្ម និងអសមកាលច្បាស់លាស់។ LAB នីមួយៗគាំទ្រសញ្ញាច្បាស់លាស់សមកាលកម្មមួយ និងសញ្ញាច្បាស់លាស់អសមកាលពីរ។

ឧបករណ៍ Intel Agilex ផ្តល់ម្ជុលកំណត់ឡើងវិញទូទាំងឧបករណ៍ (DEV_CLRn) ដែលកំណត់ឡើងវិញនូវការចុះឈ្មោះទាំងអស់នៅក្នុងឧបករណ៍។ អ្នកអាចបើកម្ជុល DEV_CLRn នៅក្នុងកម្មវិធី Intel Quartus Prime មុនពេលចងក្រង។ សញ្ញាកំណត់ឡើងវិញទូទាំងឧបករណ៍ បដិសេធរាល់សញ្ញាបញ្ជាផ្សេងទៀតទាំងអស់។

រូបភាពទី 5 ។ សញ្ញាត្រួតពិនិត្យ Intel Agilex LAB-Wide

ALM

ផ្នែកខាងក្រោមគ្របដណ្តប់ធនធាន ALM លទ្ធផល ALM និងរបៀបប្រតិបត្តិការ ALM ។

ធនធាន ALM

ALM នីមួយៗមានធនធានដែលមានមូលដ្ឋានលើ LUT ជាច្រើនដែលអាចបែងចែករវាង LUTs អាដាប់ធ័ររួមបញ្ចូលគ្នាពីរ (ALUTs) ដែលជាកម្មវិធីបន្ថែមចំនួនពីរប៊ីត និងការចុះឈ្មោះចំនួនបួន។

ជាមួយនឹងការបញ្ចូលរហូតដល់ទៅប្រាំបីសម្រាប់ ALUTs រួមបញ្ចូលគ្នាទាំងពីរ ALM មួយអាចអនុវត្តបន្សំផ្សេងៗនៃមុខងារពីរ។ អាដាប់ធ័រនេះអនុញ្ញាតឱ្យ ALM មានភាពឆបគ្នាទាំងស្រុងជាមួយនឹងស្ថាបត្យកម្ម LUT បញ្ចូលចំនួនបួន។ ALM មួយក៏អាចអនុវត្តសំណុំរងនៃមុខងារបញ្ចូលចំនួនប្រាំបីផងដែរ។

មួយ ALM មានការចុះឈ្មោះកម្មវិធីចំនួនបួន។ ការចុះឈ្មោះនីមួយៗមានច្រកដូចខាងក្រោមៈ

- ទិន្នន័យនៅក្នុង

- ទិន្នន័យចេញ

- នាឡិកា LAB ធម្មតា។

- នាឡិកា LAB ពន្យារពេល

- បើកនាឡិកា

- សមកាលកម្មច្បាស់លាស់

- អសមកាលច្បាស់លាស់

សញ្ញាសកល ម្ជុល I/O (GPIO) គោលបំណងទូទៅ ឬតក្កវិជ្ជាខាងក្នុងណាមួយអាចជំរុញនាឡិកាបើកសញ្ញា នាឡិកា និងសញ្ញាត្រួតពិនិត្យច្បាស់លាស់អសមកាល ឬសមកាលកម្មនៃការចុះឈ្មោះ ALM ។ សញ្ញាបើកនាឡិកាមានអាទិភាពលើសញ្ញាកំណត់ឡើងវិញសមកាលកម្ម។

សម្រាប់មុខងារផ្សំ ការចុះឈ្មោះត្រូវបានឆ្លងកាត់ ហើយលទ្ធផលនៃតារាងរកមើល (LUT) និងកម្មវិធីបន្ថែមជំរុញដោយផ្ទាល់ទៅលទ្ធផលនៃ ALM ។ ទិន្នផលលឿនពីរគឺអាចរកបានសម្រាប់លទ្ធផល 6 LUT និងលទ្ធផលខាងក្រោម 5 LUT ដើម្បីឆ្លងកាត់ mux លទ្ធផល ហើយភ្ជាប់ទៅ LAB ផ្សេងទៀតសម្រាប់ការកែតម្រូវផ្លូវសំខាន់។

រូបភាពទី 6 ។ ដ្យាក្រាមប្លុកកម្រិតខ្ពស់ Intel Agilex ALM

លទ្ធផល ALM

លទ្ធផល ALM

លទ្ធផលផ្លូវទូទៅនៅក្នុង ALM នីមួយៗជំរុញធនធានកំណត់ផ្លូវមូលដ្ឋាន ជួរដេក និងជួរឈរ។ លទ្ធផល ALM ចំនួនប្រាំមួយ រួមទាំងផ្លូវទិន្នផលលឿនចំនួនពីរ អាចជំរុញការភ្ជាប់ជួរឈរ ជួរដេក ឬការតភ្ជាប់ផ្លូវដោយផ្ទាល់។

លទ្ធផល LUT កម្មវិធីបន្ថែម ឬចុះឈ្មោះអាចជំរុញលទ្ធផល ALM ។ ទាំង LUT ឬ adder និងការចុះឈ្មោះ ALM អាចបណ្តេញចេញពី ALM ក្នុងពេលដំណាលគ្នា។

ការចុះឈ្មោះវេចខ្ចប់ធ្វើអោយប្រសើរឡើងនូវការប្រើប្រាស់ឧបករណ៍ដោយអនុញ្ញាតឱ្យការចុះឈ្មោះដែលមិនពាក់ព័ន្ធ និងតក្កវិជ្ជារួមបញ្ចូលគ្នាត្រូវបានខ្ចប់ទៅក្នុង ALM តែមួយ។ ALM ក៏អាចបណ្តេញចេញនូវកំណែដែលបានចុះឈ្មោះ និងមិនបានចុះឈ្មោះនៃ LUT ឬលទ្ធផលបន្ថែម។

តួលេខខាងក្រោមបង្ហាញពីការតភ្ជាប់ Intel Agilex ALM ។ នៅក្នុង Intel Quartus Prime Resource Property Editor ការតភ្ជាប់ ALM ទាំងមូលត្រូវបានធ្វើឱ្យសាមញ្ញ។ ផ្លូវមួយចំនួននឹងត្រូវបានបញ្ជូននៅខាងក្នុងដោយកម្មវិធី Intel Quartus Prime ។

រូបភាពទី 7 ។ ព័ត៌មានលម្អិតអំពីការតភ្ជាប់ Intel Agilex ALM របៀបប្រតិបត្តិការ ALM

របៀបប្រតិបត្តិការ ALM

Intel Agilex ALM ដំណើរការក្នុងរបៀបណាមួយខាងក្រោម៖

- របៀបធម្មតា។

- របៀប LUT បន្ថែម

- របៀបនព្វន្ធ

របៀបធម្មតា។

របៀបធម្មតាអនុញ្ញាតឱ្យមុខងារពីរត្រូវបានអនុវត្តនៅក្នុង Intel Agilex ALM មួយ ឬមុខងារតែមួយរហូតដល់ប្រាំមួយបញ្ចូល។

ការបញ្ចូលទិន្នន័យរហូតដល់ប្រាំបីពី LAB local interconnect គឺជាការបញ្ចូលទៅក្នុងតក្កវិជ្ជារួមបញ្ចូលគ្នា។

ALM អាចគាំទ្រការបន្សំជាក់លាក់នៃមុខងារឯករាជ្យទាំងស្រុង និងបន្សំផ្សេងៗនៃមុខងារដែលមានធាតុចូលរួម។

Intel Quartus Prime Compiler ជ្រើសរើសធាតុបញ្ចូលទៅ LUT ដោយស្វ័យប្រវត្តិ។ ALMs នៅក្នុងរបៀបធម្មតាគាំទ្រការចុះឈ្មោះវេចខ្ចប់។

រូបខាងក្រោមបង្ហាញពីការរួមបញ្ចូលគ្នានៃការតភ្ជាប់បញ្ចូលផ្សេងគ្នាសម្រាប់របៀប LUT ។ នៅក្នុងការរចនារបស់អ្នក កម្មវិធី Intel Quartus Prime អាចកំណត់ឈ្មោះបញ្ចូលផ្សេងៗគ្នា កំឡុងពេលចងក្រង។

រូបភាពទី 8 ។ ALM នៅក្នុងរបៀបធម្មតា។

ការរួមបញ្ចូលគ្នានៃមុខងារដែលមានធាតុបញ្ចូលតិចជាងអ្វីដែលបានបង្ហាញក៏ត្រូវបានគាំទ្រផងដែរ។ សម្រាប់អតីតampដូច្នេះ ការរួមបញ្ចូលគ្នានៃអនុគមន៍ដែលមានចំនួនធាតុបញ្ចូលខាងក្រោមត្រូវបានគាំទ្រ។

- 4 និង 3

- 3 និង 3

- 3 និង 2

- 5 និង 2

សម្រាប់ការវេចខ្ចប់អនុគមន៍ 5-input ពីរទៅក្នុង ALM មួយ មុខងារត្រូវតែមានធាតុបញ្ចូលទូទៅយ៉ាងហោចណាស់ពីរ។ ការបញ្ចូលទូទៅគឺ dataa និង datab ។ ការរួមបញ្ចូលគ្នានៃអនុគមន៍បញ្ចូល 4 ជាមួយមុខងារបញ្ចូល 5 ទាមទារការបញ្ចូលទូទៅមួយ (ទាំង dataa ឬ datab) ។

នៅក្នុងឧបករណ៍ដែលប្រើប្រាស់តិចតួច មុខងារដែលអាចដាក់ក្នុង ALM មួយអាចត្រូវបានអនុវត្តនៅក្នុង ALMs ដាច់ដោយឡែកពីគ្នាដោយកម្មវិធី Intel Quartus Prime ដើម្បីសម្រេចបាននូវដំណើរការល្អបំផុត។ នៅពេលដែលឧបករណ៍ចាប់ផ្តើមបំពេញកម្មវិធី Intel Quartus Prime ប្រើប្រាស់សក្តានុពលពេញលេញនៃ Intel Agilex ALM ដោយស្វ័យប្រវត្តិ។ Intel Quartus Prime Compiler ស្វែងរកមុខងារដោយស្វ័យប្រវត្តិដោយប្រើធាតុបញ្ចូលទូទៅ ឬមុខងារឯករាជ្យទាំងស្រុងដែលត្រូវដាក់ក្នុង ALM តែមួយ ដើម្បីប្រើប្រាស់ធនធានឧបករណ៍ប្រកបដោយប្រសិទ្ធភាព។ លើសពីនេះទៀត អ្នកអាចគ្រប់គ្រងការប្រើប្រាស់ធនធានដោយដៃដោយកំណត់ការចាត់តាំងទីតាំង។

រូបភាពទី 9 ។ 6- បញ្ចូលមុខងារ LUT Mode ក្នុងរបៀបធម្មតា។

រូបភាពទី 10 ។ 3- បញ្ចូលមុខងារ LUT Mode ក្នុងរបៀបធម្មតា។

រូបភាពទី 10 ។ 3- បញ្ចូលមុខងារ LUT Mode ក្នុងរបៀបធម្មតា។

ទិន្នន័យ និងទិន្នន័យ ខ អាចរកបានសម្រាប់ការចុះឈ្មោះវេចខ្ចប់។  អ្នកអាចអនុវត្តមុខងារបញ្ចូលពីបីទៅប្រាំមួយដោយប្រើធាតុបញ្ចូលខាងក្រោម៖

អ្នកអាចអនុវត្តមុខងារបញ្ចូលពីបីទៅប្រាំមួយដោយប្រើធាតុបញ្ចូលខាងក្រោម៖

- ទិន្នន័យ

- datad0

- datac0

- datac1

- datad1

- ទិន្នន័យ

- dataa និង datab—ដែល dataa និង datab ត្រូវបានចែករំលែកនៅទូទាំង LUTs ទាំងពីរ ដើម្បីផ្តល់នូវភាពបត់បែនក្នុងការអនុវត្តមុខងារផ្សេងគ្នានៅក្នុង LUT នីមួយៗ។

ទាំង dataa និង datab inputs គាំទ្រមុខងារ register packing ។ ប្រសិនបើអ្នកបើកដំណើរការមុខងារវេចខ្ចប់ចុះឈ្មោះ ទាំងការបញ្ចូល dataa និង datab ឬធាតុបញ្ចូលណាមួយរំលង LUT ហើយបញ្ចូលដោយផ្ទាល់ទៅក្នុងបញ្ជី អាស្រ័យលើរបៀបចុះឈ្មោះដែលបានប្រើ។ សម្រាប់ឧបករណ៍ Intel Agilex ប្រភេទនៃការចុះឈ្មោះកញ្ចប់ខាងក្រោមត្រូវបានគាំទ្រ៖

- 5- បញ្ចូល LUT ជាមួយនឹងផ្លូវចុះឈ្មោះ 1 កញ្ចប់

- 5- បញ្ចូល LUT ជាមួយ 2 ផ្លូវចុះឈ្មោះ packed

- LUTs 3-input ចំនួនពីរដែលមានផ្លូវចុះឈ្មោះ 2 packed

LUT 3-input ជាមួយនឹង 2 packed register paths ត្រូវបានបង្ហាញនៅក្នុងមុខងារ 3-Input LUT Mode នៅក្នុងរូប Normal Mode។ សម្រាប់ឧបករណ៍ Intel Agilex របៀប 6-input LUT មិនគាំទ្រមុខងារវេចខ្ចប់ចុះឈ្មោះទេ។

របៀប LUT បន្ថែម

រូបភាពទី 11. អនុគមន៍បញ្ចូល 8 ដែលគាំទ្រនៅក្នុងរបៀប LUT ដែលបានពង្រីក

មុខងារបញ្ចូល 8 ជាក់លាក់អាចត្រូវបានអនុវត្តនៅក្នុង ALM តែមួយដោយប្រើធាតុបញ្ចូល LUT ទាំងអស់៖

- ទិន្នន័យ

- datad0

- datac0

- ទិន្នន័យ

- ទិន្នន័យ

- datac1

- datad1

- ទិន្នន័យ

នៅក្នុងរបៀប LUT ដែលបានពង្រីក 8-input, របៀបចុះឈ្មោះដែលបានវេចខ្ចប់ត្រូវបានគាំទ្រ ផ្តល់ថាការចុះឈ្មោះដែលបានវេចខ្ចប់ចែករំលែក dataa ឬ datab input ជាមួយ 8-input LUT។

របៀបនព្វន្ធ

ALM នៅក្នុងរបៀបនព្វន្ធប្រើពីរសំណុំនៃ LUTs 4-input ចំនួនពីរ រួមជាមួយនឹង adders ពេញលេញចំនួនពីរ។ កម្មវិធីបន្ថែមដែលខិតខំប្រឹងប្រែងអនុញ្ញាតឱ្យ LUTs អនុវត្តតក្កវិជ្ជាបន្ថែមជាមុន។ ដូច្នេះ អ្នកបន្ថែមនីមួយៗអាចបន្ថែមលទ្ធផលនៃមុខងារបញ្ចូល 4 ពីរ។

របៀបនព្វន្ធក៏ផ្តល់នូវការបើកនាឡិកា បើកដំណើរការរាប់ ការគ្រប់គ្រងការឡើងលើចុះក្រោម ធ្វើសមកាលកម្ម បន្ថែម និងដកការគ្រប់គ្រង និងសមកាលកម្មច្បាស់លាស់។

ជម្រើសបើកឱ្យច្បាស់ និងនាឡិកាគឺជាសញ្ញាទូទាំង LAB ដែលប៉ះពាល់ដល់ការចុះឈ្មោះទាំងអស់ក្នុង LAB ។ អ្នកអាចបិទជាលក្ខណៈបុគ្គល ឬបើកសញ្ញាទាំងនេះសម្រាប់ការចុះឈ្មោះគូនីមួយៗនៅក្នុង LUT (ALUT) ដែលអាចសម្របបាន។ កម្មវិធី Intel Quartus Prime ដាក់ការចុះឈ្មោះណាមួយដែលមិនត្រូវបានប្រើប្រាស់ដោយបញ្ជរចូលទៅក្នុង LABs ផ្សេងទៀត។

រូបភាពទី 12 ។ Intel Agilex ALM នៅក្នុងរបៀបនព្វន្ធ

ខ្សែសង្វាក់

ខ្សែសង្វាក់

ខ្សែសង្វាក់ដឹកជញ្ជូនផ្តល់នូវមុខងារដឹកជញ្ជូនលឿនរវាងឧបករណ៍បន្ថែមដែលខិតខំប្រឹងប្រែងនៅក្នុងរបៀបនព្វន្ធ។

មុខងារជ្រើសរើស 2 ប៊ីតនៅក្នុងឧបករណ៍ Intel Agilex បំបែកការពន្យារការផ្សព្វផ្សាយរបស់ខ្សែសង្វាក់ដឹកជញ្ជូនជាមួយ ALM ។ Carry chains អាចចាប់ផ្តើមនៅក្នុង ALM ដំបូង ឬ ALM ទីប្រាំមួយនៅក្នុង LAB មួយ។ សញ្ញាបញ្ជូនចេញចុងក្រោយត្រូវបានបញ្ជូនទៅកាន់ ALM ដែលជាកន្លែងដែលវាត្រូវបានបញ្ចូលទៅក្នុងតំបន់ ជួរដេក ឬជួរឈរ។

ប្រវត្តិនៃការកែប្រែឯកសារសម្រាប់ប្លុកអារេតក្កវិជ្ជា Intel Agilex និង មគ្គុទ្ទេសក៍អ្នកប្រើប្រាស់ម៉ូឌុលតក្កវិជ្ជាសម្របខ្លួន

| កំណែឯកសារ | ការផ្លាស់ប្តូរ |

| 2022.05.24 | រូបភាពដែលបានធ្វើបច្ចុប្បន្នភាព៖ ដ្យាក្រាមប្លុកកម្រិតខ្ពស់ Intel Agilex ALM ។ |

| 2019.11.14 | បានធ្វើបច្ចុប្បន្នភាពការពិពណ៌នានៅក្នុងផ្នែក LAB Control Signals ។ |

| 2019.10.01 |

|

| 2019.04.02 | ការចេញផ្សាយដំបូង។ |

សាជីវកម្ម Intel ។

រក្សារសិទ្ធគ្រប់យ៉ាង។ Intel, និមិត្តសញ្ញា Intel និងសញ្ញា Intel ផ្សេងទៀតគឺជាពាណិជ្ជសញ្ញារបស់ Intel Corporation ឬក្រុមហ៊ុនបុត្រសម្ព័ន្ធរបស់ខ្លួន។ Intel ធានាការអនុវត្តផលិតផល FPGA និង semiconductor របស់ខ្លួនទៅនឹងលក្ខណៈបច្ចេកទេសបច្ចុប្បន្នស្របតាមការធានាស្តង់ដាររបស់ Intel ប៉ុន្តែរក្សាសិទ្ធិក្នុងការផ្លាស់ប្តូរផលិតផល និងសេវាកម្មណាមួយនៅពេលណាមួយដោយមិនមានការជូនដំណឹងជាមុន។ Intel សន្មត់ថាគ្មានទំនួលខុសត្រូវ ឬការទទួលខុសត្រូវដែលកើតចេញពីកម្មវិធី ឬការប្រើប្រាស់ព័ត៌មាន ផលិតផល ឬសេវាកម្មណាមួយដែលបានពិពណ៌នានៅទីនេះ លើកលែងតែមានការយល់ព្រមជាលាយលក្ខណ៍អក្សរដោយ Intel ។ អតិថិជនរបស់ Intel ត្រូវបានណែនាំឱ្យទទួលបានកំណែចុងក្រោយបំផុតនៃលក្ខណៈបច្ចេកទេសឧបករណ៍ មុនពេលពឹងផ្អែកលើព័ត៌មានដែលបានបោះពុម្ពផ្សាយណាមួយ និងមុនពេលធ្វើការបញ្ជាទិញផលិតផល ឬសេវាកម្ម។

*ឈ្មោះ និងម៉ាកផ្សេងទៀតអាចត្រូវបានទាមទារជាកម្មសិទ្ធិរបស់អ្នកដទៃ។

អាយអេសអូ

១៦:៩

បានចុះឈ្មោះ

ឯកសារ/ធនធាន

|

intel Agilex Logic Array Blocks និង Adaptive Logic Modules [pdf] ការណែនាំអ្នកប្រើប្រាស់ Agilex Logic Array Blocks និង Adaptive Logic Modules, Agilex, Logic Array Blocks និង Adaptive Logic Modules, Array Blocks និង Adaptive Logic Modules, Adaptive Logic Modules, ម៉ូឌុលតក្កវិជ្ជា |