Mikrokontroler Raspberry Pi SC1631

Spesifikasi Produk

- Model: RP2350

- Paket: QFN-60

- Penyimpanan Flash Internal: Tidak

- Jil.tage Regulator: Pengatur peralihan pada chip

- Pin Regulator: 5 (input 3.3V, output 1.1V, VREG_AVDD, VREG_LX, VREG_PGND)

Petunjuk Penggunaan Produk

- Bab 1 PENDAHULUAN

- Seri RP2350 menawarkan opsi paket yang berbeda dibandingkan dengan seri RP2040. RP2350A dan RP2354A hadir dalam paket QFN-60 tanpa dan dengan penyimpanan flash internal, sedangkan RP2354B dan RP2350B hadir dalam paket QFN-80 dengan dan tanpa penyimpanan flash.

- Bab 2: Kekuatan

Seri RP2350 dilengkapi dengan sakelar vol on-chip barutage regulator dengan lima pin. Regulator ini memerlukan komponen eksternal untuk pengoperasian tetapi menawarkan efisiensi daya yang lebih tinggi pada arus beban yang lebih tinggi dibandingkan dengan regulator linier dalam seri RP2040. Perhatikan sensitivitas noise pada pin VREG_AVDD yang memasok sirkuit analog.

Pertanyaan yang Sering Diajukan (FAQ)

- T: Apa perbedaan utama antara RP2350A dan RP2350B?

J: Perbedaan utamanya terletak pada keberadaan penyimpanan flash internal. RP2350A tidak memiliki penyimpanan flash internal, sedangkan RP2350B memilikinya. - T: Berapa banyak pin yang dimiliki voltage regulator di seri RP2350 punya?

A: VolumetagRegulator e dalam seri RP2350 memiliki lima pin.

Desain perangkat keras dengan RP2350 Menggunakan mikrokontroler RP2350 untuk membangun papan dan produk

Tanda penerbit

- Hak cipta © 2023-2024 Raspberry Pi Ltd.

- Dokumentasi ini dilisensikan di bawah Lisensi Creative Commons Atribusi-Tanpa-Turunan 4.0 Internasional (CC BY-ND). tanggal pembuatan: 2024-08-08 versi pembuatan: c0acc5b-bersih

- Pemberitahuan penafian hukum

- DATA TEKNIS DAN KEANDALAN UNTUK PRODUK RASPBERRY PI (TERMASUK LEMBAR DATA) SEBAGAIMANA YANG DIUBAH DARI WAKTU KE WAKTU (“SUMBER”) DISEDIAKAN OLEH RASPBERRY PI LTD (“RPL”) “SEBAGAIMANA ADANYA” DAN SETIAP JAMINAN TERSURAT MAUPUN TERSIRAT, TERMASUK, NAMUN TIDAK TERBATAS PADA, JAMINAN TERSIRAT ATAS KEMAMPUAN UNTUK DIPERDAGANGKAN DAN KESESUAIAN UNTUK TUJUAN TERTENTU DISANGKAL. HINGGA BATAS MAKSIMUM YANG DIIZINKAN OLEH HUKUM YANG BERLAKU, DALAM KEADAAN APA PUN RPL TIDAK AKAN BERTANGGUNG JAWAB ATAS SEGALA KERUGIAN LANGSUNG, TIDAK LANGSUNG, INSIDENTAL, KHUSUS, TELADAN, ATAU KONSEKUENSIAL (TERMASUK, NAMUN TIDAK TERBATAS PADA, PENGADAAN BARANG ATAU JASA PENGGANTI; HILANGNYA PENGGUNAAN, DATA, ATAU KEUNTUNGAN; ATAU GANGGUAN BISNIS) BAGAIMANA PUN PENYEBABNYA DAN PADA SEGALA TEORI TANGGUNG JAWAB, BAIK DALAM KONTRAK, TANGGUNG JAWAB MUTLAK, ATAU TINDAKAN MELAWAN HUKUM (TERMASUK KELALAIAN ATAU LAINNYA) YANG TIMBUL DALAM CARA APA PUN DARI PENGGUNAAN SUMBER DAYA, BAHKAN JIKA TELAH DIBERITAHUKAN TENTANG KEMUNGKINAN KERUGIAN TERSEBUT.

- RPL berhak melakukan penyempurnaan, perbaikan, koreksi atau modifikasi lain apa pun terhadap SUMBER DAYA atau produk apa pun yang dijelaskan di dalamnya kapan saja dan tanpa pemberitahuan lebih lanjut.

SUMBER DAYA ditujukan untuk pengguna terampil dengan tingkat pengetahuan desain yang sesuai. Pengguna bertanggung jawab penuh atas pemilihan dan penggunaan SUMBER DAYA dan setiap penerapan produk yang dijelaskan di dalamnya. Pengguna setuju untuk mengganti rugi dan membebaskan RPL dari semua kewajiban, biaya, kerusakan, atau kerugian lain yang timbul akibat penggunaan SUMBER DAYA. - RPL memberikan izin kepada pengguna untuk menggunakan SUMBER DAYA hanya jika digunakan bersama dengan produk Raspberry Pi. Semua penggunaan SUMBER DAYA lainnya dilarang. Tidak ada lisensi yang diberikan kepada RPL lain atau hak kekayaan intelektual pihak ketiga lainnya.

- AKTIVITAS BERISIKO TINGGI. Produk Raspberry Pi tidak dirancang, diproduksi, atau ditujukan untuk digunakan di lingkungan berbahaya yang memerlukan kinerja yang aman, seperti dalam pengoperasian fasilitas nuklir, sistem navigasi atau komunikasi pesawat, kontrol lalu lintas udara, sistem persenjataan, atau aplikasi yang sangat penting bagi keselamatan (termasuk sistem pendukung kehidupan dan perangkat medis lainnya), yang mana kegagalan produk dapat mengakibatkan kematian, cedera pribadi, atau kerusakan fisik atau lingkungan yang parah ("Aktivitas Berisiko Tinggi"). RPL secara khusus menolak jaminan tersurat maupun tersirat atas kesesuaian untuk Aktivitas Berisiko Tinggi dan tidak bertanggung jawab atas penggunaan atau penyertaan produk Raspberry Pi dalam Aktivitas Berisiko Tinggi.

- Produk Raspberry Pi disediakan sesuai dengan Ketentuan Standar RPL. Penyediaan SUMBER DAYA oleh RPL tidak memperluas atau mengubah Ketentuan Standar RPL, termasuk namun tidak terbatas pada pernyataan dan jaminan yang dinyatakan di dalamnya.

Bab 1 PENDAHULUAN

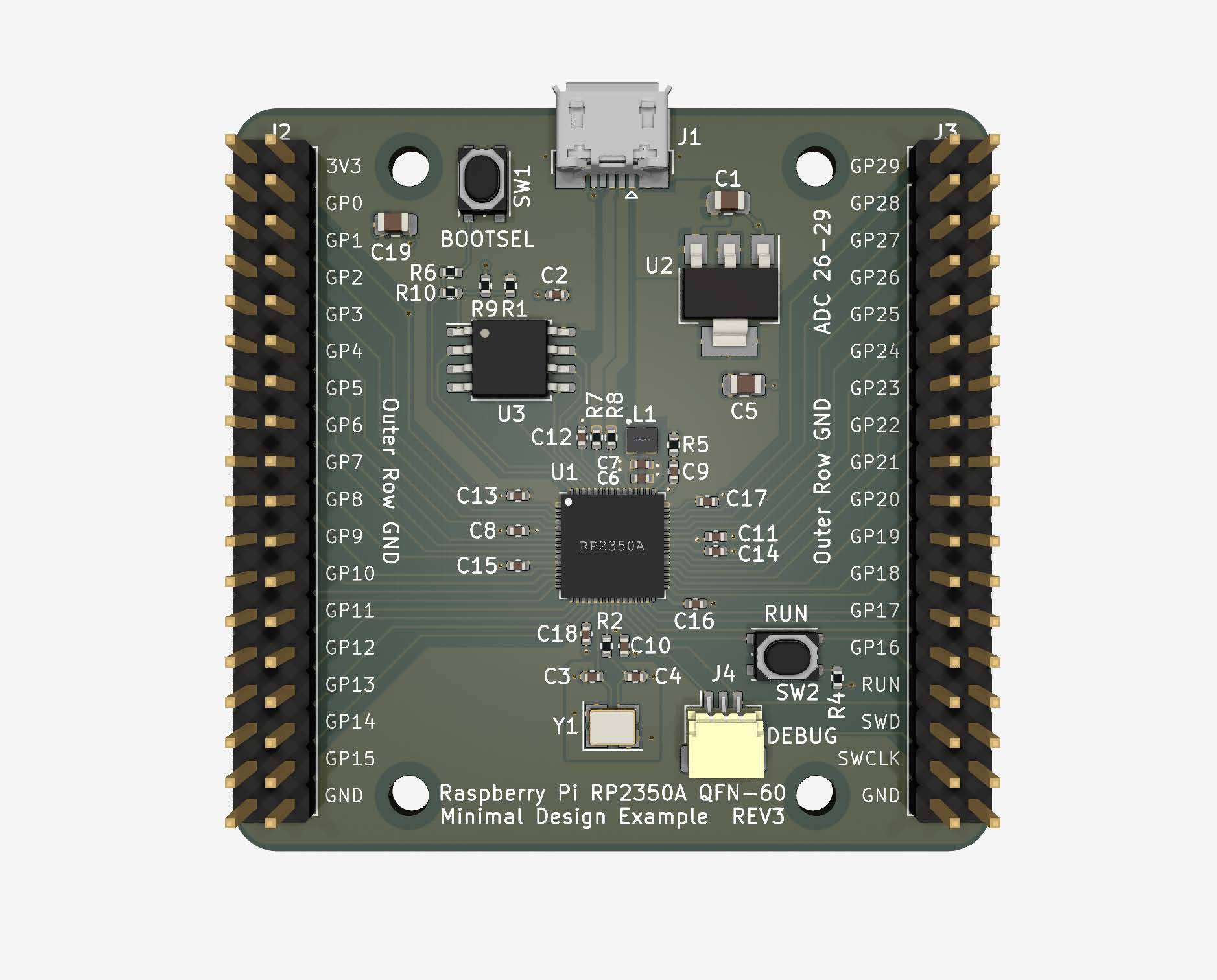

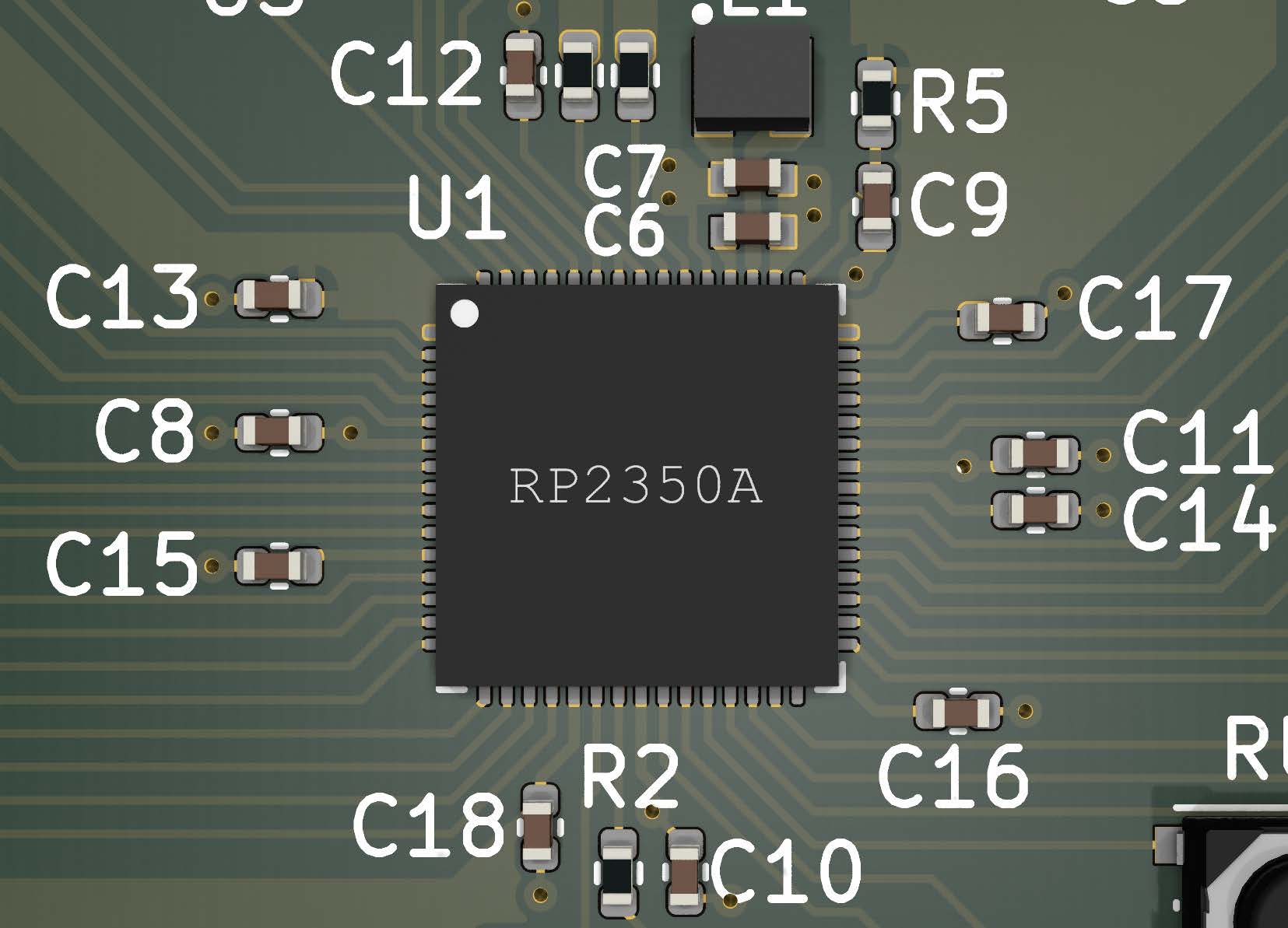

Gambar 1. Rendering 3D KiCad dari desain Minimal RP2350Aample

Saat pertama kali memperkenalkan Raspberry Pi RP2040, kami juga merilis desain 'Minimal'ample dan panduan pendamping Desain perangkat keras dengan RP2040 yang diharapkan menjelaskan bagaimana RP2040 dapat digunakan dalam papan sirkuit sederhana, dan mengapa berbagai pilihan komponen dibuat. Dengan hadirnya seri RP235x, saatnya meninjau kembali desain Minimal RP2040 asli, dan memperbaruinya untuk memperhitungkan fitur-fitur baru, dan juga untuk setiap varian paket; RP2350A dengan paket QFN-60, dan RP2350B yang merupakan QFN-80. Sekali lagi, desain ini dalam format Kicad (7.0), dan tersedia untuk diunduh (https://datasheets.raspberrypi.com/rp2350/Minimal-KiCAD.zip).

Papan Minimal

Papan Minimal asli merupakan upaya untuk menyediakan desain referensi sederhana, menggunakan komponen eksternal minimum yang diperlukan untuk menjalankan RP2040 dan tetap memiliki semua IO yang terbuka dan dapat diakses. Ini pada dasarnya terdiri dari sumber daya (regulator linier 5V hingga 3.3V), osilator kristal, memori flash, dan koneksi IO (soket micro USB dan header GPIO). Papan Minimal seri RP235x yang baru sebagian besar sama, tetapi dengan beberapa perubahan yang diperlukan karena perangkat keras baru. Selain itu, dan meskipun agak bertentangan dengan sifat desain minimal, saya telah menambahkan beberapa tombol untuk bootsel dan run, bersama dengan header SWD terpisah, yang seharusnya berarti pengalaman debug yang sama sekali tidak membuat frustrasi kali ini. Desain tidak secara tegas membutuhkan tombol-tombol ini, sinyal masih tersedia pada header, dan dapat dihilangkan jika Anda sangat memperhatikan biaya atau ruang, atau memiliki kecenderungan masokis.

Seri RP2040 vs RP235x

Perubahan yang paling jelas terlihat adalah pada paketnya. Sementara RP2040 adalah QFN-7 7x56mm, seri RP235x saat ini memiliki empat anggota yang berbeda. Ada dua perangkat yang berbagi paket QFN-60 yang sama; RP2350A yang tidak berisi penyimpanan flash internal, dan RP2354A yang memilikinya. Demikian pula, QFN-80 juga hadir dalam dua jenis; RP2354B dengan flash, dan RP2350B tanpa flash. Perangkat QFN-60 dan RP2040 asli berbagi warisan yang samatage.

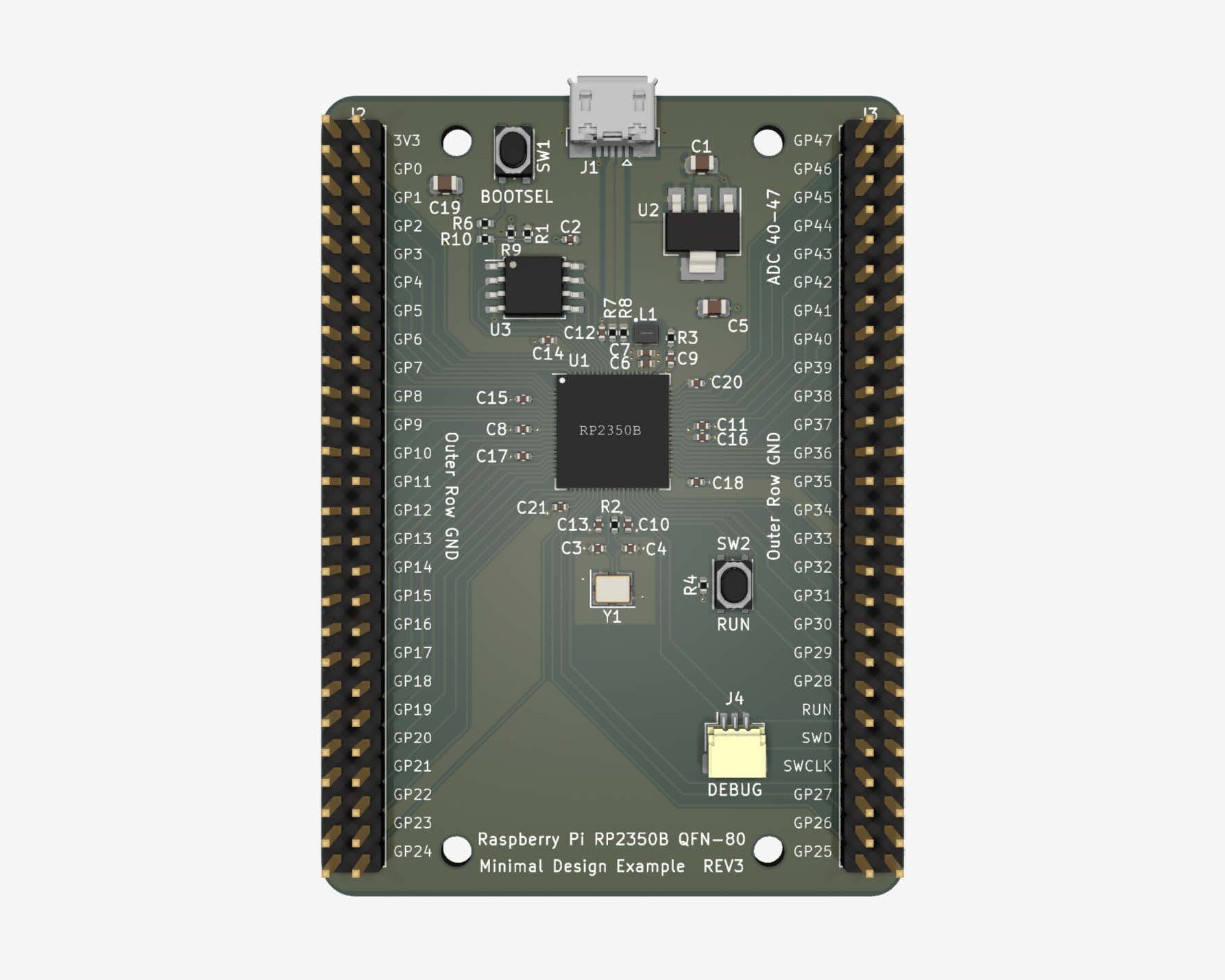

Masing-masing memiliki 30 GPIO, empat di antaranya juga terhubung ke ADC, dan berukuran 7x7mm. Meskipun demikian, RP2350A bukanlah pengganti langsung untuk RP2040, karena jumlah pin pada masing-masing berbeda. Sebaliknya, chip QFN-80 sekarang memiliki 48 GPIO, dan delapan di antaranya sekarang mampu ADC. Karena itu, sekarang kita memiliki dua papan Minimal; satu untuk perangkat 60 pin, dan satu untuk 80. Papan Minimal ini terutama dirancang untuk komponen tanpa flash internal (RP2350), namun desainnya dapat dengan mudah digunakan dengan perangkat flash internal (RP2354) hanya dengan menghilangkan memori flash onboard, atau bahkan menggunakannya sebagai perangkat flash sekunder (lebih lanjut tentang ini nanti). Ada sedikit perbedaan antara kedua papan, selain fakta bahwa versi QFN-80 memiliki baris header yang lebih panjang untuk mengakomodasi GPIO tambahan, dan papannya karenanya lebih besar.

Selain paketnya, perbedaan terbesar antara seri RP235x dan RP2040 adalah catu daya. Seri RP235x memiliki beberapa pin daya baru, dan regulator internal yang berbeda. Regulator linier 100mA dari RP2040 telah diganti dengan regulator switching 200mA, dan karenanya, memerlukan beberapa sirkuit yang sangat spesifik, dan tata letak yang tidak terlalu teliti. Sangat disarankan agar Anda mengikuti tata letak dan pilihan komponen kami dengan saksama; kami telah melalui kesulitan karena harus membuat beberapa iterasi desain, jadi semoga Anda tidak perlu melakukannya.

Gambar 2. Rendering 3D KiCad dari desain Minimal RP2350Bample

Desain

Tujuan dari desain Minimal examples adalah membuat sepasang papan sederhana menggunakan seri RP235x, yang seharusnya dapat diproduksi dengan murah dan mudah, tanpa menggunakan teknologi PCB yang tidak perlu eksotis. Oleh karena itu, papan Minimal adalah desain 2 lapis, menggunakan komponen yang seharusnya tersedia secara umum, dan semuanya dipasang di sisi atas papan. Meskipun akan lebih baik untuk menggunakan komponen yang besar dan mudah disolder dengan tangan, pitch kecil dari chip QFN (0.4 mm) berarti bahwa penggunaan beberapa komponen pasif 0402 (metrik 1005) tidak dapat dihindari jika semua GPIO akan digunakan. Meskipun menyolder komponen 0402 dengan tangan tidak terlalu menantang dengan besi solder yang layak, hampir mustahil untuk menyolder QFN tanpa peralatan khusus.

Pada beberapa bagian berikutnya, saya akan mencoba menjelaskan kegunaan sirkuit tambahan tersebut, dan mudah-mudahan bagaimana kami membuat pilihan tersebut. Karena saya akan membahas dua desain terpisah, satu untuk setiap ukuran paket, saya mencoba untuk tetap sesederhana mungkin. Sejauh mungkin, semua referensi komponen untuk kedua papan tersebut identik, jadi jika saya merujuk ke U1, R1, dst., maka komponen tersebut sama relevannya untuk kedua papan tersebut. Pengecualian yang jelas adalah ketika komponen hanya ada di salah satu papan (dalam semua kasus, ini akan berada di varian 80 pin yang lebih besar), maka komponen yang dimaksud hanya akan berada di desain QFN-80; misalnyaample, R13 hanya muncul di papan ini.

Bab 2. Kekuatan

Catu daya seri RP235x dan RP2040 sedikit berbeda kali ini, meskipun dalam konfigurasinya yang paling sederhana, ia masih memerlukan dua catu daya, 3.3V dan 1.1V. Seri RP235x secara bersamaan lebih haus daya, karena kinerjanya lebih tinggi, dan juga lebih hemat (ketika dalam kondisi daya rendah) daripada pendahulunya, dan karenanya regulator linier pada RP2040 telah ditingkatkan dengan regulator switching. Hal ini memungkinkan kita memperoleh efisiensi daya yang lebih besar pada arus yang lebih tinggi (hingga 200mA dibandingkan dengan 100mA sebelumnya).

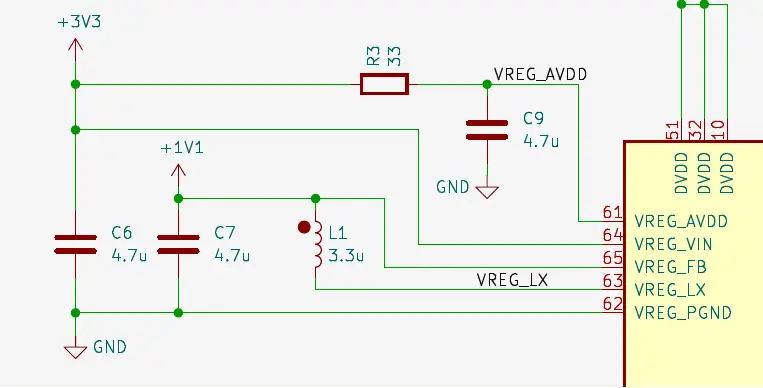

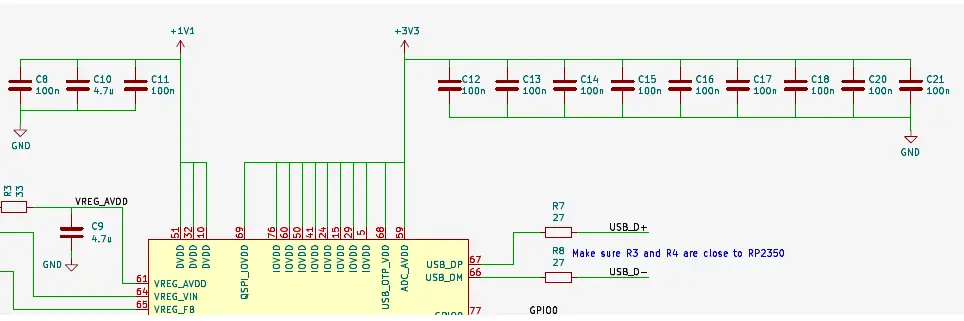

Vol baru pada chiptagpengatur

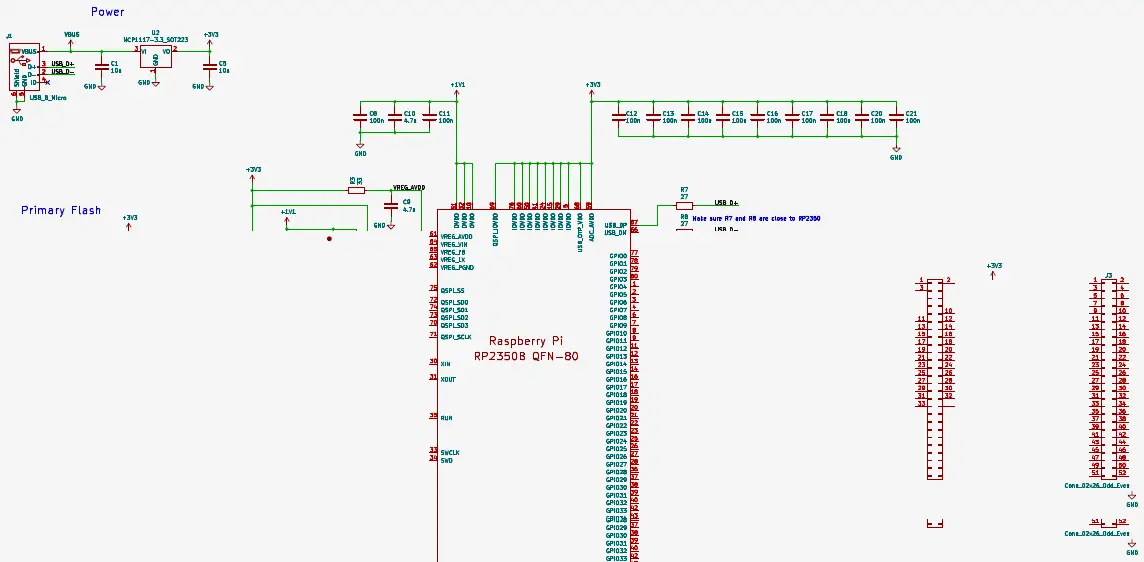

Gambar 3. Bagian skema yang menunjukkan rangkaian regulator internal

Regulator linier RP2040 memiliki dua pin, input 3.3V, dan output 1.1V untuk memasok DVDD pada chip. Kali ini, regulator seri RP235x memiliki lima pin, dan memerlukan beberapa komponen eksternal agar dapat berfungsi. Meskipun ini tampak seperti langkah mundur dalam hal kegunaan, regulator switching memiliki keunggulantagmenjadi lebih hemat daya pada arus beban yang lebih tinggi.

Sesuai namanya, regulator ini dengan cepat menghidupkan dan mematikan transistor internal yang menghubungkan input vol 3.3Vtage (VREG_VIN) ke pin VREG_LX, dan dengan bantuan induktor (L1) dan kapasitor keluaran (C7), dapat menghasilkan output DC voltage yang telah diturunkan dari input. Pin VREG_FB memonitor vol outputtage, dan menyesuaikan rasio on/off dari siklus switching, untuk memastikan volume yang dibutuhkantage dipertahankan. Karena arus besar dialihkan dari VREG_VIN ke VREG_LX, kapasitor besar (C6) yang dekat dengan input diperlukan, jadi kita tidak terlalu mengganggu pasokan 3.3V. Berbicara tentang arus pengalihan yang besar ini, regulator juga dilengkapi dengan koneksi ground return sendiri, VREG_PGND. Mirip dengan VREG_VIN dan VREG_LX, tata letak koneksi ini sangat penting, dan sementara VREG_PGND harus terhubung ke GND utama, itu harus dilakukan sedemikian rupa sehingga semua arus pengalihan yang besar kembali langsung ke pin PGND, tanpa terlalu mengganggu GND lainnya.

Pin terakhir adalah VREG_AVDD, yang memasok sirkuit analog dalam regulator, dan ini sangat sensitif terhadap noise.

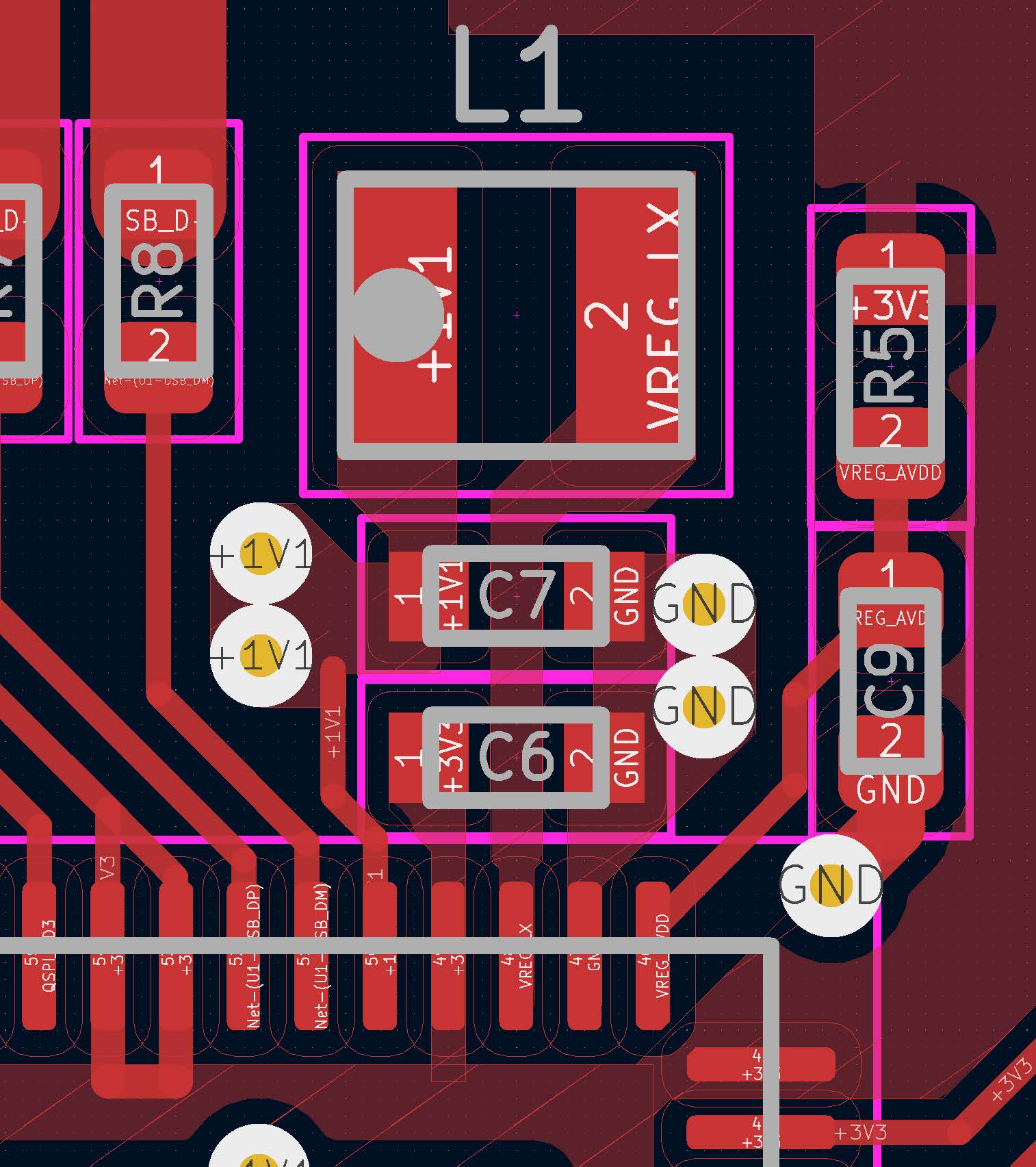

Gambar 4. Bagian skema yang menunjukkan tata letak PCB regulator

- Tata letak regulator pada papan minimal sangat mirip dengan Raspberry Pi Pico 2. Banyak sekali pekerjaan yang telah dilakukan untuk merancang sirkuit ini, dengan banyak iterasi PCB yang diperlukan untuk membuatnya sebaik mungkin. Meskipun Anda dapat menempatkan komponen-komponen ini dalam berbagai cara yang berbeda dan tetap membuat regulator 'berfungsi' (yaitu, menghasilkan output voltage pada tingkat yang tepat, cukup baik untuk menjalankan kode), kami telah menemukan bahwa regulator kami perlu diperlakukan dengan cara yang tepat untuk membuatnya senang, dan dengan senang, yang saya maksud adalah menghasilkan volume output yang benar.tage dalam berbagai kondisi arus beban.

- Saat melakukan percobaan ini, kami agak kecewa karena diingatkan bahwa dunia fisika yang tidak nyaman tidak selalu dapat diabaikan. Kami, sebagai insinyur, sebagian besar mencoba dan melakukan hal ini; menyederhanakan komponen, mengabaikan (seringkali) sifat fisik yang tidak penting, dan sebaliknya berfokus pada sifat yang kami minati. Misalnyaample, resistor sederhana tidak hanya memiliki resistansi, tetapi juga induktansi, dll. Dalam kasus kami, kami (kembali) menemukan bahwa induktor memiliki medan magnet yang terkait dengannya, dan yang terpenting, memancar ke arah yang bergantung pada arah lilitan kumparan, dan arah aliran arus. Kami juga diingatkan bahwa induktor yang 'sepenuhnya' terlindung tidak berarti seperti yang Anda pikirkan. Medan magnet dilemahkan hingga batas yang besar, tetapi beberapa masih hilang. Kami menemukan bahwa kinerja regulator dapat ditingkatkan secara besar-besaran jika induktor berada 'arah yang benar'.

- Ternyata medan magnet yang dipancarkan dari induktor yang 'berputar berlawanan arah' mengganggu kapasitor keluaran regulator (C7), yang pada gilirannya mengganggu sirkuit kontrol dalam RP2350. Dengan induktor pada orientasi yang tepat, dan tata letak yang tepat serta pemilihan komponen yang digunakan di sini, maka masalah ini akan teratasi. Tidak diragukan lagi akan ada tata letak, komponen, dll. lain yang dapat bekerja dengan induktor pada orientasi apa pun, tetapi kemungkinan besar tata letak tersebut akan menggunakan lebih banyak ruang PCB untuk melakukannya. Kami telah menyediakan tata letak yang direkomendasikan ini untuk menghemat banyak waktu teknisi yang telah kami habiskan untuk mengembangkan dan menyempurnakan solusi yang ringkas dan berfungsi dengan baik ini.

- Lebih tepatnya, kami akan mengatakan bahwa jika Anda memilih untuk tidak menggunakan mantan kamiample, maka Anda melakukannya dengan risiko Anda sendiri. Sama seperti yang sudah kami lakukan dengan RP2040 dan rangkaian kristal, di mana kami bersikeras (yah, sangat menyarankan) Anda menggunakan komponen tertentu (kami akan melakukannya lagi di bagian kristal dokumen ini).

- Arah dari induktor kecil ini hampir selalu diabaikan, dengan orientasi lilitan kumparan yang tidak mungkin disimpulkan, dan juga didistribusikan secara acak di sepanjang gulungan komponen. Ukuran casing induktor yang lebih besar sering kali dapat ditemukan memiliki tanda polaritas di atasnya, namun kami tidak dapat menemukan yang sesuai dalam ukuran casing 0806 (metrik 2016) yang telah kami pilih. Untuk tujuan ini, kami telah bekerja sama dengan Abracon untuk memproduksi komponen 3.3μH dengan titik untuk menunjukkan polaritas, dan yang terpenting, hadir dalam gulungan dengan semuanya sejajar dengan cara yang sama. TBD (atau akan segera) tersedia untuk masyarakat umum dari distributor. Seperti yang disebutkan sebelumnya, pasokan VREG_AVDD sangat sensitif terhadap derau, dan karenanya perlu difilter. Kami menemukan bahwa karena VREG_AVDD hanya menarik sekitar 200μA, filter RC 33Ω dan 4.7μF sudah memadai.

- Jadi, untuk rekapitulasi, komponen yang digunakan adalah…

- C6, C7 & C9 – 4.7μF (0402, 1005 metrik)

- L1 – Abracon TBD (0806, metrik 2016)

- R3 – 33Ω (0402, 1005 metrik)

- Lembar data RP2350 memiliki pembahasan lebih rinci tentang rekomendasi tata letak regulator, silakan lihat Komponen Eksternal dan persyaratan tata letak PCB.

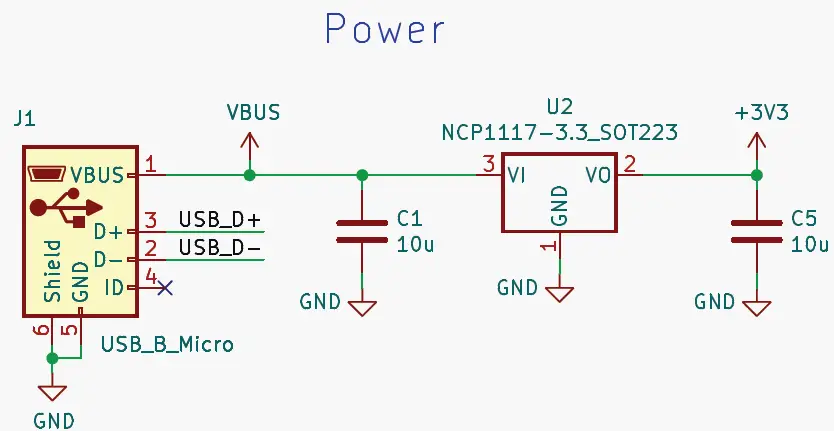

Pasokan masukan

Koneksi daya input untuk desain ini adalah melalui pin VBUS 5V dari konektor Micro-USB (berlabel J1 pada Gambar 5). Ini adalah metode umum untuk memberi daya pada perangkat elektronik, dan masuk akal di sini, karena RP2350 memiliki fungsi USB, yang akan kita sambungkan ke pin data konektor ini. Karena kita hanya memerlukan 3.3V untuk desain ini (pasokan 1.1V berasal dari internal), kita perlu menurunkan pasokan USB 5V yang masuk, dalam hal ini, menggunakan vol eksternal laintage regulator, dalam hal ini regulator linier (alias regulator Low Drop Out, atau LDO). Setelah sebelumnya memuji keunggulan penggunaan regulator switching yang efisien, mungkin juga merupakan pilihan yang bijaksana untuk menggunakannya di sini, tetapi saya memilih kesederhanaan. Pertama, menggunakan LDO hampir selalu lebih mudah. Tidak ada perhitungan yang diperlukan untuk mengetahui ukuran induktor yang harus Anda gunakan, atau seberapa besar kapasitor keluaran, dan tata letaknya biasanya juga jauh lebih mudah. Kedua, menghemat setiap tetes daya terakhir bukanlah tujuan di sini; jika memang demikian, saya akan mempertimbangkan dengan serius untuk menggunakan regulator switching, dan Anda dapat menemukanampcara melakukannya pada Raspberry Pi Pico 2. Dan ketiga, saya cukup 'meminjam' rangkaian yang sebelumnya saya gunakan pada versi RP2040 dari papan Minimal. NCP1117 (U2) yang dipilih di sini memiliki keluaran tetap 3.3V, tersedia secara luas, dan dapat menyediakan arus hingga 1A, yang akan cukup untuk sebagian besar desain. Melihat lembar data untuk NCP1117 memberi tahu kita bahwa perangkat ini memerlukan kapasitor 10μF pada masukan, dan satu lagi pada keluaran (C1 dan C5).

Kapasitor decoupling

Gambar 6. Bagian skema yang menunjukkan input catu daya RP2350, vol.tagregulator e dan kapasitor decoupling

Aspek lain dari desain catu daya adalah kapasitor decoupling yang diperlukan untuk RP2350. Kapasitor ini menyediakan dua fungsi dasar. Pertama, kapasitor ini menyaring gangguan catu daya, dan kedua, menyediakan pasokan muatan lokal yang dapat digunakan oleh sirkuit di dalam RP2350 dalam waktu singkat. Hal ini mencegah voltaglevel di sekitar langsung agar tidak turun terlalu banyak saat permintaan arus tiba-tiba meningkat. Oleh karena itu, penting untuk menempatkan decoupling dekat dengan pin daya. Biasanya, kami merekomendasikan penggunaan kapasitor 100nF per pin daya, namun, kami menyimpang dari aturan ini dalam beberapa kasus.

Gambar 7. Bagian tata letak yang menunjukkan perutean dan decoupling RP2350

- Pertama, agar dapat memiliki cukup ruang untuk semua pin chip agar dapat diarahkan keluar, menjauh dari perangkat, kita harus berkompromi dengan jumlah kapasitor decoupling yang dapat kita gunakan. Dalam desain ini, pin 53 dan 54 dari RP2350A (pin 68 dan 69 dari RP2350B) berbagi satu kapasitor (C12 pada Gambar 7 dan Gambar 6), karena tidak banyak ruang di sisi perangkat tersebut, dan komponen serta tata letak regulator diutamakan.

- Kurangnya ruang ini dapat diatasi jika kita menggunakan teknologi yang lebih kompleks/mahal, seperti komponen yang lebih kecil, atau PCB empat lapis dengan komponen di sisi atas dan bawah. Ini adalah kompromi desain; kita telah mengurangi kompleksitas dan biaya, dengan mengorbankan kapasitansi decoupling yang lebih sedikit, dan kapasitor yang sedikit lebih jauh dari chip daripada yang optimal (ini meningkatkan induktansi). Ini dapat memiliki efek membatasi kecepatan maksimum desain yang dapat beroperasi, karena voltagPasokan listrik bisa menjadi terlalu berisik dan turun di bawah volume minimum yang diizinkantage; tetapi untuk sebagian besar aplikasi, trade-off ini seharusnya dapat diterima.

- Penyimpangan lain dari aturan 100nF adalah agar kita dapat lebih meningkatkan voltagkinerja regulator; kami menyarankan penggunaan 4.7μF untuk C10, yang ditempatkan di sisi lain chip dari regulator.

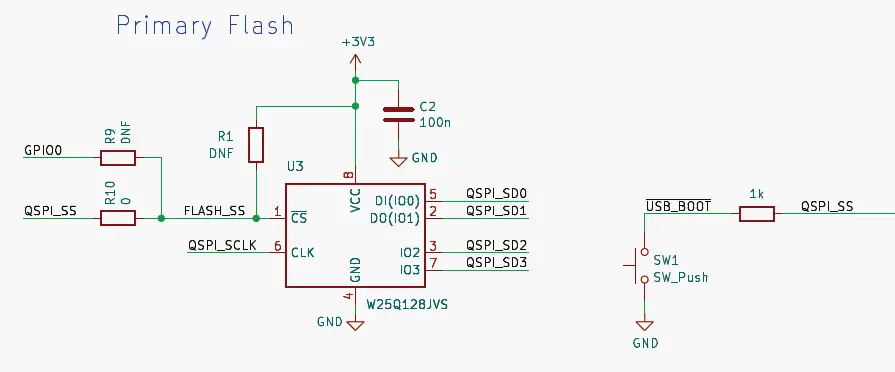

Bab 3. Memori Flash

Lampu kilat utama

Gambar 8. Bagian skema yang menunjukkan memori flash primer dan sirkuit USB_BOOT

- Agar dapat menyimpan kode program yang dapat di-boot dan dijalankan oleh RP2350, kita perlu menggunakan memori flash, khususnya memori flash quad SPI. Perangkat yang dipilih di sini adalah perangkat W25Q128JVS (U3 pada Gambar 8), yang merupakan chip 128Mbit (16MB). Ini adalah ukuran memori terbesar yang dapat didukung oleh RP2350. Jika aplikasi khusus Anda tidak memerlukan penyimpanan sebanyak itu, maka memori yang lebih kecil dan lebih murah dapat digunakan sebagai gantinya.

- Karena databus ini dapat memiliki frekuensi yang cukup tinggi dan digunakan secara teratur, pin QSPI dari RP2350 harus dihubungkan langsung ke flash, menggunakan koneksi pendek untuk menjaga integritas sinyal, dan juga untuk mengurangi crosstalk di sirkuit sekitarnya. Crosstalk adalah saat sinyal pada satu jaringan sirkuit dapat menyebabkan volatilitas yang tidak diinginkan.tagpada sirkuit tetangga, yang berpotensi menyebabkan terjadinya kesalahan.

- Sinyal QSPI_SS merupakan kasus khusus. Sinyal ini terhubung langsung ke flash, tetapi juga memiliki dua resistor (yah, empat, tetapi saya akan membahasnya nanti) yang terhubung dengannya. Yang pertama (R1) merupakan pull-up ke suplai 3.3V. Memori flash mengharuskan input pemilihan chip berada pada volume yang samatage sebagai pin pasokan 3.3V miliknya sendiri saat perangkat dinyalakan, jika tidak, perangkat tidak akan berfungsi dengan benar. Saat RP2350 dinyalakan, pin QSPI_SS-nya akan secara otomatis menjadi pull-up, tetapi ada periode waktu singkat selama penyalaan di mana status pin QSPI_SS tidak dapat dijamin. Penambahan resistor pull-up memastikan bahwa persyaratan ini akan selalu terpenuhi. R1 ditandai sebagai DNF (Do Not Fit) pada skema, karena kami telah menemukan bahwa dengan perangkat flash khusus ini, pull-up eksternal tidak diperlukan. Namun, jika flash yang berbeda digunakan, mungkin penting untuk dapat memasukkan resistor 10kΩ di sini, jadi resistor ini telah disertakan untuk berjaga-jaga.

- Resistor kedua (R6) adalah resistor 1kΩ, yang terhubung ke tombol tekan (SW1) yang diberi label 'USB_BOOT'. Ini karena pin QSPI_SS digunakan sebagai 'boot strap'; RP2350 memeriksa nilai I/O ini selama urutan boot, dan jika ditemukan logika 0, maka RP2350 kembali ke mode BOOTSEL, di mana RP2350 menampilkan dirinya sebagai perangkat penyimpanan massal USB, dan kode dapat disalin langsung ke dalamnya. Jika kita cukup menekan tombol, kita tarik pin QSPI_SS ke ground, dan jika perangkat tersebut kemudian direset (misalnya dengan mengaktifkan pin RUN), RP2350 akan memulai ulang dalam mode BOOTSEL alih-alih mencoba menjalankan konten flash. Resistor ini, R2 dan R6 (juga R9 dan R10), harus ditempatkan dekat dengan chip flash, sehingga kita menghindari panjang trek tembaga tambahan yang dapat memengaruhi sinyal.

- Semua hal di atas secara khusus berlaku untuk RP2350, yang tidak memiliki flash internal. Tentu saja, perangkat RP2354 memiliki memori flash internal 2MB, sehingga memori U3 eksternal tidak diperlukan, sehingga U3 dapat dihapus dengan aman dari skema, atau dibiarkan kosong begitu saja. Dalam kedua kasus ini, kita tetap ingin agar sakelar USB_BOOT tetap terhubung ke QSPI_SS, sehingga kita tetap dapat memasuki mode boot USB.

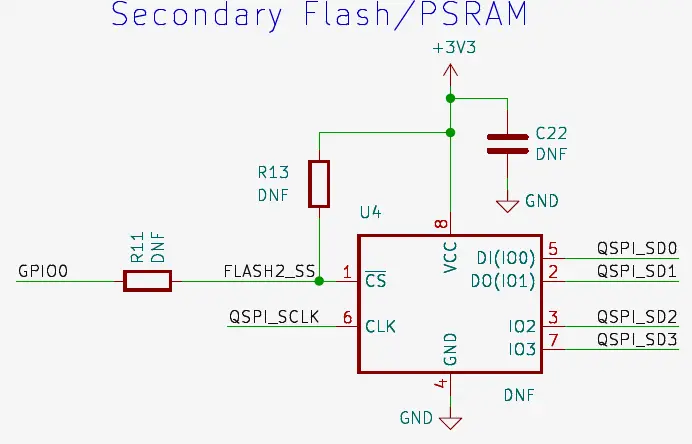

Flash sekunder atau PSRAM

- Seri RP235x sekarang mendukung perangkat memori kedua menggunakan pin QSPI yang sama, dengan GPIO yang menyediakan pemilihan chip tambahan. Jadi, jika kita menggunakan RP2354 (yang memiliki flash internal), maka kita dapat menggunakan U3 sebagai flash sekunder, atau bahkan menggantinya dengan perangkat PSRAM. Untuk melakukan ini, kita perlu memutuskan QSPI_SS dari U3, dan sebagai gantinya menghubungkannya ke GPIO yang sesuai. GPIO terdekat yang mampu menjadi pemilihan chip (XIP_CS1n) adalah GPIO0, jadi dengan menghapus 0Ω dari R10, dan memasangnya ke R9, kita sekarang dapat mengakses U3 selain flash pada chip. Untuk memanfaatkan sepenuhnyatagDari fitur ini, di mana kita memiliki dua perangkat memori eksternal sehingga komponen RP2350 tanpa flash dapat memperoleh manfaat, papan Minimal yang lebih besar dari keduanya, untuk RP2350B, menyertakan tapak opsional (U4) untuk chip memori tambahan.

Gambar 9. Bagian skema yang menunjukkan perangkat memori sekunder opsional

Agar dapat menggunakan perangkat ini, perangkat ini jelas harus diisi, begitu pula R11 (0Ω), dan R13 (10KΩ). Penambahan R11 menghubungkan GPIO0 (sinyal XIP_CS1n) ke pemilihan chip memori kedua. Pull-up pada pin pemilihan chip benar-benar diperlukan kali ini, karena status default GPIO0 adalah ditarik rendah saat dinyalakan, yang akan menyebabkan perangkat flash kita gagal. C22 juga diperlukan untuk menyediakan decoupling catu daya lokal untuk U4.

Chip flash yang didukung

Urutan probe flash awal, digunakan oleh bagian bawah untuk mengekstrak s keduatage dari flash, menggunakan perintah baca serial 03h, dengan pengalamatan 24-bit, dan clock serial sekitar 1MHz. Ia berulang kali berputar melalui empat kombinasi polaritas clock dan fase clock, mencari detik yang validtage checksum CRC32.

Sebagai s keduatage kemudian bebas untuk mengonfigurasikan eksekusi di tempat menggunakan perintah baca serial 03h yang sama, RP2350 dapat melakukan eksekusi flash di tempat yang di-cache dengan chip apa pun yang mendukung baca serial 03h dengan pengalamatan 24-bit, yang mencakup sebagian besar perangkat flash seri 25. SDK menyediakan example detik stage untuk CPOL=0 CPHA=0, pada https://github.com/raspberrypi/pico-sdk/blob/master/src/rp2350/boot_stage2/boot2_generic_03h.SUntuk mendukung pemrograman flash menggunakan rutin di bagian bawah, perangkat juga harus merespons perintah berikut:

- 02h program halaman 256-byte

- 05h status register terbaca

- 06h mengatur kait pengaktifan penulisan

- Penghapusan sektor 20h 4kB

RP2350 juga mendukung berbagai macam mode akses dual-SPI dan QSPI. Misalnyaampaku, https://github.com/raspberrypi/pico-sdk/blob/master/src/rp2350/boot_stage2/boot2_w25q080.S mengonfigurasi perangkat Winbond seri W25Q untuk mode baca berkelanjutan quad-IO, di mana RP2350 mengirimkan alamat quad-IO (tanpa awalan perintah) dan flash merespons dengan data quad-IO.

Diperlukan kehati-hatian dengan mode flash XIP saat perangkat flash berhenti merespons perintah serial standar, seperti mode baca berkelanjutan Winbond yang disebutkan di atas. Hal ini dapat menyebabkan masalah saat RP2350 direset, tetapi perangkat flash tidak dimatikan, karena flash tidak akan merespons urutan probe flash bootrom. Sebelum mengeluarkan pembacaan serial 03h, bootrom selalu mengeluarkan urutan tetap berikut, yang merupakan urutan upaya terbaik untuk menghentikan XIP pada berbagai perangkat flash:

- CSn=1, IO[3:0]=4'b0000 (melalui pull down untuk menghindari pertentangan), mengeluarkan ×32 jam

- CSn=0, IO[3:0]=4'b1111 (melalui pull up untuk menghindari pertentangan), mengeluarkan ×32 jam

- CSn=1

- CSn=0, MOSI=1'b1 (digerakkan low-Z, semua I/O lainnya Hi-Z), mengeluarkan ×16 jam

Jika perangkat pilihan Anda tidak merespons urutan ini saat dalam mode baca berkelanjutan, maka perangkat harus dipertahankan dalam kondisi di mana setiap transfer diawali dengan perintah serial. Jika tidak, RP2350 tidak akan dapat melakukan pemulihan setelah pengaturan ulang internal.

Untuk detail lebih lanjut tentang QSPI, silakan lihat QSPI Memory Interface (QMI) di lembar data RP2350.

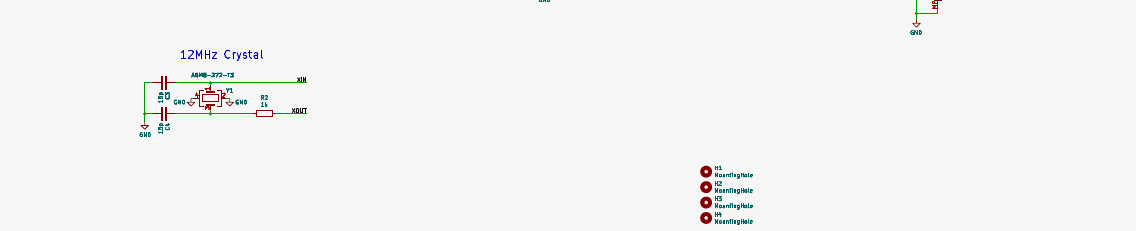

Bab 4. Osilator Kristal

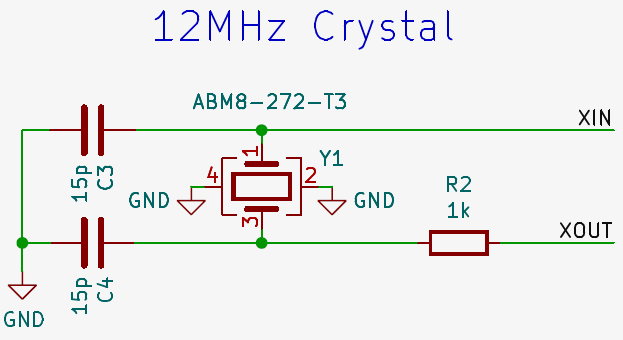

Gambar 10. Bagian skema yang menunjukkan osilator kristal dan kapasitor beban

- Secara tegas, RP2350 sebenarnya tidak memerlukan sumber clock eksternal, karena memiliki osilator internalnya sendiri. Namun, karena frekuensi osilator internal ini tidak didefinisikan atau dikontrol dengan baik, bervariasi dari chip ke chip, serta dengan volume pasokan yang berbedatages dan suhu, disarankan untuk menggunakan sumber frekuensi eksternal yang stabil. Aplikasi yang bergantung pada frekuensi yang tepat tidak mungkin dilakukan tanpa sumber frekuensi eksternal, USB menjadi sumber utamaampsaya.

- Penyediaan sumber frekuensi eksternal dapat dilakukan dengan salah satu dari dua cara: dengan menyediakan sumber jam dengan output CMOS (gelombang persegi IOVDD vol.tage) ke pin XIN, atau dengan menggunakan kristal 12MHz yang terhubung antara

- XIN dan XOUT. Menggunakan kristal merupakan pilihan yang lebih baik di sini, karena keduanya relatif murah dan sangat akurat.

- Kristal yang dipilih untuk desain ini adalah ABM8-272-T3 (Y1 pada Gambar 10). Ini adalah kristal 12MHz yang sama yang digunakan pada Raspberry Pi Pico dan Raspberry Pi Pico 2. Kami sangat menyarankan penggunaan kristal ini bersama dengan rangkaian yang menyertainya untuk memastikan bahwa jam dimulai dengan cepat dalam semua kondisi tanpa merusak kristal itu sendiri. Kristal tersebut memiliki toleransi frekuensi 30ppm, yang seharusnya cukup baik untuk sebagian besar aplikasi. Bersama dengan toleransi frekuensi +/-30ppm, ia memiliki ESR maksimum 50Ω, dan kapasitansi beban 10pF, yang keduanya memiliki pengaruh pada pilihan komponen yang menyertainya.

- Agar kristal berosilasi pada frekuensi yang diinginkan, pabrikan menentukan kapasitansi beban yang dibutuhkannya untuk melakukannya, dan dalam kasus ini, adalah 10pF. Kapasitansi beban ini dicapai dengan menempatkan dua kapasitor dengan nilai yang sama, satu di setiap sisi kristal ke tanah (C3 dan C4). Dari titik kristal view, kapasitor ini dihubungkan secara seri antara dua terminalnya. Teori rangkaian dasar memberi tahu kita bahwa kapasitor-kapasitor tersebut bergabung untuk menghasilkan kapasitansi (C3*C4)/(C3+C4), dan karena C3=C4, maka kapasitor tersebut adalah C3/2. Dalam contoh iniample, kita telah menggunakan kapasitor 15pF, jadi kombinasi seri adalah 7.5pF. Selain kapasitansi beban yang disengaja ini, kita juga harus menambahkan nilai untuk kapasitansi ekstra yang tidak disengaja, atau kapasitansi parasit, yang kita dapatkan dari jalur PCB dan pin XIN dan XOUT RP2350. Kita akan mengasumsikan nilai 3pF untuk ini, dan karena kapasitansi ini sejajar dengan C3 dan C4, kita cukup menambahkan ini untuk memberi kita total kapasitansi beban 10.5pF, yang cukup dekat dengan target 10pF. Seperti yang Anda lihat, kapasitansi parasit dari jejak PCB merupakan faktor, dan oleh karena itu kita perlu membuatnya tetap kecil sehingga kita tidak mengganggu kristal dan menghentikannya berosilasi sebagaimana dimaksud. Cobalah dan pertahankan tata letak sesingkat mungkin.

- Pertimbangan kedua adalah ESR (resistansi seri ekivalen) maksimum dari kristal. Kami memilih perangkat dengan maksimum 50Ω, karena kami menemukan bahwa ini, bersama dengan resistor seri 1kΩ (R2), adalah nilai yang baik untuk mencegah kristal menjadi terlalu terdorong dan rusak saat menggunakan level IOVDD 3.3V. Namun, jika IOVDD kurang dari 3.3V, maka arus penggerak pin XIN/XOUT berkurang, dan Anda akan menemukan bahwa amplitude kristal lebih rendah, atau bahkan mungkin tidak berosilasi sama sekali. Dalam kasus ini, nilai resistor seri yang lebih kecil perlu digunakan. Setiap penyimpangan dari rangkaian kristal yang ditunjukkan di sini, atau dengan level IOVDD selain 3.3V, akan memerlukan pengujian ekstensif untuk memastikan bahwa kristal berosilasi dalam semua kondisi, dan memulai dengan cukup cepat sehingga tidak menimbulkan masalah dengan aplikasi Anda.

Kristal yang direkomendasikan

- Untuk desain asli menggunakan RP2350, kami sarankan menggunakan Abracon ABM8-272-T3. Misalnyaample, selain desain minimal example, lihat skema papan Pico 2 di Lampiran B Lembar Data Raspberry Pi Pico 2 dan desain Pico 2 files.

- Untuk performa dan stabilitas terbaik di berbagai rentang suhu operasi, gunakan Abracon ABM8-272-T3. Anda dapat memperoleh ABM8-272-T3 langsung dari Abracon atau dari pengecer resmi. Pico 2 telah disetel khusus untuk ABM8-272-T3, yang memiliki spesifikasi berikut:

- Bahkan jika Anda menggunakan kristal dengan spesifikasi serupa, Anda perlu menguji rangkaian pada berbagai suhu untuk memastikan stabilitas.

- Osilator kristal ditenagai oleh IOVDD vol.tage. Akibatnya, kristal Abracon dan d tertentu ituampresistor ing disetel untuk operasi 3.3V. Jika Anda menggunakan vol IO yang berbedatage, Anda perlu menyetel ulang.

- Perubahan apa pun pada parameter kristal dapat menimbulkan risiko ketidakstabilan pada semua komponen yang terhubung ke sirkuit kristal.

- Jika Anda tidak dapat memperoleh kristal yang direkomendasikan langsung dari Abracon atau pengecer, hubungi aplikasi@raspberrypi.com.

Bab 5. IO

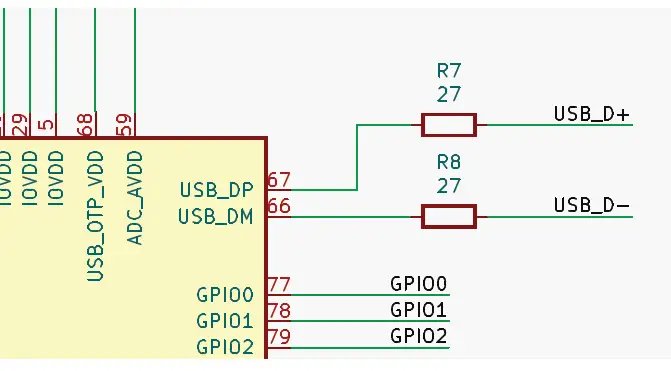

USB

Gambar 11. Bagian skema yang menunjukkan pin USB RP2350 dan terminasi seri

- RP2350 menyediakan dua pin untuk digunakan untuk USB kecepatan penuh (FS) atau kecepatan rendah (LS), baik sebagai host atau perangkat, tergantung pada perangkat lunak yang digunakan. Seperti yang telah kita bahas, RP2350 juga dapat di-boot sebagai perangkat penyimpanan massal USB, jadi menghubungkan pin-pin ini ke konektor USB (J1 pada Gambar 5) masuk akal. Pin USB_DP dan USB_DM pada RP2350 tidak memerlukan pull-up atau pull-down tambahan (diperlukan untuk menunjukkan kecepatan, FS atau LS, atau apakah itu host atau perangkat), karena ini sudah terpasang pada I/O. Namun, I/O ini memerlukan resistor terminasi seri 27Ω (R7 dan R8 pada Gambar 11), yang ditempatkan dekat dengan chip, untuk memenuhi spesifikasi impedansi USB.

- Meskipun RP2350 terbatas pada kecepatan data penuh (12Mbps), kita harus mencoba dan memastikan bahwa impedansi karakteristik jalur transmisi (jalur tembaga yang menghubungkan chip ke konektor) mendekati

- Spesifikasi USB 90Ω (diukur secara diferensial). Pada papan setebal 1 mm seperti ini, jika kita menggunakan jalur selebar 0.8 mm pada USB_DP dan USB_DM, dengan celah 0.15 mm di antara keduanya, kita akan mendapatkan impedansi karakteristik diferensial sekitar 90Ω. Hal ini untuk memastikan bahwa sinyal dapat berjalan di sepanjang jalur transmisi ini sebersih mungkin, meminimalkan volatilitastage refleksi yang dapat mengurangi integritas sinyal. Agar jalur transmisi ini berfungsi dengan baik, kita perlu memastikan bahwa tepat di bawah jalur ini terdapat ground. Area ground tembaga yang solid dan tidak terputus, membentang sepanjang jalur. Pada desain ini, hampir seluruh lapisan tembaga bawah dikhususkan untuk ground, dan perhatian khusus diberikan untuk memastikan bahwa jalur USB hanya melewati ground. Jika PCB yang lebih tebal dari 1 mm dipilih untuk bangunan Anda, maka kita memiliki dua opsi. Kita dapat merekayasa ulang jalur transmisi USB untuk mengimbangi jarak yang lebih jauh antara jalur dan ground di bawahnya (yang secara fisik mustahil), atau kita dapat mengabaikannya, dan berharap yang terbaik. USB FS bisa sangat pemaaf, tetapi jarak tempuh Anda mungkin berbeda. Ini mungkin berfungsi di banyak aplikasi, tetapi mungkin tidak akan sesuai dengan standar USB.

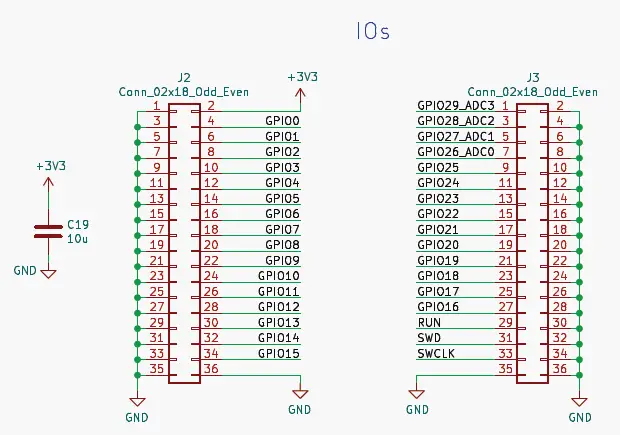

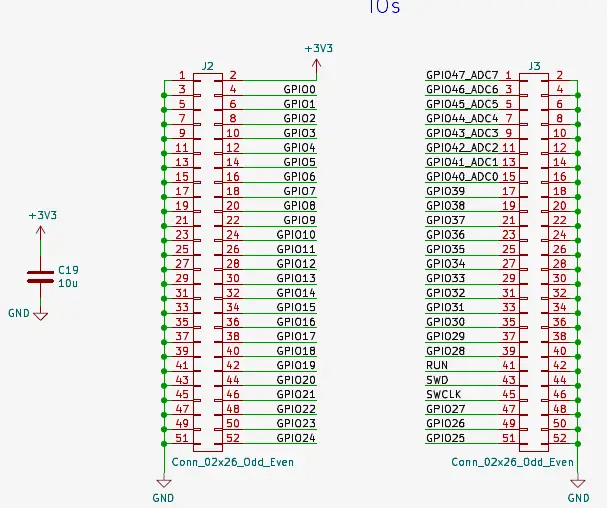

Header I/O

Gambar 12. Bagian skema yang menunjukkan header I/O 2.54mm versi QFN60

- Selain konektor USB yang telah disebutkan, terdapat sepasang header 2.54 mm baris ganda (J2 dan J3 pada Gambar 12), satu di setiap sisi papan, yang telah dihubungkan dengan I/O lainnya. Terdapat 30 GPIO pada RP2350A, sedangkan terdapat 48 GPIO pada RP2350B, sehingga header pada versi papan Minimal ini lebih besar untuk mengakomodasi pin tambahan (lihat Gambar 13).

- Karena ini adalah desain serbaguna, tanpa aplikasi khusus, I/O telah tersedia untuk dihubungkan sesuai keinginan pengguna. Baris pin bagian dalam pada setiap header adalah I/O, dan baris luar semuanya terhubung ke ground. Merupakan praktik yang baik untuk menyertakan banyak ground pada konektor I/O. Ini membantu mempertahankan ground impedansi rendah, dan juga menyediakan banyak jalur balik potensial untuk arus yang mengalir ke dan dari

- Koneksi I/O. Hal ini penting untuk meminimalkan interferensi elektromagnet yang dapat disebabkan oleh arus balik sinyal peralihan cepat yang menempuh jalur panjang dan berulang untuk melengkapi rangkaian.

- Kedua header berada pada kisi 2.54 mm yang sama, yang memudahkan penyambungan papan ini ke hal lain, seperti papan tempat memotong roti. Anda mungkin ingin mempertimbangkan untuk memasang header baris tunggal saja, bukan header baris ganda, dengan membuang baris luar sambungan ground, agar lebih mudah dipasang ke papan tempat memotong roti.

Gambar 13. Bagian skema yang menunjukkan header I/O 2.54mm versi QFN80

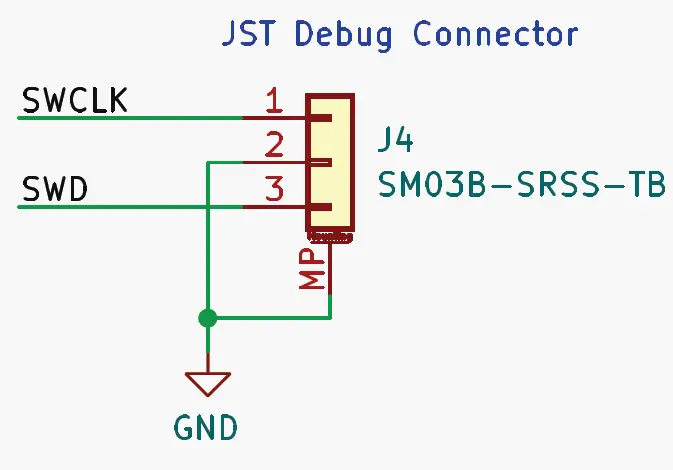

Konektor debug

Gambar 14. Bagian skema yang menunjukkan konektor JST opsional untuk debug SWD

Untuk debugging pada chip, Anda mungkin ingin menghubungkan ke antarmuka SWD dari RP2350. Dua pin, SWD dan SWCLK, tersedia pada header 2.54 mm, J3, untuk memungkinkan probe debug pilihan Anda dihubungkan dengan mudah. Selain itu, saya telah menyertakan header JST opsional, yang memungkinkan koneksi mudah ke Raspberry Pi Debug Probe. Anda tidak perlu menggunakan ini, header 2.54 mm akan cukup jika Anda memang ingin men-debug perangkat lunak, tetapi saya merasa lebih mudah untuk melakukannya. Saya telah memilih konektor horizontal, terutama karena saya suka tampilannya, meskipun tidak berada di tepi papan, tetapi yang vertikal tersedia, meskipun dengan jejak yang sedikit berbeda.

Tombol

Desain Minimal kini berisi bukan hanya satu, tetapi dua tombol, sedangkan versi RP240 tidak memilikinya. Satu untuk pemilihan boot USB seperti yang telah kita bahas sebelumnya, tetapi yang kedua adalah tombol 'reset', yang dihubungkan ke pin RUN. Keduanya tidak sepenuhnya diperlukan (meskipun tombol BOOTSEL harus diganti dengan header atau yang serupa jika mode boot USB diperlukan), dan dapat dilepas jika ruang atau biaya menjadi masalah, tetapi keduanya tentu saja membuat penggunaan RP2350 menjadi pengalaman yang jauh lebih menyenangkan.

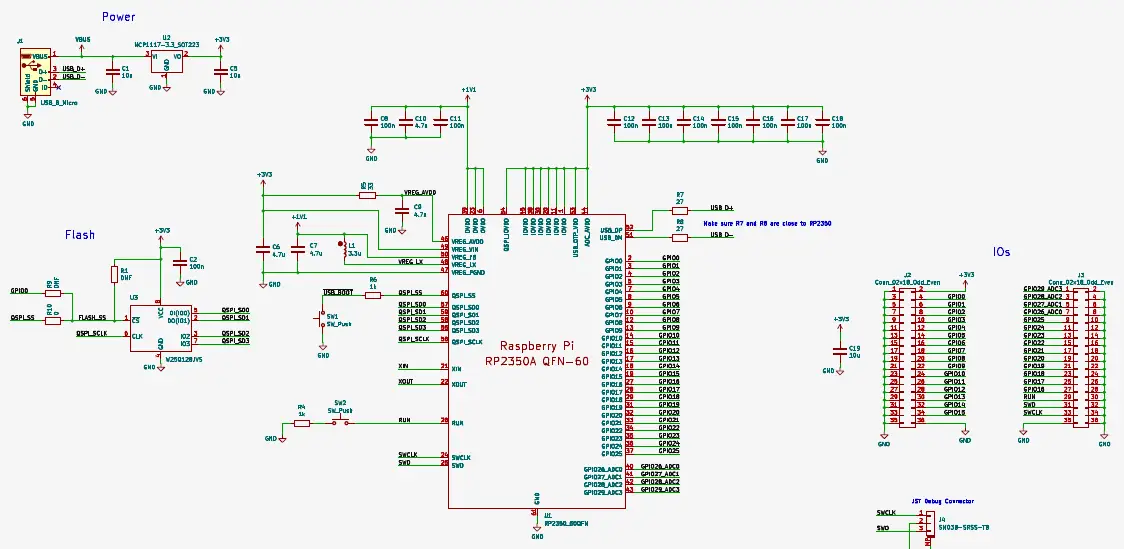

Lampiran A: Skema Lengkap - Versi RP2350A

Gambar 15. Skema lengkap Desain Minimal untuk RP2350A

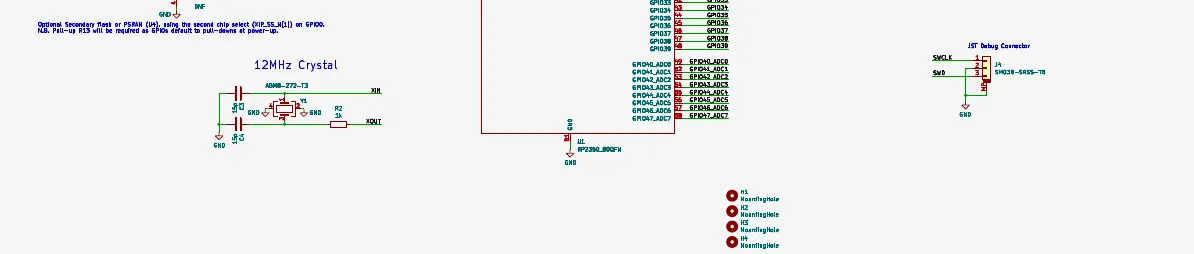

Lampiran B: Skema Lengkap - Versi RP2350B

Gambar 16. Skema lengkap Desain Minimal untuk RP2350B

Lampiran H: Riwayat Rilis Dokumentasi

8 Agustus 2024

Rilis awal.

saya Raspberry Pi

Raspberry Pi adalah merek dagang dari Raspberry Pi Ltd

Raspberry Pi Ltd

Dokumen / Sumber Daya

|

Mikrokontroler Raspberry Pi SC1631 [Bahasa Indonesia:] Panduan Instruksi Mikrokontroler Raspberry SC1631, SC1631, Mikrokontroler Raspberry, Mikrokontroler |