TOSHIBA DEBUG-A 32 Bit RISC mikrokontroleur

Enfòmasyon sou pwodwi

Espesifikasyon

- Non pwodwi: Entèfas debug

- Modèl: DEBUG-A

- Revizyon: 1.4

- Dat: 2024-10

Enstriksyon Itilizasyon Pwodwi

Entwodiksyon

Entèfas debogaj la se yon manyèl referans mikrokontroleur RISC 32-bit pou rezon debogaj.

Karakteristik

- Pò Antre / Sòti

- Enfòmasyon sou pwodwi

- Flash memwa

- Kontwòl revèy ak mòd operasyon

Kòmanse

- Konekte Entèfas Debug nan sistèm ou a lè l sèvi avèk câbles ki apwopriye yo.

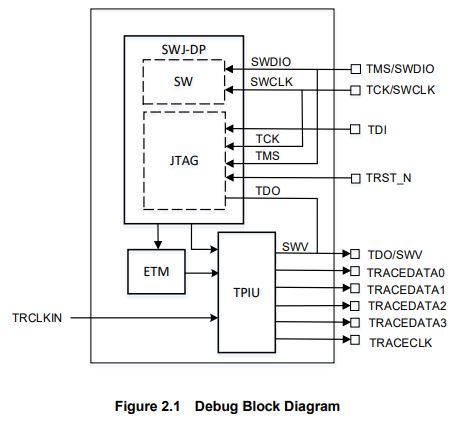

- Gade nan dyagram nan blòk Debug (Figi 2.1) pou pi byen konprann koòdone a.

- Asire bon ekipman pou pouvwa ak koneksyon.

FAQ (Kesyon yo poze souvan)

- Ki pwopriyete chak bit nan yon rejis?

Pwopriyete yo eksprime kòm R (Li sèlman), W (Ekri sèlman), oswa R/W (Li ak ekri). - Ki jan yo ta dwe rezève ti moso nan yon rejis dwe okipe?

Bits rezève pa dwe reekri, epi valè li a pa ta dwe itilize. - Ki jan nou entèprete fòma nimerik nan manyèl la?

Nimewo Egzadesimal yo gen prefiks 0x, nimewo desimal ka gen yon sifiks 0d, epi nimewo binè yo ka prefiks 0b.

Prefas

Dokiman ki gen rapò

| Non dokiman an |

| Pò Antre / Sòti |

| Enfòmasyon sou pwodwi |

| Flash memwa |

| Kontwòl revèy ak mòd operasyon |

Konvansyon

- Fòma nimerik swiv règ yo jan yo montre anba a:

- Egzadesimal: 0xABC

- Desimal: 123 oswa 0d123

Se sèlman lè li bezwen montre klèman ke yo se nimewo desimal. - Binè: 0b111

Li posib pou omite "0b la" lè kantite bit yo ka byen konprann nan yon fraz.

- Yo ajoute "_N" nan fen non siyal yo pou endike siyal aktif ki ba yo.

- Yo rele sa "afime" ke yon siyal deplase nan nivo aktif li, ak "desè" nan nivo inaktif li.

- Lè yo refere de oswa plis non siyal yo, yo dekri yo kòm [m:n].

Example: S[3:0] montre kat non siyal S3, S2, S1 ak S0 ansanm. - Karaktè ki antoure pa [ ] defini rejis la.

Example: [ABCD] - "N" ranplase nimewo sifiks de oswa plis menm kalite rejis, jaden, ak non ti.

Example: [XYZ1], [XYZ2], [XYZ3] → [XYZn] - "x" ranplase nimewo sifiks oswa karaktè inite ak chanèl nan lis anrejistreman an.

- Nan ka inite a, "x" vle di A, B, ak C, ...

Example: [ADACR0], [ADBCR0], [ADCCR0] → [ADxCR0] - Nan ka kanal la, "x" vle di 0, 1, ak 2, ...

Example: [T32A0RUNA], [T32A1RUNA], [T32A2RUNA] → [T32AxRUNA] - Ranje bit nan yon rejis ekri kòm [m: n].

Example: Bit [3: 0] eksprime seri de bit 3 a 0. - Valè konfigirasyon yon rejis eksprime swa pa nimewo egzadesimal oswa nimewo binè.

Example: [ABCD] = 0x01 (egzadisimal), [XYZn] = 1 (binè) - Mo ak byte reprezante longè bit sa a.

- Byte: 8 bit

- Mwatye mo: 16 bit

- Pawòl: 32 bit

- Double mo: 64 bit

- Pwopriyete chak bit nan yon rejis yo eksprime jan sa a:

- R: Li sèlman

- W: Ekri sèlman

- R / W: Li ak ekri yo posib.

- Sòf si sa presize, aksè enskri sipòte sèlman aksè mo.

- Rejis ki defini kòm "Rezève" pa dwe reekri. Anplis, pa sèvi ak valè li a.

- Valè li nan ti bit la ki gen yon valè default nan "-" se enkoni.

- Lè yo ekri yon rejis ki genyen tou de bit ki ka ekri ak ti ki sèlman pou li, yo ta dwe ekri ti ki pou li sèlman ak valè default yo.

- Bits rezève nan rejis ekri sèlman yo ta dwe ekri ak valè default yo. Nan ka yo ke default la se "-", swiv definisyon chak rejis.

- Pa sèvi ak pwosesis lekti-modifye-ekri nan rejis la nan yon definisyon ki diferan nan ekri ak li.

Tèm ak Abreviyasyon

Kèk nan abrevyasyon yo itilize nan dokiman sa a se jan sa a:

- SWJ-DP Fil seri JTAG Debug Port

- ETM Embedded Trace MacrocellTM

- TPIU Trace Port Entèfas Inite

- JTAG Gwoup Aksyon Tès Konjwen

- SW Fil Serial

- SWV Fil Serial Viewer

Deskripsyon yo

Fil Serial JTAG Debug Port (SWJ-DP) inite pou entèfas ak zouti debogaj yo ak inite Embedded Trace Macrocell (ETM) pou pwodiksyon tras enstriksyon yo entegre. Done tras yo soti nan broch yo dedye (TRACEDATA[3:0], SWV) pou debogaj la atravè Inite Entèfas Port Trace sou chip (TPIU).

| Klasifikasyon fonksyon | Fonksyon | Operasyon |

| SWJ-DP | JTAG | Li posib konekte JTAG sipòte zouti debogaj. |

| SW | Li posib pou konekte zouti debogaj Serial Fil yo. | |

| ETM | Tras | Li posib pou konekte zouti debogaj sipò ETM Trace yo. |

Pou plis detay sou SWJ-DP, ETM ak TPIU, al gade nan "Manyèl Referans Teknik Pwosesè Arm ® Cortex-M3 ®"/"Manyèl Referans Teknik Pwosesè Arm Cortex-M4".

Konfigirasyon

Figi 2.1 montre dyagram blòk koòdone debug la.

| Non. | Senbòl | Non siyal | I/O | Manyèl referans ki gen rapò |

| 1 | TRCLKIN | Revèy Fonksyon Trace | Antre | Kontwòl revèy ak mòd operasyon |

| 2 | TMS | JTAG Seleksyon mòd tès | Antre | Pò Antre / Sòti, Enfòmasyon sou pwodwi |

| 3 | SWDIO | Serial Fil Done Antre / Sòti | Antre / Sòti | Pò Antre / Sòti, Enfòmasyon sou pwodwi |

| 4 | TCK | JTAG Serial Clock opinyon | Antre | Pò Antre / Sòti, Enfòmasyon sou pwodwi |

| 5 | SWCLK | Serial Fil Revèy | Antre | Pò Antre / Sòti, Enfòmasyon sou pwodwi |

| 6 | TDO | JTAG Sòti Done Tès | Sòti | Pò Antre / Sòti, Enfòmasyon sou pwodwi |

| 7 | SWV | Fil Serial Viewer Sòti a | Sòti | Pò Antre / Sòti, Enfòmasyon sou pwodwi |

| 8 | TDI | JTAG Tès Done Antre | Antre | Pò Antre / Sòti, Enfòmasyon sou pwodwi |

| 9 | TRST_N | JTAG Tès RESET_N | Antre | Pò Antre / Sòti, Enfòmasyon sou pwodwi |

| 10 | TRACEDATA0 | Tras done 0 | Sòti | Pò Antre / Sòti, Enfòmasyon sou pwodwi |

| 11 | TRACEDATA1 | Tras done 1 | Sòti | Pò Antre / Sòti, Enfòmasyon sou pwodwi |

| 12 | TRACEDATA2 | Tras done 2 | Sòti | Pò Antre / Sòti, Enfòmasyon sou pwodwi |

| 13 | TRACEDATA3 | Tras done 3 | Sòti | Pò Antre / Sòti, Enfòmasyon sou pwodwi |

| 14 | TRACECLK | Trace Clock | Sòti | Pò Antre / Sòti, Enfòmasyon sou pwodwi |

- SWJ-DP

- SWJ-DP sipòte Serial Wire Debug Port (SWCLK, SWDIO), JTAG Debug Port (TDI, TDO, TMS, TCK, TRST_N), ak pwodiksyon tras soti nan fil seri Viewer (SWV).

- Lè w sèvi ak SWV a, tanpri mete yon bit ki aplikab ki pèmèt revèy la a 1 (pwovizyon pou revèy) nan rezèv revèy la epi sispann enskri ([CGSPCLKEN] ). Pou plis detay, gade "Kontwòl revèy ak mòd operasyon" ak "Pò Antre/Sòti" nan manyèl referans la.

- J laTAG Debug Port oswa PIN TRST_N pa egziste depann sou pwodwi a. Pou plis detay, gade "Enfòmasyon sou pwodwi" nan manyèl referans la.

- ETM

- ETM sipòte siyal done nan kat broch (TRACEDATA) ak yon sèl PIN siyal revèy (TRACECLK).

- Lè w sèvi ak ETM a, tanpri mete yon bit ki aplikab pou pèmèt revèy la a 1 (pwovizyon pou revèy) nan rezèv revèy la epi sispann enskri ([CGSPCLKEN] ). Pou plis detay, gade "Kontwòl revèy ak mòd operasyon" ak "Pò Antre/Sòti" nan manyèl referans la.

- ETM pa sipòte tou depann de pwodwi a. Pou plis detay, gade "Enfòmasyon sou pwodwi" nan manyèl referans la.

Fonksyon ak operasyon

Revèy Pwovizyon pou

Lè w sèvi ak Trace oswa SWV, tanpri mete yon bit ki aplikab ki pèmèt revèy la a 1 (pwovizyon pou revèy) nan rejis sispann rezèv revèy ADC Trace Clock ([CGSPCLKEN] ). Pou plis detay, gade "Kontwòl revèy ak mòd operasyon" nan manyèl referans la.

Koneksyon ak Zouti Debug

- Konsènan yon koneksyon ak zouti debug, gade rekòmandasyon manifakti yo. Broch koòdone debug gen yon rezistans rale-up ak yon rezistans rale-desann. Lè broch koòdone debug yo konekte ak ekstèn pull-up oswa pulldown, tanpri peye atansyon sou nivo opinyon.

- Lè fonksyon sekirite a pèmèt, CPU a pa ka konekte ak zouti debug la.

Fonksyon periferik nan mòd Halt

- Mòd la kenbe vle di ke eta a kote CPU a sispann (kraze) sou zouti nan debogaj

- Lè CPU a antre nan mòd nan kanpe, revèy la watchdog (WDT) otomatikman sispann. Lòt fonksyon periferik kontinye ap fonksyone.

Itilizasyon Egzample

- Broch koòdone debug yo ka itilize tou kòm pò jeneral.

- Apre lageasing reset, the particular pins of the debug interface pins are initialized as the debug interface pins. The other debug interface pins should be changed to the debug interface pins if needed.

Debug koòdone Debug broch koòdone JTAG TRST_N TDI TDO TCK TMS TRACEDATA [3:0] TRACECLK SW – – SWV SWCLK SWDIO Debug pins status after releasing reset

Valab

Valab

Valab

Valab

Valab

Envalid

Envalid

JTAG (Ak TRST_N)

✔ ✔ ✔ ✔ ✔ N/A N/A JTAG (San TRST_N)

N/A

✔

✔

✔

✔

N/A

N/A

JTAG+TRASE ✔ ✔ ✔ ✔ ✔ ✔ ✔ SW N/A N/A N/A ✔ ✔ N/A N/A SW+TRASE N/A N/A N/A ✔ ✔ ✔ ✔ SW + SWV N/A N/A ✔ ✔ ✔ N/A N/A Fonksyon debug enfim N/A N/A N/A N/A N/A N/A N/A

Prekosyon

Pwen enpòtan pou itilize broch entèfas debogaj yo itilize kòm pò jeneral

- Apre lageasing reset, if the debug interface pins are used as the general I/O ports by the user program, the debug tool cannot be connected.

- Si broch koòdone debug yo itilize pou lòt fonksyon, tanpri peye atansyon sou anviwònman yo.

- Si zouti debug la pa ka konekte, li ka refè koneksyon debug pou efase memwa flash la lè l sèvi avèk yon sèl mòd BOOT soti nan ekstèn. Pou plis detay, tanpri al gade manyèl referans "Flash memwa".

Istwa revizyon

| Revizyon | Dat | Deskripsyon |

| 1.0 | 2017-09-04 | Premye lage |

|

1.1 |

2018-06-19 |

– Kontni

Modifye Table of Contents to Contents -1 Deskripsyon ARM modifye pou bra. -2. Konfigirasyon Referans "manyèl referans" ajoute nan SWJ-DP Referans "manyèl referans" ajoute nan SWJ-ETM |

|

1.2 |

2018-10-22 |

– Konvansyon

Modifye eksplikasyon sou trademark – 4. Itilizasyon Egzample Te ajoute ansyenample pou SW+TRACE nan Table4.1 – Ranplase RESTRIKSYON SOU ITILIZE PWODWI |

|

1.3 |

2019-07-26 |

– Figi 2.1 revize

– 2 Te ajoute revèy pou itilize fonksyon SWV. – 3.1 Te ajoute revèy pou itilize fonksyon SWV. modifye soti nan "ETM" nan "Trace". – 3.3 Te ajoute deskripsyon mòd kenbe. |

| 1.4 | 2024-10-31 | - Aparans mete ajou |

RESTRIKSYON SOU ITILIZE PWODWI

Toshiba Corporation ak filiales li yo ak afilye yo kolektivman refere yo kòm "TOSHIBA".

Materyèl, lojisyèl ak sistèm ki dekri nan dokiman sa a kolektivman refere yo kòm "Pwodwi".

- TOSHIBA rezève dwa pou fè chanjman nan enfòmasyon ki nan dokiman sa a ak pwodwi ki gen rapò san avètisman.

- Dokiman sa a ak nenpòt enfòmasyon ki ladan l yo pa ka repwodui san pèmisyon alekri anvan TOSHIBA. Menm avèk pèmisyon alekri TOSHIBA, repwodiksyon akseptab sèlman si repwodiksyon se san chanjman/omisyon.

- Menmsi TOSHIBA travay kontinyèlman pou amelyore kalite ak fyab pwodwi a, pwodwi a ka fonksyone byen oswa echwe. Kliyan yo responsab pou konfòme yo ak estanda sekirite yo epi pou yo bay bon jan konsepsyon ak pwoteksyon pou pyès ki nan konpitè, lojisyèl, ak sistèm yo ki minimize risk epi evite sitiyasyon kote yon malfonksyònman oswa echèk nan yon pwodwi ka lakòz pèt nan lavi moun, blesi kòporèl oswa domaj nan pwopriyete, ki gen ladan pèt done oswa koripsyon. Anvan kliyan yo sèvi ak pwodwi a, kreye desen ki gen ladan pwodwi a, oswa enkòpore pwodwi a nan pwòp aplikasyon yo, kliyan yo dwe tou refere ak konfòme yo ak (a) dènye vèsyon yo nan tout enfòmasyon TOSHIBA ki enpòtan, ki gen ladan san limitasyon, dokiman sa a, espesifikasyon yo. , fèy done yo ak nòt aplikasyon pou pwodwi yo ak prekosyon ak kondisyon ki dekri nan "Toshiba Semiconductor Reliability Handbook" ak (b) enstriksyon yo pou aplikasyon an ak ki pwodwi a pral itilize ak oswa pou. Kliyan yo se sèlman responsab pou tout aspè nan konsepsyon pwodwi yo oswa aplikasyon yo, ki gen ladan men pa limite a (a) detèmine si apwopriye a nan itilizasyon Pwodwi sa a nan konsepsyon oswa aplikasyon sa yo; (b) evalye ak detèmine aplikab nenpòt enfòmasyon ki nan dokiman sa a, oswa nan tablo, dyagram, pwogram, algorithm, s.ampsikui aplikasyon yo, oswa nenpòt lòt dokiman referans; epi (c) valide tout paramèt opere pou konsepsyon ak aplikasyon sa yo. TOSHIBA PA ASime Okenn RESPONSABILITE POU DESIGN OSWA APLIKASYON PWODWI KLIYAN.

- PWODWI PA NI NI NI NI GEN GEN GENYEN NI GARANTI POU ITILIZE NAN EKIPMAN OSWA SISTÈM KI MANDE NIVO KALITÈ AK/OSWA Fyab ekstraòdinè, AK/OSWA YON DEFÒKSYON OSWA ECHEK KI KA KOZE PÈDI LAVI MOUN, BÒMASYON, PWOPRIYÈ, PWOPRIYÈ AK PWODIKSYON. SERYE PUBLIK IMPACT ("ITILIZASYON SOU PWOBLÈ"). Eksepte pou aplikasyon espesifik jan yo endike ekspreseman nan dokiman sa a, Itilizasyon Envolontè gen ladan, san limitasyon, ekipman yo itilize nan enstalasyon nikleyè, ekipman yo itilize nan endistri ayewospasyal, ekipman medikal, ekipman yo itilize pou otomobil, tren, bato, ak lòt transpò, ekipman siyal trafik. , ekipman yo itilize pou kontwole konbisyon oswa eksplozyon, aparèy sekirite, asansè ak èskalator, aparèy ki gen rapò ak pouvwa elektrik, ak ekipman yo itilize nan domèn ki gen rapò ak finans. SI OU ITILIZE PWODWI A POU PWODWI SA SAB, TOSHIBA PA ASime Okenn RESPONSABILITE POU PWODWI A. Pou plis detay, tanpri kontakte reprezantan lavant TOSHIBA ou a.

- Pa demonte, analize, reverse-enjenyè, chanje, modifye, tradui oswa kopye pwodwi, kit an antye oswa an pati.

- Pwodwi yo pa dwe itilize oswa enkòpore nan nenpòt pwodwi oswa sistèm ki gen fabrike, itilizasyon oswa vann entèdi dapre nenpòt lwa oswa règleman ki aplikab.

- Enfòmasyon ki genyen ladan l yo prezante sèlman kòm konsèy pou itilizasyon pwodwi. TOSHIBA pa pran okenn responsablite pou nenpòt vyolasyon patant oswa nenpòt lòt dwa pwopriyete entelektyèl twazyèm pati ki ka lakòz nan itilizasyon Pwodwi a. Pa gen okenn lisans sou okenn dwa pwopriyete entelektyèl akòde pa dokiman sa a, si eksprime oswa implicite, pa estoppel oswa otreman.

- PA YON AKÒ EKRI SIYEN, SÒF JAN KONDISYON AK KONDISYON VANT PWODWI YO YO PWOVIZE, AK PWODISYON MAKSIMÒM LA LWA OBLÈ, TOSHIBA (1) PA ASime Okenn RESPONSABILITE KELÒT, TANKOU SAN LIMITATION, ENDIRÈK, ESPESYÈL. DOmaj OSWA PÈT ENSEDANTAN, KI ENKLI SAN LIMITATION, PÈDI PROFI, PÈDI OPÒNITE, ENTÈRIPYON BIZNIS AK PÈD DONE, AK (2) REJTE NENPÒT AK TOUT GARANTI AK KONDISYON EXPRESS OSWA ENPLIKITE KI GENYEN AK VANT, ITILIZYON ENFÒMASYON, PWODWI, ENKLI. GARANTI OSWA KONDISYON MARCHANDABILITE, APTITE POU YON OBJEKTIF PARTICULIER, PREZISYON ENFÒMASYON, OSWA NON INFRACTION.

- Pa sèvi ak oswa fè disponib pwodwi oswa lojisyèl ki gen rapò oswa teknoloji pou nenpòt ki rezon militè, ki gen ladan san limitasyon, pou konsepsyon, devlopman, itilize, estoke oswa fabrikasyon zam nikleyè, chimik, oswa byolojik oswa pwodwi teknoloji misil (zam destriksyon an mas) . Pwodwi ak lojisyèl ak teknoloji ki gen rapò ka kontwole anba lwa ak règleman ekspòtasyon aplikab yo ki gen ladan, san limitasyon, Lwa sou Echanj Etranjè Japonè ak Komès Etranjè ak Règleman Administrasyon Ekspòtasyon Ameriken an. Ekspòtasyon ak re-ekspòtasyon pwodwi oswa lojisyèl oswa teknoloji ki gen rapò ak entèdi entèdi eksepte an konfòmite ak tout lwa ak règleman ekspòtasyon ki aplikab yo.

- Tanpri kontakte reprezantan lavant TOSHIBA ou a pou plis detay sou zafè anviwònman tankou konpatibilite RoHS nan pwodwi. Tanpri itilize Pwodwi a an konfòmite ak tout lwa ak règleman ki aplikab ki kontwole enklizyon oswa itilizasyon sibstans kontwole, ki gen ladan san limitasyon, Directive RoHS Inyon Ewopeyen an. TOSHIBA OKENN RESPONSABILITE POU DOMAS OUBYEN PÈT KI GENYEN KÒZ KI RESULTE KI PA KONFÒMITE AK LWA AK RÈGLEMAN APLIKAB.

Toshiba Electronics Devices & Storage Corporation: https://toshiba.semicon-storage.com/

Dokiman / Resous

|

TOSHIBA DEBUG-A 32 Bit RISC mikrokontroleur [pdfEnstriksyon yo DEBUG-A 32 Bit RISC Microcontroller, DEBUG-A, 32 Bit RISC Microcontroller, RISC Microcontroller, Microcontroller |